JP2011205101A - 半導体メモリ装置及びその製造方法 - Google Patents

半導体メモリ装置及びその製造方法 Download PDFInfo

- Publication number

- JP2011205101A JP2011205101A JP2011065756A JP2011065756A JP2011205101A JP 2011205101 A JP2011205101 A JP 2011205101A JP 2011065756 A JP2011065756 A JP 2011065756A JP 2011065756 A JP2011065756 A JP 2011065756A JP 2011205101 A JP2011205101 A JP 2011205101A

- Authority

- JP

- Japan

- Prior art keywords

- pull

- well region

- semiconductor memory

- memory device

- active region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 222

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 64

- 239000000758 substrate Substances 0.000 claims abstract description 124

- 239000004020 conductor Substances 0.000 claims abstract description 62

- 229910052751 metal Inorganic materials 0.000 claims description 166

- 239000002184 metal Substances 0.000 claims description 166

- 238000000034 method Methods 0.000 claims description 34

- 229910021332 silicide Inorganic materials 0.000 claims description 21

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 21

- 238000005530 etching Methods 0.000 claims description 8

- 238000003860 storage Methods 0.000 claims description 8

- 230000010354 integration Effects 0.000 abstract description 10

- 239000010408 film Substances 0.000 description 78

- 101100215339 Arabidopsis thaliana ACT11 gene Proteins 0.000 description 47

- 101100217138 Mus musculus Actr10 gene Proteins 0.000 description 47

- 101100215368 Dictyostelium discoideum act21 gene Proteins 0.000 description 43

- 101100215341 Arabidopsis thaliana ACT12 gene Proteins 0.000 description 41

- 101100161922 Dictyostelium discoideum act22 gene Proteins 0.000 description 38

- 101100054763 Dictyostelium discoideum act23 gene Proteins 0.000 description 37

- 238000002955 isolation Methods 0.000 description 25

- 238000009792 diffusion process Methods 0.000 description 16

- 239000012535 impurity Substances 0.000 description 16

- 238000005468 ion implantation Methods 0.000 description 15

- 101100054764 Dictyostelium discoideum act24 gene Proteins 0.000 description 13

- 239000007769 metal material Substances 0.000 description 12

- 238000010586 diagram Methods 0.000 description 10

- 101100054766 Dictyostelium discoideum act25 gene Proteins 0.000 description 9

- 238000000059 patterning Methods 0.000 description 9

- 101100054767 Dictyostelium discoideum act26 gene Proteins 0.000 description 8

- 239000010949 copper Substances 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- 101100463786 Zea mays PG14 gene Proteins 0.000 description 7

- 125000006850 spacer group Chemical group 0.000 description 7

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 5

- 229910052750 molybdenum Inorganic materials 0.000 description 5

- 239000011733 molybdenum Substances 0.000 description 5

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 5

- 229910052721 tungsten Inorganic materials 0.000 description 5

- 239000010937 tungsten Substances 0.000 description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 150000002500 ions Chemical class 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229920005591 polysilicon Polymers 0.000 description 4

- 229910052707 ruthenium Inorganic materials 0.000 description 4

- 229910052715 tantalum Inorganic materials 0.000 description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- 239000005380 borophosphosilicate glass Substances 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 239000005360 phosphosilicate glass Substances 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- QXZUUHYBWMWJHK-UHFFFAOYSA-N [Co].[Ni] Chemical compound [Co].[Ni] QXZUUHYBWMWJHK-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

- H10B10/12—Static random access memory [SRAM] devices comprising a MOSFET load element

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

Landscapes

- Semiconductor Memories (AREA)

Abstract

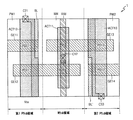

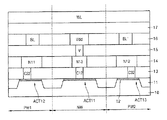

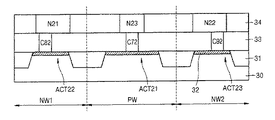

【解決手段】第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、第1ウェル領域は、第2ウェル領域と第3ウェル領域との間に配され、第1ウェル領域は、第1タイプ導電体を含み、第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板;第1ウェル領域に一列に形成され、電源端子を共有する第1プルアップ素子及び第2プルアップ素子;第2ウェル領域に第1プルアップ素子と隣接するように配される第1プルダウン素子;第3ウェル領域に第2プルアップ素子と隣接するように配される第2プルダウン素子;第2ウェル領域に第2プルアップ素子と隣接するように配される第1アクセス素子;第3ウェル領域に第1プルアップ素子と隣接するように形成される第2アクセス素子;を含む半導体メモリ装置である。

【選択図】図1

Description

5 電子システム

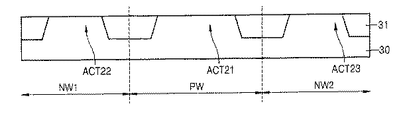

10,30 基板

11,31 素子分離膜

12,32 シリサイド層

13,33 第1絶縁層

14,34 第2絶縁層

15,35 第3絶縁層

16,36 第4絶縁層

17,37 第5絶縁層

51 プロセッサ

52 メモリ

53 入出力装置

111,112,113,311,312,313 ソース領域及びドレイン領域

131,331 ゲート絶縁膜

132,332 キャッピング膜

133,333 スペーサ

511 記憶装置

Claims (59)

- 第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板と、

前記第1ウェル領域に一列に形成され、電源端子を共有する第1プルアップ素子及び第2プルアップ素子と、

前記第2ウェル領域に、前記第1プルアップ素子と隣接するように配される第1プルダウン素子と、

前記第3ウェル領域に、前記第2プルアップ素子と隣接するように配される第2プルダウン素子と、

前記第2ウェル領域に、前記第2プルアップ素子と隣接するように配される第1アクセス素子と、

前記第3ウェル領域に、前記第1プルアップ素子と隣接するように配される第2アクセス素子と、を含む半導体メモリ装置。 - 前記第1プルアップ素子及び第2プルアップ素子は、単一活性領域に配され、前記単一活性領域は、前記第1ウェル領域に含まれることを特徴とする請求項1に記載の半導体メモリ装置。

- 前記第1プルアップ素子及び前記第1プルダウン素子は、第1インバータを構成し、

前記第2プルアップ素子及び前記第2プルダウン素子は、第2インバータを構成することを特徴とする請求項1に記載の半導体メモリ装置。 - 前記第1アクセス素子は、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結され、

前記第2アクセス素子は、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結されることを特徴とする請求項3に記載の半導体メモリ装置。 - 前記第1アクセス素子は、ワードラインに印加される電圧によって制御され、1対のビットラインのうち第1ビットラインを、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結させる第1アクセス・トランジスタを含むことを特徴とする請求項3に記載の半導体メモリ装置。

- 前記第2アクセス素子は、前記ワードラインに印加される電圧によって制御され、前記1対のビットラインのうち第2ビットラインを、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結させる第2アクセス・トランジスタを含むことを特徴とする請求項5に記載の半導体メモリ装置。

- 前記第1アクセス素子及び前記第1プルダウン素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第2ウェル領域に含まれることを特徴とする請求項1に記載の半導体メモリ装置。

- 前記第2アクセス素子及び前記第2プルダウン素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第3ウェル領域に含まれることを特徴とする請求項1に記載の半導体メモリ装置。

- 前記第1タイプ導電体は、N型導電体であって、前記第2タイプ導電体は、P型導電体であることを特徴とする請求項1に記載の半導体メモリ装置。

- 前記第1プルアップ素子は、前記電源端子に連結されるソースを有するPチャネル・トランジスタを含み、

前記第1プルダウン素子は、前記Pチャネル・トランジスタのドレインに連結されるドレイン、前記Pチャネル・トランジスタのゲートに連結されるゲート、及び接地端子に連結されるソースを有するNチャネル・トランジスタを含むことを特徴とする請求項9に記載の半導体メモリ装置。 - 前記第2プルアップ素子は、前記電源端子に連結されるソースを有するPチャネル・トランジスタを含み、

前記第2プルダウン素子は、前記Pチャネル・トランジスタのドレインに連結されるドレイン、前記Pチャネル・トランジスタのゲートに連結されるゲート、及び接地端子に連結されるソースを有するNチャネル・トランジスタを含むことを特徴とする請求項9に記載の半導体メモリ装置。 - 前記第1アクセス素子は、ワードラインに連結されるゲートを有するNチャネル・トランジスタを含み、

前記第2アクセス素子は、前記ワードラインに連結されるゲートを有するNチャネル・トランジスタを含むことを特徴とする請求項9に記載の半導体メモリ装置。 - 前記半導体メモリ装置は、電子システムに含まれ、

前記電子システムは、バスを介して互いに通信するメモリ部、プロセッサ及び入出力装置を含み、

前記プロセッサは、前記半導体メモリ装置を含む記憶装置を含むことを特徴とする請求項1に記載の半導体メモリ装置。 - 第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板と、

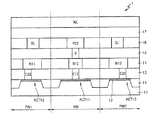

前記第1ウェル領域に含まれ、第1プルアップ素子及び第2プルアップ素子が一列に配される第1活性領域と、

前記第2ウェル領域に含まれ、前記第2プルアップ素子に隣接した第1アクセス素子、及び前記第1プルアップ素子に隣接した第1プルダウン素子が配される第2活性領域と、

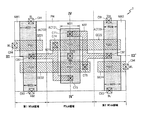

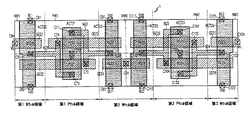

前記第3ウェル領域に含まれ、前記第1プルアップ素子に隣接した第2アクセス素子、及び前記第2プルアップ素子に隣接した第2プルダウン素子が配される第3活性領域と、を含む半導体メモリ装置。 - 前記第1プルアップ素子及び第2プルアップ素子は、第1方向に沿って一列に配され、

前記第1プルアップ素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルダウン素子及び前記第2アクセス素子と隣接するように配され、

前記第2プルアップ素子は、前記第2方向に沿って、前記第2プルダウン素子及び前記第1アクセス素子と隣接するように配されることを特徴とする請求項14に記載の半導体メモリ装置。 - 前記第1活性領域及び第2活性領域の上部を横切る方向に、前記基板の上部に形成される第1ゲート電極と、

前記第1活性領域及び第3活性領域の上部を横切る方向に、前記基板の上部に形成される第2ゲート電極と、をさらに含み、

前記第1プルアップ素子と前記第1プルダウン素子は、前記第1ゲート電極に共通して連結されて第1インバータを構成し、前記第2プルアップ素子と前記第2プルダウン素子は、前記第2ゲート電極に共通して連結されて第2インバータを構成することを特徴とする請求項14に記載の半導体メモリ装置。 - 前記第1アクセス素子を、前記第2インバータの入力端子、及び前記第1インバータの出力端子に連結させる第1金属配線と、

前記第2アクセス素子を、前記第1インバータの入力端子、及び前記第2インバータの出力端子に連結させる第2金属配線と、をさらに含むことを特徴とする請求項16に記載の半導体メモリ装置。 - 前記第1金属配線及び前記第2金属配線は、同一層に配されることを特徴とする請求項17に記載の半導体メモリ装置。

- 前記第1金属配線及び前記第2金属配線は、互いに異なる層に配されることを特徴とする請求項17に記載の半導体メモリ装置。

- 前記第2活性領域の上部を横切る方向に、前記基板の上部に形成される第3ゲート電極と、

前記第3活性領域の上部を横切る方向に、前記基板の上部に形成される第4ゲート電極と、をさらに含むことを特徴とする請求項16に記載の半導体メモリ装置。 - 前記第3ゲート電極及び第4ゲート電極と平行な方向に伸張するように、前記基板の上部に形成され、前記第3ゲート電極及び第4ゲート電極に連結されるワードラインをさらに含むことを特徴とする請求項20に記載の半導体メモリ装置。

- 前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される1対のビットラインをさらに含み、

前記1対のビットラインのうち第1ビットラインは、前記第1アクセス素子に連結され、

前記1対のビットラインのうち第2ビットラインは、前記第2アクセス素子に連結されることを特徴とする請求項14に記載の半導体メモリ装置。 - 前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される電源電極ラインをさらに含み、

前記電源電極ラインは、前記第1プルアップ素子と第2プルアップ素子との間に形成されたコンタクトプラグを介して、前記第1プルアップ素子及び第2プルアップ素子に連結されることを特徴とする請求項14に記載の半導体メモリ装置。 - 前記第1タイプ導電体は、N型導電体であって、前記第2タイプ導電体は、P型導電体であることを特徴とする請求項14に記載の半導体メモリ装置。

- 第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板を提供する段階であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む段階と、

前記第1ウェル領域上に含まれた第1活性領域に、第1プルアップ素子及び第2プルアップ素子を一列に形成する段階と、

前記第2ウェル領域上に含まれた第2活性領域に、前記第1プルアップ素子と隣接した第1プルダウン素子と、前記第2プルアップ素子と隣接した第1アクセス素子と、を形成する段階と、

前記第3ウェル領域上に含まれた第3活性領域に、前記第2プルアップ素子と隣接した第2プルダウン素子と、前記第1プルアップ素子と隣接した第2アクセス素子と、を形成する段階と、を含む半導体メモリ装置の製造方法。 - 前記第1プルアップ素子及び第2プルアップ素子は、第1方向に沿って一列に形成され、

前記第1プルアップ素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルダウン素子及び前記第2アクセス素子と隣接するように配され、

前記第2プルアップ素子は、前記第2方向に沿って、前記第2プルダウン素子及び前記第1アクセス素子と隣接するように配されることを特徴とする請求項25に記載の半導体メモリ装置の製造方法。 - 前記第1活性領域、第2活性領域及び第3活性領域のうち少なくとも1つの領域の上部を横切る方向に、前記基板の上部に形成される複数の導電性パターンを形成する段階をさらに含み、

前記第1プルアップ素子と前記第1プルダウン素子は、前記複数の導電性パターンのうち一つに共通して連結されて第1インバータを構成し、

前記第2プルアップ素子と前記第2プルダウン素子は、前記複数の導電性パターンのうち他の一つに共通して連結されて第2インバータを構成することを特徴とする請求項25に記載の半導体メモリ装置の製造方法。 - 前記第1アクセス素子を、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結させる第1金属配線;前記第2アクセス素子を、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結させる第2金属配線;を形成する段階をさらに含むことを特徴とする請求項27に記載の半導体メモリ装置の製造方法。

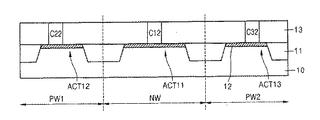

- 前記第1金属配線及び第2金属配線を形成する段階は、

前記基板の上部に第1絶縁膜を形成する段階と、

前記第1絶縁膜の一部領域をエッチングして複数の第1コンタクトホールを形成し、前記複数の第1コンタクトホールに金属を充填して複数のコンタクトプラグを形成する段階と、

前記複数のコンタクトプラグが形成された前記第1絶縁膜上に、第2絶縁膜を形成する段階と、

前記第2絶縁膜の一部領域をエッチングして複数の第2コンタクトホールを形成し、前記複数の第2コンタクトホールに金属を充填し、前記第1金属配線及び第2金属配線を形成する段階と、を含み、

前記第1金属配線及び第2金属配線は、前記複数のコンタクトプラグを介して、前記第1ウェル領域、第2ウェル領域及び第3ウェル領域のうち少なくとも一つに連結されることを特徴とする請求項28に記載の半導体メモリ装置の製造方法。 - 前記第1ウェル領域、第2ウェル領域及び第3ウェル領域のうち少なくとも一つにシリサイド層を形成する段階をさらに含み、

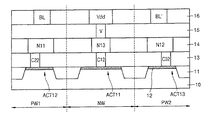

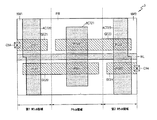

前記複数のコンタクトプラグは、前記シリサイド層に連結されることを特徴とする請求項29に記載の半導体メモリ装置の製造方法。 - 第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板と、

前記第1ウェル領域に一列に形成されて接地端子を共有する第1プルダウン素子及び第2プルダウン素子と、

前記第2ウェル領域に、前記第1プルダウン素子と隣接するように配される第1プルアップ素子と、

前記第3ウェル領域に、前記第2プルダウン素子と隣接するように配される第2プルアップ素子と、

前記第2ウェル領域に、前記第2プルダウン素子と隣接するように配される第1アクセス素子と、

前記第3ウェル領域に、前記第1プルダウン素子と隣接するように配される第2アクセス素子と、を含む半導体メモリ装置。 - 前記第1プルダウン素子及び第2プルダウン素子は、単一活性領域に配され、前記単一活性領域は、前記第1ウェル領域に含まれることを特徴とする請求項31に記載の半導体メモリ装置。

- 前記第1プルダウン素子及び前記第1プルアップ素子は、第1インバータを構成し、

前記第2プルダウン素子及び前記第2プルアップ素子は、第2インバータを構成することを特徴とする請求項31に記載の半導体メモリ装置。 - 前記第1アクセス素子は、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結され、

前記第2アクセス素子は、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結されることを特徴とする請求項33に記載の半導体メモリ装置。 - 前記第1アクセス素子は、ワードラインに印加される電圧によって制御され、1対のビットラインのうち第1ビットラインを、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結させる第1アクセス・トランジスタを含むことを特徴とする請求項33に記載の半導体メモリ装置。

- 前記第2アクセス素子は、前記ワードラインに印加される電圧によって制御され、前記1対のビットラインのうち第2ビットラインを、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結させる第2アクセス・トランジスタを含むことを特徴とする請求項35に記載の半導体メモリ装置。

- 前記第1アクセス素子及び前記第1プルアップ素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第2ウェル領域に含まれることを特徴とする請求項31に記載の半導体メモリ装置。

- 前記第2アクセス素子及び前記第2プルアップ素子は、単一活性領域内に一列に配され、前記単一活性領域は、前記第2ウェル領域に含まれることを特徴とする請求項31に記載の半導体メモリ装置。

- 前記第1タイプ導電体は、P型導電体であって、前記第2タイプ導電体は、N型導電体であることを特徴とする請求項31に記載の半導体メモリ装置。

- 前記第1プルダウン素子は、前記接地端子に連結されるソースを有するNチャネル・トランジスタを含み、

前記第1プルアップ素子は、前記Nチャネル・トランジスタのドレインに連結されるドレイン、前記Nチャネル・トランジスタのゲートに連結されるゲート、及び電源端子に連結されるソースを有するPチャネル・トランジスタを含むことを特徴とする請求項39に記載の半導体メモリ装置。 - 前記第2プルダウン素子は、前記接地端子に連結されるソースを有するNチャネル・トランジスタを含み、

前記第2プルアップ素子は、前記Nチャネル・トランジスタのドレインに連結されるドレイン、前記Nチャネル・トランジスタのゲートに連結されるゲート、及び電源端子に連結されるソースを有するPチャネル・トランジスタを含むことを特徴とする請求項39に記載の半導体メモリ装置。 - 前記第1アクセス素子は、ワードラインに連結されるゲートを有するPチャネル・トランジスタを含み、

前記第2アクセス素子は、前記ワードラインに連結されるゲートを有するPチャネル・トランジスタを含むことを特徴とする請求項39に記載の半導体メモリ装置。 - 前記半導体メモリ装置は、電子システムに含まれ、

前記電子システムは、バスを介して互いに通信するメモリ部、プロセッサ及び入出力装置を含み、

前記プロセッサは、前記半導体メモリ装置を含む記憶装置を含むことを特徴とする請求項31に記載の半導体メモリ装置。 - 第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板と、

前記第1ウェル領域に含まれ、第1プルダウン素子及び第2プルダウン素子が一列に配される第1活性領域と、

前記第2ウェル領域に含まれ、前記第2プルダウン素子に隣接した第1アクセス素子、及び前記第1プルダウン素子に隣接した第1プルアップ素子が配される第2活性領域と、

前記第3ウェル領域に含まれ、前記第1プルダウン素子に隣接した第2アクセス素子、及び前記第2プルダウン素子に隣接した第2プルアップ素子が配される第3活性領域と、を含む半導体メモリ装置。 - 前記第1プルダウン素子及び第2プルダウン素子は、第1方向に沿って一列に配され、

前記第1プルダウン素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルアップ素子及び前記第2アクセス素子と隣接するように配され、

前記第2プルダウン素子は、前記第2方向に沿って、前記第2プルアップ素子及び前記第1アクセス素子と隣接するように配されることを特徴とする請求項44に記載の半導体メモリ装置。 - 前記第1活性領域及び第2活性領域の上部を横切る方向に、前記基板の上部に形成される第1ゲート電極と、

前記第1活性領域及び第3活性領域の上部を横切る方向に、前記基板の上部に形成される第2ゲート電極と、をさらに含み、

前記第1プルダウン素子と前記第1プルアップ素子は、前記第1ゲート電極に共通して連結されて第1インバータを構成し、前記第2プルダウン素子と前記第2プルアップ素子は、前記第2ゲート電極に共通して連結されて第2インバータを構成することを特徴とする請求項44に記載の半導体メモリ装置。 - 前記第1アクセス素子を、前記第2インバータの入力端子、及び前記第1インバータの出力端子に連結させる第1金属配線と、

前記第2アクセス素子を、前記第1インバータの入力端子、及び前記第2インバータの出力端子に連結させる第2金属配線と、をさらに含むことを特徴とする請求項46に記載の半導体メモリ装置。 - 前記第1金属配線及び前記第2金属配線は、同一層に配されることを特徴とする請求項47に記載の半導体メモリ装置。

- 前記第1金属配線及び前記第2金属配線は、互いに異なる層に配されることを特徴とする請求項47に記載の半導体メモリ装置。

- 前記第2活性領域の上部を横切る方向に、前記基板の上部に形成される第3ゲート電極と、

前記第3活性領域の上部を横切る方向に、前記基板の上部に形成される第4ゲート電極と、をさらに含むことを特徴とする請求項46に記載の半導体メモリ装置。 - 前記第3ゲート電極及び第4ゲート電極と平行な方向に伸張するように、前記基板の上部に形成され、前記第3ゲート電極及び第4ゲート電極に連結されるワードラインをさらに含むことを特徴とする請求項50に記載の半導体メモリ装置。

- 前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される1対のビットラインをさらに含み、

前記1対のビットラインのうち第1ビットラインは、前記第1アクセス素子の一端に連結され、

前記1対のビットラインのうち第2ビットラインは、前記第2アクセス素子の他端に連結されることを特徴とする請求項44に記載の半導体メモリ装置。 - 前記第1活性領域、第2活性領域及び第3活性領域と平行な方向に伸張するように、前記基板の上部に形成される接地電極ラインをさらに含み、

前記接地電極ラインは、前記第1プルダウン素子と第2プルダウン素子との間に形成されたコンタクトプラグを介して、前記第1プルダウン素子及び第2プルダウン素子に連結されることを特徴とする請求項44に記載の半導体メモリ装置。 - 前記第1タイプ導電体は、P型導電体であって、前記第2タイプ導電体は、N型導電体であることを特徴とする請求項44に記載の半導体メモリ装置。

- 第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板を提供する段階であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む段階と、

前記第1ウェル領域上に含まれた第1活性領域に、第1プルダウン素子及び第2プルダウン素子を一列に形成する段階と、

前記第2ウェル領域上に含まれた第2活性領域に、前記第1プルダウン素子と隣接した第1プルアップ素子及び前記第2プルダウン素子と隣接した第1アクセス素子を形成する段階と、

前記第3ウェル領域上に含まれた第3活性領域に、前記第2プルダウン素子と隣接した第2プルアップ素子と、前記第1プルダウン素子と隣接した第2アクセス素子と、を形成する段階と、を含む半導体メモリ装置の製造方法。 - 前記第1プルダウン素子及び第2プルダウン素子は、第1方向に沿って一列に形成され、

前記第1プルダウン素子は、前記第1方向と垂直である第2方向に沿って、前記第1プルアップ素子及び前記第2アクセス素子と隣接するように配され、

前記第2プルダウン素子は、前記第2方向に沿って、前記第2プルアップ素子及び前記第1アクセス素子と隣接するように配されることを特徴とする請求項55に記載の半導体メモリ装置の製造方法。 - 前記第1活性領域、第2活性領域及び第3活性領域のうち少なくとも1つの領域の上部を横切る方向に、前記基板の上部に形成される複数の導電性パターンを形成する段階をさらに含み、

前記第1プルダウン素子と前記第1プルアップ素子は、前記複数の導電性パターンのうち一つに共通して連結されて第1インバータを構成し、

前記第2プルダウン素子と前記第2プルアップ素子は、前記複数の導電性パターンのうち他の一つに共通して連結されて第2インバータを構成することを特徴とする請求項55に記載の半導体メモリ装置の製造方法。 - 前記第1アクセス素子を、前記第2インバータの入力端子と、前記第1インバータの出力端子と、に連結させる第1金属配線;前記第2アクセス素子を、前記第1インバータの入力端子と、前記第2インバータの出力端子と、に連結させる第2金属配線;を形成する段階をさらに含むことを特徴とする請求項57に記載の半導体メモリ装置の製造方法。

- 第1ウェル領域、第2ウェル領域及び第3ウェル領域を含む基板であって、前記第1ウェル領域は、前記第2ウェル領域と前記第3ウェル領域との間に配され、前記第1ウェル領域は、第1タイプ導電体を含み、前記第2ウェル領域及び第3ウェル領域は、第2タイプ導電体をそれぞれ含む基板を含み、

前記第1ウェル領域は、第1積層構造を含み、前記第1積層構造は、第1単一活性層上に連続して積層された第1コンタクトプラグ、第1金属絶縁層、ビアプラグ、及び電源電圧または接地電圧ラインを含み、

前記第2ウェル領域は、第2積層構造を含み、前記第2積層構造は、第2単一活性層上に連続して積層された第2コンタクトプラグ及び第2金属絶縁層を含み、

前記第3ウェル領域は、第3積層構造を含み、前記第3積層構造は、第3単一活性層上に連続して積層された第3コンタクトプラグ及び第3金属絶縁層を含むことを特徴とする半導体メモリ装置。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2010-0026406 | 2010-03-24 | ||

| KR20100026406 | 2010-03-24 | ||

| KR1020110001087A KR20110107268A (ko) | 2010-03-24 | 2011-01-05 | 반도체 메모리 장치 및 그 제조 방법 |

| KR10-2011-0001087 | 2011-01-05 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011205101A true JP2011205101A (ja) | 2011-10-13 |

| JP2011205101A5 JP2011205101A5 (ja) | 2014-05-08 |

Family

ID=44656326

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011065756A Pending JP2011205101A (ja) | 2010-03-24 | 2011-03-24 | 半導体メモリ装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20110235407A1 (ja) |

| JP (1) | JP2011205101A (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8598633B2 (en) * | 2012-01-16 | 2013-12-03 | GlobalFoundries, Inc. | Semiconductor device having contact layer providing electrical connections |

| US9111634B2 (en) * | 2012-07-13 | 2015-08-18 | Freescale Semiconductor, Inc. | Methods and structures for multiport memory devices |

| KR20140049356A (ko) * | 2012-10-17 | 2014-04-25 | 삼성전자주식회사 | 반도체 소자 |

| JP6258672B2 (ja) * | 2013-11-21 | 2018-01-10 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| US9251888B1 (en) | 2014-09-15 | 2016-02-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | SRAM cells with vertical gate-all-round MOSFETs |

| KR102223970B1 (ko) * | 2015-03-12 | 2021-03-09 | 삼성전자주식회사 | 반도체 장치, 레이아웃 시스템 및 스탠다드 셀 라이브러리 |

| TWI685088B (zh) * | 2015-07-15 | 2020-02-11 | 聯華電子股份有限公司 | 靜態隨機存取記憶體單元結構以及靜態隨機存取記憶體佈局結構 |

| US9620509B1 (en) * | 2015-10-30 | 2017-04-11 | Taiwan Semiconductor Manufacturing Co., Ltd. | Static random access memory device with vertical FET devices |

| JP2017108031A (ja) * | 2015-12-11 | 2017-06-15 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| KR102256055B1 (ko) | 2017-04-06 | 2021-05-27 | 삼성전자주식회사 | 반도체 소자 |

| US10490558B2 (en) * | 2017-05-31 | 2019-11-26 | Qualcomm Incorporated | Reducing or avoiding mechanical stress in static random access memory (SRAM) strap cells |

| US10276581B1 (en) * | 2017-10-31 | 2019-04-30 | Taiwan Semiconductor Manufacturing Co., Ltd. | Integrated circuit chip and manufacturing method thereof |

| US10861859B2 (en) | 2018-06-29 | 2020-12-08 | Taiwan Semiconductor Manufacturing Company Ltd. | Memory cells with butted contacts and method of forming same |

| US10964705B2 (en) * | 2018-09-10 | 2021-03-30 | Semiconductor Components Industries, Llc | Method of forming a semiconductor device |

| US11048849B2 (en) * | 2018-10-31 | 2021-06-29 | Taiwan Semiconductor Manufacturing Company Ltd. | Integrated circuit and method of manufacturing the same |

| CN111463210B (zh) * | 2020-04-08 | 2021-07-20 | 长江存储科技有限责任公司 | 一种外围电路及三维存储器 |

| CN117395984A (zh) * | 2022-06-29 | 2024-01-12 | 长鑫存储技术有限公司 | 半导体结构及其制作方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003060089A (ja) * | 2001-08-16 | 2003-02-28 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2003086713A (ja) * | 2001-06-28 | 2003-03-20 | Matsushita Electric Ind Co Ltd | Sram装置 |

| JP2003152111A (ja) * | 2001-11-13 | 2003-05-23 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2006269674A (ja) * | 2005-03-23 | 2006-10-05 | Nec Electronics Corp | 半導体集積回路 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6295224B1 (en) * | 1999-12-30 | 2001-09-25 | Stmicroelectronics, Inc. | Circuit and method of fabricating a memory cell for a static random access memory |

| US6898111B2 (en) * | 2001-06-28 | 2005-05-24 | Matsushita Electric Industrial Co., Ltd. | SRAM device |

| US7605447B2 (en) * | 2005-09-22 | 2009-10-20 | International Business Machines Corporation | Highly manufacturable SRAM cells in substrates with hybrid crystal orientation |

| US7592247B2 (en) * | 2006-10-04 | 2009-09-22 | International Business Machines Corporation | Sub-lithographic local interconnects, and methods for forming same |

| US7957178B2 (en) * | 2008-01-04 | 2011-06-07 | Texas Instruments Incorporated | Storage cell having buffer circuit for driving the bitline |

| US8315084B2 (en) * | 2010-03-10 | 2012-11-20 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fully balanced dual-port memory cell |

| US8183639B2 (en) * | 2010-10-07 | 2012-05-22 | Freescale Semiconductor, Inc. | Dual port static random access memory cell layout |

-

2011

- 2011-03-08 US US13/043,009 patent/US20110235407A1/en not_active Abandoned

- 2011-03-24 JP JP2011065756A patent/JP2011205101A/ja active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003086713A (ja) * | 2001-06-28 | 2003-03-20 | Matsushita Electric Ind Co Ltd | Sram装置 |

| JP2003060089A (ja) * | 2001-08-16 | 2003-02-28 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2003152111A (ja) * | 2001-11-13 | 2003-05-23 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP2006269674A (ja) * | 2005-03-23 | 2006-10-05 | Nec Electronics Corp | 半導体集積回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110235407A1 (en) | 2011-09-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2011205101A (ja) | 半導体メモリ装置及びその製造方法 | |

| US20210257470A1 (en) | Semiconductor device | |

| US8976573B2 (en) | Apparatus for SRAM cells | |

| KR100746220B1 (ko) | 적층된 노드 콘택 구조체들과 적층된 박막 트랜지스터들을채택하는 반도체 집적회로들 및 그 제조방법들 | |

| KR101420494B1 (ko) | Rom 셀을 위한 장치 | |

| US7982221B2 (en) | Semiconductor memory device having three dimensional structure | |

| TWI478322B (zh) | 唯讀記憶體單元陣列 | |

| US20090224330A1 (en) | Semiconductor Memory Device and Method for Arranging and Manufacturing the Same | |

| KR20140070306A (ko) | Sram 셀의 컨택 플러그 및 이의 형성 방법 | |

| US10658010B2 (en) | Apparatus for high speed ROM cells | |

| JP7549765B2 (ja) | 単一半導体ダイにおけるモノリシック集積および/または不均一集積の最適化のための統合スケーリングおよびストレッチングプラットフォーム | |

| KR20110107268A (ko) | 반도체 메모리 장치 및 그 제조 방법 | |

| US20180342524A1 (en) | Method of fabricating vertical transistor device | |

| TWI831376B (zh) | 半導體裝置及記憶體裝置的製造方法 | |

| TW201836076A (zh) | 記憶體元件及其製作方法 | |

| CN117500264A (zh) | 半导体装置 | |

| JP2011165882A (ja) | 半導体記憶装置及びその製造方法 | |

| JP2006157045A (ja) | 半導体集積回路装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140324 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140324 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20141226 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20141226 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150113 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150622 |