JP2011014904A - ビアがガウジングされた相互接続構造体及びその製造方法 - Google Patents

ビアがガウジングされた相互接続構造体及びその製造方法 Download PDFInfo

- Publication number

- JP2011014904A JP2011014904A JP2010142938A JP2010142938A JP2011014904A JP 2011014904 A JP2011014904 A JP 2011014904A JP 2010142938 A JP2010142938 A JP 2010142938A JP 2010142938 A JP2010142938 A JP 2010142938A JP 2011014904 A JP2011014904 A JP 2011014904A

- Authority

- JP

- Japan

- Prior art keywords

- dielectric material

- forming

- conductive

- dielectric

- opening

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

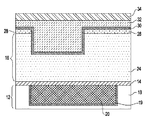

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

- H01L21/76808—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures involving intermediate temporary filling with material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76805—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics the opening being a via or contact hole penetrating the underlying conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76843—Barrier, adhesion or liner layers formed in openings in a dielectric

- H01L21/76844—Bottomless liners

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76843—Barrier, adhesion or liner layers formed in openings in a dielectric

- H01L21/76846—Layer combinations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53214—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being aluminium

- H01L23/53223—Additional layers associated with aluminium layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53257—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being a refractory metal

- H01L23/53266—Additional layers associated with refractory-metal layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/494,564 US7964966B2 (en) | 2009-06-30 | 2009-06-30 | Via gouged interconnect structure and method of fabricating same |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011014904A true JP2011014904A (ja) | 2011-01-20 |

| JP2011014904A5 JP2011014904A5 (enExample) | 2013-10-03 |

Family

ID=43379790

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010142938A Pending JP2011014904A (ja) | 2009-06-30 | 2010-06-23 | ビアがガウジングされた相互接続構造体及びその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7964966B2 (enExample) |

| JP (1) | JP2011014904A (enExample) |

| KR (1) | KR20110001894A (enExample) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20110003191A (ko) * | 2009-07-03 | 2011-01-11 | 삼성전자주식회사 | 소자 분리막 및 반도체 소자의 형성 방법 |

| US9177917B2 (en) * | 2010-08-20 | 2015-11-03 | Micron Technology, Inc. | Semiconductor constructions |

| US9054110B2 (en) * | 2011-08-05 | 2015-06-09 | Taiwan Semiconductor Manufacturing Company, Ltd. | Low-K dielectric layer and porogen |

| US8835305B2 (en) | 2012-07-31 | 2014-09-16 | International Business Machines Corporation | Method of fabricating a profile control in interconnect structures |

| US8749060B2 (en) * | 2012-09-21 | 2014-06-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of semiconductor integrated circuit fabrication |

| US9030013B2 (en) * | 2012-09-21 | 2015-05-12 | Taiwan Semiconductor Manufacturing Company, Ltd. | Interconnect structures comprising flexible buffer layers |

| US10043706B2 (en) | 2013-01-18 | 2018-08-07 | Taiwan Semiconductor Manufacturing Company Limited | Mitigating pattern collapse |

| US10032712B2 (en) | 2013-03-15 | 2018-07-24 | Taiwan Semiconductor Manufacturing Company Limited | Semiconductor structure |

| CN104078445A (zh) * | 2013-03-29 | 2014-10-01 | 联华电子股份有限公司 | 插塞结构及其制作工艺 |

| US9349691B2 (en) | 2014-07-24 | 2016-05-24 | International Business Machines Corporation | Semiconductor device with reduced via resistance |

| US9991200B2 (en) | 2014-09-25 | 2018-06-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | Air gap structure and method |

| US9685370B2 (en) | 2014-12-18 | 2017-06-20 | Globalfoundries Inc. | Titanium tungsten liner used with copper interconnects |

| US10211148B2 (en) * | 2015-12-14 | 2019-02-19 | International Business Machines Corporation | Structural enhancement of Cu nanowires |

| US9935051B2 (en) | 2016-08-18 | 2018-04-03 | International Business Machines Corporation | Multi-level metallization interconnect structure |

| JP2018107227A (ja) * | 2016-12-26 | 2018-07-05 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置、半導体装置の製造方法、及び、固体撮像素子 |

| CN110024103B (zh) * | 2016-12-29 | 2023-06-30 | 英特尔公司 | 自对准通孔 |

| US11018054B2 (en) | 2017-04-12 | 2021-05-25 | Intel Corporation | Integrated circuit interconnects |

| KR102438179B1 (ko) * | 2017-11-02 | 2022-08-30 | 삼성전자주식회사 | 반도체 장치 및 이를 포함하는 반도체 패키지, 및 상기 반도체 장치의 제조 방법 |

| US20200111741A1 (en) * | 2018-10-09 | 2020-04-09 | International Business Machines Corporation | Vertical electrical fuse |

| US11177169B2 (en) * | 2019-06-21 | 2021-11-16 | International Business Machines Corporation | Interconnects with gouged vias |

| CN119364753A (zh) * | 2023-07-12 | 2025-01-24 | 长鑫科技集团股份有限公司 | 半导体结构及其制备方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2008036115A1 (en) * | 2006-03-01 | 2008-03-27 | International Business Machines Corporation | Novel structure and method for metal integration |

| US20080128907A1 (en) * | 2006-12-01 | 2008-06-05 | International Business Machines Corporation | Semiconductor structure with liner |

| JP2008543078A (ja) * | 2005-05-31 | 2008-11-27 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド | 補強層を設けることによって低k誘電体内に埋め込まれる銅含有線を形成するための技術 |

| JP2009027048A (ja) * | 2007-07-23 | 2009-02-05 | Panasonic Corp | 半導体装置の製造方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5162869B2 (ja) * | 2006-09-20 | 2013-03-13 | 富士通セミコンダクター株式会社 | 半導体装置およびその製造方法 |

| US7846834B2 (en) * | 2008-02-04 | 2010-12-07 | International Business Machines Corporation | Interconnect structure and method for Cu/ultra low k integration |

| US7834457B2 (en) * | 2008-02-28 | 2010-11-16 | International Business Machines Corporation | Bilayer metal capping layer for interconnect applications |

-

2009

- 2009-06-30 US US12/494,564 patent/US7964966B2/en active Active

-

2010

- 2010-06-18 KR KR1020100057973A patent/KR20110001894A/ko not_active Withdrawn

- 2010-06-23 JP JP2010142938A patent/JP2011014904A/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008543078A (ja) * | 2005-05-31 | 2008-11-27 | アドバンスト・マイクロ・ディバイシズ・インコーポレイテッド | 補強層を設けることによって低k誘電体内に埋め込まれる銅含有線を形成するための技術 |

| WO2008036115A1 (en) * | 2006-03-01 | 2008-03-27 | International Business Machines Corporation | Novel structure and method for metal integration |

| JP2009528702A (ja) * | 2006-03-01 | 2009-08-06 | インターナショナル・ビジネス・マシーンズ・コーポレーション | 金属統合のための新規な構造体及び方法 |

| US20080128907A1 (en) * | 2006-12-01 | 2008-06-05 | International Business Machines Corporation | Semiconductor structure with liner |

| JP2009027048A (ja) * | 2007-07-23 | 2009-02-05 | Panasonic Corp | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7964966B2 (en) | 2011-06-21 |

| US20100327446A1 (en) | 2010-12-30 |

| KR20110001894A (ko) | 2011-01-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5430946B2 (ja) | 相互接続構造体形成方法 | |

| US7964966B2 (en) | Via gouged interconnect structure and method of fabricating same | |

| US8354751B2 (en) | Interconnect structure for electromigration enhancement | |

| US7867895B2 (en) | Method of fabricating improved interconnect structure with a via gouging feature absent profile damage to the interconnect dielectric | |

| JP5462807B2 (ja) | 高い漏れ抵抗を有する相互接続構造体 | |

| US7834457B2 (en) | Bilayer metal capping layer for interconnect applications | |

| JP5255292B2 (ja) | 2層金属キャップを有する相互接続構造体及びその製造方法 | |

| JP5419328B2 (ja) | 障壁冗長構成要素を有する相互接続構造体および相互接続構造体を形成する方法 | |

| US8232196B2 (en) | Interconnect structure having a via with a via gouging feature and dielectric liner sidewalls for BEOL integration | |

| JP5089575B2 (ja) | 相互接続構造体及びその製造方法 | |

| US7846834B2 (en) | Interconnect structure and method for Cu/ultra low k integration | |

| US20080128907A1 (en) | Semiconductor structure with liner | |

| KR20100098673A (ko) | 상호접속 구조에 대한 귀금속 캡 | |

| JP5385610B2 (ja) | 相互接続構造体の形成方法 | |

| KR100632038B1 (ko) | 다층 금속 배선의 제조 방법 | |

| JP2005129746A (ja) | 半導体装置の製造方法および半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130301 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20130801 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130805 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20130805 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20130801 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20130924 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131022 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20140120 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20140123 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20140216 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140507 |