JP2010098243A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2010098243A JP2010098243A JP2008269901A JP2008269901A JP2010098243A JP 2010098243 A JP2010098243 A JP 2010098243A JP 2008269901 A JP2008269901 A JP 2008269901A JP 2008269901 A JP2008269901 A JP 2008269901A JP 2010098243 A JP2010098243 A JP 2010098243A

- Authority

- JP

- Japan

- Prior art keywords

- comb

- electrode

- electrodes

- semiconductor device

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims description 63

- 230000005669 field effect Effects 0.000 claims abstract description 20

- 230000005540 biological transmission Effects 0.000 claims description 72

- 239000000758 substrate Substances 0.000 claims description 36

- 150000001875 compounds Chemical class 0.000 claims description 4

- 244000126211 Hericium coralloides Species 0.000 claims 3

- 230000007423 decrease Effects 0.000 claims 2

- 230000036961 partial effect Effects 0.000 abstract description 91

- 238000000034 method Methods 0.000 abstract description 8

- 230000004888 barrier function Effects 0.000 description 48

- 239000010410 layer Substances 0.000 description 41

- 102100032533 ADP/ATP translocase 1 Human genes 0.000 description 32

- 101000768061 Escherichia phage P1 Antirepressor protein 1 Proteins 0.000 description 32

- 101000796932 Homo sapiens ADP/ATP translocase 1 Proteins 0.000 description 32

- 230000002829 reductive effect Effects 0.000 description 29

- 239000003990 capacitor Substances 0.000 description 24

- 230000003321 amplification Effects 0.000 description 20

- 238000003199 nucleic acid amplification method Methods 0.000 description 20

- 238000001514 detection method Methods 0.000 description 17

- 238000010586 diagram Methods 0.000 description 17

- 230000006870 function Effects 0.000 description 17

- 101100381996 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) BRO1 gene Proteins 0.000 description 12

- 229910000980 Aluminium gallium arsenide Inorganic materials 0.000 description 10

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 9

- 230000009467 reduction Effects 0.000 description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 239000012535 impurity Substances 0.000 description 5

- 238000012545 processing Methods 0.000 description 5

- 238000010897 surface acoustic wave method Methods 0.000 description 5

- 238000004891 communication Methods 0.000 description 4

- 230000009977 dual effect Effects 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 238000002955 isolation Methods 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 238000004088 simulation Methods 0.000 description 4

- 230000005236 sound signal Effects 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000010295 mobile communication Methods 0.000 description 3

- 229910052697 platinum Inorganic materials 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 230000002238 attenuated effect Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 230000005533 two-dimensional electron gas Effects 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/40—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels

- H10D30/47—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels having 2D charge carrier gas channels, e.g. nanoribbon FETs or high electron mobility transistors [HEMT]

- H10D30/471—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT]

- H10D30/473—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT] having confinement of carriers by multiple heterojunctions, e.g. quantum well HEMT

- H10D30/4732—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT] having confinement of carriers by multiple heterojunctions, e.g. quantum well HEMT using Group III-V semiconductor material

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B1/00—Details of transmission systems, not covered by a single one of groups H04B3/00 - H04B13/00; Details of transmission systems not characterised by the medium used for transmission

- H04B1/38—Transceivers, i.e. devices in which transmitter and receiver form a structural unit and in which at least one part is used for functions of transmitting and receiving

- H04B1/40—Circuits

- H04B1/44—Transmit/receive switching

- H04B1/48—Transmit/receive switching in circuits for connecting transmitter and receiver to a common transmission path, e.g. by energy of transmitter

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/257—Source or drain electrodes for field-effect devices for lateral devices wherein the source or drain electrodes are characterised by top-view geometrical layouts, e.g. interdigitated, semi-circular, annular or L-shaped electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/517—Gate electrodes for field-effect devices for FETs for IGFETs characterised by the conducting layers

- H10D64/519—Gate electrodes for field-effect devices for FETs for IGFETs characterised by the conducting layers characterised by their top-view geometrical layouts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/10—Integrated device layouts

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B7/00—Radio transmission systems, i.e. using radiation field

- H04B7/02—Diversity systems; Multi-antenna system, i.e. transmission or reception using multiple antennas

- H04B7/04—Diversity systems; Multi-antenna system, i.e. transmission or reception using multiple antennas using two or more spaced independent antennas

- H04B7/08—Diversity systems; Multi-antenna system, i.e. transmission or reception using multiple antennas using two or more spaced independent antennas at the receiving station

- H04B7/0802—Diversity systems; Multi-antenna system, i.e. transmission or reception using multiple antennas using two or more spaced independent antennas at the receiving station using antenna selection

- H04B7/0831—Compensation of the diversity switching process for non-uniform properties or faulty operations of the switches used in the diversity switching process

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/601—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Transceivers (AREA)

- Junction Field-Effect Transistors (AREA)

Abstract

【解決手段】メアンダ構造をしているトランジスタQ1において、ゲート入力側に最も近い部分トランジスタのゲート幅を大きくする。具体的には、図5に示すように、櫛歯状電極CL(1)をその他の櫛歯状電極CL(2)〜CL(n)よりも長くするように構成している。言い換えれば、フィンガー長Lw1をその他のフィンガー長Lwjよりも長くしている。特に、櫛歯状電極CL(1)を櫛歯状電極CL(1)〜CL(n)の中で最も長くする。

【選択図】図5

Description

<携帯電話機の構成および動作>

図1は、携帯電話機の送受信部の構成を示すブロック図である。図1に示すように、携帯電話機1は、アプリケーションプロセッサ2、メモリ3、ベースバンド部4、RFIC5、電力増幅器6、SAW(Surface Acoustic Wave)フィルタ7、アンテナスイッチ8およびアンテナ9を有している。

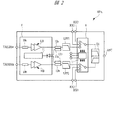

上述したように、デジタル携帯電話機から信号を送信する際、電力増幅器6によって信号は増幅された後、アンテナスイッチ8を介してアンテナ9から出力される。この電力増幅器6とアンテナスイッチ8とは例えば、1つのRFモジュールHPAとして製品化されている。以下では、このRFモジュールHPAの回路ブロック構成について説明する。図2は、本実施の形態1におけるRFモジュールHPAの回路ブロック構成を示す図である。図2において、本実施の形態1におけるRFモジュールHPAは、電力増幅器6、出力整合回路12a、12b、検波回路13a、13b、ローパスフィルタLPF1、LPF2、アンテナスイッチ8およびダイプレクサDiを有している。

本実施の形態1におけるRFモジュールHPAは上記のように構成されており、以下に、その動作について説明する。図2に示すように、本実施の形態1では、GSM低周波帯域の信号およびGSM高周波帯域の信号を増幅することができるように構成されているが、動作は同様なので、GSM低周波帯域の信号を増幅する動作について説明する。なお、通信方式は、GSM方式について説明しているが、その他の通信方式であってもよい。

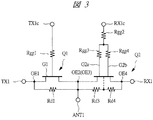

本実施の形態1は、RFモジュールHPAに搭載されるアンテナスイッチに着目している。以下では、このアンテナスイッチの回路構成について説明する。図3は、アンテナスイッチを構成する回路の一例を示す図である。図3に示すように、アンテナスイッチには、送信端子TX1、アンテナ端子ANT1および受信端子RX1を有している。送信端子TX1は電力増幅器の出力に接続されており、アンテナ端子ANT1はアンテナに接続されている。そして、受信端子RX1は受信回路の入力に接続されている。

アンテナスイッチを構成するトランジスタQ1やトランジスタQ2は、例えば、電界効果トランジスタの一種であるHEMT(High Electron Mobility Transistor)から構成される。このHEMTのデバイス構造について説明する。

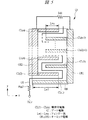

続いて、本実施の形態1の特徴点を含むトランジスタQ1のレイアウト構成について説明する。図5は、本実施の形態1におけるトランジスタQ1のレイアウト構成を示す図である。図5において、y軸方向に延在するようにオーミック電極OE1とオーミック電極OE2が形成されている。すなわち、オーミック電極OE1とオーミック電極OE2とは、一定距離だけ離間し、かつ、それぞれがy軸方向に延在するように配置されている。そして、オーミック電極OE1のオーミック電極OE2と対向する面に複数の櫛歯状電極CL(1)、CL(3)・・・CL(2j+1)が形成されている。この複数の櫛歯状電極CL(1)、CL(3)・・・CL(2j+1)は、x軸方向に突き出るように配置されている。同様に、オーミック電極OE2のオーミック電極OE1と対向する面にも複数の櫛歯状電極CL(2)、CL(4)・・・CL(n)が形成されている。この複数の櫛歯状電極CL(2)、CL(4)・・・CL(n)もx軸方向に突き出るように配置されている。この櫛歯状電極CL(1)、CL(3)・・・CL(2j+1)および櫛歯状電極CL(2)、CL(4)・・・CL(n)は、メサ領域MRに形成されている。

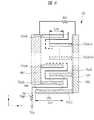

図6は、本実施の形態1におけるメアンダ構造を示す平面図である。図6に示すように、アンテナスイッチを構成するトランジスタQ1はメアンダ構造をしている。この図6に示すメアンダ構造によって1つのトランジスタQ1が構成されているが、1つのトランジスタQ1は、複数の部分トランジスタCF1、CF2・・・CFjから構成されているとみなすことができる。具体的には、図6から、メアンダ構造をした1つのトランジスタQ1は、部分トランジスタCF1、CF2・・・CFjを並列に接続した構造をしているということができる。例えば、部分トランジスタCF1は、櫛歯状電極CL(1)と櫛歯状電極CL(2)を一対のオーミック電極とし、その間に配置されているゲート電極G1からなるトランジスタとみなすことができる。詳細には、部分トランジスタCF1は、フィンガー長Lw1に対応したトランジスタである。同様に、部分トランジスタCF2は、櫛歯状電極CL(2)と櫛歯状電極CL(3)を一対のオーミック電極とし、その間に配置されているゲート電極G1からなるトランジスタとみなすことができる。詳細には、部分トランジスタCF2は、フィンガー長Lw2(図示せず)に対応したトランジスタである。

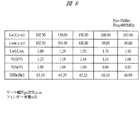

次に、本実施の形態1によれば、高次高調波を低減できることを定量的に説明する。本実施の形態1では、図7に示す等価回路図を用いてシミュレーションを行い、送信時にオンしているトランジスタQ1から発生する高次高調波を算出した。シミュレーションの条件としては、入力信号の電力Pinを35dBm、入力信号の周波数を880MHzとしている。このとき、メアンダ構造をしているトランジスタQ1のゲート幅Wgを2050μmとし、フィンガー本数を20本に固定して評価している。

前記実施の形態1では、シングルゲート構造のトランジスタに本発明を適用する例を説明したが、本実施の形態2では、デュアルゲート構造のトランジスタに本発明を適用する例について説明する。

本実施の形態3では、メアンダ構造を有するトランジスタにおいて、櫛歯状電極の長さ(フィンガー長)がゲート電極に制御信号を入力する入力側から遠くなるにつれて短くなる例について説明する。

前記実施の形態1では、アンテナスイッチを構成するトランジスタとして高電子移動度トランジスタ(HEMT)を使用する例について説明したが、本実施の形態4では、アンテナスイッチを構成するトランジスタとしてMOSFET(Metal Oxide Semiconductor Field Effect Transistor)を使用する例について説明する。

2 アプリケーションプロセッサ

3 メモリ

4 ベースバンド部

5 RFIC

6 電力増幅器

7 SAWフィルタ

8 アンテナスイッチ

9 アンテナ

10a 整合回路

10b 整合回路

11 制御回路

12a 出力整合回路

12b 出力整合回路

13a 検波回路

13b 検波回路

14 デコーダ

20 半絶縁性基板

21 エピタキシャル層

22 バッファ層

23 AlGaAs層

24 n型GaAs層

30 半導体基板

31 埋め込み絶縁層

32 シリコン層

ANT アンテナ

ANT1 アンテナ端子

C1a 容量

C1b 容量

C2a 容量

C2b 容量

CF1 部分トランジスタ

CF2 部分トランジスタ

CL(1) 櫛歯状電極

CL(2) 櫛歯状電極

CL(3) 櫛歯状電極

CL(4) 櫛歯状電極

CL(2j+1) 櫛歯状電極

CL(n−1) 櫛歯状電極

CL(n)櫛歯状電極

D1 ドレイン領域

D1a ショットキーバリアダイオード

D1b ショットキーバリアダイオード

D2a ショットキーバリアダイオード

D2b ショットキーバリアダイオード

Di ダイプレクサ

EX エクステンション領域

G ゲート電極

G1 ゲート電極

G1a ゲート電極

G1b ゲート電極

G2a ゲート電極

G2b ゲート電極

GOX ゲート絶縁膜

HB 増幅回路

HPA RFモジュール

IL 層間絶縁膜

L1 配線

LB 増幅回路

LPF1 ローパスフィルタ

LPF2 ローパスフィルタ

LW1 フィンガー長

LWn フィンガー長

MR メサ領域

OE1 オーミック電極

OE2 オーミック電極

OE3 オーミック電極

OE4 オーミック電極

PLG プラグ

Q1 トランジスタ

Q2 トランジスタ

Qc トランジスタ

Qr1 トランジスタ

Qr2 トランジスタ

Rd1 抵抗

Rd2 抵抗

Rd3 抵抗

Rd4 抵抗

Rgg1 ゲート抵抗

Rgg2 ゲート抵抗

Rgg3 ゲート抵抗

Rgg4 ゲート抵抗

Rgg12 ゲート抵抗

Ron1 オン抵抗

Ron2 オン抵抗

RX1 受信端子

RX1c ゲート端子

RX2 受信端子

RX2c ゲート端子

RX3 受信端子

RX4 受信端子

RXc ゲート端子

S1 ソース領域

STI 素子分離領域

SW サイドウォール

TX1 送信端子

TX1c ゲート端子

TX(HB)in 入力端子

TX(LB)in 入力端子

Vct 直流電源

Vin 高周波電圧

Vrf1 RF電圧

Vrf2 RF電圧

Vrfg1 RF電圧

Claims (18)

- 半導体基板上に形成された電界効果トランジスタを備え、

前記電界効果トランジスタは、

(a)前記半導体基板の第1方向に延在し、互いに対向するように配置された第1オーミック電極および第2オーミック電極と、

(b)前記第1オーミック電極の前記第2オーミック電極と対向する対向面から前記第1方向と交差する第2方向に突き出た複数の第1櫛歯状電極と、

(c)前記第2オーミック電極の前記第1オーミック電極と対向する対向面から前記第1方向と交差する前記第2方向に突き出た複数の第2櫛歯状電極と、

(d)前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極とを交互に櫛歯状に配置することにより、前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極の間に形成される隙間に沿って延在するゲート電極とを有する半導体装置であって、

前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極を含む櫛歯状電極のうち、前記ゲート電極に制御信号を入力する入力側に最も近い櫛歯状電極の長さを、その他の櫛歯状電極の長さよりも長くすることを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極の間に形成される隙間に沿って、互いに並行する複数のゲート電極が延在していることを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記ゲート電極に制御信号を入力する入力側に最も近い櫛歯状電極の長さが、櫛歯状電極の中で最も長さが長いことを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記複数の第1櫛歯状電極の長さがそれぞれ異なり、かつ、前記複数の第2櫛歯状電極の長さもそれぞれ異なることを特徴とする半導体装置。 - 請求項4記載の半導体装置であって、

前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極を含む櫛歯状電極の長さが、前記ゲート電極に制御信号を入力する入力側から遠くなるにつれて、短くなることを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記電界効果トランジスタは、高電子移動度トランジスタであることを特徴とする半導体装置。 - 請求項6記載の半導体装置であって、

前記ゲート電極と前記半導体基板の間には半導体層が形成されており、

前記ゲート電極と前記半導体層の境界にはショットキー接合が形成されていることを特徴とする半導体装置。 - 請求項7記載の半導体装置であって、

前記半導体基板は化合物半導体から形成されていることを特徴とする半導体装置。 - 請求項1記載の半導体装置であって、

前記ゲート電極と前記半導体基板の間にゲート絶縁膜が形成されていることを特徴とする半導体装置。 - 請求項9記載の半導体装置であって、

前記半導体基板はSOI基板、もしくは、SOS基板であることを特徴とする半導体装置。 - 送信信号の送信と受信信号の受信を切り替えるアンテナスイッチを半導体基板上に備え、

前記アンテナスイッチは、

(a)前記送信信号を入力する第1端子と、

(b)アンテナに接続された第2端子と、

(c)前記受信信号を出力する第3端子と、

(d)前記第1端子と前記第2端子との間に接続された第1スイッチング素子と、

(e)前記第2端子と前記第3端子との間に接続された第2スイッチング素子とを有し、

前記送信信号の送信時に、前記第1スイッチング素子は導通状態となり、かつ、前記第2スイッチング素子は非導通状態となる一方、前記受信信号の受信時に、前記第1スイッチング素子は非導通となり、かつ、前記第2スイッチング素子は導通状態となる半導体装置であって、

前記第1スイッチング素子は電界効果トランジスタから構成され、

前記電界効果トランジスタは、

(f1)前記半導体基板の第1方向に延在し、互いに対向するように配置された第1オーミック電極および第2オーミック電極と、

(f2)前記第1オーミック電極の前記第2オーミック電極と対向する対向面から前記第1方向と交差する第2方向に突き出た複数の第1櫛歯状電極と、

(f3)前記第2オーミック電極の前記第1オーミック電極と対向する対向面から前記第1方向と交差する前記第2方向に突き出た複数の第2櫛歯状電極と、

(f4)前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極とを交互に櫛歯状に配置することにより、前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極の間に形成される隙間に沿って延在するゲート電極とを有し、

前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極を含む櫛歯状電極のうち、前記ゲート電極に制御信号を入力する入力側に最も近い櫛歯状電極の長さを、その他の櫛歯状電極の長さよりも長くすることを特徴とする半導体装置。 - 請求項11記載の半導体装置であって、

前記第2スイッチング素子も前記第1スイッチング素子と同様の構成をしている前記電界効果トランジスタから構成されていることを特徴とする半導体装置。 - 請求項11記載の半導体装置であって、

前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極の間に形成される隙間に沿って、互いに並行する複数のゲート電極が延在していることを特徴とする半導体装置。 - 請求項11記載の半導体装置であって、

前記ゲート電極に制御信号を入力する入力側に最も近い櫛歯状電極の長さが、櫛歯状電極の中で最も長さが長いことを特徴とする半導体装置。 - 請求項11記載の半導体装置であって、

前記複数の第1櫛歯状電極の長さがそれぞれ異なり、かつ、前記複数の第2櫛歯状電極の長さもそれぞれ異なることを特徴とする半導体装置。 - 請求項15記載の半導体装置であって、

前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極を含む櫛歯状電極の長さが、前記ゲート電極に制御信号を入力する入力側から遠くなるにつれて、短くなることを特徴とする半導体装置。 - (a)送信信号を増幅する第1増幅器と、

(b)前記送信信号の送信時に、前記第1増幅器で増幅された前記送信信号をアンテナから送信されるようにスイッチング動作し、受信信号の受信時に、前記アンテナで受信した受信信号を受信回路へ出力するようにスイッチング動作するアンテナスイッチを備え、

前記アンテナスイッチは、

(b1)前記送信信号を入力する第1端子と、

(b2)アンテナに接続された第2端子と、

(b3)前記受信信号を出力する第3端子と、

(b4)前記第1端子と前記第2端子との間に接続された第1スイッチング素子と、

(b5)前記第2端子と前記第3端子との間に接続された第2スイッチング素子とを有し、

前記送信信号の送信時に、前記第1スイッチング素子は導通状態となり、かつ、前記第2スイッチング素子は非導通状態となる一方、前記受信信号の受信時に、前記第1スイッチング素子は非導通となり、かつ、前記第2スイッチング素子は導通状態となる半導体装置であって、

前記第1スイッチング素子は電界効果トランジスタから構成され、

前記電界効果トランジスタは、

(c1)半導体基板の第1方向に延在し、互いに対向するように配置された第1オーミック電極および第2オーミック電極と、

(c2)前記第1オーミック電極の前記第2オーミック電極と対向する対向面から前記第1方向と交差する第2方向に突き出た複数の第1櫛歯状電極と、

(c3)前記第2オーミック電極の前記第1オーミック電極と対向する対向面から前記第1方向と交差する前記第2方向に突き出た複数の第2櫛歯状電極と、

(c4)前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極とを交互に櫛歯状に配置することにより、前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極の間に形成される隙間に沿って延在するゲート電極とを有し、

前記複数の第1櫛歯状電極と前記複数の第2櫛歯状電極を含む櫛歯状電極のうち、前記ゲート電極に制御信号を入力する入力側に最も近い櫛歯状電極の長さを、その他の櫛歯状電極の長さよりも長くすることを特徴とする半導体装置。 - 請求項17記載の半導体装置であって、

前記半導体装置は、携帯電話機のRFモジュールを構成していることを特徴とする半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008269901A JP5644042B2 (ja) | 2008-10-20 | 2008-10-20 | 半導体装置 |

| US12/564,939 US8115234B2 (en) | 2008-10-20 | 2009-09-23 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008269901A JP5644042B2 (ja) | 2008-10-20 | 2008-10-20 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010098243A true JP2010098243A (ja) | 2010-04-30 |

| JP5644042B2 JP5644042B2 (ja) | 2014-12-24 |

Family

ID=42107955

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008269901A Expired - Fee Related JP5644042B2 (ja) | 2008-10-20 | 2008-10-20 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8115234B2 (ja) |

| JP (1) | JP5644042B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012009615A (ja) * | 2010-06-24 | 2012-01-12 | Fujitsu Ltd | 化合物半導体装置及びその製造方法 |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20110100001A (ko) * | 2010-03-03 | 2011-09-09 | 삼성전기주식회사 | 개선된 고조파 특성을 갖는 고주파 송신 모듈 |

| JP5776143B2 (ja) * | 2010-07-06 | 2015-09-09 | サンケン電気株式会社 | 半導体装置 |

| US11043432B2 (en) * | 2013-11-12 | 2021-06-22 | Skyworks Solutions, Inc. | Radio-frequency switching devices having improved voltage handling capability |

| US11901243B2 (en) * | 2013-11-12 | 2024-02-13 | Skyworks Solutions, Inc. | Methods related to radio-frequency switching devices having improved voltage handling capability |

| DE112015002750T5 (de) | 2014-06-12 | 2017-04-27 | Skyworks Solutions Inc. | Vorrichtungen und Verfahren in Bezug auf Richtkoppler |

| EP3062349B1 (en) * | 2015-02-25 | 2019-10-09 | Nxp B.V. | Semiconductor device comprising a switch |

| US9780090B2 (en) * | 2015-10-19 | 2017-10-03 | Nxp Usa, Inc. | Integrated circuits and devices with interleaved transistor elements, and methods of their fabrication |

| US9953938B2 (en) * | 2016-03-30 | 2018-04-24 | Skyworks Solutions, Inc. | Tunable active silicon for coupler linearity improvement and reconfiguration |

| US10084224B2 (en) * | 2016-04-29 | 2018-09-25 | Skyworks Solutions, Inc. | Compensated electromagnetic coupler |

| WO2017189825A1 (en) * | 2016-04-29 | 2017-11-02 | Skyworks Solutions, Inc. | Tunable electromagnetic coupler and modules and devices using same |

| WO2017196652A2 (en) | 2016-05-09 | 2017-11-16 | Skyworks Solutions, Inc. | Self-adjusting electromagnetic coupler with automatic frequency detection |

| US10164681B2 (en) | 2016-06-06 | 2018-12-25 | Skyworks Solutions, Inc. | Isolating noise sources and coupling fields in RF chips |

| US10403955B2 (en) | 2016-06-22 | 2019-09-03 | Skyworks Solutions, Inc. | Electromagnetic coupler arrangements for multi-frequency power detection, and devices including same |

| US10742189B2 (en) | 2017-06-06 | 2020-08-11 | Skyworks Solutions, Inc. | Switched multi-coupler apparatus and modules and devices using same |

| US10483392B2 (en) * | 2017-12-15 | 2019-11-19 | Qualcomm Incorporated | Capacitive tuning using backside gate |

| JP2022128597A (ja) | 2021-02-23 | 2022-09-02 | スカイワークス ソリューションズ,インコーポレイテッド | スイッチング可能インダクタを備えたスマート双方向性結合器 |

| US12057611B2 (en) | 2021-06-02 | 2024-08-06 | Skyworks Solutions, Inc. | Directional coupler with multiple arrangements of termination |

| US12113114B2 (en) * | 2021-10-22 | 2024-10-08 | Wolfspeed, Inc. | Transistor with ohmic contacts |

| TWI802086B (zh) * | 2021-11-17 | 2023-05-11 | 啟碁科技股份有限公司 | 通訊裝置與射頻構件 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6135714B2 (ja) * | 1979-02-09 | 1986-08-14 | Fujitsu Ltd | |

| JPH0729918A (ja) * | 1993-07-08 | 1995-01-31 | Sumitomo Electric Ind Ltd | 高周波電界効果トランジスタ |

| JPH11163205A (ja) * | 1997-12-01 | 1999-06-18 | Nec Corp | 半導体装置 |

| JP2002164441A (ja) * | 2000-11-27 | 2002-06-07 | Matsushita Electric Ind Co Ltd | 高周波スイッチ回路装置 |

| JP2003258001A (ja) * | 2002-03-05 | 2003-09-12 | Murata Mfg Co Ltd | 高周波半導体装置 |

| JP2005159157A (ja) * | 2003-11-27 | 2005-06-16 | Renesas Technology Corp | 半導体装置 |

| JP2006165224A (ja) * | 2004-12-07 | 2006-06-22 | Renesas Technology Corp | スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003168736A (ja) * | 2001-11-30 | 2003-06-13 | Hitachi Ltd | 半導体素子及び高周波電力増幅装置並びに無線通信機 |

-

2008

- 2008-10-20 JP JP2008269901A patent/JP5644042B2/ja not_active Expired - Fee Related

-

2009

- 2009-09-23 US US12/564,939 patent/US8115234B2/en active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6135714B2 (ja) * | 1979-02-09 | 1986-08-14 | Fujitsu Ltd | |

| JPH0729918A (ja) * | 1993-07-08 | 1995-01-31 | Sumitomo Electric Ind Ltd | 高周波電界効果トランジスタ |

| JPH11163205A (ja) * | 1997-12-01 | 1999-06-18 | Nec Corp | 半導体装置 |

| JP2002164441A (ja) * | 2000-11-27 | 2002-06-07 | Matsushita Electric Ind Co Ltd | 高周波スイッチ回路装置 |

| JP2003258001A (ja) * | 2002-03-05 | 2003-09-12 | Murata Mfg Co Ltd | 高周波半導体装置 |

| JP2005159157A (ja) * | 2003-11-27 | 2005-06-16 | Renesas Technology Corp | 半導体装置 |

| JP2006165224A (ja) * | 2004-12-07 | 2006-06-22 | Renesas Technology Corp | スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012009615A (ja) * | 2010-06-24 | 2012-01-12 | Fujitsu Ltd | 化合物半導体装置及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5644042B2 (ja) | 2014-12-24 |

| US20100096667A1 (en) | 2010-04-22 |

| US8115234B2 (en) | 2012-02-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5644042B2 (ja) | 半導体装置 | |

| JP5706103B2 (ja) | 半導体装置 | |

| US10298222B2 (en) | High performance radio frequency switch | |

| CN101252352B (zh) | 半导体集成电路器件及高频功率放大器模块 | |

| JP5632663B2 (ja) | 半導体装置 | |

| JP5237842B2 (ja) | 半導体装置 | |

| JP4272142B2 (ja) | スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール | |

| JP5375307B2 (ja) | 半導体装置 | |

| US8509682B2 (en) | Compact switch with enhanced linearity performance | |

| WO2023286798A1 (ja) | 電力増幅回路及び電力増幅方法 | |

| US20230246639A1 (en) | Switching time reduction of an rf switch | |

| JP2013526214A (ja) | Rf(無線周波数)スイッチ | |

| KR101309445B1 (ko) | 고주파 스위치 | |

| JP2011258642A (ja) | 半導体装置およびその製造方法 | |

| JP2008021949A (ja) | 半導体素子及びこれを備える通信機器 | |

| JP5494890B2 (ja) | 半導体集積回路装置および高周波モジュール | |

| WO2015159668A1 (ja) | 半導体装置、アンテナスイッチ回路、および無線通信装置 | |

| JP5052215B2 (ja) | 半導体スイッチ回路 | |

| JP2009141379A (ja) | スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール | |

| JP2009081474A (ja) | スイッチング素子並びにそれを用いたアンテナスイッチ回路及び高周波モジュール | |

| JP2005328328A (ja) | 可変利得増幅器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110916 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20120323 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130731 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130806 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131003 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140128 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140319 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140805 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141007 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141020 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5644042 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |