JP2010074247A - 発振回路、dc−dcコンバータ及び半導体装置 - Google Patents

発振回路、dc−dcコンバータ及び半導体装置 Download PDFInfo

- Publication number

- JP2010074247A JP2010074247A JP2008236402A JP2008236402A JP2010074247A JP 2010074247 A JP2010074247 A JP 2010074247A JP 2008236402 A JP2008236402 A JP 2008236402A JP 2008236402 A JP2008236402 A JP 2008236402A JP 2010074247 A JP2010074247 A JP 2010074247A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- clock signal

- signal

- frequency

- delay

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/089—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal the phase or frequency detector generating up-down pulses

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/44—Circuits or arrangements for compensating for electromagnetic interference in converters or inverters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/081—Details of the phase-locked loop provided with an additional controlled phase shifter

- H03L7/0812—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used

- H03L7/0814—Details of the phase-locked loop provided with an additional controlled phase shifter and where no voltage or current controlled oscillator is used the phase shifting device being digitally controlled

Landscapes

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Manipulation Of Pulses (AREA)

- Dc-Dc Converters (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Abstract

【解決手段】周波数が下限周波数と上限周波数の間を連続的に変化しながら往復する発振回路において、アップダウン制御回路20は、第1の検出回路30がクロック信号のハイレベル又はローレベルの時間が第1の遅延時間以下になったことを検出した場合は、ダウン信号を可変周波数発振回路に出力し、第2の検出回路40がクロック信号のハイレベル又はローレベルの時間が第2の遅延時間以上になったことを検出した場合は、アップ信号を可変周波数発振回路10に出力する。

【選択図】図1

Description

20…アップダウン制御回路、

30…第1の検出回路、

40…第2の検出回路、

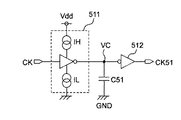

50…第1の遅延回路、

60…第2の遅延回路、

51〜63…遅延回路、

511…定電流インバータ回路、

512…インバータ回路、

C51…コンデンサ。

Claims (11)

- 周波数が下限周波数と上限周波数の間を連続的に変化しながら往復する発振回路において、

アップ信号に応じて周波数が上昇し、ダウン信号に応じて周波数が低下する可変周波数発振回路と、

前記可変周波数発振回路から出力されるクロック信号を第1の遅延時間だけ遅延させた第1のクロック信号を出力する第1の遅延回路と、

前記クロック信号を前記第1の遅延時間より長い第2の遅延時間だけ遅延させた第2のクロック信号を出力する第2の遅延回路と、

前記クロック信号と、前記第1のクロック信号とを比較し、前記クロック信号のハイレベル又はローレベルの時間が前記第1の遅延時間以下になったことを検出する第1の検出回路と、

前記クロック信号と、前記第2のクロック信号とを比較し、前記クロック信号のハイレベル又はローレベルの時間が前記第2の遅延時間以上になったことを検出する第2の検出回路と、

前記第1の検出回路と前記第2の検出回路の出力信号を入力し、前記アップ信号と前記ダウン信号を出力するアップダウン制御回路を備え、

前記アップダウン制御回路は、前記第1の検出回路が前記クロック信号のハイレベル又はローレベルの時間が前記第1の遅延時間以下になったことを検出した場合は、前記ダウン信号を前記可変周波数発振回路に出力し、

前記第2の検出回路が前記クロック信号のハイレベル又はローレベルの時間が前記第2の遅延時間以上になったことを検出した場合は、前記アップ信号を前記可変周波数発振回路に出力するように構成したことを特徴とする発振回路。 - 前記第1及び第2の遅延時間が、前記クロック信号のハイレベル又はローレベルのうちの短い方の時間の1/2より長い場合は、前記クロック信号のハイレベル又はローレベルのうちの短い方の時間の1/2より短い遅延時間の遅延回路を複数直列接続して構成したことを特徴とする請求項1記載の発振回路。

- 前記遅延回路は、コンデンサの充放電時間を用いた遅延回路で構成したことを特徴とする請求項2記載の発振回路。

- 前記第2の遅延回路の一部に前記第1の遅延回路の一部もしくは全部を用いたことを特徴とする請求項1乃至3のうちのいずれか1つに記載の発振回路。

- 前記第1の検出回路はDタイプフリップフロップ回路で構成し、前記Dタイプフリップフロップ回路のデータ端子に前記第1のクロック信号を入力し、クロック端子に前記クロック信号を入力し、前記第1の検出回路の出力信号を前記Dタイプフリップフロップ回路の出力端子から出力するように構成したことを特徴とする請求項1記載の発振回路。

- 前記第2の検出回路はDタイプフリップフロップ回路で構成し、前記Dタイプフリップフロップ回路のデータ端子に前記第2のクロック信号を反転した信号を入力し、クロック端子に前記クロック信号を入力し、前記第2の検出回路の出力信号を前記Dタイプフリップフロップ回路の出力端子から出力するように構成した請求項1記載の発振回路。

- 前記クロック信号のデューティ比を50%に設定したことを特徴とする請求項1乃至6のうちのいずれか1つに記載の発振回路。

- 前記第1の遅延時間を前記上限周波数の周期の1/2に設定し、前記第2の遅延時間を前記下限周波数の周期の1/2に設定したことを特徴とする請求項7記載の発振回路。

- 請求項1乃至8のうちのいずれか1つに記載の発振回路から出力される前記クロック信号をスイッチングトランジスタのオンオフ信号に用いてDC−DCコンバータを構成したことを特徴とするDC−DCコンバータ。

- 無線用送信回路、無線用受信回路、又は無線用送受信回路の電源に用いるように構成したことを特徴とする請求項9記載のDC−DCコンバータ。

- 請求項10記載のDC−DCコンバータと、前記無線用送信回路、前記無線用受信回路又は前記無線用送受信回路とを同一半導体装置に集積するように構成したことを特徴とする半導体装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008236402A JP4879240B2 (ja) | 2008-09-16 | 2008-09-16 | 発振回路、dc−dcコンバータ及び半導体装置 |

| US13/063,845 US8436685B2 (en) | 2008-09-16 | 2009-08-24 | Oscillating circuit, DC-DC converter, and semiconductor device |

| KR1020117006119A KR101196609B1 (ko) | 2008-09-16 | 2009-08-24 | 발진 회로, dc-dc 컨버터 및 반도체 장치 |

| EP20090814226 EP2329597B1 (en) | 2008-09-16 | 2009-08-24 | Oscillating circuit, dc-dc converter, and semiconductor device |

| PCT/JP2009/004071 WO2010032380A1 (en) | 2008-09-16 | 2009-08-24 | Oscillating circuit, dc-dc converter, and semiconductor device |

| CN200980136163XA CN102160291B (zh) | 2008-09-16 | 2009-08-24 | 振荡电路、dc-dc转换器和半导体器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008236402A JP4879240B2 (ja) | 2008-09-16 | 2008-09-16 | 発振回路、dc−dcコンバータ及び半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010074247A true JP2010074247A (ja) | 2010-04-02 |

| JP4879240B2 JP4879240B2 (ja) | 2012-02-22 |

Family

ID=42039232

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008236402A Expired - Fee Related JP4879240B2 (ja) | 2008-09-16 | 2008-09-16 | 発振回路、dc−dcコンバータ及び半導体装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8436685B2 (ja) |

| EP (1) | EP2329597B1 (ja) |

| JP (1) | JP4879240B2 (ja) |

| KR (1) | KR101196609B1 (ja) |

| CN (1) | CN102160291B (ja) |

| WO (1) | WO2010032380A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108141130A (zh) * | 2015-09-15 | 2018-06-08 | 日本电气株式会社 | 切换电源设备、切换电源的驱动方法和切换电源的驱动程序 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| AU2008299220B2 (en) | 2007-09-10 | 2011-07-21 | Calcimedica, Inc. | Compounds that modulate intracellular calcium |

| MX2011002149A (es) | 2008-08-27 | 2011-04-05 | Calcimedica Inc | Compuestos que modulan el calcio intracelular. |

| EP2477982A4 (en) | 2009-09-16 | 2013-04-03 | Calcimedica Inc | COMPOUNDS THAT MODULATE INTRACELLULAR CALCIUM |

| JP6186726B2 (ja) | 2013-01-07 | 2017-08-30 | 株式会社リコー | Pwm信号生成回路、プリンタ、及びpwm信号生成方法 |

| US11742862B2 (en) * | 2021-08-25 | 2023-08-29 | Nanya Technology Corporation | Delay locked loop device and method for operating the same |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002056678A (ja) * | 2000-08-14 | 2002-02-22 | Mitsubishi Electric Corp | 基板バイアス電圧発生回路 |

| JP2002158549A (ja) * | 2000-11-17 | 2002-05-31 | Sony Corp | デジタルパワーアンプ装置 |

| JP2002223564A (ja) * | 2001-01-25 | 2002-08-09 | Sharp Corp | 電圧変換回路及びこれを備えた半導体集積回路装置 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09266425A (ja) | 1996-03-28 | 1997-10-07 | Aiwa Co Ltd | 電子機器 |

| JPH09266426A (ja) | 1996-03-28 | 1997-10-07 | Aiwa Co Ltd | 電力増幅器 |

| JP3434734B2 (ja) | 1999-06-22 | 2003-08-11 | エヌイーシーマイクロシステム株式会社 | Pll回路 |

| US6674274B2 (en) * | 2001-02-08 | 2004-01-06 | Linear Technology Corporation | Multiple phase switching regulators with stage shedding |

| JP2004046911A (ja) | 2002-07-03 | 2004-02-12 | Ricoh Co Ltd | 光ディスク再生装置 |

| US6954112B2 (en) * | 2003-08-18 | 2005-10-11 | Semiconductor Components Industries, L.L.C. | Method of forming a variable frequency oscillator and structure therefor |

| JP4129010B2 (ja) * | 2005-07-12 | 2008-07-30 | 富士通株式会社 | 遅延回路 |

| JP4732887B2 (ja) | 2005-12-16 | 2011-07-27 | 株式会社リコー | 情報再生処理装置 |

| CN100553087C (zh) * | 2006-06-30 | 2009-10-21 | 美国凹凸微系有限公司 | 可变频率多相振荡器 |

| JP2007122871A (ja) | 2006-12-28 | 2007-05-17 | Ricoh Co Ltd | 光ディスク再生装置 |

-

2008

- 2008-09-16 JP JP2008236402A patent/JP4879240B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-24 US US13/063,845 patent/US8436685B2/en active Active

- 2009-08-24 CN CN200980136163XA patent/CN102160291B/zh not_active Expired - Fee Related

- 2009-08-24 EP EP20090814226 patent/EP2329597B1/en not_active Not-in-force

- 2009-08-24 KR KR1020117006119A patent/KR101196609B1/ko not_active IP Right Cessation

- 2009-08-24 WO PCT/JP2009/004071 patent/WO2010032380A1/en active Application Filing

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002056678A (ja) * | 2000-08-14 | 2002-02-22 | Mitsubishi Electric Corp | 基板バイアス電圧発生回路 |

| JP2002158549A (ja) * | 2000-11-17 | 2002-05-31 | Sony Corp | デジタルパワーアンプ装置 |

| JP2002223564A (ja) * | 2001-01-25 | 2002-08-09 | Sharp Corp | 電圧変換回路及びこれを備えた半導体集積回路装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108141130A (zh) * | 2015-09-15 | 2018-06-08 | 日本电气株式会社 | 切换电源设备、切换电源的驱动方法和切换电源的驱动程序 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR101196609B1 (ko) | 2012-11-02 |

| US8436685B2 (en) | 2013-05-07 |

| EP2329597B1 (en) | 2015-05-13 |

| CN102160291B (zh) | 2013-08-28 |

| EP2329597A1 (en) | 2011-06-08 |

| US20110163816A1 (en) | 2011-07-07 |

| JP4879240B2 (ja) | 2012-02-22 |

| EP2329597A4 (en) | 2014-03-05 |

| WO2010032380A1 (en) | 2010-03-25 |

| CN102160291A (zh) | 2011-08-17 |

| KR20110043771A (ko) | 2011-04-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4879240B2 (ja) | 発振回路、dc−dcコンバータ及び半導体装置 | |

| US10171089B2 (en) | PVT-free calibration function using a doubler circuit for TDC resolution in ADPLL applications | |

| US20030058053A1 (en) | Phase locked loop for reducing electromagnetic interference | |

| US8531214B2 (en) | Spread spectrum clock generators | |

| US20100289548A1 (en) | Frequency Generator for Generating Signals with Variable Frequencies | |

| US8952734B2 (en) | Frequency-control circuits and signal generation devices using the same | |

| US11063515B2 (en) | Power converter | |

| US11005366B2 (en) | Mixed power converter including switched-capacitor conversion circuit and inductor buck circuit | |

| JP4628434B2 (ja) | 発振周波数制御回路、その発振周波数制御回路を有するdc−dcコンバータ及び半導体装置 | |

| JP2006222524A (ja) | 発振回路 | |

| US7656214B1 (en) | Spread-spectrum clock generator | |

| US20040189358A1 (en) | Power-on reset circuit and method for low-voltage chips | |

| US6959063B1 (en) | Fractional-N phase locked loop | |

| JP5941244B2 (ja) | クロック発生回路、電源供給システム及びクロック信号の周波数変更方法 | |

| US20110018598A1 (en) | Pll circuit | |

| JP3446425B2 (ja) | 周波数同期回路 | |

| KR100960799B1 (ko) | 지터링 방식의 발진기 | |

| JPH09172371A (ja) | Pll回路に設けたチャージポンプの制御方法及びpll回路 | |

| US6680633B2 (en) | Small-sized analog generator producing clock signals | |

| JP5567389B2 (ja) | クロック発生回路 | |

| JP2006319446A (ja) | 分周回路 | |

| JP2002217725A (ja) | Pll周波数シンセサイザ回路 | |

| JPH07142966A (ja) | 逓倍回路 | |

| JP2007288536A (ja) | 位相シフト回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110804 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111101 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111129 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4879240 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141209 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |