JP2010034976A - 誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法 - Google Patents

誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法 Download PDFInfo

- Publication number

- JP2010034976A JP2010034976A JP2008196438A JP2008196438A JP2010034976A JP 2010034976 A JP2010034976 A JP 2010034976A JP 2008196438 A JP2008196438 A JP 2008196438A JP 2008196438 A JP2008196438 A JP 2008196438A JP 2010034976 A JP2010034976 A JP 2010034976A

- Authority

- JP

- Japan

- Prior art keywords

- error correction

- length

- subframe

- encoding

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Error Detection And Correction (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

Abstract

【解決手段】入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成し、サブフレームごとにブロック符号による誤り訂正符号化を行うとともに、情報ビットが所定の情報長に満たないサブフレームに対し、当該サブフレームの情報長に応じて検査ビット長を変動させて誤り訂正符号化する。

【選択図】図2

Description

図1は、この発明の実施の形態1による誤り訂正符号化装置を用いたデジタル伝送システム(以下、単に伝送システムと呼ぶ)の構成を示すブロック図である。図1において、実施の形態1によるデジタル伝送システムAは、誤り訂正符号化装置1、変調器2、通信路3、復調器4、アナログ/デジタル(A/D)変換器5、及び誤り訂正復号装置6を備える。

図2は、図1中の誤り訂正符号化装置の構成を概略的に示すブロック図である。図2において、誤り訂正符号化装置1は、第1の多重分離回路7、フレーム生成回路8、FEC符号化回路9、第1の多重化回路10及び制御回路11を備える。情報源に接続する第1の多重分離回路7からフレーム生成回路8、FEC符号化回路9、第1の多重化回路10の順で接続しており、第1の多重分離回路7から後段へ処理データが順次入力されて符号化処理が行われる。

次に、誤り訂正符号化装置1の動作について説明する。

第1の多重分離回路7は、情報源から入力した第1の情報系列を多重分離して、第2の情報系列に変換する。この変換方法は、情報源から入力された情報系列の態様に応じて異なる。つまり、入力した情報系列の並列数(直列若しくは所定の並列)及び動作周波数等の違いによって異なる。なお、情報系列の態様は、入力側の処理と出力側の処理とで整合していればよい。また、情報系列の態様の違い自体は、この発明の特徴となるものではない。

図3は、図1中の誤り訂正復号装置の構成を概略的に示すブロック図である。図3において、誤り訂正復号装置6は、誤り訂正符号化装置1が符号化した誤り訂正符号を復号する機能を有し、第2の多重分離回路12、フレーム同期回路13、FEC復号回路14、フレーム分離回路15、第2の多重化回路16、及び制御回路17を備える。図1中のA/D変換器5に接続する第2の多重分離回路12からフレーム同期回路13、FEC復号回路14、フレーム分離回路15、第2の多重化回路16の順で接続しており、第2の多重分離回路12から後段へ処理データが順次入力されて復号処理が行われる。

図4は、図3中のFEC復号回路の構成を概略的に示すブロック図であり、RS符号による符号化に対応した回路構成を示している。図4において、FEC復号回路14は、シンドローム演算回路18、ユークリッド演算回路19、チェンサーチ演算回路20、復号結果演算回路21、及び遅延バッファ22を備える。

定義:1の原始2q−1乗根αの連続するm個のベキαi,i=0,・・・,m−1を根に持つガロア体GF(2q)上の多項式を生成多項式とする符号(mは偶数)。

Si=Y(αi)(i=1,2,・・・,m) ・・・(1)

次に、誤り訂正復号装置6の動作について説明する。

誤り訂正復号装置6に直列の順序で入力された第1の量子化受信系列は、第2の多重分離回路12によりq並列の順序に変換され、第2の量子化受信系列が生成される。なお、第2の多重分離回路12で実施される多重分離処理は、第1の多重化回路10の逆変換に対応するものとなる。

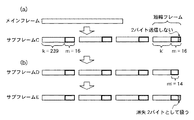

誤り訂正符号化装置1のFEC符号化回路9は、図5に示すように、通常のサブフレームの情報長をkシンボルとし、パリティ長をmシンボルと定めたとき、入力された情報系列の最後に対応する短縮フレームに対し、予め設定された条件でパリティ長m’を変動させる。また、短縮フレームの情報長k’は、入力された情報系列であるイーサネット(登録商標)フレームの長さ及び通常のサブフレームの情報長kに基づいて、一意に定まる。なお、FEC符号化回路9による、情報長k’に対するパリティ長m’は、下記の算出基準1,2に基づいて設定する。

算出基準1として、復号後ビット誤り率を基準として、これが均一になるような条件を定める。具体的には、下記式(4)に基づいて算出する。但し、通常のサブフレームの符号語ck,mの復号後ビット誤り率をBER(ck,m,s)とし、短縮フレームの符号語ck',m'の復号後ビット誤り率をBER(ck',m',s)と定義する。また、sは、通信路3の信号対雑音比、関数BERは通信路モデルにより規定されるものである。

RS符号の復号後ビット誤り率は、パリティ長固定で情報長を短くすると、同一信号対雑音比に対して向上することが知られている。逆に言うと、従来の短縮フレームは、通常の符号語に比べて訂正能力が向上する一方、符号化率が劣る。このため、短縮フレームについてのみ、通常の符号語と同程度の復号後ビット誤り率BERになるように、パリティ長さm’を短縮するように切り替える。これにより、従来より符号化率が向上する。

算出基準2として、各サブフレームの分割された入力情報系列の情報長を基準として、予め設定する閾値の条件を定める。具体的には下記式(5)に基づいて算出する。但し、k1,k2,・・・は予め設定する閾値であり、伝送条件等により適宜定めるものである。この算出基準2では、短縮フレームのパリティ長m’の算出基準を、短縮フレームの情報長k’のみで規定する。このように算出基準2では、短縮フレームの情報長の場合分けによってパリティ長m’を決定できるので、上記式(4)に基づく算出処理より演算を簡易化できる。

上記実施の形態1は、誤り訂正符号化装置1において、パリティ長m’<mの短縮フレームについて、情報長k’及びパリティ長m’のブロック符号として符号化する場合を示した。これに対し、この実施の形態2では、短縮フレームを情報長k’及びパリティ長mのブロック符号として符号化し、差分m−m’については送信せずに棄却する処理を説明する。

図7は、実施の形態2による訂正符号化を説明するための図であり、この図に沿って説明する。実施の形態2による誤り訂正符号化装置1のFEC符号化回路9は、図7(a)中のサブフレームCに示すように、短縮フレームを情報長k’及びパリティ長mのブロック符号として符号化処理する。また、差分m−m’(図7(a)の例では、2バイト分)については送信せずに棄却する。これにより、実施の形態2による誤り訂正符号化装置1から通信路3へは、図7(b)中のサブフレームDに示すような系列(短縮フレームのパリティ長がm’=14バイト)が送信される。

S’i=Y(αi)・λ(αi)(i=1,2,・・・,m) ・・・(6)

λ(z)=(1−αj1'z)(1−αj2'z)・・・(1−αjh'z)・・・(7)

Claims (9)

- 入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成するフレーム生成手段と、

前記フレーム生成手段で生成されたサブフレームごとにブロック符号による誤り訂正符号化を行うとともに、情報ビットが前記所定の情報長に満たないサブフレームに対し、当該サブフレームの情報長に応じて検査ビット長を変動させて誤り訂正符号化する符号化手段とを備えた誤り訂正符号化装置。 - 符号化手段は、所定の情報長を有するサブフレームとの間で、復号後のビット誤り率が均一になるように、前記所定の情報長に満たないサブフレームに付与する検査ビット長を設定することを特徴とする請求項1記載の誤り訂正符号化装置。

- 符号化手段は、所定の情報長に満たないサブフレームの情報長と所定の閾値を比較し、この比較結果に応じて前記サブフレームに付与する検査ビット長を設定することを特徴とする請求項1記載の誤り訂正符号化装置。

- 符号化手段は、所定の情報長に満たないサブフレームの情報長が所定の閾値よりも短い場合、前記サブフレームに付与する検査ビット長を、フレーム生成手段で生成された他のサブフレームの検査ビット長より短くすることを特徴とする請求項3記載の誤り訂正符号化装置。

- 符号化手段は、フレーム生成手段で生成されたサブフレームごとにブロック符号による誤り訂正符号化を行うとともに、情報ビットが前記所定の情報長に満たない短縮されたサブフレームに対し、当該サブフレームの情報長に応じて検査ビットの一部を棄却して誤り訂正符号化することを特徴とする請求項1記載の誤り訂正符号化装置

- 符号化手段は、ブロック符号としてリード−ソロモン符号を用いることを特徴とする請求項1から請求項5のうちのいずれか1項記載の誤り訂正符号化装置。

- 請求項1から請求項6のうちのいずれか1項記載の誤り訂正符号化装置で生成された誤り訂正符号化データを受信し、当該誤り訂正符号化データを構成する各サブフレームに同期するためのフレーム同期信号を生成するフレーム同期手段と、

前記フレーム同期手段で生成されたフレーム同期信号に基づいて、前記誤り訂正符号化データを、前記サブフレームごとに誤り訂正を行って復号するとともに、所定の情報長に満たないサブフレームに当該情報長に応じた長さの検査ビットを付与した符号化データを復号する復号手段とを備えた誤り訂正復号装置。 - 符号化手段は、請求項5記載の誤り訂正符号化装置で棄却された検査ビットの一部を消失ビットとみなして復号することを特徴とする請求項7記載の誤り訂正復号装置。

- 入力した情報系列を所定の情報長ごとに分割して複数のサブフレームを生成するステップと、

前記ステップで生成されたサブフレームごとにブロック符号による誤り訂正符号化を行うとともに、情報ビットが前記所定の情報長に満たないサブフレームに対し、当該サブフレームの情報長に応じて検査ビット長を変動させて誤り訂正符号化するステップとを備えた誤り訂正符号化方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008196438A JP2010034976A (ja) | 2008-07-30 | 2008-07-30 | 誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008196438A JP2010034976A (ja) | 2008-07-30 | 2008-07-30 | 誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010034976A true JP2010034976A (ja) | 2010-02-12 |

| JP2010034976A5 JP2010034976A5 (ja) | 2011-03-24 |

Family

ID=41738935

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008196438A Pending JP2010034976A (ja) | 2008-07-30 | 2008-07-30 | 誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010034976A (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2362454A2 (en) | 2010-02-19 | 2011-08-31 | Asahi Glass Company Limited | Substrate for mounting light-emitting element and light-emitting device |

| CN102438207A (zh) * | 2011-12-12 | 2012-05-02 | 河海大学 | 一种无线多跳网中的实时多播方法 |

| JP2013009191A (ja) * | 2011-06-24 | 2013-01-10 | Fujitsu Ltd | 誤り訂正処理回路および誤り訂正処理方法 |

| CN103138880A (zh) * | 2011-11-30 | 2013-06-05 | 北京东方广视科技股份有限公司 | 编解码方法和设备 |

| CN103138881A (zh) * | 2011-11-30 | 2013-06-05 | 北京东方广视科技股份有限公司 | 编解码方法和设备 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06188746A (ja) * | 1992-07-20 | 1994-07-08 | Digital Equip Corp <Dec> | 誤り訂正システム |

| JPH07336364A (ja) * | 1994-06-08 | 1995-12-22 | Canon Inc | デジタル無線通信システム |

| JPH11136218A (ja) * | 1997-10-27 | 1999-05-21 | Nec Corp | データ伝送システム、データ送信装置およびデータ伝送方法 |

| JP2000315955A (ja) * | 1999-04-30 | 2000-11-14 | Mitsubishi Electric Corp | 符号化方法、シンドローム演算方法、誤りビット数推定方法、誤りビット位置推定方法、復号方法および復号装置 |

| JP2007537651A (ja) * | 2004-05-13 | 2007-12-20 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | Mimoofdm無線ローカルエリアネットワークを実現するための方法及びシステム |

-

2008

- 2008-07-30 JP JP2008196438A patent/JP2010034976A/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06188746A (ja) * | 1992-07-20 | 1994-07-08 | Digital Equip Corp <Dec> | 誤り訂正システム |

| JPH07336364A (ja) * | 1994-06-08 | 1995-12-22 | Canon Inc | デジタル無線通信システム |

| JPH11136218A (ja) * | 1997-10-27 | 1999-05-21 | Nec Corp | データ伝送システム、データ送信装置およびデータ伝送方法 |

| JP2000315955A (ja) * | 1999-04-30 | 2000-11-14 | Mitsubishi Electric Corp | 符号化方法、シンドローム演算方法、誤りビット数推定方法、誤りビット位置推定方法、復号方法および復号装置 |

| JP2007537651A (ja) * | 2004-05-13 | 2007-12-20 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | Mimoofdm無線ローカルエリアネットワークを実現するための方法及びシステム |

Non-Patent Citations (1)

| Title |

|---|

| JPN6012048984; IEEE Std 802.16a-2003 (Amendment to IEEE Std 802.16-2001) , 2003, p.93-95 * |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2362454A2 (en) | 2010-02-19 | 2011-08-31 | Asahi Glass Company Limited | Substrate for mounting light-emitting element and light-emitting device |

| JP2013009191A (ja) * | 2011-06-24 | 2013-01-10 | Fujitsu Ltd | 誤り訂正処理回路および誤り訂正処理方法 |

| US9166739B2 (en) | 2011-06-24 | 2015-10-20 | Fujitsu Limited | Error correction processing circuit and error correction processing method |

| CN103138880A (zh) * | 2011-11-30 | 2013-06-05 | 北京东方广视科技股份有限公司 | 编解码方法和设备 |

| CN103138881A (zh) * | 2011-11-30 | 2013-06-05 | 北京东方广视科技股份有限公司 | 编解码方法和设备 |

| CN102438207A (zh) * | 2011-12-12 | 2012-05-02 | 河海大学 | 一种无线多跳网中的实时多播方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9081677B2 (en) | Method and device for estimating input bit error ratio | |

| JP4382124B2 (ja) | 誤り訂正符号化装置及び誤り訂正復号装置 | |

| JP5466317B2 (ja) | データ伝送方法 | |

| US8522116B2 (en) | Systems and methods for performing forward error correction | |

| US9148175B2 (en) | Error correction coding device, error correction decoding device and method therefor | |

| US20150039977A1 (en) | Method And Apparatus For Error Detection In A Communication System | |

| JPH11191758A (ja) | 情報データ多重化伝送システムとその多重化装置及び分離装置 | |

| CN1625859A (zh) | 以太网中的前向纠错编码 | |

| US7870466B2 (en) | Parallel cyclic code generation device and parallel cyclic code error detection device | |

| JP2009077391A (ja) | 符号化装置及び復号装置 | |

| JP2012517138A (ja) | 削除訂正畳み込み符号および畳み込みターボ符号のための符号化法および復号法 | |

| JP2012527815A (ja) | エンコーダ、デコーダ、符号化、及び復号化方法 | |

| KR20110066084A (ko) | 정보 객체의 인코딩을 위한 방법 및 이를 이용한 인코더 | |

| JP2010034976A (ja) | 誤り訂正符号化装置、誤り訂正復号装置及び誤り訂正符号化方法 | |

| JP2010268114A (ja) | 誤り訂正符号化方法、誤り訂正復号方法、誤り訂正符号化装置および誤り訂正復号装置 | |

| KR20090074183A (ko) | 데이터를 인코딩 및 디코딩하는 방법 및 장치 | |

| JP2006295510A (ja) | Fecフレーム符号化装置、fec多重化装置、fec多重分離装置、および光通信装置 | |

| JP6265938B2 (ja) | 誤り訂正装置、光受信器および光伝送装置 | |

| KR20120004662A (ko) | 오류 정정의 병렬 처리를 위한 방송 신호 부호화 및 복호화 방법, 이를 위한 방송 신호 송수신 장치 및 이를 위한 시스템 | |

| JP2010200247A (ja) | デジタル伝送システム及びデジタル伝送方法 | |

| JP2013070289A (ja) | 誤り訂正方法、誤り訂正装置、送信機、受信機及び誤り訂正プログラム | |

| KR20050054405A (ko) | 이동통신시스템에서 상이한 전송시간간격들을 가지는채널들을 다중화하는 전송률 정합 방법 및 장치 | |

| JP2006060296A (ja) | 連接符号システムおよび連接符号処理方法、復号装置 | |

| JP2007116591A (ja) | 符号化装置、復号化装置、および符号化・復号化システム | |

| US20080043856A1 (en) | Encoding System Using a Non-Binary Turbo Code and an Encoding Method Thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110207 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120910 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120918 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130212 |