JP2010020846A - 半導体記憶装置の読み出し回路 - Google Patents

半導体記憶装置の読み出し回路 Download PDFInfo

- Publication number

- JP2010020846A JP2010020846A JP2008180969A JP2008180969A JP2010020846A JP 2010020846 A JP2010020846 A JP 2010020846A JP 2008180969 A JP2008180969 A JP 2008180969A JP 2008180969 A JP2008180969 A JP 2008180969A JP 2010020846 A JP2010020846 A JP 2010020846A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- circuit

- gate

- transistor

- connection node

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 19

- 230000015654 memory Effects 0.000 claims description 26

- 239000003990 capacitor Substances 0.000 claims description 14

- 239000000758 substrate Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 230000006870 function Effects 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 230000005689 Fowler Nordheim tunneling Effects 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

Images

Landscapes

- Read Only Memory (AREA)

Abstract

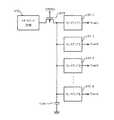

【解決手段】センスアンプ131の接続ノードAの電圧を所定電圧に初期設定するためのスタートアップ回路132を設けた。スタートアップ回路132の出力端子と接続ノードAの間には、Pチャネル型MOSトランジスタからなる転送ゲートMT6が挿入されている。転送ゲートMT6のオンオフは、そのゲートに印加されたスタートアップ・イネーブル信号STPENによって制御される。すなわち、転送ゲートMT6は、スタートアップ・イネーブル信号STPENがロウのときにオンし、スタートアップ回路132の出力電圧Soutを接続ノードAに転送する。

【選択図】図3

Description

(EEPROMの全体の構成)

図1は、半導体記憶装置の回路ブロック図である。図示のように、メモリアレイ領域10において、複数のビット線BL0〜BLnがY方向に延びており、Y方向と直交するX方向に、複数のワード線WL0〜WLm、複数のソース線SL0〜SLmが延びている。複数のビット線BL0〜BLnと複数のワード線WL0〜WLmの各交差点に対応して、複数のメモリセルMCが設けられている。

メモリセルMCの具体的な構成例について、図2を参照して説明する。このメモリセルMCは、スプリットゲート型であり、半導体基板101上に所定間隔を隔てて形成されたドレイン領域113及びソース領域114の間にチャネル領域115が形成されている。チャネル領域115の一部上からソース領域114の一部上にゲート絶縁膜105を介して延在するフローティングゲート109が形成され、該フローティングゲート109の上部及び側部を、トンネル絶縁膜110を介して被覆し、かつドレイン領域113の一部上に延在したコントロールゲート112が形成されている。

次に、本願の特徴である、読み出し回路13の具体的な構成例について、図3乃至図5を参照して説明する。この読み出し回路13は、センスアンプ131、スタートアップ回路132、スタートアップ回路132の出力電圧をセンスアンプ131に転送する転送ゲートMT6を備えている。

Vdd−Vtp<VA<Vdd+VF ・・・・(1)

ここで、Vtpは、MT3のしきい値、VFはMT3のドレインと半導体基板で形成されるダイオードの順方向電圧であり、約0.6Vである。

スタートアップ回路132の第1の構成例について、図6を参照して説明する。図示のように、Pチャネル型の第7のMOSトランジスタMT7と抵抗素子R1が直列に接続されている。MT7のゲートは、MT7とR1の接続ノードに接続される。つまり、MT7はダイオード接続されており、ダイオードとして働く。MT7のソースには電源電圧Vddが印加され、抵抗素子R1の一方の端子は接地されている。MT7とR1の接続ノードが出力端子となる。MT7とR1には、電流iが定常的に流れる。

13 読み出し回路

BL0〜BL5 ビット線 WL0〜WL3 ワード線 SL0〜SL3 ソース線

101 半導体基板 105 ゲート絶縁膜

109 フローティングゲート 109a 突起部 110 トンネル絶縁膜

112 コントロールゲート 113 ドレイン領域 114 ソース領域

115 チャネル領域

Claims (4)

- メモリセルからのデータ電圧がゲートに印加された第1のトランジスタと、リファレンス電圧がゲートに印加された第2のトランジスタと、前記第1のトランジスタに直列に接続され、ゲートが前記第1のトランジスタとの接続ノードに接続された第3のトランジスタと、前記第2のトランジスタに直列に接続され、ゲートが前記第3のトランジスタのゲートに接続された第4のトランジスタと、を備え、前記データ電圧と前記リファレンス電圧との差を増幅して出力するセンスアンプと、

前記接続ノードの電圧を所定電圧に初期設定するスタートアップ回路と、

前記スタートアップ回路により前記接続ノードの電圧を所定電圧に設定した後に、

前記センスアンプを活性化させる制御スイッチと、を備えることを特徴とする半導体記憶装置の読み出し回路。 - 前記スタートアップ回路は、電源電圧と接地の間に直列接続されたダイオードと抵抗素子を備え、前記ダイオードと抵抗素子の接続ノードから前記所定電圧を出力することを特徴とする請求項1に記載の半導体記憶装置の読み出し回路。

- 前記スタートアップ回路は、電源電圧と接地の間に直列接続されたダイオードと抵抗素子と、

第1の端子と第2の端子を有し、前記第1の端子が接地されたキャパシタと、

前記キャパシタの第2の端子に接続され、ダイオードと抵抗素子の接続ノードの電圧に応じて、前記キャパシタの前記第2の端子の電圧が前記所定電圧になるまで前記キャパシタを充電し、充電が完了した時にオフするスイッチング素子と、を備えることを特徴とする請求項1に記載の半導体記憶装置の読み出し回路。 - 前記スタートアップ回路は複数のセンスアンプに共通に設けられていることを特徴とする請求項3に記載の半導体記憶装置の読み出し回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008180969A JP5341412B2 (ja) | 2008-07-11 | 2008-07-11 | 半導体記憶装置の読み出し回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008180969A JP5341412B2 (ja) | 2008-07-11 | 2008-07-11 | 半導体記憶装置の読み出し回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010020846A true JP2010020846A (ja) | 2010-01-28 |

| JP5341412B2 JP5341412B2 (ja) | 2013-11-13 |

Family

ID=41705575

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008180969A Active JP5341412B2 (ja) | 2008-07-11 | 2008-07-11 | 半導体記憶装置の読み出し回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5341412B2 (ja) |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60145593A (ja) * | 1984-01-06 | 1985-08-01 | Toshiba Corp | 半導体メモリ用センス回路 |

| JPS61126684A (ja) * | 1984-11-26 | 1986-06-14 | Hitachi Ltd | メモリを内蔵した半導体集積回路 |

| JPH11203882A (ja) * | 1998-01-19 | 1999-07-30 | Denso Corp | 半導体記憶装置 |

| JP2000011662A (ja) * | 1998-06-22 | 2000-01-14 | Nkk Corp | 低消費高速型センスアンプ |

| JP2001101872A (ja) * | 1999-09-30 | 2001-04-13 | Mitsubishi Electric Corp | 増幅回路 |

| WO2004025817A1 (ja) * | 2002-09-11 | 2004-03-25 | Mitsubishi Denki Kabushiki Kaisha | 電圧検出回路およびこれを用いた内部電圧発生回路 |

| JP2004241101A (ja) * | 2003-02-07 | 2004-08-26 | United Memories Inc | 集積回路装置、読出データ増幅器、および読出データ増幅器を動作させるための方法 |

| JP2008021088A (ja) * | 2006-07-12 | 2008-01-31 | Yamaha Corp | 基準電圧発生回路 |

-

2008

- 2008-07-11 JP JP2008180969A patent/JP5341412B2/ja active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60145593A (ja) * | 1984-01-06 | 1985-08-01 | Toshiba Corp | 半導体メモリ用センス回路 |

| JPS61126684A (ja) * | 1984-11-26 | 1986-06-14 | Hitachi Ltd | メモリを内蔵した半導体集積回路 |

| JPH11203882A (ja) * | 1998-01-19 | 1999-07-30 | Denso Corp | 半導体記憶装置 |

| JP2000011662A (ja) * | 1998-06-22 | 2000-01-14 | Nkk Corp | 低消費高速型センスアンプ |

| JP2001101872A (ja) * | 1999-09-30 | 2001-04-13 | Mitsubishi Electric Corp | 増幅回路 |

| WO2004025817A1 (ja) * | 2002-09-11 | 2004-03-25 | Mitsubishi Denki Kabushiki Kaisha | 電圧検出回路およびこれを用いた内部電圧発生回路 |

| JP2004241101A (ja) * | 2003-02-07 | 2004-08-26 | United Memories Inc | 集積回路装置、読出データ増幅器、および読出データ増幅器を動作させるための方法 |

| JP2008021088A (ja) * | 2006-07-12 | 2008-01-31 | Yamaha Corp | 基準電圧発生回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5341412B2 (ja) | 2013-11-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5235422B2 (ja) | 不揮発性半導体記憶装置 | |

| US6243292B1 (en) | Nonvolatile semiconductor memory device capable of reducing memory array area | |

| JP5193701B2 (ja) | 半導体記憶装置 | |

| JP4083147B2 (ja) | 半導体記憶装置 | |

| JP2010211899A (ja) | 半導体記憶装置 | |

| KR100893474B1 (ko) | 반도체 기억 장치 | |

| CN107808683B (zh) | 用于读取阵列中的闪存单元的带位线预充电电路的改进读出放大器 | |

| CN102142279B (zh) | 半导体存储装置 | |

| JP5240291B2 (ja) | 不揮発性半導体メモリ素子および半導体装置 | |

| JP4541355B2 (ja) | 電流電圧変換回路 | |

| US5910918A (en) | Data writing circuit for a nonvolatile semiconductor memory | |

| JPH10214491A (ja) | 不揮発性半導体メモリの消去方法及び消去装置 | |

| JP3825596B2 (ja) | 半導体記憶装置及びその制御方法 | |

| US5253210A (en) | Paritioned bit line structure of EEPROM and method of reading data therefrom | |

| JP5477483B2 (ja) | 不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置 | |

| JP5341412B2 (ja) | 半導体記憶装置の読み出し回路 | |

| JP4286085B2 (ja) | 増幅器及びそれを用いた半導体記憶装置 | |

| JP5044201B2 (ja) | 半導体記憶装置 | |

| JP2002184192A (ja) | 不揮発性半導体記憶装置とその書き換え方法 | |

| JP5487539B2 (ja) | 不揮発性半導体記憶素子 | |

| JPH0765589A (ja) | 不揮発性半導体記憶装置 | |

| JP2010015643A (ja) | 半導体記憶装置及び半導体記憶装置のデータ読み出し方法 | |

| JP5522296B2 (ja) | 不揮発性半導体記憶装置 | |

| JPH04252497A (ja) | 不揮発性半導体記憶装置 | |

| CN118658509A (zh) | 一种sonos闪存控制器系统、电子设备和编程方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20110531 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20110602 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110624 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130123 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130207 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130215 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20130301 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130404 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130418 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130701 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130723 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130808 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5341412 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |