JP2010010487A - 固体撮像装置及び電子機器 - Google Patents

固体撮像装置及び電子機器 Download PDFInfo

- Publication number

- JP2010010487A JP2010010487A JP2008169447A JP2008169447A JP2010010487A JP 2010010487 A JP2010010487 A JP 2010010487A JP 2008169447 A JP2008169447 A JP 2008169447A JP 2008169447 A JP2008169447 A JP 2008169447A JP 2010010487 A JP2010010487 A JP 2010010487A

- Authority

- JP

- Japan

- Prior art keywords

- photodiode

- solid

- state imaging

- imaging device

- gate electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/803—Pixels having integrated switching, control, storage or amplification elements

- H10F39/8037—Pixels having integrated switching, control, storage or amplification elements the integrated elements comprising a transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/802—Geometry or disposition of elements in pixels, e.g. address-lines or gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/806—Optical elements or arrangements associated with the image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/813—Electronic components shared by multiple pixels, e.g. one amplifier shared by two pixels

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Abstract

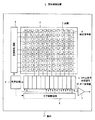

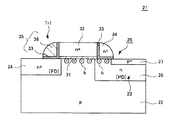

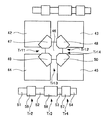

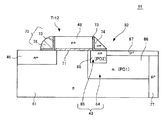

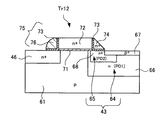

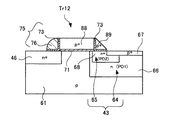

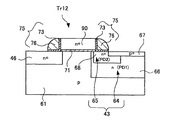

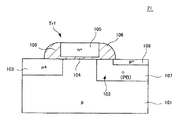

【解決手段】単位画素内に、第1のフォトダイオード64と、第2のフォトダイオード65とからなる光電変換部43を有し、第2のフォトダイオード65が、転送ゲート電極72近傍に位置し、第1のフォトダイオード64よりも高い不純物濃度を有している。

【選択図】図4

Description

本発明に係る電子機器によれば、固体撮像装置における信号電荷の読み出し特性を改善することができる。

出力回路7は、カラム信号処理回路5の各々から水平信号線10を通して順次に供給される信号に対し、信号処理を行って出力する。

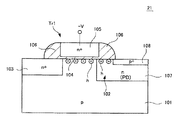

n+ゲート電極48及びn+ポリサイドウォール74を有する構成を有するので、第1実施の形態と同様の効果も奏する。

その他の構成は、図4の第2実施の形態と同様であるので、図4と対応する部分には同一符号を付して重複説明を省略する。

その他の構成は、図4の第2実施の形態と同様であるので、図4と対応する部分には同一符号を付して重複説明を省略する。

その他の構成は、図4の第2実施の形態と同様であるので、図4と対応する部分には同一符号を付して重複説明を省略する。

この例では、転送ゲート電極90による電界で第2のフォトダイオード65表面がホールピニング状態になる。

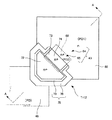

図14に、本発明の電子機器の一例としてカメラに適用した実施の形態を示す。本実施の形態に係るカメラ95は、光学系(光学レンズ)96と、固体撮像装置97と、信号処理回路98とを備えてなる。固体撮像装置97は、上述した各実施の形態のいずれか1つの固体撮像装置が適用される。光学系96は、被写体からの像光(入射光)を固体撮像装置97の撮像面上に結像させる。これにより、固体撮像装置97の光電変換素子において一定期間信号電荷が蓄積される。信号処理回路98は、固体撮像装置97の出力信号に対して種々の信号処理を施して出力する。本実施の形態のカメラ95は、光学系96、固体撮像装置97、信号処理回路98がモジュール化したカメラモジュールの形態を含む。

さらに、図14の構成は、光学系96、固体撮像装置97、信号処理回路98がモジュール化した撮像機能を有するモジュール、いわゆる撮像機能モジュ−ルとして構成することができる。本発明は、このような撮像機能モジュールを備えた電子機器を構成することができる。

Claims (9)

- 光電変換部と、

フローティングディフージョン部と、

n型半導体による転送ゲート電極と、

前記転送ゲート電極の前記光電変換部側に絶縁膜を介して形成されたn型半導体によるサイドウォールと、

前記転送ゲート電極の前記フローティングディフージョン部側に形成された絶縁層によるサイドウォールと

を有する固体撮像装置。 - 電荷蓄積時に、前記n型半導体によるサイドウォール下の前記光電変換部の表面が、ゲート電圧により、信号電荷と逆の電荷でピニングされる

請求項1記載の固体撮像装置。 - 単位画素内に、

第1のフォトダイオードと、第2のフォトダイオードとからなる光電変換部を有し、

前記第2のフォトダイオードが、転送ゲート電極近傍に位置し、前記第1のフォトダイオードよりも高い不純物濃度を有している

固体撮像装置。 - 前記第1のフォトダイオードは、表面に電荷蓄積領域とは逆導電型のアキュムレーション領域が形成された埋め込み型フォトダイオードで形成され、

前記第2のフォトダイオードは、表面に転送ゲート電極による電界、もしくは転送ゲート電極に絶縁膜を介して形成された半導体によるサイドウォールにより、信号電荷と逆の電荷が励起されるフォトダイオードで形成される

請求項3記載の固体撮像装置。 - 転送ゲート電極の前記第2のフォトダイオード側に所要導電型半導体によるサイドウォールが形成される

請求項4記載の固体撮像装置。 - 固体撮像装置と、

前記固体撮像装置の光電変換部に入射光を導く光学系と、

前記固体撮像装置の出力信号を処理する信号処理回路を備え、

前記固体撮像装置は、

光電変換部と、

フローティングディフージョン部と、

n型半導体による転送ゲート電極と、

前記転送ゲート電極の前記光電変換部側に絶縁膜を介して形成されたn型半導体によるサイドウォールと、

前記転送ゲート電極の前記フローティングディフージョン部側に形成された絶縁層によるサイドウォールと

を有する電子機器。 - 前記固体撮像装置において、電荷蓄積時、前記n型半導体によるサイドウォール下の前記光電変換部の表面が、ゲート電圧により、信号電荷と逆の電荷でピニングされる

請求項6記載の電子機器。 - 固体撮像装置と、

前記固体撮像装置の光電変換部に入射光を導く光学系と、

前記固体撮像装置の出力信号を処理する信号処理回路を備え、

前記固体撮像装置は、単位画素内に、第1のフォトダイオードと、第2のフォトダイオードとからなる光電変換部を有し、

前記第2のフォトダイオードが、転送ゲート電極近傍に位置し、前記第1のフォトダイオードよりも高い不純物濃度を有している

電子機器。 - 前記固体撮像装置において、

前記第1のフォトダイオードは、表面に電荷蓄積領域とは逆導電型のアキュムレーション領域が形成された埋め込み型フォトダイオードで形成され、

前記第2のフォトダイオードは、表面に転送ゲート電極による電界、もしくは転送ゲート電極に絶縁膜を介して形成された半導体によるサイドウォールにより、信号電荷と逆の電荷が励起されるフォトダイオードで形成される

請求項8記載の電子機器。

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008169447A JP4788742B2 (ja) | 2008-06-27 | 2008-06-27 | 固体撮像装置及び電子機器 |

| TW101143787A TW201310631A (zh) | 2008-06-27 | 2009-06-04 | 固體攝像裝置及電子機器 |

| TW098118585A TWI404200B (zh) | 2008-06-27 | 2009-06-04 | Solid-state imaging devices and electronic machines |

| KR1020090056815A KR20100002184A (ko) | 2008-06-27 | 2009-06-25 | 고체 촬상 장치 및 전자 기기 |

| US12/491,740 US8169523B2 (en) | 2008-06-27 | 2009-06-25 | Solid-state imaging device and electronic apparatus |

| CN2009101422372A CN101615621B (zh) | 2008-06-27 | 2009-06-26 | 固体摄像装置和电子装置 |

| CN201210120959.XA CN102683370B (zh) | 2008-06-27 | 2009-06-26 | 固体摄像装置及其制造方法以及电子装置 |

| US13/408,393 US8593553B2 (en) | 2008-06-27 | 2012-02-29 | Solid-state imaging device and electronic apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008169447A JP4788742B2 (ja) | 2008-06-27 | 2008-06-27 | 固体撮像装置及び電子機器 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010145456A Division JP5083380B2 (ja) | 2010-06-25 | 2010-06-25 | 固体撮像装置及び電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010010487A true JP2010010487A (ja) | 2010-01-14 |

| JP4788742B2 JP4788742B2 (ja) | 2011-10-05 |

Family

ID=41446919

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008169447A Expired - Fee Related JP4788742B2 (ja) | 2008-06-27 | 2008-06-27 | 固体撮像装置及び電子機器 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US8169523B2 (ja) |

| JP (1) | JP4788742B2 (ja) |

| KR (1) | KR20100002184A (ja) |

| CN (2) | CN102683370B (ja) |

| TW (2) | TWI404200B (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011239070A (ja) * | 2010-05-07 | 2011-11-24 | Sony Corp | 固体撮像装置、および、その製造方法、電子機器 |

| CN105990387A (zh) * | 2015-03-19 | 2016-10-05 | 精工爱普生株式会社 | 固体摄像元件及其制造方法 |

| JP2016178144A (ja) * | 2015-03-19 | 2016-10-06 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| JP2016178145A (ja) * | 2015-03-19 | 2016-10-06 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| JP2017199855A (ja) * | 2016-04-28 | 2017-11-02 | 国立大学法人静岡大学 | 絶縁ゲート型半導体素子及び固体撮像装置 |

| JP2019140637A (ja) * | 2018-02-15 | 2019-08-22 | キヤノン株式会社 | 撮像装置及び撮像システム |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5029624B2 (ja) * | 2009-01-15 | 2012-09-19 | ソニー株式会社 | 固体撮像装置及び電子機器 |

| JP5535685B2 (ja) * | 2010-02-26 | 2014-07-02 | パナソニック株式会社 | 固体撮像装置及び駆動方法 |

| JP5539029B2 (ja) * | 2010-05-28 | 2014-07-02 | キヤノン株式会社 | 固体撮像装置の製造方法 |

| JP2012244125A (ja) * | 2011-05-24 | 2012-12-10 | Toshiba Corp | 固体撮像装置及びその製造方法 |

| CN102214696B (zh) * | 2011-05-27 | 2016-06-22 | 上海华虹宏力半导体制造有限公司 | 功率mos器件及功率mos器件制造方法 |

| CN102324430B (zh) * | 2011-09-20 | 2013-04-24 | 天津大学 | 电荷快速转移的四管有源像素及其制作方法 |

| US9970862B2 (en) | 2014-07-16 | 2018-05-15 | International Business Machines Corporation | Reflective tag and polarized light sensor for transmitting information |

| JP6623594B2 (ja) * | 2015-07-22 | 2019-12-25 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| TWI731026B (zh) * | 2016-01-15 | 2021-06-21 | 新加坡商海特根微光學公司 | 半導體器件 |

| KR102679205B1 (ko) * | 2019-07-02 | 2024-06-28 | 에스케이하이닉스 주식회사 | 이미지 센싱 장치 |

| CN114175622B (zh) * | 2019-09-17 | 2024-11-19 | 索尼半导体解决方案公司 | 摄像元件和摄像装置 |

| CN115280502A (zh) * | 2020-03-18 | 2022-11-01 | 索尼半导体解决方案公司 | 成像装置和电子设备 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11284167A (ja) * | 1998-03-31 | 1999-10-15 | Toshiba Corp | 半導体装置およびその製造方法および固体撮像装置 |

| JP2000091552A (ja) * | 1998-09-11 | 2000-03-31 | Toshiba Corp | 固体撮像装置 |

| JP2002217397A (ja) * | 2001-01-15 | 2002-08-02 | Sony Corp | 固体撮像装置及びその駆動方法 |

| JP2003101004A (ja) * | 2001-09-25 | 2003-04-04 | Toshiba Corp | 固体撮像装置及びその製造方法 |

| JP2004273640A (ja) * | 2003-03-06 | 2004-09-30 | Sony Corp | 固体撮像素子及びその製造方法 |

| JP2008166607A (ja) * | 2006-12-28 | 2008-07-17 | Sony Corp | 固体撮像装置とその製造方法、並びに半導体装置とその製造方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5889315A (en) * | 1994-08-18 | 1999-03-30 | National Semiconductor Corporation | Semiconductor structure having two levels of buried regions |

| JP4200545B2 (ja) * | 1998-06-08 | 2008-12-24 | ソニー株式会社 | 固体撮像素子およびその駆動方法、並びにカメラシステム |

| JP2004014911A (ja) * | 2002-06-10 | 2004-01-15 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| US7105793B2 (en) * | 2003-07-02 | 2006-09-12 | Micron Technology, Inc. | CMOS pixels for ALC and CDS and methods of forming the same |

| US7232712B2 (en) * | 2003-10-28 | 2007-06-19 | Dongbu Electronics Co., Ltd. | CMOS image sensor and method for fabricating the same |

| JP4341421B2 (ja) * | 2004-02-04 | 2009-10-07 | ソニー株式会社 | 固体撮像装置 |

| JP4502278B2 (ja) * | 2004-02-27 | 2010-07-14 | 国立大学法人東北大学 | 固体撮像装置、ラインセンサ、光センサおよび固体撮像装置の動作方法 |

| JP2006032681A (ja) | 2004-07-16 | 2006-02-02 | Sony Corp | 半導体装置および物理情報取得装置並びに半導体装置の駆動方法 |

| KR100674986B1 (ko) * | 2005-08-05 | 2007-01-29 | 삼성전자주식회사 | 이미지센서 및 그 제조방법 |

| US7795655B2 (en) * | 2006-10-04 | 2010-09-14 | Sony Corporation | Solid-state imaging device and electronic device |

| JP2008103644A (ja) * | 2006-10-20 | 2008-05-01 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2008166677A (ja) * | 2006-12-08 | 2008-07-17 | Sony Corp | 固体撮像装置とその製造方法並びにカメラ |

| KR100836507B1 (ko) * | 2006-12-27 | 2008-06-09 | 동부일렉트로닉스 주식회사 | 씨모스 이미지 센서의 제조방법 |

| KR100880528B1 (ko) * | 2007-06-01 | 2009-01-28 | 매그나칩 반도체 유한회사 | Cmos 이미지 센서 |

| US7759756B2 (en) * | 2008-02-04 | 2010-07-20 | Sharp Laboratories Of America, Inc. | Dual-pixel full color CMOS imager |

-

2008

- 2008-06-27 JP JP2008169447A patent/JP4788742B2/ja not_active Expired - Fee Related

-

2009

- 2009-06-04 TW TW098118585A patent/TWI404200B/zh not_active IP Right Cessation

- 2009-06-04 TW TW101143787A patent/TW201310631A/zh unknown

- 2009-06-25 US US12/491,740 patent/US8169523B2/en not_active Expired - Fee Related

- 2009-06-25 KR KR1020090056815A patent/KR20100002184A/ko not_active Ceased

- 2009-06-26 CN CN201210120959.XA patent/CN102683370B/zh not_active Expired - Fee Related

- 2009-06-26 CN CN2009101422372A patent/CN101615621B/zh not_active Expired - Fee Related

-

2012

- 2012-02-29 US US13/408,393 patent/US8593553B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH11284167A (ja) * | 1998-03-31 | 1999-10-15 | Toshiba Corp | 半導体装置およびその製造方法および固体撮像装置 |

| JP2000091552A (ja) * | 1998-09-11 | 2000-03-31 | Toshiba Corp | 固体撮像装置 |

| JP2002217397A (ja) * | 2001-01-15 | 2002-08-02 | Sony Corp | 固体撮像装置及びその駆動方法 |

| JP2003101004A (ja) * | 2001-09-25 | 2003-04-04 | Toshiba Corp | 固体撮像装置及びその製造方法 |

| JP2004273640A (ja) * | 2003-03-06 | 2004-09-30 | Sony Corp | 固体撮像素子及びその製造方法 |

| JP2008166607A (ja) * | 2006-12-28 | 2008-07-17 | Sony Corp | 固体撮像装置とその製造方法、並びに半導体装置とその製造方法 |

Cited By (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10720458B2 (en) | 2010-05-07 | 2020-07-21 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| US10355037B2 (en) | 2010-05-07 | 2019-07-16 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| US11671721B2 (en) | 2010-05-07 | 2023-06-06 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| US10978506B2 (en) | 2010-05-07 | 2021-04-13 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| JP2011239070A (ja) * | 2010-05-07 | 2011-11-24 | Sony Corp | 固体撮像装置、および、その製造方法、電子機器 |

| US9923005B2 (en) | 2010-05-07 | 2018-03-20 | Sony Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| US10050073B2 (en) | 2010-05-07 | 2018-08-14 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| US9653499B2 (en) | 2010-05-07 | 2017-05-16 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| US10177184B2 (en) | 2010-05-07 | 2019-01-08 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| US9438833B2 (en) | 2010-05-07 | 2016-09-06 | Sony Semiconductor Solutions Corporation | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus |

| US9818789B2 (en) | 2015-03-19 | 2017-11-14 | Seiko Epson Corporation | Solid-state imaging device and manufacturing method thereof |

| US9520436B2 (en) | 2015-03-19 | 2016-12-13 | Dexerials Corporation | Solid-state imaging device and manufacturing method thereof |

| JP2016178143A (ja) * | 2015-03-19 | 2016-10-06 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| JP2016178145A (ja) * | 2015-03-19 | 2016-10-06 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| CN105990387B (zh) * | 2015-03-19 | 2021-03-30 | 精工爱普生株式会社 | 固体摄像元件及其制造方法 |

| JP2016178144A (ja) * | 2015-03-19 | 2016-10-06 | セイコーエプソン株式会社 | 固体撮像素子及びその製造方法 |

| CN105990387A (zh) * | 2015-03-19 | 2016-10-05 | 精工爱普生株式会社 | 固体摄像元件及其制造方法 |

| JP2017199855A (ja) * | 2016-04-28 | 2017-11-02 | 国立大学法人静岡大学 | 絶縁ゲート型半導体素子及び固体撮像装置 |

| JP2019140637A (ja) * | 2018-02-15 | 2019-08-22 | キヤノン株式会社 | 撮像装置及び撮像システム |

| JP7108421B2 (ja) | 2018-02-15 | 2022-07-28 | キヤノン株式会社 | 撮像装置及び撮像システム |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102683370B (zh) | 2015-02-25 |

| JP4788742B2 (ja) | 2011-10-05 |

| CN101615621A (zh) | 2009-12-30 |

| US8169523B2 (en) | 2012-05-01 |

| US20120154657A1 (en) | 2012-06-21 |

| CN102683370A (zh) | 2012-09-19 |

| US20090322919A1 (en) | 2009-12-31 |

| TW201310631A (zh) | 2013-03-01 |

| TW201010069A (en) | 2010-03-01 |

| KR20100002184A (ko) | 2010-01-06 |

| CN101615621B (zh) | 2012-06-27 |

| TWI404200B (zh) | 2013-08-01 |

| US8593553B2 (en) | 2013-11-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4788742B2 (ja) | 固体撮像装置及び電子機器 | |

| US11817473B2 (en) | Solid-state imaging device, drive method thereof and electronic apparatus | |

| US11710753B2 (en) | Solid-state imaging device and method of manufacturing the same, and imaging apparatus | |

| JP5471174B2 (ja) | 固体撮像装置とその製造方法、及び電子機器 | |

| JP4224036B2 (ja) | フォトダイオード領域を埋め込んだイメージセンサ及びその製造方法 | |

| JP4514188B2 (ja) | 光電変換装置及び撮像装置 | |

| JP5537523B2 (ja) | 固体撮像装置 | |

| KR20090056846A (ko) | 고체 촬상 소자 및 카메라 | |

| JP2009277798A (ja) | 固体撮像装置及び電子機器 | |

| JP2011159758A (ja) | 固体撮像装置とその製造方法、並びに電子機器 | |

| JP5083380B2 (ja) | 固体撮像装置及び電子機器 | |

| US11569279B2 (en) | Solid-state imaging device, method of manufacturing solid-state imaging device, and electronic apparatus | |

| WO2025134543A1 (ja) | 光検出装置 | |

| JP2013211295A (ja) | 固体撮像装置及びその製造方法、電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100416 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100427 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100625 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110621 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110704 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140729 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |