JP2010010187A - 半導体集積回路装置の製造方法 - Google Patents

半導体集積回路装置の製造方法 Download PDFInfo

- Publication number

- JP2010010187A JP2010010187A JP2008164388A JP2008164388A JP2010010187A JP 2010010187 A JP2010010187 A JP 2010010187A JP 2008164388 A JP2008164388 A JP 2008164388A JP 2008164388 A JP2008164388 A JP 2008164388A JP 2010010187 A JP2010010187 A JP 2010010187A

- Authority

- JP

- Japan

- Prior art keywords

- integrated circuit

- semiconductor integrated

- circuit device

- manufacturing

- resin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W70/045—

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3421—Leaded components

- H05K3/3426—Leaded components characterised by the leads

-

- H10W70/421—

-

- H10W70/424—

-

- H10W70/457—

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10742—Details of leads

- H05K2201/1075—Shape details

- H05K2201/10795—Details of lead tips, e.g. pointed

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10742—Details of leads

- H05K2201/10886—Other details

- H05K2201/10909—Materials of terminal, e.g. of leads or electrodes of components

-

- H10W72/0198—

-

- H10W72/536—

-

- H10W72/5363—

-

- H10W72/5449—

-

- H10W72/5522—

-

- H10W74/00—

-

- H10W90/756—

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

- Lead Frames For Integrated Circuits (AREA)

Abstract

【解決手段】複数のリードの外端部を束ねるタイ・バーを有する多連リードフレームを用いたQFN型パッケージの半導体集積回路装置の製造方法において、モールド・キャビティ外周とタイ・バー間に充填された封止レジンをレーザにより除去した後、半田メッキ等の表面処理を実行する。

【選択図】図11

Description

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

(a)複数の単位デバイス領域を有し、各単位デバイス領域内に半導体チップが固定されたリードフレームをモールド金型にセットして、前記半導体チップを封止レジンにより封止することにより、各単位デバイス領域内にレジン封止体を形成する工程、

ここで、各単位デバイス領域は、以下を含む:

(i)前記半導体チップが固定された、ほぼ矩形のダイ・パッド;

(ii)前記ダイ・パッドの各辺の外部から、前記レジン封止体の底面と、ほぼ同一平面を形成するように延びて、前記レジン封止体の側面から突出した複数のリード;

(iii)前記複数のリードの外端部の近傍を連結するタイ・バー;

(iv)前記複数のリード間を充填し、前記レジン封止体の前記側面から突出するリード間レジン突出部、

更に、前記半導体集積回路装置の製造方法は以下の工程を含む:

(b)前記工程(a)の後、各単位デバイス領域内の前記リード間レジン突出部にレーザ光を照射することによって、前記リード間レジン突出部を除去する工程;

(c)前記工程(b)の後、各単位デバイス領域内の前記複数のリードの露出部表面に半田層を形成する工程;

(d)前記工程(c)の後、各単位デバイス領域内の前記複数のリードの前記外端部を切断することによって、前記複数のリードと前記タイ・バーを分離するとともに、前記レジン封止体を前記リードフレームから切断・分離する工程。

(e)前記工程(b)の後で前記工程(c)の前に、前記複数のリードの表面に対して、前記複数のリードをカソードとして水溶液中で電解処理を実行する工程。

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

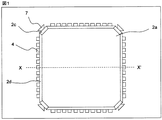

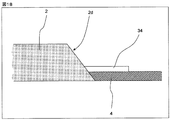

図1は本願発明の一実施の形態の半導体集積回路装置の製造方法により製造された半導体集積回路装置のQFN型パッケージ構造の一例を示すパッケージ上面図である。図2は本願発明の一実施の形態の半導体集積回路装置の製造方法により製造された半導体集積回路装置のパッケージ構造の一例を示すパッケージ下面図である。図3は図1及び図2のX−X’断面に対応するパッケージ断面図である(ほぼ図5のX−X’断面にも対応している)。図28は従来のQFN型パッケージ構造の問題点を説明するためのパッケージ全体斜視図である。これらに基づいて、本願の一実施形態の半導体集積回路装置の製造方法による半導体集積回路装置のパッケージ構造等を説明する。

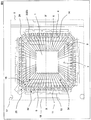

図4は本願発明の一実施の形態の半導体集積回路装置の製造方法に使用するリードフレームの単位デバイス領域の拡大上面図である。図5は本願発明の一実施の形態の半導体集積回路装置の製造方法の工程途中(レジン封止体分離工程前)におけるリードフレームの単位デバイス領域の拡大透視上面図である。図6は本願発明の一実施の形態の半導体集積回路装置の製造方法に使用するリードフレームの単位デバイス領域の9個分にあたる拡大上面図である。図7は本願発明の一実施の形態の半導体集積回路装置の製造方法に使用するリードフレームの全体上面図である。これらに基づいて、本願の一実施形態の半導体集積回路装置の製造方法に使用するリードフレームの構造を説明する。リードフレームの材料は、たとえば錫およびニッケル等を含有する銅を主要な成分とする銅系材料であるが、Zr添加の銅系材料、鉄添加の銅系材料、またはその他の銅系材料でもい。なお、ここでは、リードフレームはエッチングによりパターニングされている。打ち抜きでも可能であるが、エッチングの方が微細加工精度に優れるほか、ハーフ・エッチ等の組み合わせに有効である。

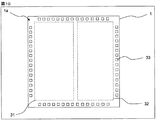

図8は本願発明の一実施の形態の半導体集積回路装置の製造方法の工程途中(ダイ・ボンディング途中)におけるリードフレームの全体上面図である。図9は本願発明の一実施の形態の半導体集積回路装置の製造方法の工程途中(封止工程完了)におけるリードフレームの全体上面図である。図10は本願発明の一実施の形態の半導体集積回路装置の製造方法に使用する半導体チップの一例の平面回路配置図である。図11は本願発明の一実施の形態の半導体集積回路装置の製造方法の主要プロセス・ブロック・フロー図である。図12は本願発明の一実施の形態の半導体集積回路装置の製造方法の一要素プロセス(封止工程)の上面図である(この上面図においては、わかりやすいように、上金型は取り除かれている)。図13は図12のA−A’断面に対応する金型およびデバイスの断面図である。図14は図12のB−B’断面に対応する金型およびデバイスの断面図である。図15は図12のC−C’断面に対応する金型およびデバイスの断面図である。図16は本願発明の一実施の形態の半導体集積回路装置の製造方法の工程途中(封止工程完了)におけるリードフレームの単位デバイス領域の部分拡大上面図である。図17は本願発明の一実施の形態の半導体集積回路装置の製造方法の一要素プロセス(レーザによるリード間レジン突出部除去工程)における処理の様子を説明するためのリードフレーム部分正面図である。図18は図16のD−D’断面に対応するデバイスの断面図である。図19は本願発明の一実施の形態の半導体集積回路装置の製造方法の一要素プロセス(電解残留レジン除去工程)における処理の様子を説明するためのリードフレーム部分正面図である。図20は図19のD−D’断面に対応するデバイスの断面図である。図21は図19のD−D’断面に対応するデバイスの他の断面図である。図22は本願発明の一実施の形態の半導体集積回路装置の製造方法の一要素プロセス(ウォータ・ジェット残留レジン除去工程)における処理の様子を説明するためのリードフレーム部分正面図である。図23は本願発明の一実施の形態の半導体集積回路装置の製造方法の工程途中(ウォータ・ジェット残留レジン除去工程完了)におけるリードフレームの単位デバイス領域の部分拡大上面図である。図24は本願発明の一実施の形態の半導体集積回路装置の製造方法の工程途中(タイ・バー切断前)におけるリードフレームの単位デバイス領域の部分拡大上面図である。図25は本願発明の一実施の形態の半導体集積回路装置の製造方法の一要素プロセス(タイ・バー切断工程)における処理の様子を説明するためのリードフレーム部分正面図である。図26は本願発明の一実施の形態の半導体集積回路装置の製造方法の一要素プロセス(レジン封止体分離工程後)におけるレジン封止体(半導体集積回路装置パッケージ)の部分斜視図である。図27は図26のレジン封止体を配線基板に実装したときの様子を示す配線基板および半導体集積回路装置パッケージの部分斜視図である。これらに基づいて、本願の一実施形態の半導体集積回路装置の製造方法の処理フローを説明する。

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

2 レジン封止体

2b (レジン封止体の)底面

2d (レジン封止体の)側面

3 ダイ・パッド

3d (ダイ・パッドの)辺

4 リード

4d (リードの)外端部

8 単位デバイス領域

11 タイ・バー

12 リードフレーム

41 半田層

51 モールド金型

54 リード間レジン突出部

61 レーザ光

Claims (20)

- 以下の工程を含む半導体集積回路装置の製造方法:

(a)複数の単位デバイス領域を有し、各単位デバイス領域内に半導体チップが固定されたリードフレームをモールド金型にセットして、前記半導体チップを封止レジンにより封止することにより、各単位デバイス領域内にレジン封止体を形成する工程、

ここで、各単位デバイス領域は、以下を含む:

(i)前記半導体チップが固定された、ほぼ矩形のダイ・パッド;

(ii)前記ダイ・パッドの各辺の外部から、前記レジン封止体の底面と、ほぼ同一平面を形成するように延びて、前記レジン封止体の側面から突出した複数のリード;

(iii)前記複数のリードの外端部の近傍を連結するタイ・バー;

(iv)前記複数のリード間を充填し、前記レジン封止体の前記側面から突出するリード間レジン突出部、

更に、前記半導体集積回路装置の製造方法は以下の工程を含む:

(b)前記工程(a)の後、各単位デバイス領域内の前記リード間レジン突出部にレーザ光を照射することによって、前記リード間レジン突出部を除去する工程;

(c)前記工程(b)の後、各単位デバイス領域内の前記複数のリードの露出部表面に半田層を形成する工程;

(d)前記工程(c)の後、各単位デバイス領域内の前記複数のリードの前記外端部を切断することによって、前記複数のリードと前記タイ・バーを分離するとともに、前記レジン封止体を前記リードフレームから切断・分離する工程。 - 前記1項の半導体集積回路装置の製造方法において、前記工程(b)において、前記複数のリードにも前記レーザ光を照射することによって、前記複数のリード上のレジン・バリを除去する。

- 前記2項の半導体集積回路装置の製造方法において、更に、以下の工程を含む:

(e)前記工程(b)の後で前記工程(c)の前に、前記複数のリードの表面に対して、前記複数のリードをカソードとして水溶液中で電解処理を実行する工程。 - 前記3項の半導体集積回路装置の製造方法において、前記工程(e)の後で前記工程(c)の前に、前記複数のリードの表面に対して、ウォータ・ジェット処理を実行する工程。

- 前記4項の半導体集積回路装置の製造方法において、前記工程(a)の封止は、トランスファ・モールドによって実行される。

- 前記1項の半導体集積回路装置の製造方法において、前記レーザ光は、近赤外光である。

- 前記1項の半導体集積回路装置の製造方法において、前記レーザ光は、YAGレーザから得られるものである。

- 前記1項の半導体集積回路装置の製造方法において、前記レーザ光の波長は、1064nmである。

- 前記1項の半導体集積回路装置の製造方法において、前記レジン封止体から突出した全リード数は封止体一個あたり、20本以上、150本以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記レジン封止体から突出した全リード数は封止体一個あたり、40本以上、150本以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記レジン封止体から突出した全リード数は封止体一個あたり、50本以上、150本以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記複数のリードの突出長さは、0.1mm以上、0.5mm以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記複数のリードの突出長さは、0.2mm以上、0.4mm以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記複数のリードのピッチは、0.2mm以上、0.8mm以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記レジン封止体の厚さは、0.3mm以上、1.2mm以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記レジン封止体の幅は、3mm以上、10mm以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記リードフレームの主要部の材質は、銅を主要な成分とする。

- 前記1項の半導体集積回路装置の製造方法において、前記リードフレームの厚さは、厚い部分で0.1mm以上、0.3mm以下である。

- 前記1項の半導体集積回路装置の製造方法において、前記半田層は鉛フリーである。

- 前記1項の半導体集積回路装置の製造方法において、前記封止レジンは、ハロゲン・フリーである。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008164388A JP5334239B2 (ja) | 2008-06-24 | 2008-06-24 | 半導体装置の製造方法 |

| US12/432,075 US8026130B2 (en) | 2008-06-24 | 2009-04-29 | Method for manufacturing a semiconductor integrated circuit device |

| US13/225,788 US8338927B2 (en) | 2008-06-24 | 2011-09-06 | Semiconductor device with the leads projected from sealing body |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008164388A JP5334239B2 (ja) | 2008-06-24 | 2008-06-24 | 半導体装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012184744A Division JP5519745B2 (ja) | 2012-08-24 | 2012-08-24 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010010187A true JP2010010187A (ja) | 2010-01-14 |

| JP5334239B2 JP5334239B2 (ja) | 2013-11-06 |

Family

ID=41431667

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008164388A Active JP5334239B2 (ja) | 2008-06-24 | 2008-06-24 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US8026130B2 (ja) |

| JP (1) | JP5334239B2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012094598A (ja) * | 2010-10-25 | 2012-05-17 | Mitsui High Tec Inc | 半導体装置の樹脂バリ除去方法 |

| JP2014022399A (ja) * | 2012-07-12 | 2014-02-03 | Mitsui High Tec Inc | リードフレームおよびリードフレームの製造方法 |

| JP2014165340A (ja) * | 2013-02-25 | 2014-09-08 | Seiko Instruments Inc | 半導体装置の製造方法 |

| CN110265310A (zh) * | 2018-03-12 | 2019-09-20 | 台湾积体电路制造股份有限公司 | 封装体及其形成方法 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8673687B1 (en) * | 2009-05-06 | 2014-03-18 | Marvell International Ltd. | Etched hybrid die package |

| WO2011142006A1 (ja) | 2010-05-12 | 2011-11-17 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US8716845B2 (en) * | 2011-04-15 | 2014-05-06 | Texas Instruments Incorporated | Lead frame strip for reduced mold sticking during degating |

| US8525312B2 (en) * | 2011-08-12 | 2013-09-03 | Tessera, Inc. | Area array quad flat no-lead (QFN) package |

| US8587099B1 (en) | 2012-05-02 | 2013-11-19 | Texas Instruments Incorporated | Leadframe having selective planishing |

| TWI500090B (zh) * | 2012-11-13 | 2015-09-11 | 矽品精密工業股份有限公司 | 半導體封裝件之製法 |

| US9449890B1 (en) * | 2013-05-10 | 2016-09-20 | Amkor Technology, Inc. | Methods for temporary bussing of semiconductor package substrates |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07142664A (ja) * | 1993-11-18 | 1995-06-02 | Nec Corp | 樹脂封止半導体装置の製造方法 |

| JP2000299400A (ja) * | 1999-04-14 | 2000-10-24 | Sony Corp | ノンリード・フラットパッケージ型半導体装置 |

| JP2001093921A (ja) * | 1999-09-22 | 2001-04-06 | Toshiba Corp | 半導体装置の製造方法 |

| JP2004247612A (ja) * | 2003-02-14 | 2004-09-02 | Sanyo Electric Co Ltd | 半導体装置およびその製造方法 |

| JP2005209999A (ja) * | 2004-01-26 | 2005-08-04 | Ricoh Co Ltd | 半導体装置及びリードフレーム、並びに半導体装置の製造方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05315381A (ja) | 1992-05-07 | 1993-11-26 | Nec Corp | 半導体製造装置 |

| US5661086A (en) * | 1995-03-28 | 1997-08-26 | Mitsui High-Tec, Inc. | Process for manufacturing a plurality of strip lead frame semiconductor devices |

| US6281568B1 (en) | 1998-10-21 | 2001-08-28 | Amkor Technology, Inc. | Plastic integrated circuit device package and leadframe having partially undercut leads and die pad |

| MY133357A (en) * | 1999-06-30 | 2007-11-30 | Hitachi Ltd | A semiconductor device and a method of manufacturing the same |

| JP2001102510A (ja) | 1999-09-28 | 2001-04-13 | Mitsubishi Electric Corp | 半導体の組立方法 |

| US6605865B2 (en) * | 2001-03-19 | 2003-08-12 | Amkor Technology, Inc. | Semiconductor package with optimized leadframe bonding strength |

| US7122884B2 (en) * | 2002-04-16 | 2006-10-17 | Fairchild Semiconductor Corporation | Robust leaded molded packages and methods for forming the same |

| JP2004014823A (ja) * | 2002-06-07 | 2004-01-15 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| KR100538485B1 (ko) * | 2003-11-12 | 2005-12-23 | 삼성전자주식회사 | 리드 프레임을 이용한 범프 칩 캐리어 패키지의 제조 방법 |

| JP4674813B2 (ja) | 2006-02-08 | 2011-04-20 | セイコーインスツル株式会社 | 半導体デバイスの製造方法 |

| JP2008117875A (ja) * | 2006-11-02 | 2008-05-22 | Renesas Technology Corp | 半導体装置および半導体装置の製造方法 |

-

2008

- 2008-06-24 JP JP2008164388A patent/JP5334239B2/ja active Active

-

2009

- 2009-04-29 US US12/432,075 patent/US8026130B2/en active Active

-

2011

- 2011-09-06 US US13/225,788 patent/US8338927B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07142664A (ja) * | 1993-11-18 | 1995-06-02 | Nec Corp | 樹脂封止半導体装置の製造方法 |

| JP2000299400A (ja) * | 1999-04-14 | 2000-10-24 | Sony Corp | ノンリード・フラットパッケージ型半導体装置 |

| JP2001093921A (ja) * | 1999-09-22 | 2001-04-06 | Toshiba Corp | 半導体装置の製造方法 |

| JP2004247612A (ja) * | 2003-02-14 | 2004-09-02 | Sanyo Electric Co Ltd | 半導体装置およびその製造方法 |

| JP2005209999A (ja) * | 2004-01-26 | 2005-08-04 | Ricoh Co Ltd | 半導体装置及びリードフレーム、並びに半導体装置の製造方法 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012094598A (ja) * | 2010-10-25 | 2012-05-17 | Mitsui High Tec Inc | 半導体装置の樹脂バリ除去方法 |

| JP2014022399A (ja) * | 2012-07-12 | 2014-02-03 | Mitsui High Tec Inc | リードフレームおよびリードフレームの製造方法 |

| JP2014165340A (ja) * | 2013-02-25 | 2014-09-08 | Seiko Instruments Inc | 半導体装置の製造方法 |

| CN110265310A (zh) * | 2018-03-12 | 2019-09-20 | 台湾积体电路制造股份有限公司 | 封装体及其形成方法 |

| CN110265310B (zh) * | 2018-03-12 | 2022-11-15 | 台湾积体电路制造股份有限公司 | 封装体及其形成方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8026130B2 (en) | 2011-09-27 |

| US20090317948A1 (en) | 2009-12-24 |

| US8338927B2 (en) | 2012-12-25 |

| JP5334239B2 (ja) | 2013-11-06 |

| US20110316137A1 (en) | 2011-12-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5334239B2 (ja) | 半導体装置の製造方法 | |

| JP5689514B2 (ja) | 半導体装置の製造方法 | |

| JP5380244B2 (ja) | 半導体装置の製造方法 | |

| JP5634033B2 (ja) | 樹脂封止型半導体装置とその製造方法 | |

| US8742559B2 (en) | Manufacturing method of semiconductor device, and semiconductor device | |

| CN101587869B (zh) | 可颠倒无引线封装及其堆叠和制造方法 | |

| US8017447B1 (en) | Laser process for side plating of terminals | |

| JP5319571B2 (ja) | 半導体装置の製造方法 | |

| US8597989B2 (en) | Manufacturing method of semiconductor device | |

| CN116601749A (zh) | 形成具有焊料增强引线框端子的表面安装式集成电路封装的方法 | |

| JP4086202B2 (ja) | 半導体装置の製造方法 | |

| JP5507344B2 (ja) | 半導体装置の製造方法 | |

| JP5894209B2 (ja) | 半導体装置 | |

| JP5519745B2 (ja) | 半導体装置 | |

| JP2014187308A (ja) | 半導体装置の製造方法 | |

| CN115588657A (zh) | 引线框架、半导体装置及引线框架的制造方法 | |

| JP6143726B2 (ja) | 樹脂封止型半導体装置とその製造方法、リードフレーム | |

| KR20020093250A (ko) | 리드 노출형 리드 프레임 및 그를 이용한 리드 노출형반도체 패키지 | |

| JP2008252005A (ja) | バリ取り方法および半導体装置の製造方法 | |

| JP5816659B2 (ja) | 半導体装置の製造方法 | |

| JP4335203B2 (ja) | 半導体装置の製造方法 | |

| JP2017108191A (ja) | 半導体装置 | |

| JP2014236039A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110610 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120625 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120628 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120824 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130523 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130702 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130725 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130726 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5334239 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |