以下、本発明の実施の形態について、図面を参照して詳細に説明する。

図1は、本発明の一実施の形態に係る液晶表示装置(液晶表示装置1)の全体構成を表すものである。この液晶表示装置1は、液晶表示パネル2と、バックライト部3と、画像処理部41と、マルチ画素変換部43と、リファレンス電圧生成部45と、データドライバ51と、ゲートドライバ52と、タイミング制御部61と、バックライト制御部63とを備えている。

バックライト部3は、液晶表示パネル2に対して光を照射する光源であり、例えばCCFL(Cold Cathode Fluorescent Lamp:冷陰極蛍光ランプ)やLED(Light Emitting Diode:発光ダイオード)などを含んで構成される。

液晶表示パネル2は、後述するゲートドライバ52から供給される駆動信号に従って、データドライバ51から供給される駆動電圧に基づいてバックライト部3から発せられる光を変調することにより、映像信号Dinに基づく映像表示を行うものであり、全体としてマトリクス状に並んで配置された複数の画素20を含んで構成されている。各画素20は、R(Red:赤),G(Green:緑)またはB(Blue:青)に対応する画素(図示しないR,G,B用のカラーフィルタが設けられている画素であり、R,G,Bの色の表示光を射出する画素)により構成されている。また、各画素20内には、2つのサブ画素(後述するサブ画素20A,20B)を含む画素回路が形成されている。なお、この画素回路の詳細構成については、後述する(図2,図3)。

画像処理部41は、外部からの映像信号Dinに対して所定の画像処理を施すことにより、RGB信号である映像信号D1を生成するものである。

マルチ画素変換部43は、後述するルックアップテーブル(LUT)を用いることにより、画像処理部41から供給される映像信号D1を、各サブ画素用の2つの映像信号D2a,D2bに変換する(マルチ画素変換を行う)と共に、これら映像信号D2a,D2bをタイミング制御部61へ供給するものである。このLUTは、映像信号D1の輝度レベルの階調と、各サブ画素に対応する映像信号の輝度レベルの階調とを、R,G,Bに対応する画素の映像信号ごとに対応付けてなるものである。なお、LUTの詳細については、後述する(図4)。

リファレンス電圧生成部45は、データドライバ51に対し、後述するD/A(デジタル/アナログ)変換を施す際に用いるリファレンス電圧Vrefを供給するものである。具体的には、このリファレンス電圧Vrefは、黒電圧(後述する0階調の輝度レベルの電圧)から白電圧(例えば、後述する255階調の輝度レベルの電圧)までの複数の基準電圧により構成されている。また、本実施の形態では、このリファレンス電圧Vrefは、R,G,Bに対応する画素間で共通のものとなっている。なお、このリファレンス電圧生成部45は、例えば複数の抵抗器が直列接続された抵抗ツリー構造などにより構成される。

ゲートドライバ52は、タイミング制御部61によるタイミング制御に従って、液晶表示パネル2内の各画素20を図示しない走査線(後述するゲート線G)に沿って線順次駆動するものである。

データドライバ51は、液晶表示パネル2の各画素20(より詳細には、各画素20内の各サブ画素)へそれぞれ、タイミング制御部61から供給される映像信号D2a,D2bに基づく駆動電圧を供給するものである。具体的には、このデータドライバ51は、映像信号D2a,D2bに対し、リファレンス電圧生成部45から供給されるリファレンス電圧Vrefを用いてそれぞれD/A変換を施すことにより、アナログ信号である映像信号(上記駆動電圧)を生成し、各画素20へ出力するようになっている。

バックライト駆動部62は、バックライト部3の点灯動作を制御するものである。タイミング制御部61は、ゲートドライバ52およびデータドライバ51の駆動タイミングを制御すると共に、映像信号D2a,D2bをデータドライバ51へ供給するものである。

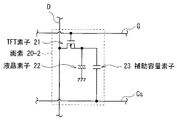

次に、図2および図3を参照して、各画素20に形成された画素回路の構成について詳細に説明する。図2は、この画素20内の画素回路の回路構成例を表したものである。また、図3は、この画素回路内の液晶素子における画素電極の平面構成例を表したものである。

画素20は、2つのサブ画素20A,20Bにより構成され、マルチ画素構造となっている。サブ画素20Aは、主容量素子である液晶素子22Aと、補助容量素子23Aと、薄膜トランジスタ(TFT:Thin Film Transistor)素子21Aとを有している。サブ画素20Bも同様に、主容量素子である液晶素子22Bと、補助容量素子23Bと、TFT素子21Bとを有している。また、画素20には、駆動対象の画素を線順次で選択するための1本のゲート線Gと、駆動対象の画素に対してサブ画素20A,20Bごとにそれぞれ駆動電圧(データドライバ51から供給される駆動電圧)を供給する2本のデータDA,DBと、補助容量素子23A,23Bの対向電極側に対して所定の基準電位を供給するためのバスラインである1本の補助容量線Csとが接続されている。

液晶素子22Aは、データ線DAからTFT素子21Aを介して一端に供給される駆動電圧に応じて、表示のための動作を行う(表示光を射出する)表示要素として機能している。また、液晶素子22Bも同様に、データ線DBからTFT素子21Bを介して一端に供給される駆動電圧に応じて、表示のための動作を行う(表示光を射出する)表示要素として機能している。これら液晶素子22A,22Bは、VAモードの液晶により構成された液晶層(図示せず)と、この液晶層を挟む一対の電極(図示せず)とを含んで構成されている。これら一対の電極のうちの一方(一端)側(図2中の符号P1A,P1B側)は、TFT素子21A,21Bのソースおよび補助容量素子23A,23Bの一端に接続され、他方(他端)側は接地されている。また、一対の電極のうちの一方側(図2中の符号P1A,P1B側)の電極は、例えば図3に示したような平面形状の画素電極220となっており、サブ画素20A側の画素電極と、サブ画素20B(20B−1,20B−2からなる)側の画素電極とから構成されている。

補助容量素子23A,23Bは、液晶素子22A,22Bの蓄積電荷を安定化させるための容量素子である。補助容量素子23Aの一端(一方の電極)は、液晶素子22Aの一端およびTFT素子21Aのソースに接続され、他端(対向電極)は補助容量線Csに接続されている。また、補助容量素子23Bの一端(一方の電極)は、液晶素子22Bの一端およびTFT素子21Bのソースに接続され、他端(対向電極)は補助容量線Csに接続されている。

TFT素子21Aは、MOS−FET(Metal Oxide Semiconductor−Field Effect Transistor)により構成されており、ゲートがゲート線Gに接続され、ソースが液晶素子22Aの一端および補助容量素子23Aの一端に接続され、ドレインがデータ線DAに接続されている。このTFT素子21Aは、液晶素子22Aの一端および補助容量素子23Aの一端に対し、サブ画素20A用の駆動電圧(映像信号D2aに基づく駆動電圧)を供給するためのスイッチング素子として機能している。具体的には、ゲートドライバ52からゲート線Gを介して供給される選択信号に応じて、データ線DAと液晶素子22Aおよび補助容量素子23Aの一端同士との間を選択的に導通させるようになっている。

TFT素子21Bも同様にMOS−FETにより構成されており、ゲートがゲート線Gに接続され、ソースが液晶素子22Bの一端および補助容量素子23Bの一端に接続され、ドレインがデータ線DBに接続されている。このTFT素子21Bは、液晶素子22Bの一端および補助容量素子23Bの一端に対し、サブ画素20B用の駆動電圧(映像信号D2bに基づく駆動電圧)を供給するためのスイッチング素子として機能している。具体的には、ゲートドライバ52からゲート線Gを介して供給される選択信号に応じて、データ線DBと液晶素子22Bおよび補助容量素子23Bの一端同士との間を選択的に導通させるようになっている。

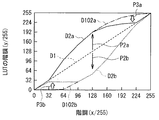

次に、図4を参照して、マルチ画素変換部43において用いられるLUTについて詳細に説明する。なお、以下説明する特性図においては、一例として、輝度レベルの階調が、0/255階調(黒表示状態)から255/255階調(白表示状態)までに設定されているものとする。

このLUTは、例えば図4中の矢印P2a,P2bで示したように、マルチ画素変換部43に供給される映像信号D1の輝度レベルの階調を、サブ画素20A用の映像信号D2aの輝度レベルの階調と、サブ画素20B用の映像信号D2bの輝度レベルの階調とに分割するためのものである。すなわち、映像信号D1に基づき、各画素20に対する表示駆動を、サブ画素20A,20Bごとに空間的に2つに分割して分割駆動動作を行うために用いられるものである。言い換えると、このときの分割駆動動作は、液晶素子22Aに対して印加される液晶印加電圧が映像信号D1に対応する入力印加電圧以上の高電圧側となるように分割駆動動作を行う第1の分割駆動動作(サブ画素20Aに対する分割駆動動作)と、液晶素子22Bに対して印加される液晶印加電圧が上記入力印加電圧以下の低電圧側となるように分割駆動動作を行う第2の分割駆動動作(サブ画素20Bに対する分割駆動動作)と、により構成されている。

また、このLUTでは、サブ画素20Aに対する分割駆動動作の際に、例えば図4中の矢印P2aで示したように、少なくとも中間輝度領域において、液晶素子22Aへの液晶印加電圧が、映像信号D1に対応する入力印加電圧よりも高電圧側となっている。そして、例えば図4中の矢印P3aで示したように、高輝度領域において、液晶素子22Aへの液晶印加電圧が、映像信号D1に対応する入力印加電圧以上の高電圧側となりつつ、中間輝度領域と比べて低電圧傾向となっている。具体的には、このような高輝度領域における液晶素子22Aへの液晶印加電圧は、映像信号D1に対応する入力印加電圧以上かつ、「液晶の方位角ぶれ」が発生する電圧以下に設定されるようになっている。

さらに、このLUTでは、サブ画素20Bに対する分割駆動動作の際に、例えば図4中の矢印P2bで示したように、少なくとも中間輝度領域において、液晶素子22Bへの液晶印加電圧が、映像信号D1に対応する入力印加電圧よりも低電圧側となっている。そして、例えば図4中の矢印P3bで示したように、低輝度領域において、液晶素子22Bへの液晶印加電圧が、映像信号D1に対応する入力印加電圧以下の低電圧側となりつつ、中間輝度領域と比べて高電圧傾向となっている。具体的には、低輝度領域のうちの映像信号D1における最低輝度階調(0階調)以外では、液晶素子22Bへの液晶印加電圧が、この最低輝度階調に対応する最低電圧よりも高電圧側となるように設定されている(映像信号D1における0階調以外では、映像信号D2bにおいて0階調とならないように設定されている)。

ここで、マルチ画素変換部43、タイミング制御部61、リファレンス電圧生成部45、データドライバ51およびゲートドライバ52が、本発明における「駆動部」の一具体例に対応する。また、図4に示したLUTが、本発明における「第1のLUT」の一具体例に対応する。また、サブ画素20Aが本発明における「第1のサブ画素群」の一具体例に対応し、サブ画素20Bが本発明における「第2のサブ画素群」の一具体例に対応する。

次に、本実施の形態の液晶表示装置1の動作について説明する。

まず、図1〜図4を参照して、液晶表示装置1の基本動作について説明する。

この液晶表示装置1では、図1に示したように、外部から供給された映像信号Dinが画像処理部41により画像処理され、各画素20用の映像信号D1が生成される。この映像信号D1は、マルチ画素変換部43へ供給される。マルチ画素変換部43では、上述したLUTを用いることにより、供給された映像信号D1が、各サブ画素20A,20B用の2つの映像信号D2a,D2bに変換される(マルチ画素変換)。これら2つの映像信号D2a,D2bはそれぞれ、タイミング制御部61を介してデータドライバ51へ供給される。データドライバ51では、リファレンス電圧生成部45から供給されるリファレンス電圧Vrefを用いて映像信号D2a,D2bに対するD/A変換が施され、アナログ信号である2つの映像信号が生成される。そしてこれら2つの映像信号に基づき、ゲートドライバ52およびデータドライバ51から出力される各画素20内のサブ画素20A,20Bへの駆動電圧によって、画素20ごとに線順次表示駆動動作がなされる。

具体的には、図2および図3に示したように、ゲートドライバ52からゲート線Gを介して供給される選択信号に応じて、TFT素子21A,21Bのオン・オフが切り替えられ、データ線DA,DBと液晶素子22A,22Bおよび補助容量素子23A,23Bとの間が選択的に導通されることにより、データドライバ51から供給される2つの映像信号に基づく駆動電圧が液晶素子22A,22Bおよび補助容量素子23A,23Bへと供給され、表示駆動動作がなされる。

すると、データ線DA,DBと液晶素子22A,22Bおよび補助容量素子23A,23Bとの間が導通された画素20では、バックライト部30からの照明光が液晶表示パネル2において変調され、表示光として出力される。これにより、映像信号Dinに基づく映像表示が、液晶表示装置1において行われる。

次に、図1〜図4に加えて図5〜図7を参照して、本発明の液晶表示装置の駆動動作の特徴的部分について、比較例と比較しつつ詳細に説明する。ここで、図5〜図7は、比較例に係る従来の液晶表示装置におけるLUTと、そのLUTを用いた場合の問題点とについて説明するためのものである。

まず、本実施の形態の液晶表示装置1では、図4に示したLUTを用いることにより、VAモードの液晶を用いた各画素20の液晶素子22A,22Bに対する表示駆動における動作を行う際に、映像信号D1に基づき、各画素20に対する表示駆動が空間的に2つに分割されて分割駆動動作がなされる(図4中の矢印P2a,P2b参照)。具体的には、各画素20が2つのサブ画素20A,20Bにより構成されると共に、映像信号D1に対してマルチ画素変換がなされた映像信号D3a,D3b(図示せず;データドライバ51から供給されるアナログ信号からなる2つの映像信号)に基づき、各画素20に対する表示駆動をサブ画素20A,20Bごとに空間的に2つに分割して分割駆動動作がなされる。したがって、そのような分割駆動動作を行わない場合と比べ、表示画面を斜め方向(例えば、45°方向)から見た場合のガンマ特性(映像信号D1の輝度レベルの階調と、輝度との関係を示す特性)の変動(表示画面を正面方向から見た場合からの変動)が、分散される。これにより、例えば図14中の輝度特性Ym(45°)のように、マルチ画素構造による分割駆動動作を行っていない場合(例えば、図14中の輝度特性Ys(45°))と比べ、輝度の視野角特性が向上する。

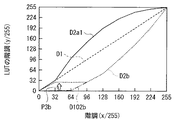

一方、比較例に係る液晶表示装置においても、同様にマルチ画素構造による分割駆動動作を行っているため(例えば、図5中の矢印P102a,P102b参照)、マルチ画素構造による分割駆動動作を行っていない場合と比べ、輝度の視野角特性が向上している。ただし、この比較例では、図4に示した本実施の形態のLUTの代わりに、図5に示したようなLUTを用いることにより、マルチ画素構造による分割駆動動作がなされている。具体的には、このLUTでは、サブ画素20Aに対する分割駆動動作(図5中の映像信号D102aに対応)における動作を行う際に、高輝度領域において、図4中の矢印P3aで示したような低電圧傾向となっていない。また、サブ画素20Bに対する分割駆動動作(図5中の映像信号D102bに対応)における動作を行う際にも、低輝度領域において、図4中の矢印P3bで示したような高電圧傾向となっていない。

ここで、このようなLUTを用いている比較例に係る液晶表示装置では、上記のように、サブ画素20Aに対する分割駆動動作の際に高輝度領域において低電圧傾向となっていないと共に、サブ画素20Bに対する分割駆動動作の際に低輝度領域において高電圧傾向となっていないため、以下のような現象が生じやすくなってしまう。そしてその結果、動画表示特性が低下し、表示画質が劣化してしまうことになる。

具体的には、まず、例えば図6中の符号P103a,P103bで示したように、サブ画素20A内の液晶素子22Aへ印加する電圧(液晶印加電圧)において、低電圧(例えば、0階調/255階調)から高電圧(例えば、255階調/255階調)へ遷移する際に、所望の電圧値(輝度値)まで輝度が上がらず、液晶の応答時間が悪化してしまいやすくなる。これは、サブ画素構造のようなハーフトーン技術を用いた場合、サブ画素20Aには、ハーフトーン技術を用いない場合と比べてより低い階調から高電圧を印加することとなるため、「液晶の方位角ぶれ」による応答時間の悪化が、より多くの階調において発生することによるものである。

また、例えば図5中の映像信号D102bのように、サブ画素20B内の液晶素子22Bへ印加する電圧(液晶印加電圧)では、オーバードライブ(OD)駆動を行う際に、ハーフトーン技術を用いない場合と比べて0階調を用いる場合が増えるため、液晶印加電圧を、低電圧から高電圧へと急激に上昇させなければならなくなる。その結果、オーバードライブ駆動によって液晶の応答速度が改善されるものの、例えば図7中の符号P104で示したように、オーバードライブ駆動終了後に本来の階調の電圧が印加された際に、「ゆり戻し現象」が生じやすくなってしまう。

これに対し、本実施の形態の液晶表示装置1では、図4に示したLUTにおいて、サブ画素20Aに対する分割駆動動作の際に、図4中の矢印P3aで示したように、高輝度領域において、液晶素子22Aへの液晶印加電圧が、映像信号D1に対応する入力印加電圧以上の高電圧側となりつつ、中間輝度領域と比べて低電圧傾向となっている。具体的には、このような高輝度領域における液晶素子22Aへの液晶印加電圧は、映像信号D1に対応する入力印加電圧以上かつ、「液晶の方位角ぶれ」が発生する電圧以下に設定されている。これにより、高輝度領域においてそのような低電圧傾向となっていない比較例の分割駆動動作と比べ、液晶印加電圧において低電圧から高電圧へ遷移する際の急激な上昇が抑えられる。よって、「液晶の方位角ぶれ」が発生する階調数が低減(例えば、32階調から6階調へと低減)することとなる。なお、このとき、サブ画素20Bに対する分割駆動動作の際に、映像信号D1の場合と比べてガンマ特性が変化しないよう、高輝度領域において逆に高電圧傾向となっている。

また、サブ画素20Bに対する分割駆動動作の際に、例えば図4中の矢印P3bで示したように、低輝度領域において、液晶素子22Bへの液晶印加電圧が、映像信号D1に対応する入力印加電圧以下の低電圧側となりつつ、中間輝度領域と比べて高電圧傾向となっている。具体的には、低輝度領域のうちの映像信号D1における最低輝度階調(0階調)以外では、液晶素子22Bへの液晶印加電圧が、この最低輝度階調に対応する最低電圧よりも高電圧側となるように設定されている(映像信号D1における0階調以外では、映像信号D2bにおいて0階調とならないように設定されている)。これにより、低輝度領域においてそのような高電圧傾向となっていない比較例の分割駆動動作と比べ、オーバードライブ駆動を行う際に、液晶印加圧における低電圧から高電圧への急激な上昇が抑えられる。よって、「ゆり戻し現象」が発生する階調数が低減(例えば、64階調から20階調へと低減)することとなる。なお、このときも、サブ画素20Aに対する分割駆動動作の際に、映像信号D1の場合と比べてガンマ特性が変化しないよう、低輝度領域において逆に低電圧傾向となっている。

以上のように本実施の形態では、VAモードの液晶を用いた各画素20の液晶素子22A,22Bに対する表示駆動における動作を行う際に、各画素20に対する表示駆動を空間的に2つ分割して分割駆動動作を行うようにしたので、そのような分割駆動動作を行わない場合と比べ、表示画面を斜め方向から見た場合のガンマ特性の変動を分散させることができ、輝度の視野角特性を向上させることができる。また、サブ画素20Aに対する分割駆動動作の際に、高輝度領域において、液晶素子22Aへの液晶印加電圧が、映像信号D1に対応する入力印加電圧以上の高電圧側となりつつ中間輝度領域と比べて低電圧傾向となるようにしたので、液晶印加電圧において低電圧から高電圧へ遷移する際の急激な上昇を抑えることができ、従来の分割駆動動作の場合と比べて液晶の方位角ぶれを発生しにくくすることができる。さらに、サブ画素20Bに対する分割駆動動作の際に、低輝度領域において、液晶素子22Bへの液晶印加電圧が、映像信号D1に対応する入力印加電圧以下の低電圧側となりつつ中間輝度領域と比べて高電圧傾向となるようにしたので、オーバードライブ駆動を行う際に、液晶印加圧における低電圧から高電圧への急激な上昇が抑えることができ、従来の分割駆動動作の場合と比べてゆり戻し現象を発生しにくくすることができる。よって、VAモードの液晶を用いた液晶表示装置において、輝度の視野角特性を向上させつつ、従来よりも表示画質を向上させることが可能となる。

具体的には、各画素20を2つのサブ画素20A,20Bにより構成すると共に、映像信号D1に対してマルチ画素変換がなされた映像信号D3a,D3bに基づき、各画素20に対する表示駆動をサブ画素20A,20Bごとに空間的に2つに分割して分割駆動動作を行うようにしたので、上記効果を得ることが可能となる。

また、映像信号D1と各サブ画素20A,20Bに対応する映像信号D3a,D3bとを対応付けてなるLUTを用いることにより、各画素20に対する表示駆動を、サブ画素20A,20Bごとに空間的に2つに分割して分割駆動動作を行うことが可能となる。

さらに、サブ画素20Bに対する分割駆動動作の際に、低輝度領域のうちの映像信号D1における最低輝度階調(0階調)以外では、液晶素子22Bへの液晶印加電圧が、この最低輝度階調に対応する最低電圧よりも高電圧側となるように設定(映像信号D1における0階調以外では、映像信号D2bにおいて0階調とならないように設定)したので、オーバードライブ駆動を行う際に、ゆり戻し現象をより発生しにくくすることができる。

以上、実施の形態を挙げて本発明を説明したが、本発明はこの実施の形態に限定されるものではなく、種々の変形が可能である。

例えば、上記実施の形態では、例えば図4に示したLUTのように、「液晶の方位角ぶれ」および「ゆり戻し現象」の2つの現象を発生しにくくするため、図中の矢印P3a,P3bで示した2つの対策を行った場合について説明したが、これら2つの対策のうちの一方のみを行うようにしてもよい。具体的には、例えば図8に示したLUTのように、「液晶の方位角ぶれ」の現象のみを発生しにくくするため、図中の矢印P3aで示した1つの対策を行うようにしてもよい。また、例えば図9に示したLUTのように、「ゆり戻し現象」のみを発生しにくくするため、図中の矢印P3bで示した1つの対策を行うようにしてもよい。これらのように構成した場合でも、輝度の視野角特性を向上させつつ、従来と比べてある程度表示画質を向上させることが可能となる。

また、上記実施の形態では、図2に示した画素20およびサブ画素20A,20Bのように、各画素20において、1本のゲート線Gおよび2本のデータ線DA,DBが接続されている場合のマルチ画素構造について説明したが、例えば図10に示した画素20−1およびサブ画素20A−1,20B−1のように、各画素20−1において、2本のゲート線GA,GBおよび1本のデータ線Dが接続されているようなマルチ画素構造においても、本発明を適用することが可能である。なお、このような画素20−1の場合、例えば、表示駆動の単位フレーム(1フレーム期間)を時間軸に沿って2分割して2つのサブフレーム期間を設けると共に、各サブフレーム期間内でゲート線GA,GBから供給される選択信号およびデータドライバDから供給される駆動電圧に従って、各サブ画素20A,20Bが駆動されることになる。

また、上記実施の形態では、図1および図4に示したように、映像信号D1と各サブ画素20A,20Bに対応する映像信号D3a,D3bとを対応付けてなるLUTを用いることにより、各画素20に対する表示駆動をサブ画素20A,20Bごとに空間的に2つに分割して分割駆動動作を行う場合について説明したが、他の手法を用いるようにしてもよい。具体的には、例えば図11に示した液晶表示装置1Aのように、画像処理部41から供給される映像信号D1をデータドライバ51において映像信号D3a,D3b(図示せず)へD/A変換する際に用いるリファレンス電圧が、サブ画素20A,20Bごとに互いに異なる(サブ画素20Aに対応するリファレンス電圧VrefAと、サブ画素20Bに対応するリファレンス電圧VrefBとが、互いに異なっている)ように設定することにより、上記実施の形態と同様に、各画素20に対する表示駆動をサブ画素20A,20Bごとに空間的に2つに分割して分割駆動動作を行うようにしてもよい。このように構成した場合も、上記実施の形態と同様の効果を得ることが可能である。なお、この場合においても、図10に示したようなマルチ画素構造を適用することが可能である。

また、上記実施の形態では、各画素20を2つのサブ画素20A,20Bにより構成すると共に、各画素20に対する表示駆動をサブ画素20A,20Bごとに空間的に2つに分割して分割駆動動作を行う場合について説明したが、他の手法を用いるようにしてもよい。具体的には、例えば図12に示したような通常のシングル構造の画素20−2(1つの液晶素子22、1つの補助容量素子23および1つのTFT素子21を有すると共に、1本のゲート線Gおよび1本のデータ線Dが接続されている)において、例えば図13に示したように、表示駆動の単位フレーム(1フレーム期間)を2つのサブフレーム期間SFA,SFBに時間的に分割すると共に、所望の輝度を高輝度のサブフレームSFAと低輝度のサブフレームSFBとを用いて分割して表現することによって、マルチ画素構造の場合と同様にハーフトーンの効果を得るようにしてもよい。より具体的には、映像信号D1に基づき、各画素20−2に対する表示駆動を、サブフレーム期間SFA,SFBごとに時間的に2つに分割して分割駆動動作を行うようにしてもよい。言い換えると、このときの分割駆動動作は、液晶素子22に対して印加される液晶印加電圧が映像信号D1に対応する入力印加電圧以上の高電圧側となるように分割駆動動作を行う第1の分割駆動動作(サブフレーム期間SFAに対する分割駆動動作)と、液晶素子22に対して印加される液晶印加電圧が上記入力印加電圧以下の低電圧側となるように分割駆動動作を行う第2の分割駆動動作(サブフレーム期間SFBに対する分割駆動動作)と、により構成されている。また、このように、各画素20−2に対する表示駆動をサブフレーム期間SFA,SFBごとに時間的に2つに分割して分割駆動動作を行う手法としては、図4に示したLUTと同様に、映像信号D1と各サブフレーム期間SFA,SFBに対応する映像信号とを対応付けてなるLUT(第2のLUT)を用いるようにしてもよい。あるいは、図11に示した液晶表示装置1Aの場合と同様に、映像信号D1をD/A変換する際に用いるリファレンス電圧が、サブフレーム期間SFA,SFBごとに互いに異なるように設定するようにしてもよい。これらのように構成した場合も、上記実施の形態と同様の効果を得ることが可能である。

また、上記実施の形態では、画素電極220の平面形状を具体的に挙げて説明したが、画素電極の平面形状は、図3に示したものには限られない。

さらに、各画素20内のサブ画素の数および1フレーム期間内のサブフレーム期間の数は、これまで説明したような2つの場合には限られず、3つ以上であってもよい。

1,1A…液晶表示装置、2…液晶表示パネル、20,20−1,20−2…画素、20A,20A−1,20B,20B−1…サブ画素、21,21A,21B…TFT素子、22,22A,22B…液晶素子、220…画素電極、23,23A,23B…補助容量素子、3…バックライト部、41…画像処理部、43…マルチ画素変換部、45,45A…リファレンス電圧生成部、51…データドライバ、52…ゲートドライバ、61…タイミング制御部、62…バックライト駆動部、Din…映像信号、D1,D2a,D2b…映像信号、Vref,VrefA,VrefB…リファレンス電圧、G,GA,GB…ゲート線、D,DA,DB…データ線、Cs…補助容量線、SFA,SFB…サブフレーム期間。