JP2010004395A - 平衡不平衡変換器及び増幅回路モジュール - Google Patents

平衡不平衡変換器及び増幅回路モジュール Download PDFInfo

- Publication number

- JP2010004395A JP2010004395A JP2008162323A JP2008162323A JP2010004395A JP 2010004395 A JP2010004395 A JP 2010004395A JP 2008162323 A JP2008162323 A JP 2008162323A JP 2008162323 A JP2008162323 A JP 2008162323A JP 2010004395 A JP2010004395 A JP 2010004395A

- Authority

- JP

- Japan

- Prior art keywords

- terminal

- balanced

- unbalanced

- power supply

- degree phase

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 230000003321 amplification Effects 0.000 title claims abstract description 4

- 238000003199 nucleic acid amplification method Methods 0.000 title claims abstract description 4

- 239000003990 capacitor Substances 0.000 claims abstract description 60

- 239000000758 substrate Substances 0.000 claims description 67

- 238000010030 laminating Methods 0.000 claims description 13

- 239000003989 dielectric material Substances 0.000 claims description 6

- 230000015572 biosynthetic process Effects 0.000 claims description 3

- 238000010586 diagram Methods 0.000 description 13

- 230000008878 coupling Effects 0.000 description 5

- 238000010168 coupling process Methods 0.000 description 5

- 238000005859 coupling reaction Methods 0.000 description 5

- 238000002955 isolation Methods 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 3

- 241001125929 Trisopterus luscus Species 0.000 description 2

- 230000002238 attenuated effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- 238000000034 method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H7/00—Multiple-port networks comprising only passive electrical elements as network components

- H03H7/42—Networks for transforming balanced signals into unbalanced signals and vice versa, e.g. baluns

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H1/00—Constructional details of impedance networks whose electrical mode of operation is not specified or applicable to more than one type of network

- H03H2001/0021—Constructional details

- H03H2001/0085—Multilayer, e.g. LTCC, HTCC, green sheets

Landscapes

- Filters And Equalizers (AREA)

- Amplifiers (AREA)

Abstract

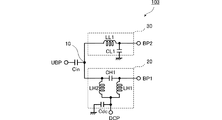

【解決手段】平衡不平衡変換器103は、不平衡端子UBPが接続される分岐点10と第1の端子BP1との間に90度位相回路20、分岐点10と第2の端子BP2との間に−90度位相回路30をそれぞれ備えている。第1の端子BP1と電源供給端子DCPとの間には第1のインダクタLH1、分岐点10と電源供給端子DCPとの間には第2のインダクタLH2をそれぞれ接続し、電源供給端子DCPと接地との間には電源供給端子側キャパシタCdcをシャントに接続している。分岐点10と第2の端子BP2との間には第2の端子側直列インダクタLL1を直列に接続している。

【選択図】図6

Description

このようにして、極性の反転した平衡信号と不平衡信号との変換を行う。

(1) 電源供給端子、不平衡端子および第1・第2の端子から成る1組の平衡端子を有し、前記不平衡端子と前記第1・第2の端子とは分岐点を介して接続され、前記分岐点と前記第1の端子との間に配置される線路に対して直列に接続された第1の端子側直列キャパシタ(CH1)を含む90度位相回路(90度進相回路)と、前記分岐点と前記第2の端子との間に配置される線路に対して直列に接続された第2の端子側直列インダクタ(LL1)を含む−90度位相回路(90度遅相回路)と、を備えてなる平衡不平衡変換器において、

前記90度位相回路は、一方端が前記第1の端子側直列キャパシタの前記第1の端子側に接続され、他方端が前記電源供給端子に接続された第1のインダクタ(LH1)と、一方端が前記第1の端子側直列キャパシタの前記分岐点側に接続され、他方端が前記電源供給端子に接続された第2のインダクタ(LH2)と、を含むことを特徴とする。

これにより、電源供給端子から印加されるバイアス電圧(電流)が不平衡端子側へ流れ込むこともない。また、不平衡端子側直列キャパシタ(Cin)はハイパスフィルタとしても作用するため、不要な低域信号の減衰効果もある。

この構成により、少ない回路要素数で−90度位相回路を構成できる。

この構成により、少ない回路要素数で−90度位相回路を構成できる。

これにより、ローパスフィルタである−90度位相回路の設計自由度が向上する。また、次数を増やすことで帯域付近の通過特性の傾きを小さくできるため、バランス特性の1つである振幅差の傾きを小さくし、バランス特性を向上することができる。

この構成により、90度位相回路と−90度位相回路との干渉が抑制できる。

これにより2つの平衡端子間のアイソレーションが向上する。

この構成により、各端子間の結合が防止され、アイソレーションが向上する。

第1の実施形態に係る平衡不平衡変換器の構成を図2〜図4を参照して説明する。

図2は平衡不平衡変換器101の回路図である。この平衡不平衡変換器101は、第1の端子BP1、第2の端子BP2からなる1組の平衡端子と不平衡端子UBPとを有する。不平衡端子UBPが接続される分岐点10と第1の端子BP1との間には90度位相回路20を備えていて、分岐点10と第2の端子BP2との間には−90度位相回路30を備えている。

このようにして表面実装型チップ部品である平衡不平衡変換器を構成する。

また、上下に配置しているインダクタLH1,LH2同士の距離を離して配置することによって、インダクタLH1,LH2間の不要な結合が抑制できる。

図5は、積層基板の端面及び上下面への各端子の引き出し方を変えた例を示す図である。内部の主要部の構成及び回路は第1の実施形態の場合と同様である。

第1の実施形態において図3・図4に示した例では、平衡端子BP1,BP2の間にグランド端子GNDを配置したが、例えば図5(A)に示すように、平衡端子BP1,BP2の間に電源供給端子側キャパシタCdcにより高周波接地された電源供給端子DCPを配置してもよい。

図6は第3の実施形態に係る平衡不平衡変換器103の回路図である。第1の実施形態において図2に示した平衡不平衡変換器101と異なるのは、不平衡端子UBPと分岐点10との間に不平衡端子側直列キャパシタCinを直列接続した点である。その他の構成は第1の実施形態の場合と同様である。

この例では、誘電体層67,68に形成した電極によって不平衡端子側直列キャパシタCinを構成している。その他は図3に示したものと同様である。

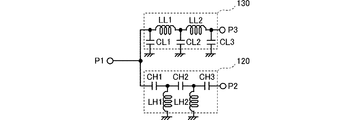

図8は第4の実施形態に係る平衡不平衡変換器の回路図である。図8(A)に示す平衡不平衡変換器104Aは、第2の端子BP2と第2の端子側並列キャパシタCL1との間に第2端子側の第2の直列インダクタLL2を備えている。その他の構成は図2に示したものと同様である。

図9は第5の実施形態に係る平衡不平衡変換器の回路図である。

図9(A)に示す平衡不平衡変換器105Aは、−90度位相回路32の第2の端子側並列キャパシタCL1の一端を第2の端子側直列インダクタLL1の第2の端子側に接続するとともに、他方を電源供給端子DCPに接続している。電源供給端子DCPは電源供給端子側キャパシタCdcによって高周波的に接地されているので、−90度位相回路32は図2に示した−90度位相回路30と同様に作用する。

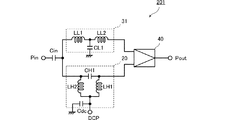

図11は第6の実施形態に係る増幅回路モジュール201の回路図である。図11において90度位相回路20、−90度位相回路31及び不平衡端子側直列キャパシタCinによって平衡不平衡変換器を構成している。この平衡不平衡変換器の構成は図8(B)に示したものと同様である。この平衡不平衡変換回路の平衡端子に平衡入力型の平衡増幅器40を接続している。

20…90度位相回路

30〜33…−90度位相回路

40…平衡増幅器

51〜69…誘電体層

70A,70B,70C…積層基板

101…平衡不平衡変換器

103〜105…平衡不平衡変換器

BP1…第1の端子

BP2…第2の端子

Cdc…電源供給端子側キャパシタ

CH1…第1の端子側直列キャパシタ

Cin…不平衡端子側直列キャパシタ

CL1…第2の端子側並列キャパシタ

DCP…電源供給端子

GND…グランド端子

LH1…第1のインダクタ

LH2…第2のインダクタ

LL1…第2の端子側直列インダクタ

LL2…第2の端子側の第2の直列インダクタ

Pin…不平衡入力端子

Pout…不平衡出力端子

UBP…不平衡端子

Claims (14)

- 電源供給端子、不平衡端子および第1・第2の端子から成る1組の平衡端子を有し、前記不平衡端子と前記第1・第2の端子とは分岐点を介して接続され、前記分岐点と前記第1の端子との間に配置される線路に対して直列に接続された第1の端子側直列キャパシタを含む90度位相回路と、前記分岐点と前記第2の端子との間に配置される線路に対して直列に接続された第2の端子側直列インダクタを含む−90度位相回路と、を備えてなる平衡不平衡変換器において、

前記90度位相回路は、一方端が前記第1の端子側直列キャパシタの前記第1の端子側に接続され、他方端が前記電源供給端子に接続された第1のインダクタと、一方端が前記第1の端子側直列キャパシタの前記分岐点側に接続され、他方端が前記電源供給端子に接続された第2のインダクタと、を含むことを特徴とする平衡不平衡変換器。 - 前記不平衡端子と前記分岐点との間に直列に不平衡端子側直列キャパシタが接続された、請求項1に記載の平衡不平衡変換器。

- 前記−90度位相回路は、前記第2の端子側直列インダクタの第2の端子側と接地との間に接続された第2の端子側並列キャパシタを含む、請求項1または2に記載の平衡不平衡変換器。

- 前記−90度位相回路は、前記第2の端子側直列インダクタの第2の端子側と前記電源供給端子との間に接続された第2の端子側並列キャパシタを含む、請求項1または2に記載の平衡不平衡変換器。

- 前記−90度位相回路は、前記第2の端子側直列インダクタと前記第2の端子側並列キャパシタとの接続点と前記第2の端子との間に直列に接続された第2の端子側の第2の直列インダクタを含む、請求項1〜4のいずれかに記載の平衡不平衡変換器。

- 前記90度位相回路は、前記電源供給端子と接地との間に接続された電源供給端子側キャパシタを含む、請求項1〜5のいずれかに記載の平衡不平衡変換器。

- 前記90度位相回路と前記−90度位相回路は、電極パターンを形成した誘電体層を積層してなる積層基板に構成され、前記積層基板の一方の主面からの透視状態で前記90度位相回路と前記−90度位相回路の形成範囲の中心位置が異なっている、請求項1〜6のいずれかに記載の平衡不平衡変換器。

- 前記電源供給端子側キャパシタ以外の回路と前記−90度位相回路とが、電極パターンを形成した誘電体層を積層してなる積層基板に構成された、請求項4に記載の平衡不平衡変換器。

- 前記90度位相回路に含まれる、第1のインダクタ、第2のインダクタ及び前記−90度位相回路に含まれる第2の端子側直列インダクタの積層方向の上下にグランド電極及びキャパシタ電極が設けられた、請求項7または8に記載の平衡不平衡変換器。

- 前記積層基板は矩形状の誘電体を積層してなり、積層基板の少なくとも下面に前記第1・第2の端子、前記不平衡端子、前記電源供給端子をそれぞれ備え、前記第1・第2の端子は前記積層基板の対向する辺にそれぞれ配置されている、請求項7〜9のいずれかに記載の平衡不平衡変換器。

- 前記積層基板は矩形状の誘電体を積層してなり、積層基板の少なくとも下面に前記第1・第2の端子、前記不平衡端子、前記電源供給端子をそれぞれ備え、前記第1・第2の端子は前記電源供給端子を挟み込むように前記積層基板の1辺に配置されている、請求項7〜9のいずれかに記載の平衡不平衡変換器。

- 前記積層基板は矩形状の誘電体を積層してなり、積層基板の少なくとも下面に前記第1・第2の端子、前記不平衡端子、前記電源供給端子、及び前記グランド電極と導通するグランド端子を備え、前記第1・第2の端子は前記グランド端子を挟み込むように前記積層基板の1辺に配置されている、請求項7〜9のいずれかに記載の平衡不平衡変換器。

- 前記積層基板は矩形状の誘電体を積層してなり、積層基板の少なくとも下面に前記第1・第2の端子、前記不平衡端子、前記電源供給端子をそれぞれ備え、これらの端子は前記積層基板の四辺または四隅にそれぞれ配置されている、請求項7〜9のいずれかに記載の平衡不平衡変換器。

- 請求項1〜13のいずれかに記載の平衡不平衡変換器と、前記第1・第2の端子に接続されて平衡増幅を行う平衡増幅器とを備えた増幅回路モジュール。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008162323A JP4591559B2 (ja) | 2008-06-20 | 2008-06-20 | 平衡不平衡変換器及び増幅回路モジュール |

| US12/483,271 US7978021B2 (en) | 2008-06-20 | 2009-06-12 | Balanced-to-unbalanced transformer and amplifier circuit module |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008162323A JP4591559B2 (ja) | 2008-06-20 | 2008-06-20 | 平衡不平衡変換器及び増幅回路モジュール |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010004395A true JP2010004395A (ja) | 2010-01-07 |

| JP4591559B2 JP4591559B2 (ja) | 2010-12-01 |

Family

ID=41430612

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008162323A Active JP4591559B2 (ja) | 2008-06-20 | 2008-06-20 | 平衡不平衡変換器及び増幅回路モジュール |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7978021B2 (ja) |

| JP (1) | JP4591559B2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012205195A (ja) * | 2011-03-28 | 2012-10-22 | Tdk Corp | 積層構造型バラン |

| JP2013034041A (ja) * | 2011-08-01 | 2013-02-14 | Murata Mfg Co Ltd | 不平衡−平衡変換回路素子 |

| JP2014519234A (ja) * | 2011-05-04 | 2014-08-07 | エプコス アクチエンゲゼルシャフト | 音響体積波で動作するbawフィルタ |

| JP2018006790A (ja) * | 2016-06-27 | 2018-01-11 | 株式会社村田製作所 | 高周波電子部品 |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8358179B2 (en) * | 2009-09-10 | 2013-01-22 | Stats Chippac, Ltd. | Semiconductor device and method of forming directional RF coupler with IPD for additional RF signal processing |

| DE102012208555B4 (de) * | 2012-05-22 | 2023-07-27 | Rohde & Schwarz GmbH & Co. Kommanditgesellschaft | Schaltbare Frequenzweiche und Signalgenerator |

| JP5660087B2 (ja) * | 2012-08-09 | 2015-01-28 | 株式会社村田製作所 | バラントランス |

| US9875724B2 (en) | 2012-08-21 | 2018-01-23 | Beijing Lenovo Software Ltd. | Method and electronic device for adjusting display |

| DE102013209450A1 (de) * | 2013-05-22 | 2014-11-27 | Siemens Aktiengesellschaft | Symmetrierschaltung |

| TWI530017B (zh) * | 2013-07-31 | 2016-04-11 | Murata Manufacturing Co | Balanced - unbalanced converter |

| WO2015186578A1 (ja) * | 2014-06-06 | 2015-12-10 | 株式会社村田製作所 | 移相回路 |

| JP6112075B2 (ja) * | 2014-06-27 | 2017-04-12 | 株式会社村田製作所 | 電子部品 |

| CN104734134B (zh) * | 2015-04-09 | 2019-06-28 | 国家电网公司 | 一种换流器接地系统 |

| JP6288472B2 (ja) * | 2015-07-24 | 2018-03-07 | 株式会社村田製作所 | 平衡不平衡変換器 |

| JP6593192B2 (ja) * | 2016-01-26 | 2019-10-23 | Tdk株式会社 | 方向性結合器 |

| WO2017204621A1 (en) * | 2016-05-26 | 2017-11-30 | Greenpeak Technologies B.V. | Balun circuit arrangement |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10200360A (ja) * | 1997-01-07 | 1998-07-31 | Tdk Corp | 積層バルントランス |

| JP2003046358A (ja) * | 2001-05-16 | 2003-02-14 | Matsushita Electric Ind Co Ltd | 積層フィルタ、積層複合デバイス、および通信装置 |

| JP2005166702A (ja) * | 2003-11-28 | 2005-06-23 | Tdk Corp | バラン |

| JP2007129565A (ja) * | 2005-11-04 | 2007-05-24 | Alps Electric Co Ltd | ローパスフィルタ |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3668150B2 (ja) | 2001-04-17 | 2005-07-06 | 日本無線株式会社 | バイアス回路 |

| US7023301B2 (en) | 2001-05-16 | 2006-04-04 | Matsushita Electric Industrial Co., Ltd. | Laminated filter with a single shield conductor, integrated device, and communication apparatus |

| JP4241400B2 (ja) | 2004-01-09 | 2009-03-18 | 株式会社豊田中央研究所 | 平衡線路−不平衡線路接続器 |

| JP3944193B2 (ja) | 2004-02-09 | 2007-07-11 | 太陽誘電株式会社 | バランおよびバランスフィルタおよび無線通信機器 |

| JP2006129444A (ja) * | 2004-09-30 | 2006-05-18 | Renesas Technology Corp | 高周波電力増幅器および高周波電力増幅器モジュール |

| FR2878092A1 (fr) * | 2004-11-18 | 2006-05-19 | St Microelectronics Sa | Balun a elements localises |

| JP2008098769A (ja) | 2006-10-06 | 2008-04-24 | Toyota Central R&D Labs Inc | 周波数可変アンテナ |

| US7688158B2 (en) * | 2007-09-28 | 2010-03-30 | Intel Corporation | Digitally tuned, integrated baluns with enhanced linearity for multi-band radio applications |

-

2008

- 2008-06-20 JP JP2008162323A patent/JP4591559B2/ja active Active

-

2009

- 2009-06-12 US US12/483,271 patent/US7978021B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10200360A (ja) * | 1997-01-07 | 1998-07-31 | Tdk Corp | 積層バルントランス |

| JP2003046358A (ja) * | 2001-05-16 | 2003-02-14 | Matsushita Electric Ind Co Ltd | 積層フィルタ、積層複合デバイス、および通信装置 |

| JP2005166702A (ja) * | 2003-11-28 | 2005-06-23 | Tdk Corp | バラン |

| JP2007129565A (ja) * | 2005-11-04 | 2007-05-24 | Alps Electric Co Ltd | ローパスフィルタ |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012205195A (ja) * | 2011-03-28 | 2012-10-22 | Tdk Corp | 積層構造型バラン |

| JP2014519234A (ja) * | 2011-05-04 | 2014-08-07 | エプコス アクチエンゲゼルシャフト | 音響体積波で動作するbawフィルタ |

| US9859868B2 (en) | 2011-05-04 | 2018-01-02 | Snaptrack, Inc. | BAW-filter operating using bulk acoustic waves and passive components forming a balun |

| JP2013034041A (ja) * | 2011-08-01 | 2013-02-14 | Murata Mfg Co Ltd | 不平衡−平衡変換回路素子 |

| US9059681B2 (en) | 2011-08-01 | 2015-06-16 | Murata Manufacturing Co., Ltd. | Unbalanced-balanced conversion circuit element |

| JP2018006790A (ja) * | 2016-06-27 | 2018-01-11 | 株式会社村田製作所 | 高周波電子部品 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090315636A1 (en) | 2009-12-24 |

| US7978021B2 (en) | 2011-07-12 |

| JP4591559B2 (ja) | 2010-12-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4591559B2 (ja) | 平衡不平衡変換器及び増幅回路モジュール | |

| CN103580637B (zh) | 平衡不平衡变压器 | |

| JP5677499B2 (ja) | 高周波回路モジュール | |

| JP5018858B2 (ja) | 高周波モジュール | |

| WO2014061448A1 (ja) | 高周波モジュール | |

| JP5609918B2 (ja) | スイッチモジュール | |

| JPWO2016125719A1 (ja) | 高周波スイッチモジュール | |

| JP5783186B2 (ja) | 積層基板モジュール | |

| JPWO2012102284A1 (ja) | 送信モジュール | |

| CN102301610B (zh) | 天线共用模块 | |

| JP5609996B2 (ja) | 電力増幅回路 | |

| JP5636662B2 (ja) | 高周波モジュール | |

| CN204244072U (zh) | 多通道型dc-dc转换器 | |

| JP2024098344A (ja) | 電力増幅回路 | |

| JPWO2018235452A1 (ja) | ノイズ除去回路およびノイズ除去素子 | |

| JP4656514B2 (ja) | 平衡−不平衡変換回路及びこれを用いた高周波部品 | |

| TWI424612B (zh) | 寬頻帶耦合濾波器 | |

| CN1983712B (zh) | 具滤波器功能的平衡至非平衡转换器 | |

| JP2011243829A (ja) | 積層型電子部品 | |

| KR20130033159A (ko) | 전력 결합기를 이용한 씨모스 전력 증폭기 | |

| JP2006108814A (ja) | バランスフィルタ | |

| JP2016100797A (ja) | フィルタ一体型カプラおよび通信モジュール | |

| JP3153518U (ja) | 複合バラン | |

| JP4900623B2 (ja) | 複合バラン | |

| JP2005303193A (ja) | チップ型コンデンサアレイ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091007 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100323 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100520 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100520 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100817 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100830 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4591559 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |