JP2008524846A - 薄膜トランジスタのためのn型半導体材料 - Google Patents

薄膜トランジスタのためのn型半導体材料 Download PDFInfo

- Publication number

- JP2008524846A JP2008524846A JP2007546723A JP2007546723A JP2008524846A JP 2008524846 A JP2008524846 A JP 2008524846A JP 2007546723 A JP2007546723 A JP 2007546723A JP 2007546723 A JP2007546723 A JP 2007546723A JP 2008524846 A JP2008524846 A JP 2008524846A

- Authority

- JP

- Japan

- Prior art keywords

- thin film

- fluorine

- article

- semiconductor material

- organic semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09B—ORGANIC DYES OR CLOSELY-RELATED COMPOUNDS FOR PRODUCING DYES, e.g. PIGMENTS; MORDANTS; LAKES

- C09B5/00—Dyes with an anthracene nucleus condensed with one or more heterocyclic rings with or without carbocyclic rings

- C09B5/62—Cyclic imides or amidines of peri-dicarboxylic acids of the anthracene, benzanthrene, or perylene series

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having a potential-jump barrier or a surface barrier

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/464—Lateral top-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having a potential-jump barrier or a surface barrier

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/466—Lateral bottom-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/10—OLEDs or polymer light-emitting diodes [PLED]

- H10K50/14—Carrier transporting layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K85/00—Organic materials used in the body or electrodes of devices covered by this subclass

- H10K85/60—Organic compounds having low molecular weight

- H10K85/615—Polycyclic condensed aromatic hydrocarbons, e.g. anthracene

- H10K85/621—Aromatic anhydride or imide compounds, e.g. perylene tetra-carboxylic dianhydride or perylene tetracarboxylic di-imide

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K85/00—Organic materials used in the body or electrodes of devices covered by this subclass

- H10K85/60—Organic compounds having low molecular weight

- H10K85/649—Aromatic compounds comprising a hetero atom

- H10K85/654—Aromatic compounds comprising a hetero atom comprising only nitrogen as heteroatom

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/549—Organic PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Chemical & Material Sciences (AREA)

- Physics & Mathematics (AREA)

- Spectroscopy & Molecular Physics (AREA)

- Engineering & Computer Science (AREA)

- Materials Engineering (AREA)

- Organic Chemistry (AREA)

- Optics & Photonics (AREA)

- Thin Film Transistor (AREA)

Abstract

Description

N,N'-ジアルキルペリレンテトラカルボン酸ジイミドの合成は、Rademacher, A.他、Chem. Ber. 1982 115, 2927に記載されている。本発明によれば、Aldrich Chemical Companyから入手可能なペリレンテトラカルボン酸ジイミド、3〜4当量過剰のアミン、例えば、やはりAldrichから入手可能なペンタフルオロアニリン、触媒量の酢酸亜鉛、及びジアンヒドリド分子1グラム当たり10〜15 mlのキノリンの混合物を、温度約220℃で4〜5時間にわたって加熱した。混合物を室温まで冷やしておき、そして沈澱した固形物を捕集し、濾過し、そしてアセトンで、続いてそれぞれ200 mlの沸騰0.1 M水性Na2CO3、沸騰水、及び高温トルエンで洗浄し、これを、生成物が実質的に溶解されることになる温度未満で維持する。次いで、10-5〜10-6 Torrで一連の昇華を施すことにより、固形物を精製する。

本発明の種々の材料の電気特性を試験するために、トップコンタクト幾何学的配置を使用して、電界効果トランジスタを典型的な形式で形成した。使用した基板は、重度にドープされたシリコンウェハーである。これはトランジスタのゲートとしても役立つ。ゲート誘電体は、厚さ165 nmの熱成長させられたSiO2層である。ゲート誘電体の表面を処理することにより電気特性を改善できることが、p型及びn型トランジスタの両方に関して、以前に示されている。本明細書中に記載された試験のほとんどの場合、酸化物表面は、薄い(<10 nm)スピン塗布ポリマー層、又はオクタデシルトリクロロシラン(OTS)の自己集成単層(SAM)で処理された。典型的には、未処理酸化物試料が比較例に含まれた。

製作されたデバイスの電気的特徴付けを、Hewlett Packard HP 4145b(商標)パラメータ分析器で実施した。空気中のデバイスの安定性を意図的に試験することを除けば、プローブ測定ステーションは、全ての測定に対して正のN2環境内で保持した。白色光に対する感光性を検査する場合を除いては、測定を硫黄光下で実施した。デバイスを試験前に空気に対して暴露した。

下記例は、フッ素非含有N,N'置換型3,4,9,10ペリレンテトラカルボン酸ジイミドと比較して、フッ素含有N,N'-ジアリール3,4,9,10ペリレン系テトラカルボン酸ジイミドを含む本発明のデバイスが、高い移動度及びオン/オフ比を有する、改善されたnチャネル半導体フィルムを提供することを実証する。飽和領域内で計算された移動度は、0.05〜0.2 cm2/Vsであり、オン/オフ比は104〜105であった。改善された性能に加えて、デバイスはまた、典型的なnチャネルTFTに対して改善された空気中の安定性、及び優れた再現性を示す。

この例は、フッ素非含有N,N'-ジフェニル3,4,9,10ペリレンテトラカルボン酸ジイミドC-1から形成されたn型TFTデバイスを実証する。

この例は、本発明によるフッ素含有N,N'-ジアリール3,4,9,10ペリレン系テトラカルボン酸ジイミドI-1から形成されたn型TFTデバイスの改善された性能を実証する。

この例は、フッ素含有N,N'-ジフェニル3,4,9,10ペリレン系テトラカルボン酸ジイミドI-10から形成されたn型TFTデバイスの改善された性能を実証する。OTFTのアクティブ材料として発明I-1を使用したn型TFTデバイスを、例1におけるように形成した。複数のOTFTを調製し、そしてそれぞれの堆積作業に関して試験した。平均した結果を表2に示す。

この例は、トリフルオロメチル含有N,N'-ジフェニル3,4,9,10ペリレン系テトラカルボン酸ジイミドI-14から形成されたn型TFTデバイスの改善された性能を実証する。

この例は、半導体膜層の厚さに関連して、本発明において使用されたアクティブ材料の堅牢性を実証する。

この例は、半導体材料の堆積中の基板温度に関連して、本発明において使用されたアクティブ材料の堅牢性を実証する。

この例は、OTFTデバイスの幾何学的配置に関連して、本発明において使用された材料の堅牢性を実証する。

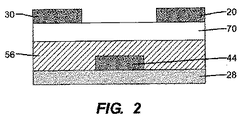

28 基板

30 ドレイン電極

44 ゲート電極

56 ゲート誘電体

70 半導体

Claims (29)

- 各イミド窒素原子に直接に結合されている、1つ又は2つ以上のフッ素含有基が結合された炭素環式又は複素環式芳香環系を有する、フッ素含有N,N'-ジアリールペリレン系テトラカルボン酸ジイミド化合物を含む有機半導体材料から成る薄膜を、薄膜トランジスタ内に含んで成る物品。

- 該薄膜トランジスタが、誘電層を含む電界効果トランジスタであり、第3のコンタクト手段がゲート電極であり、第1及び第2のコンタクト手段がソース電極及びドレイン電極であり、そして該ゲート電極と該有機半導体材料薄膜との両方が該誘電層に接触し、そして該ソース電極と該ドレイン電極との両方が該有機半導体材料薄膜と接触している限り、該誘電層、該ゲート電極、該有機半導体材料薄膜、該ソース電極、及び該ドレイン電極が任意の配列を成している請求項1に記載の物品。

- 該有機半導体材料が、0.01 cm2/Vsを上回る電子移動度を示すことができる請求項1に記載の物品。

- A1及びA2部分がそれぞれ独立して、1つ又は2つ以上のフッ素もしくはフルオロアルキル基又はこれらの任意の組み合わせで置換されたフェニル環系を含む請求項4に記載の物品。

- 該フッ素含有基が、フッ素原子、フルオロアルキル基、環原子数5〜10のフッ素化炭素環式又は複素環式芳香環系、及びこれらの組み合わせから選択される請求項4に記載の物品。

- A1及びA2がそれぞれ縮合芳香環を含む請求項4に記載の物品。

- Xが独立して、アルキル、アルケニル、アルコキシ、ハロゲン、及びシアノ、又はこれらの組み合わせから選択される請求項4に記載の物品。

- 該2つのフェニル環のそれぞれの環上のR1〜R5のうちの少なくとも2つが、フッ素含有基である請求項9に記載の物品。

- 該2つのフェニル環のそれぞれの環上のR1〜R5の全てが、フッ素含有基である請求項9に記載の物品。

- nがゼロであり、そして該2つのフェニル環のそれぞれの環上のR1〜R5のどれもがフッ素原子である請求項11に記載の物品。

- 該薄膜トランジスタのソース/ドレイン電流のオン/オフ比が、104以上である請求項1に記載の物品。

- 該ゲート電極が、前記有機半導体材料を通る該ソース電極と該ドレイン電極との間の電流を、該ゲート電極に印加される電圧によって制御するように適合されている請求項2に記載の物品。

- 該ゲート誘電体が、無機又は有機の電気絶縁材料を含む請求項15に記載の物品。

- 該薄膜トランジスタが、任意に可撓性である非関与支持体をさらに含む請求項1に記載の物品。

- 該ソース電極、ドレイン電極、及びゲート電極がそれぞれ独立して、ドープ型シリコン、金属、及び導電性ポリマーから選択された材料を含む請求項2に記載の物品。

- 請求項1に記載の複数の薄膜トランジスタを含む、集積回路、アクティブマトリックスディスプレイ、及び太陽電池から成る群から選択される電子デバイス。

- 複数の薄膜トランジスタが、任意に可撓性である非関与支持体上にある請求項19に記載の電子デバイス。

- 必ずしも下記順序通りではないが、以下の各工程:

(a) 各イミド窒素原子に直接に結合されている、1つ又は2つ以上のフッ素含有基が結合された炭素環式又は複素環式芳香環系を有する、フッ素含有N,N'-ジアリールペリレン系テトラカルボン酸ジイミド化合物を含む有機半導体材料から成る薄膜を、有機半導体材料薄膜が0.01 cm2/Vsを上回る電界効果電子移動度を示すように、基板上に堆積する工程、

(b) 離隔されたソース電極とドレイン電極とを形成する工程、該ソース電極と該ドレイン電極はnチャネル半導体膜によって分離され、且つ該nチャネル半導体膜と電気的に接続されている;及び

(c) 該半導体材料から離隔されたゲート電極を形成する工程

を含んで成る薄膜半導体デバイスの製作方法。 - 該化合物が、昇華によって又は液相堆積によって該基板上に堆積され、該基板が堆積中に100℃以下の温度を有する請求項21に記載の方法。

- 前記電極と前記薄膜との間の界面に対する前処理が行われない請求項21に記載の方法。

- 該フッ素含有N,N'-ジアリールペリレン系テトラカルボン酸ジイミド化合物が、N,N'-ビス(ペンタフルオロフェニル)ペリレン3,4,9,10テトラカルボン酸ジイミドから成る請求項21に記載の方法。

- 必ずしも下記順序通りではないが、以下の各工程:

(a) 支持体を用意する工程;

(b) 該基板上にゲート電極材料を提供する工程;

(c) 該ゲート電極材料上にゲート誘電体を提供する工程;

(d) 該ゲート誘電体上に、有機半導体材料薄膜を堆積する工程;

(e) 該有機半導体材料の薄膜に隣接して、ソース電極及びドレイン電極を提供する工程

を含む請求項21に記載の方法。 - 該工程が上記順序で行われる請求項25に記載の方法。

- 該支持体が可撓性である請求項25に記載の方法。

- 全体的に、100℃のピーク温度未満で行われる請求項25に記載の方法。

- 請求項21に記載の方法によって形成された複数の薄膜トランジスタを含んで成る集積回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/015,897 US7326956B2 (en) | 2004-12-17 | 2004-12-17 | Fluorine-containing N,N′-diaryl perylene-based tetracarboxylic diimide compounds as N-type semiconductor materials for thin film transistors |

| PCT/US2005/043505 WO2006065548A2 (en) | 2004-12-17 | 2005-12-02 | N-type semiconductor materials for thin film transistors |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008524846A true JP2008524846A (ja) | 2008-07-10 |

| JP2008524846A5 JP2008524846A5 (ja) | 2008-12-11 |

Family

ID=36588362

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007546723A Pending JP2008524846A (ja) | 2004-12-17 | 2005-12-02 | 薄膜トランジスタのためのn型半導体材料 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7326956B2 (ja) |

| EP (1) | EP1825533A2 (ja) |

| JP (1) | JP2008524846A (ja) |

| KR (1) | KR20070098807A (ja) |

| CN (1) | CN101084589A (ja) |

| TW (1) | TW200633285A (ja) |

| WO (1) | WO2006065548A2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011052721A1 (ja) | 2009-10-29 | 2011-05-05 | 大日精化工業株式会社 | 有機半導体材料、有機半導体薄膜および有機薄膜トランジスタ |

| WO2011052719A1 (ja) | 2009-10-29 | 2011-05-05 | 大日精化工業株式会社 | ペリレンテトラカルボキシジイミド誘導体 |

| WO2012029544A1 (ja) | 2010-08-29 | 2012-03-08 | 国立大学法人信州大学 | 有機半導体微粒子材料、有機半導体薄膜、有機半導体膜形成用分散液、有機半導体薄膜の製造方法および有機薄膜トランジスタ |

| JP2014519490A (ja) * | 2011-05-11 | 2014-08-14 | ビーエーエスエフ ソシエタス・ヨーロピア | ハロゲン化ペリレンベースの半導体材料 |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1980791B (zh) * | 2004-01-26 | 2012-08-22 | 西北大学 | 苝n-型半导体和相关器件 |

| US7198977B2 (en) * | 2004-12-21 | 2007-04-03 | Eastman Kodak Company | N,N′-di(phenylalky)-substituted perylene-based tetracarboxylic diimide compounds as n-type semiconductor materials for thin film transistors |

| GB0506899D0 (en) * | 2005-04-05 | 2005-05-11 | Plastic Logic Ltd | Multiple conductive layer TFT |

| US8138075B1 (en) | 2006-02-06 | 2012-03-20 | Eberlein Dietmar C | Systems and methods for the manufacture of flat panel devices |

| US7569693B2 (en) * | 2006-06-12 | 2009-08-04 | Northwestern University | Naphthalene-based semiconductor materials and methods of preparing and use thereof |

| US7947837B2 (en) * | 2006-10-25 | 2011-05-24 | Polyera Corporation | Organic semiconductor materials and methods of preparing and use thereof |

| US7902363B2 (en) | 2006-11-17 | 2011-03-08 | Polyera Corporation | Diimide-based semiconductor materials and methods of preparing and using the same |

| KR20090117730A (ko) * | 2007-01-08 | 2009-11-12 | 폴리에라 코퍼레이션 | 아렌-비스(디카르복스이미드)-기재 반도체 물질, 및 이를 제조하기 위한 관련된 중간체의 제조 방법 |

| CN100456517C (zh) * | 2007-01-23 | 2009-01-28 | 中国科学院长春应用化学研究所 | 轴向取代酞菁化合物用于制备有机薄膜晶体管的应用 |

| WO2008091670A2 (en) * | 2007-01-24 | 2008-07-31 | Polyera Corporation | Organic semiconductor materials and precursors thereof |

| US7649199B2 (en) * | 2008-04-11 | 2010-01-19 | Eastman Kodak Company | N-type semiconductor materials in thin film transistors and electronic devices |

| KR101012542B1 (ko) * | 2008-12-12 | 2011-02-07 | 재단법인대구경북과학기술원 | 고분자 화합물 및 그를 포함하는 태양전지 |

| US8283469B2 (en) * | 2010-03-24 | 2012-10-09 | National Tsing Hua University | Perylene diimide derivative and organic semiconductor element using the same material |

| US8411489B2 (en) | 2010-04-30 | 2013-04-02 | Eastman Kodak Company | Semiconducting devices and methods of preparing |

| US8314265B2 (en) | 2010-04-30 | 2012-11-20 | Eastman Kodak Company | Aromatic amic acids or amic esters and compositions |

| US20110269966A1 (en) * | 2010-04-30 | 2011-11-03 | Deepak Shukla | Semiconducting articles |

| US8530270B2 (en) | 2010-04-30 | 2013-09-10 | Eastman Kodak Company | Methods of preparing semiconductive compositions and devices |

| US8404892B2 (en) | 2010-05-27 | 2013-03-26 | Eastman Kodak Company | Aromatic amic acid salts and compositions |

| WO2012117089A1 (en) | 2011-03-03 | 2012-09-07 | Basf Se | Perylene-based semiconducting materials |

| US8471020B2 (en) | 2011-03-03 | 2013-06-25 | Basf Se | Perylene-based semiconducting materials |

| JP2014529593A (ja) | 2011-08-12 | 2014-11-13 | ビーエーエスエフ ソシエタス・ヨーロピアBasf Se | フッ素化ペリレンベースの半導体材料 |

| CN105862133B (zh) * | 2015-01-23 | 2021-04-13 | 国家纳米科学中心 | 一种n型有机半导体晶体材料及其制备方法和用途 |

| JP7464397B2 (ja) | 2020-01-31 | 2024-04-09 | 保土谷化学工業株式会社 | ペリレン誘導体化合物、該化合物を用いた有機半導体用組成物、該有機半導体用組成物を用いた有機薄膜トランジスタ |

| CN111892605B (zh) * | 2020-06-10 | 2021-11-02 | 中国科学院化学研究所 | 新型五元环苝二酰亚胺分子材料及其制备方法与应用 |

| WO2023187690A1 (en) * | 2022-03-30 | 2023-10-05 | Oti Lumionics Inc. | Nitrogen-containing heterocyclic compounds for forming a patterning coating and devices incorporating same |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE1141740B (de) * | 1962-01-09 | 1962-12-27 | Basf Ag | Verfahren zur Herstellung eines Farbstoffes |

| JP2002289353A (ja) * | 2001-03-26 | 2002-10-04 | Pioneer Electronic Corp | 有機半導体ダイオード |

| WO2004013922A2 (en) * | 2002-08-06 | 2004-02-12 | Avecia Limited | Organic electronic devices |

| JP2004247716A (ja) * | 2003-01-23 | 2004-09-02 | Mitsubishi Chemicals Corp | 積層体の製造方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2664430B1 (fr) | 1990-07-04 | 1992-09-18 | Centre Nat Rech Scient | Transistor a effet de champ en couche mince de structure mis, dont l'isolant et le semiconducteur sont realises en materiaux organiques. |

| US6387727B1 (en) | 1999-03-29 | 2002-05-14 | Agere Systems Guardian Corp. | Device comprising n-channel semiconductor material |

| US6635507B1 (en) | 1999-07-14 | 2003-10-21 | Hughes Electronics Corporation | Monolithic bypass-diode and solar-cell string assembly |

| US7026643B2 (en) | 2001-05-04 | 2006-04-11 | International Business Machines Corporation | Organic n-channel semiconductor device of N,N' 3,4,9,10 perylene tetracarboxylic diimide |

| CN1190709C (zh) * | 2002-01-25 | 2005-02-23 | 浙江大学 | 含有氟代苝酰亚胺的单层有机光电导体及其制备方法 |

| DE10218618A1 (de) * | 2002-04-25 | 2003-11-06 | Basf Ag | Verfahren zur Herstellung von Perylen-3,4:9,10-tetracarbonsäuredimiden und Perylen-3,4:9,10-tetracarbonsäuredianhydrid sowie von Naphthalin-1,8-dicarbonsäureimiden |

| EP1361619A3 (en) | 2002-05-09 | 2007-08-15 | Konica Corporation | Organic thin-film transistor, organic thin-film transistor sheet and manufacturing method thereof |

| CN1980791B (zh) | 2004-01-26 | 2012-08-22 | 西北大学 | 苝n-型半导体和相关器件 |

| US7057205B2 (en) | 2004-03-17 | 2006-06-06 | Lucent Technologies Inc. | P-type OFET with fluorinated channels |

-

2004

- 2004-12-17 US US11/015,897 patent/US7326956B2/en not_active Expired - Fee Related

-

2005

- 2005-12-02 JP JP2007546723A patent/JP2008524846A/ja active Pending

- 2005-12-02 WO PCT/US2005/043505 patent/WO2006065548A2/en active Application Filing

- 2005-12-02 CN CNA2005800432979A patent/CN101084589A/zh active Pending

- 2005-12-02 KR KR1020077013632A patent/KR20070098807A/ko not_active Application Discontinuation

- 2005-12-02 EP EP05852668A patent/EP1825533A2/en not_active Withdrawn

- 2005-12-16 TW TW094144605A patent/TW200633285A/zh unknown

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE1141740B (de) * | 1962-01-09 | 1962-12-27 | Basf Ag | Verfahren zur Herstellung eines Farbstoffes |

| JP2002289353A (ja) * | 2001-03-26 | 2002-10-04 | Pioneer Electronic Corp | 有機半導体ダイオード |

| WO2004013922A2 (en) * | 2002-08-06 | 2004-02-12 | Avecia Limited | Organic electronic devices |

| JP2004247716A (ja) * | 2003-01-23 | 2004-09-02 | Mitsubishi Chemicals Corp | 積層体の製造方法 |

Non-Patent Citations (1)

| Title |

|---|

| JPN6012005686; Hong-Zheng Chen etc.: 'A novel organic n-type material:fluorinated perylene diimide' Solar Energy Materials & Solar Cells Vol.87, 20041202, 521-527 * |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011052721A1 (ja) | 2009-10-29 | 2011-05-05 | 大日精化工業株式会社 | 有機半導体材料、有機半導体薄膜および有機薄膜トランジスタ |

| WO2011052719A1 (ja) | 2009-10-29 | 2011-05-05 | 大日精化工業株式会社 | ペリレンテトラカルボキシジイミド誘導体 |

| US9133193B2 (en) | 2009-10-29 | 2015-09-15 | Dainichiseika Color & Chemicals Mfg. Co., Ltd. | Organic semiconductor material, organic semiconductor thin film, and organic thin film transistor |

| WO2012029544A1 (ja) | 2010-08-29 | 2012-03-08 | 国立大学法人信州大学 | 有機半導体微粒子材料、有機半導体薄膜、有機半導体膜形成用分散液、有機半導体薄膜の製造方法および有機薄膜トランジスタ |

| US9518224B2 (en) | 2010-08-29 | 2016-12-13 | Shinshu University | Organic semiconductor particulate material, organic semiconductor thin-film, dispersion liquid for forming organic semiconductor film, method for producing organic semiconductor thin-film, and organic thin-film transistor |

| JP2014519490A (ja) * | 2011-05-11 | 2014-08-14 | ビーエーエスエフ ソシエタス・ヨーロピア | ハロゲン化ペリレンベースの半導体材料 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20070098807A (ko) | 2007-10-05 |

| WO2006065548A2 (en) | 2006-06-22 |

| US7326956B2 (en) | 2008-02-05 |

| US20060131564A1 (en) | 2006-06-22 |

| CN101084589A (zh) | 2007-12-05 |

| EP1825533A2 (en) | 2007-08-29 |

| WO2006065548A3 (en) | 2007-01-04 |

| TW200633285A (en) | 2006-09-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2008524846A (ja) | 薄膜トランジスタのためのn型半導体材料 | |

| JP5336385B2 (ja) | 半導体材料としてのナフタレン系テトラカルボン酸ジイミド化合物 | |

| TWI423493B (zh) | 用於薄膜電晶體之n型半導體材料、製造薄膜半導體裝置之方法、電子裝置及積體電路 | |

| US7579619B2 (en) | N,N′-di(arylalkyl)-substituted naphthalene-based tetracarboxylic diimide compounds as n-type semiconductor materials for thin film transistors | |

| TWI416721B (zh) | 作為n型半導體材料之經n,n’-二環烷基取代之以萘為主的四羧酸二醯亞胺 | |

| US7629605B2 (en) | N-type semiconductor materials for thin film transistors | |

| US8187915B2 (en) | Aryl dicarboxylic acid diimidazole-based compounds as n-type semiconductor materials for thin film transistors | |

| US7858970B2 (en) | Heterocycloalkyl-substituted naphthalene-based tetracarboxylic diimide compounds as N-type semiconductor materials for thin film transistors |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081020 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081020 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120207 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120502 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120511 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121023 |