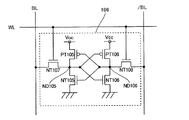

従来、データの入力および出力を行うための単一のポートを有するシングルポートSRAMセルを用いた半導体記憶装置が知られている。図8は、従来の一例によるシングルポートSRAMセルを示した回路図である。図8を参照して、従来の一例によるシングルポートSRAMセル106は、4つのnチャネルトランジスタ(nチャネルトランジスタNT105〜NT108)および2つのpチャネルトランジスタ(pチャネルトランジスタPT105およびPT106)の合計6つのトランジスタから構成されており、フリップフロップ回路を基本構成としている。

図8に示した従来の一例によるシングルポートSRAMセルを用いた半導体記憶装置の動作としては、まず、初期状態において、ワード線WLの電位はLレベルに保持されている。これにより、初期状態では、nチャネルトランジスタNT107およびNT108のゲートの電位はLレベルに保持されるので、nチャネルトランジスタNT107およびNT108はオフ状態に保持されている。この状態で、ノードND105の電位がHレベルであるとともに、ノードND106の電位がLレベルである場合には、nチャネルトランジスタNT106およびpチャネルトランジスタPT106のゲートの電位は、Hレベルになるので、nチャネルトランジスタNT106はオン状態になるとともに、pチャネルトランジスタPT106はオフ状態になる。このとき、nチャネルトランジスタNT108は、オフ状態であるので、nチャネルトランジスタNT106を介して接地電位が供給されることにより、ノードND106の電位は、Lレベルに保持される。

そして、ノードND106の電位がLレベルに保持されることにより、nチャネルトランジスタNT105およびpチャネルトランジスタPT105のゲートの電位は、Lレベルになるので、nチャネルトランジスタNT105はオフ状態になるとともに、pチャネルトランジスタPT105はオン状態になる。このとき、nチャネルトランジスタNT107は、オフ状態であるので、pチャネルトランジスタPT105を介して正電圧Vccが供給されることにより、ノードND105は、Hレベルに保持される。

上記のように、シングルポートSRAMセル106では、nチャネルトランジスタNT107およびNT108をオフ状態に保持することにより、ノードND105の電位およびノードND106の電位を保持することが可能となる。そして、ロウアドレスを選択するHレベルの信号をワード線WLに供給すると、nチャネルトランジスタNT107およびNT108のゲートの電位がHレベルに上昇するので、nチャネルトランジスタNT107およびNT108はオン状態になる。これにより、ビット線BLおよび/BLを介して、シングルポートSRAMセル106に対してデータの書き込みおよび読み出しを行うことが可能となる。

しかしながら、図8に示した従来の一例によるシングルポートSRAMセルを用いた半導体記憶装置では、所定のワード線WLを選択してHレベルの信号を供給すると、そのワード線WLに接続された全てのシングルポートSRAMセル106のnチャネルトランジスタNT107およびNT108がオン状態になる。これにより、Hレベルの信号を供給したワード線WLに接続される全てのシングルポートSRAMセル106に接続される全てのビット線対BLおよび/BLが活性化される。このように、所定のワード線WLを選

択してHレベルの信号を供給すると、全てのビット線対BLおよび/BLが活性化されるので、一方の系統から所定のシングルポートSRAMセル106にアクセスしている間は、他方の系統からどのシングルポートSRAMセル106に対してもアクセスすることはできない。このため、一方の系統からのアクセス中は、他方の系統からのアクセスはウェイト状態になるので、図8に示した従来の一例によるシングルポートSRAMセルを用いた半導体記憶装置では、半導体記憶装置の動作速度を向上するのは困難であるという不都合があった。

そこで、図8に示した従来の一例によるシングルポートSRAMセルを用いた半導体記憶装置の不都合を解消するために、2つの異なる系統から同時にデータの書き込みおよび読み出しを行うことが可能なデュアルポートSRAMセルを用いることにより、動作速度を向上させた半導体記憶装置が種々提案されている(たとえば、特許文献1参照)。

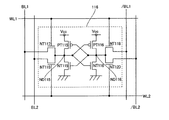

図9は、特許文献1に開示された従来の一般的なデュアルポートSRAMセルを示した回路図である。図9を参照して、従来の提案された一例によるデュアルポートSRAMセル116は、6つのnチャネルトランジスタ(nチャネルトランジスタNT115〜NT120)および2つのpチャネルトランジスタ(pチャネルトランジスタPT115およびPT116)の合計8つのトランジスタから構成されている。また、このデュアルポートSRAMセル116は、図8に示した従来の一例によるシングルポートSRAMセル106と異なり、データの入力および出力を行うためのポートを2つ備えている。この2つのポートは、それぞれ、nチャネルトランジスタNT117およびNT118と、nチャネルトランジスタNT119およびNT120とによって構成されている。また、nチャネルトランジスタNT117およびNT118によって構成されたポートには、ビット線対BL1および/BL1と、ワード線WL1とが接続されている。nチャネルトランジスタNT119およびNT120によって構成されたポートには、ビット線対BL2および/BL2と、ワード線WL2とが接続されている。なお、nチャネルトランジスタNT115、nチャネルトランジスタNT116、pチャネルトランジスタPT115およびpチャネルトランジスタPT116は、図8に示したnチャネルトランジスタNT105、nチャネルトランジスタNT106、pチャネルトランジスタPT105およびpチャネルトランジスタPT106と同様のフリップフロップ回路を基本構成としている。

次に、図9に示した従来の提案された一例によるデュアルポートSRAMセルを用いた半導体記憶装置の動作としては、まず、nチャネルトランジスタNT115およびNT116と、pチャネルトランジスタPT115およびPT116とにより、ノードND115およびND116の電位を保持する動作は、図8に示したシングルポートSRAMセルを用いた半導体記憶装置の動作と同様である。そして、ロウアドレスを選択するHレベルの信号をワード線WL1に供給すると、nチャネルトランジスタNT117およびNT118のゲートの電位がHレベルに上昇するので、nチャネルトランジスタNT117およびNT118はオン状態になる。これにより、ビット線対BL1および/BL1を介して、デュアルポートSRAMセル116にデータの書き込みおよび読み出しを行うことが可能となる。また、ロウアドレスを選択するHレベルの信号をワード線WL2に供給すると、nチャネルトランジスタNT119およびNT120のゲートの電位がHレベルに上昇するので、nチャネルトランジスタNT119およびNT120はオン状態になる。これにより、ビット線対BL2および/BL2を介して、デュアルポートSRAMセル116にデータの書き込みおよび読み出しを行うことが可能となる。この場合、ワード線WL1にHレベルの信号を供給したとしても、ビット線対BL2および/BL2は活性化されないとともに、ワード線WL2にHレベルの信号を供給したとしても、ビット線対BL1および/BL1は活性化されないので、一方のポートから所定のデュアルポートSRAMセル116にアクセスしている間に他方のポートから所定のデュアルポートSRAMセル116以外のデュアルポートSRAMセル116にアクセスすることができる。このように

、デュアルポートSRAMセル116を用いた半導体記憶装置では、異なる2つのデュアルポートSRAMセル116に対して、ビット線対BL1および/BL1と、ビット線対BL2および/BL2との2つの異なる系統から同時にデータの書き込みおよび読み出しを行うことができるので、半導体記憶装置に対して、2つの異なる系統から同時にアクセスすることが可能となる。これにより、一方の系統からのアクセス中に、他方の系統からのアクセスがウェイト状態になるのを抑制することができるので、半導体記憶装置の動作速度を向上することができる。

特開平5−109279号公報

上記目的を達成するために、この発明の一の局面における半導体記憶装置は、互いに交差するように配置された複数のビット線および複数のワード線と、ビット線とワード線とに接続され、データの入力および出力を行うための単一のポートを有するシングルポートSRAMセルと、ワード線に接続され、ロウアドレスを選択する第1ロウデコーダおよび第2ロウデコーダと、ビット線に接続され、カラムアドレスを選択する第1カラムデコー

ダおよび第2カラムデコーダとを備えている。また、ワード線は、複数のローカルワード線に分割されている。

上記一の局面による半導体記憶装置では、第1ロウデコーダおよび第2ロウデコーダと、第1カラムデコーダおよび第2カラムデコーダとを設けるとともに、ワード線を複数のローカルワード線に分割することによって、第1ロウデコーダおよび第1カラムデコーダにより選択されたアドレスと、第2ロウデコーダおよび第2カラムデコーダにより選択されたアドレスとに対応するローカルワード線のみを活性化することができる。これにより、別々のアドレス(カラムアドレス)に対応した2つの異なるローカルワード線を、それぞれ、同時に活性化することができる。このため、同時に活性化された2つの異なるローカルワード線が接続される2つのシングルポートSRAMセルを、それぞれ、同時に活性化することができる。これにより、2つのシングルポートSRAMセルに接続される2つの異なるビット線のみを同時に活性化することができるので、2つの異なるビット線を介して2つのシングルポートSRAMセルに、それぞれ、同時にデータの書き込みおよび読み出しを行うことができる。このため、半導体記憶装置に対して、2つの異なる系統から同時にアクセスすることが可能になる。その結果、一方の系統からのアクセス中に、他方の系統からのアクセスがウェイト状態になるのを抑制することができるので、半導体記憶装置の動作速度を向上することができる。

また、上記一の局面では、ワード線を複数のローカルワード線に分割することによって、第1ロウデコーダおよび第2ロウデコーダにより選択されたロウアドレスと、第1カラムデコーダおよび第2カラムデコーダにより選択されたカラムアドレスとに対応するローカルワード線のみを活性化することができるので、分割しないワード線を用いた従来の半導体記憶装置と異なり、1本のワード線が活性化するのに伴って全てのビット線が活性化するのを抑制することができる。これにより、ワード線が活性化するのに伴って活性化されるビット線の数を低減することができるので、その分、半導体記憶装置の消費電力を低減することができる。また、シングルポートSRAMセルを用いて半導体記憶装置を構成することによって、デュアルポートSRAMセルを用いて半導体記憶装置を構成する場合に比べて、ビット線の数およびトランジスタの数が少ない分、シングルポートSRAMセルが形成されるメモリセルアレイ領域の面積を小さくすることができる。その結果、デュアルポートSRAMセルを用いて半導体記憶装置を構成する場合に比べて、半導体記憶装置をより小型化することができる。

上記一の局面による半導体記憶装置において、好ましくは、ローカルワード線は、第1ロウデコーダおよび第1カラムデコーダのアドレス選択信号と、第2ロウデコーダおよび第2カラムデコーダのアドレス選択信号とに応答して活性化される。このように構成すれば、容易に、第1ロウデコーダおよび第1カラムデコーダにより選択されたアドレスと、第2ロウデコーダおよび第2カラムデコーダにより選択されたアドレスとに対応するローカルワード線のみを活性化することができる。これにより、容易に、別々のアドレス(カラムアドレス)に対応した2つの異なるローカルワード線を、それぞれ、同時に活性化することができる。

上記一の局面による半導体記憶装置において、好ましくは、ワード線は、第1ロウデコーダおよび第1カラムデコーダにより選択された第1アドレスと、第2ロウデコーダおよび第2カラムデコーダにより選択された第2アドレスとの各々に対応する2つのローカルワード線が、それぞれ、同時に活性化するように構成されている。このように構成すれば、同時に活性化された第1アドレスのローカルワード線および第2アドレスのローカルワード線の各々に接続される2つのシングルポートSRAMセルを、同時に活性化することができる。これにより、2つのシングルポートSRAMセルの各々に接続される2つの異なるビット線を介して、2つのシングルポートSRAMセルに、それぞれ、同時にデータ

の書き込みおよび読み出しを行うことができる。このため、容易に、半導体記憶装置に対して、2系統から同時にアクセスすることが可能になる。

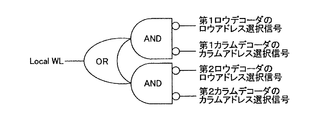

上記一の局面による半導体記憶装置において、好ましくは、第1ロウデコーダおよび第1カラムデコーダのアドレスを選択する2つの信号の論理積と、第2ロウデコーダおよび第2カラムデコーダのアドレスを選択する2つの信号の論理積との少なくとも一方の論理積を取って活性化した信号を、ローカルワード線に供給するサブデコード回路をさらに備えている。このように構成すれば、第1ロウデコーダおよび第1カラムデコーダからアドレス選択信号を対応するサブデコード回路に供給するとともに、第2ロウデコーダおよび第2カラムデコーダからアドレス選択信号を対応するサブデコード回路に供給することにより、容易に、第1ロウデコーダおよび第1カラムデコーダと、第2ロウデコーダおよび第2カラムデコーダとにより選択された2つのアドレスのローカルワード線のみを活性化することができる。

この場合、好ましくは、サブデコード回路は、ローカルワード線毎に設けられており、ビット線の延びる方向に沿って隣接する2つのサブデコード回路は、互いに、サブデコード回路を構成するトランジスタの一部を共有している。このように構成すれば、1つのサブデコード回路を構成するトランジスタの数を低減することができるので、その分、サブデコード回路の大きさを小さくすることができる。

上記一の局面による半導体記憶装置において、好ましくは、実質的に同時に入力した所定の容量のデータを所定のビット単位毎に別サイクル、かつ、別アドレスに書き込むためのアクセス手段をさらに備えている。このように構成すれば、容易に、半導体記憶装置に対して同時に入力した所定の容量のデータを所定のビット単位毎に別々のサイクルで書き込むことができるとともに、同時に入力した所定の容量のデータを所定のビット単位毎に別々のアドレスのシングルポートSRAMセルに書き込むことができる。

この場合において、好ましくは、アクセス手段は、所定のビット単位毎に、個別にデータの書き込みまたは読み出しを行う。このように構成すれば、所定のビット単位のデータの書き込み中に、書き込みを行うビット単位以外のビット単位のデータの読み出しを行うことができる。

以下、本発明の実施形態を図面に基づいて説明する。

(第1実施形態)

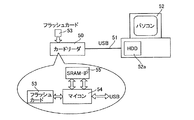

図1は、本発明の第1実施形態による半導体記憶装置(SRAM−IP)を含むカードリーダの構成を示した模式図である。この第1実施形態によるSRAM−IPを含むカードリーダ50は、図1に示すように、USBケーブル51を介してパーソナルコンピュータ(以下、「パソコン」という)52に接続されている。このパソコン52は、データを記憶するためのハードディスク52aを備えている。また、カードリーダ50は、データの記録媒体であるフラッシュカード53を装着することができるように構成されている。また、カードリーダ50は、マイクロコンピュータ(以下、「マイコン」という)54と、SRAM−IP(intellectual property)55とを備えている。ここで、SRAM−IP55は、チップ内に組み込まれるSRAMの機能ブロックを意味する。このSRAM−IP55は、パソコン52のハードディスク52aおよびフラッシュカード53から出力されたデータを一時的にストックする機能を有する。なお、SRAM−IP55の詳細については後述する。また、マイコン54は、パソコン52のハードディスク52aとフラッシュカード53およびSRAM−IP55との間のデータのやり取りを制御するために設けられている。

また、第1実施形態によるSRAM−IP55を含むカードリーダ50の動作としては、フラッシュカード53からパソコン52のハードディスク52aにデータを転送する場合には、まず、フラッシュカード53に記録されたデータが、カードリーダ50のマイコン54に出力される。マイコン54に出力されたデータは、マイコン54がSRAM−IP55にアクセスすることにより、SRAM−IP55に書き込まれる。そして、SRAM−IP55に書き込まれたデータは、マイコン54がSRAM−IP55にアクセスすることにより、SRAM−IP55から読み出される。SRAM−IP55から読み出されたデータは、マイコン54およびUSBケーブル51を介してパソコン52に出力される。そして、パソコン52に出力されたデータは、パソコン52のハードディスク52aに記憶される。

一方、パソコン52のハードディスク52aからフラッシュカード53にデータを転送する場合には、まず、パソコン52のハードディスク52aに記録されたデータが、USBケーブル51を介して、カードリーダ50のマイコン54に出力される。マイコン54に出力されたデータは、マイコン54がSRAM−IP55にアクセスすることにより、SRAM−IP55に書き込まれる。そして、SRAM−IP55に書き込まれたデータは、マイコン54がSRAM−IP55にアクセスすることにより、SRAM−IP55から読み出される。SRAM−IP55から読み出されたデータは、マイコン54からフラッシュカード53に出力されることにより、フラッシュカード53に記録される。

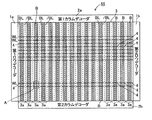

図2は、本発明の第1実施形態による半導体記憶装置(SRAM−IP)の構成を示した平面図である。図3は、図2に示した第1実施形態による半導体記憶装置(SRAM−IP)のサブデコード回路の論理回路を示した図である。図4は、図2に示した第1実施形態による半導体記憶装置(SRAM−IP)の回路図である。なお、図4に示した回路図は、図2中の破線で囲った領域Aの回路図に相当する。図5は、図4に示した第1実施形態による半導体記憶装置(SRAM−IP)の回路図のシングルポートSRAMセル部分を示した拡大回路図である。次に、図2〜図5を参照して、本発明の第1実施形態による半導体記憶装置(SRAM−IP)の構成について説明する。

この第1実施形態によるSRAM−IP55は、図2に示すように、ロウアドレスを選択する2つの第1ロウデコーダ1aおよび第2ロウデコーダ1bと、カラムアドレスを選択する2つの第1カラムデコーダ2aおよび第2カラムデコーダ2bとを備えている。また、SRAM−IP55は、シングルポートSRAMセルなどが形成されるメモリセルアレイ領域3を備えている。このメモリセルアレイ領域3は、16個のブロック3aに分割されている。また、メモリセルアレイ領域3には、互いに交差するように複数のビット線対BLおよび/BLと、複数のワード線WLとが配置されている。なお、図2では、メモリセルアレイ領域3の1つのブロック3aに対して1組のビット線対BLおよび/BLのみを示したが、第1実施形態では、1つのブロック3aに対して32組のビット線対BLおよび/BLが設けられている。また、図2では、ワード線WLの一部のみを示したが、第1実施形態では、128本のワード線WLが設けられている。

ここで、第1実施形態では、各ワード線WLは、メモリセルアレイ領域3の16個に分割されたブロック3aに対応して16本のローカルワード線4に分割されている。また、図2中の斜線領域Bには、図3に示すような入力が反転されたAND−OR回路からなる論理回路を構成するサブデコード回路5aおよび5b(図4参照)が形成されている。また、図3の論理回路のうちの一方のAND回路には、第1ロウデコーダ1a(図2参照)のロウアドレス選択信号および第1カラムデコーダ2aのカラムアドレス選択信号が入力され、他方のAND回路には、第2ロウデコーダ1bのロウアドレス選択信号および第2カラムデコーダ2bのカラムアドレス選択信号が入力される。これにより、第1ロウデコ

ーダ1a(図2参照)のロウアドレス選択信号および第1カラムデコーダ2aのカラムアドレス選択信号の論理積と、第2ロウデコーダ1bのロウアドレス選択信号および第2カラムデコーダ2bのカラムアドレス選択信号の論理積とのうちのいずれか一方の論理積を取って活性化した信号が、OR回路からローカルワード線4(図2参照)に出力される。具体的には、第1ロウデコーダ1a(図2参照)のロウアドレス選択信号および第1カラムデコーダ2aのカラムアドレス選択信号が共にLレベルの場合、または、第2ロウデコーダ1bのロウアドレス選択信号および第2カラムデコーダ2bのカラムアドレス選択信号が共にLレベルの場合には、OR回路からローカルワード線4(図2および図4参照)にHレベルの信号が出力される。

また、SRAM−IP55のメモリセルアレイ領域3(図2参照)の1つのブロック3aの斜線領域Bには、図4に示すように、各ローカルワード線4毎に、1つのサブデコード回路5a(5b)が設けられている。また、サブデコード回路5aおよび5bは、ビット線対BLおよび/BLの延びる方向に沿って設けられている。このサブデコード回路5aおよび5bの両側には、複数のビット線対BLおよび/BLが配置されている。また、ビット線対BLおよび/BLに交差するように複数のローカルワード線4が設けられている。また、サブデコード回路5aおよび5bは、それぞれ、異なるローカルワード線4に接続されている。なお、図4では、5組のビット線対BLおよび/BLのみを示したが、第1実施形態では、メモリセルアレイ領域3(図2参照)の1つのブロック3aに対して32組のビット線対BLおよび/BLが設けられている。また、図4では、2本のローカルワード線4のみを示したが、第1実施形態では、1つのブロック3aに対して、128本のローカルワード線4が設けられている。また、図4では、2つのサブデコード回路5aおよび5bのみを示したが、第1実施形態では、128本設けられたローカルワード線4のそれぞれに対応して128個のサブデコード回路5a(5b)が設けられている。

また、図4に示すように、サブデコード回路5aは、4つのnチャネルトランジスタ(nチャネルトランジスタNT1〜NT4)と、4つのpチャネルトランジスタ(pチャネルトランジスタPT1〜PT4)とから構成されている。nチャネルトランジスタNT1のソースは、接地されており、ゲートには、第1ロウデコーダ1a(図2参照)からロウアドレス選択信号ROW11が供給される。また、nチャネルトランジスタNT1のドレインは、nチャネルトランジスタNT2のソースに接続されている。また、nチャネルトランジスタNT2のゲートには、第2カラムデコーダ2b(図2参照)のカラムアドレス選択信号CL2が供給される。また、nチャネルトランジスタNT2のドレインは、pチャネルトランジスタPT1のドレインに接続されている。また、nチャネルトランジスタNT2のドレインとpチャネルトランジスタPT1のドレインとの間のノードND2は、ローカルワード線4に接続されている。また、pチャネルトランジスタPT1のゲートには、第1ロウデコーダ1a(図2参照)からロウアドレス選択信号ROW11が供給される。また、pチャネルトランジスタPT1のソースは、pチャネルトランジスタPT2のドレインに接続されている。pチャネルトランジスタPT2のゲートには、第1カラムデコーダ2a(図2参照)のカラムアドレス選択信号CL1が供給される。また、pチャネルトランジスタPT2のソースには、正電圧Vccが供給される。

また、nチャネルトランジスタNT3のソースは、接地されており、ゲートには、第1カラムデコーダ2a(図2参照)のカラムアドレス選択信号CL1が供給される。また、nチャネルトランジスタNT3のドレインは、nチャネルトランジスタNT4のソースに接続されている。nチャネルトランジスタNT3のドレインと、nチャネルトランジスタNT4のソースとの間のノードND3は、nチャネルトランジスタNT1のドレインとnチャネルトランジスタNT2のソースとの間のノードND1と接続されている。また、nチャネルトランジスタNT4のゲートには、第2ロウデコーダ1b(図2参照)からロウアドレス選択信号ROW21が供給される。また、nチャネルトランジスタNT4のドレ

インは、pチャネルトランジスタPT3のドレインに接続されている。また、nチャネルトランジスタNT4のドレインと、pチャネルトランジスタPT3のドレインとの間のノードND4は、ローカルワード線4に接続されている。また、pチャネルトランジスタPT3のゲートには、第2ロウデコーダ1b(図2参照)のロウアドレス選択信号ROW21が供給される。また、pチャネルトランジスタPT3のソースは、pチャネルトランジスタPT4のドレインに接続されている。pチャネルトランジスタPT4のゲートには、第2カラムデコーダ2b(図2参照)からカラムアドレス選択信号CL2が供給される。また、pチャネルトランジスタPT4のソースには、正電圧Vccが供給される。また、ビット線対BLおよび/BLの延びる方向に沿って、サブデコード回路5aに隣接するように別のサブデコード回路5bが設けられている。このサブデコード回路5bの構成は、上記したサブデコード回路5aの構成と同様である。

ここで、第1実施形態では、サブデコード回路5aとサブデコード回路5bとは、互いに、pチャネルトランジスタPT2とpチャネルトランジスタPT4とを共有している。具体的には、サブデコード回路5aにおけるpチャネルトランジスタPT2は、サブデコード回路5bにおけるpチャネルトランジスタPT4に相当する。また、サブデコード回路5aにおけるpチャネルトランジスタPT4は、サブデコード回路5bにおけるpチャネルトランジスタPT2に相当する。

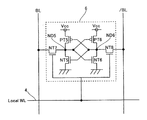

また、ローカルワード線4と、ビット線対BLおよび/BLとが交差する位置には、それぞれ、1つのシングルポートSRAMセル6が配置されている。このシングルポートSRAMセル6は、ビット線対BLおよび/BLと、ローカルワード線4とに接続されている。また、シングルポートSRAMセル6は、図5に示すように、4つのnチャネルトランジスタ(nチャネルトランジスタNT5〜NT8)および2つのpチャネルトランジスタ(pチャネルトランジスタPT5およびPT6)の合計6つのトランジスタを備えている。nチャネルトランジスタNT5のソースは、接地されており、ドレインは、pチャネルトランジスタPT5のドレインに接続されている。また、pチャネルトランジスタPT5のソースには、正電圧Vccが供給される。

また、nチャネルトランジスタNT6のソースは、接地されており、ドレインは、pチャネルトランジスタPT6のドレインに接続されている。また、nチャネルトランジスタNT6のドレインとpチャネルトランジスタPT6のドレインとの間のノードND6には、nチャネルトランジスタNT5およびpチャネルトランジスタPT5のゲートが接続されている。また、pチャネルトランジスタPT6のソースには、正電圧Vccが供給される。また、nチャネルトランジスタNT6およびpチャネルトランジスタPT6のゲートは、nチャネルトランジスタNT5のドレインとpチャネルトランジスタPT5のドレインとの間のノードND5に接続されている。

また、nチャネルトランジスタNT7のソースまたはドレインの一方は、ノードND5に接続されており、ソースまたはドレインの他方は、ビット線BLに接続されている。また、nチャネルトランジスタNT8のソースまたはドレインの一方は、ノードND6に接続されており、ソースまたはドレインの他方は、反転ビット線/BLに接続されている。また、nチャネルトランジスタNT7およびNT8のゲートは、ローカルワード線4に接続されている。これらのnチャネルトランジスタNT7およびNT8によって、シングルポートSRAMセル6の単一のポートが構成されている。

図6は、本発明の第1実施形態による半導体記憶装置(SRAM−IP)の動作を説明するための平面図である。次に、図6を参照して、本発明の第1実施形態によるSRAM−IPの動作について説明する。

本発明の第1実施形態によるSRAM−IP55の動作としては、図6に示すように、第1ロウデコーダ1aからロウアドレス選択信号ROW11が出力されるとともに、第1カラムデコーダ2aからカラムアドレス選択信号CL1が出力される。そして、この第1ロウデコーダ1aのロウアドレス選択信号ROW11と、第1カラムデコーダ2aのカラムアドレス選択信号CL1とに応答して、第1アドレスのローカルワード線4aがHレベルの電位になる。その一方で、第2ロウデコーダ1bからロウアドレス選択信号ROWnnが出力されるとともに、第2カラムデコーダ2bからカラムアドレス選択信号CLnが出力される。そして、この第2ロウデコーダ1bのロウアドレス選択信号ROWnnと、第2カラムデコーダ2bのカラムアドレス選択信号CLnとに応答して、第2アドレスのローカルワード線4bがHレベルの電位になる。

このように、第1実施形態では、第1ロウデコーダ1aおよび第1カラムデコーダ2aにより選択された第1アドレスと、第2ロウデコーダ1bおよび第2カラムデコーダ2bにより選択された第2アドレスとの各々に対応する2つのローカルワード線4aおよび4bを、同時にHレベルの電位にすることが可能である。これにより、ローカルワード線4aおよび4bと、選択された2組のビット線対BLおよび/BLとの間に配置された2つのシングルポートSRAMセル6に対して、同時にアクセスすることが可能となる。ただし、この第1実施形態によるSRAM−IP55では、同じビット線対BLおよび/BLに繋がる2つのシングルポートSRAMセル6には、同時にアクセスすることはできず、ビット線対BLおよび/BLが異なる2つのシングルポートSRAMセル6についてのみアクセス可能である。つまり、第1実施形態では、カラムアドレスが異なる2つのシングルポートSRAMセル6について同時にアクセス可能である。

次に、図4〜図6を参照して、第1ロウデコーダ1a、第2ロウデコーダ1b、第1カラムデコーダ2aおよび第2カラムデコーダ2bにより選択されたローカルワード線4がHレベルの電位になる際のサブデコード回路5aおよびシングルポートSRAMセル6の動作について説明する。まず、初期状態では、図6に示した第1ロウデコーダ1a、第2ロウデコーダ1b、第1カラムデコーダ2aおよび第2カラムデコーダ2bから、それぞれ、図4に示すように、Hレベルの信号ROW11、ROW21、CL1およびCL2が、サブデコード回路5aに入力されている。これにより、nチャネルトランジスタNT1〜NT4およびpチャネルトランジスタPT1〜PT4のゲートの電位は、Hレベルになるので、nチャネルトランジスタNT1〜NT4はオン状態になるとともに、pチャネルトランジスタPT1〜PT4はオフ状態になる。このため、ノードND2およびノードND4には、nチャネルトランジスタNT1〜NT4を介して接地電位(GND)が供給されるので、ノードND2およびノードND4の電位はLレベルになる。これにより、初期状態では、ローカルワード線4の電位はLレベルになっている。また、この初期状態では、ローカルワード線4の電位がLレベルであることにより、シングルポートSRAMセル6(図5参照)のnチャネルトランジスタNT7およびNT8がオフ状態になっている。これにより、シングルポートSRAMセル6に対して、ビット線対BLおよび/BLからデータの書き込みおよび読み出しができない状態になっているので、初期状態では、ビット線対BLおよび/BLは不活性な状態になっている。

次に、第1ロウデコーダ1a(図6参照)からサブデコード回路5a(図4参照)に入力されているロウアドレス選択信号ROW11がLレベルになる。これにより、nチャネルトランジスタNT1およびpチャネルトランジスタPT1のゲートの電位はLレベルになるので、nチャネルトランジスタNT1はオフ状態になるとともに、pチャネルトランジスタPT1はオン状態になる。その一方で、第1カラムデコーダ2a(図6参照)からサブデコード回路5a(図4参照)に入力されているカラムアドレス選択信号CL1がLレベルになる。これにより、nチャネルトランジスタNT3およびpチャネルトランジスタPT2のゲートの電位はLレベルになるので、nチャネルトランジスタNT3がオフ状

態になるとともに、pチャネルトランジスタPT2がオン状態になる。

このとき、nチャネルトランジスタNT2およびNT4は、オン状態に保持されるとともに、pチャネルトランジスタPT3およびPT4は、オフ状態に保持されているので、pチャネルトランジスタPT1およびPT2を介して、ノードND2に正電圧Vccが供給されることにより、ノードND2の電位はHレベルに上昇する。これにより、ローカルワード線4の電位はHレベルになる。ローカルワード線4の電位がHレベルになると、図5に示すように、シングルポートSRAMセル6のnチャネルトランジスタNT7およびNT8のゲートの電位がHレベルに上昇するので、nチャネルトランジスタNT7およびNT8はオン状態になる。これにより、ビット線対BLおよび/BLからシングルポートSRAMセル6にデータの書き込みおよび読み出しを行うことが可能となるので、ビット線対BLおよび/BLが活性化される。

第1実施形態では、上記のように、第1ロウデコーダ1aおよび第2ロウデコーダ1bと、第1カラムデコーダ2aおよび第2カラムデコーダ2bとを設けるとともに、ワード線WLを複数のワード線4に分割することによって、第1ロウデコーダ1aおよび第1カラムデコーダ2aにより選択されたアドレスと、第2ロウデコーダ1bおよび第2カラムデコーダ2bにより選択されたアドレスとに対応するローカルワード線4aおよび4bのみをHレベルの電位にすることができる。これにより、別々のアドレス(カラムアドレス)に対応した2つの異なるローカルワード線4aおよび4bを、それぞれ、同時にHレベルの電位にすることができる。このため、同時にHレベルの電位にされた2つの異なるローカルワード線4aおよび4bが接続される2つのシングルポートSRAMセル6のnチャネルトランジスタNT7およびNT8を、同時にオン状態にすることができる。これにより、2つのシングルポートSRAMセル6に接続される2組の異なるビット線対BLおよび/BLのみを同時に活性化することができるので、2組の異なるビット線対BLおよび/BLを介して、2つのシングルポートSRAMセル6に、それぞれ、同時にデータの書き込みおよび読み出しを行うことができる。このため、SRAM−IP55に対して、2つの異なる系統から同時にアクセスすることが可能になる。その結果、一方の系統からのアクセス中に、他方の系統からのアクセスがウェイト状態になるのを抑制することができるので、SRAM−IP55の動作速度を向上させることができる。これにより、図1に示したカードリーダ50において、パソコン52のハードディスク52aとフラッシュカード53との間でデータのやり取りをする場合に、SRAM−IP55に対して、データを書き込むためのアクセスと、SRAM−IP55に書き込まれたデータを読み出すためのアクセスとを同時に行うことができるので、カードリーダ50の動作速度を向上させることができる。

また、第1実施形態では、ワード線WLを複数のローカルワード線4に分割することによって、第1ロウデコーダ1aおよび第2ロウデコーダ1bにより選択されたロウアドレスと、第1カラムデコーダ2aおよび第2カラムデコーダ2bにより選択されたカラムアドレスとに対応するローカルワード線4aおよび4bのみをHレベルの電位にすることができるので、分割しないワード線WLを用いた従来の半導体記憶装置と異なり、1本のワード線WLの電位がHレベルになるのに伴って全てのビット線対BLおよび/BLが活性化するのを抑制することができる。これにより、ワード線WLの電位がHレベルになるのに伴って活性化されるビット線対BLおよび/BLの数を低減することができるので、その分、SRAM−IP55の消費電力を低減することができる。その結果、第1実施形態によるSRAM−IP55を含むカードリーダ50(図1参照)の消費電力を低減することができる。

また、第1実施形態では、シングルポートSRAMセル6を用いてSRAM−IP55を構成することによって、デュアルポートSRAMセルを用いてSRAM−IP55を構

成する場合に比べて、ビット線対BLおよび/BLの数、および、トランジスタの数が少ない分、シングルポートSRAMセル6が形成されるメモリセルアレイ領域3の面積を小さくすることができる。その結果、デュアルポートSRAMセルを用いてSRAM−IP55を構成する場合に比べて、SRAM−IP55をより小型化することができる。

また、第1実施形態では、ビット線対BLおよび/BLの伸びる方向に沿って隣接する2つのサブデコード回路5aおよび5bが、互いに、サブデコード回路5a(5b)を構成するpチャネルトランジスタPT2およびPT4を共有することによって、サブデコード回路5a(5b)を構成するトランジスタの数を低減することができるので、その分、サブデコード回路5aおよび5bの大きさを小さくすることができる。

(第2実施形態)

図7は、本発明の第2実施形態による半導体記憶装置(SRAM−IP)の構成を示した平面図である。図7を参照して、本発明の第2実施形態の構成について説明する。この第2実施形態では、上記第1実施形態と異なり、同時に入力した所定の容量のデータを1バイト(8ビット)単位毎に別サイクルで、かつ、別アドレスに書き込むためのアクセス手段を有する半導体記憶装置(SRAM−IP)について説明する。

この第2実施形態によるSRAM−IP65の構成としては、図7に示すように、SRAM−IP65の第2カラムデコーダ2bに、データの入力および出力を行うための4つ(4バイト分)の入出力回路部10が接続されている。なお、図7では、図面の簡略化のため1つ(1バイト分)の入出力回路部10の構成のみを示している。この入出力回路部10は、本発明の「アクセス手段」の一例である。また、各々の入出力回路部10は、それぞれ、8つの回路部11〜18を含んでいる。この8つの回路部11〜18は、それぞれ、ラッチ回路L0a〜L7aおよびL0b〜L7bと、センスアンプSA0〜SA7とを備えている。また、ラッチ回路L0a〜L7aは、それぞれ、入力回路DIN0〜DIN7に接続されているとともに、データ線DL0〜DL7を介して第2カラムデコーダ2bに接続されている。また、センスアンプSA0〜SA7は、それぞれ、データ線DL0〜DL7を介して第2カラムデコーダ2bに接続されているとともに、ラッチ回路L0b〜L7bを介して、出力回路DOUT0〜DOUT7に接続されている。また、各々の入出力回路部10には、それぞれ、ライトイネーブル信号WE0〜WE3が供給される。この入出力回路部10に供給されるライトイネーブル信号WE0〜WE3は、それぞれ、ラッチ回路L0a〜L7aに入力されるように構成されている。また、ラッチ回路L0a〜L7aは、入出力回路部10の回路部11〜18に入力されたデータを一時的に保持するために設けられている。また、各々のラッチ回路L0a〜L7aは、Lレベルのライトイネーブル信号WE0〜WE3が入力された場合には、保持しているデータをデータ線DL0〜DL7に出力する一方、Hレベルのライトイネーブル信号WE0〜WE3が入力された場合には、保持しているデータをデータ線DL0〜DL7に出力しないように構成されている。また、センスアンプSA0〜SA7は、シングルポートSRAMセル(図示せず)からの出力信号を増幅する機能を有する。また、ラッチ回路L0b〜L7bの制御は、ライト制御信号や入力ラッチ信号と同様に、バイト単位毎に制御されている。これにより、リードしたデータを、データをリードしたサイクルの次のサイクルやさらに次のサイクルまで出力し続けることも可能である。なお、これ以外のSRAM−IP65の構成は、上記した第1実施形態によるSRAM−IP55の構成と同様である。

次に、第2実施形態によるSRAM−IP65の動作としては、まず、外部からSRAM−IP65に同時に所定の容量のデータが入力されると、その所定の容量のデータはバイト単位毎に4つのデータD0〜D3に分割される。そして、バイト単位毎に4つに分割されたデータD0〜D3は、それぞれ、4つの入出力回路部10の回路部11〜18に入力される。具体的には、8ビットの4つのデータD0〜D3は、それぞれ、1バイト目〜

4バイト目の入力回路DIN0〜DIN7を介して回路部11〜18の各々のラッチ回路L0a〜L7aに入力される。このとき、4つの入出力回路部10の全てのラッチ回路L0a〜L7aには、Hレベルのライトイネーブル信号WE0〜WE3を入力する。これにより、データD0〜D3は、4つの入出力回路部10の各々の回路部11〜18のラッチ回路L0a〜L7aで一旦保持される。

この際、第2実施形態では、ライトイネーブル信号WE0〜WE3を制御することにより、同時に入力された所定の容量のデータをバイト単位毎に分割したデータD0〜D3を、それぞれ、別サイクルで、かつ、別アドレスに書き込むことが可能である。具体的には、まず、第1サイクルにおいて、データD0〜D3のうちD0のみを第1アドレスに書き込む場合には、第1ロウデコーダ1aおよび第1カラムデコーダ1bにより第1アドレスのシングルポートSRAMセル(図示せず)を活性化させる。そして、この状態で、データD0を保持している1バイト目の入出力回路部10にLレベルのライトイネーブル信号WE0を入力するとともに、2バイト目〜4バイト目の他の入出力回路部10にHレベルのライトイネーブル信号WE1〜WE3をそれぞれ入力する。これにより、Lレベルのライトイネーブル信号WE0が入力された1バイト目の入出力回路部10のラッチ回路L0a〜L7aから、それぞれ、対応するデータ線DL0〜DL7に8ビットのデータD0が出力される一方、Hレベルのライトイネーブル信号WE1〜WE3がそれぞれ入力された2バイト目〜4バイト目の入出力回路部10の各々のラッチ回路L0a〜L7aからデータD1〜D3は出力されない。そして、1バイト目のデータ線DL0〜DL7に出力された8ビットのデータD0は、第2カラムデコーダ2bとビット線対BLおよび/BLとを介して、活性化された第1アドレスのシングルポートSRAMセル(図示せず)に書き込まれる。

そして、次の第2サイクルにおいて、第1アドレスと異なる第2アドレスのシングルポートSRAMセル(図示せず)を活性化させるとともに、Lレベルのライトイネーブル信号WE1をデータD1を保持する2バイト目の入出力回路部10のラッチ回路L0a〜L7aに入力する。これにより、第1サイクルでは出力されなかった8ビットのデータD1が、データD1を保持する2バイト目の入出力回路部10のラッチ回路L0a〜L7aから対応するデータ線DL0〜DL7に出力される。そして、データ線DL0〜DL7に出力された8ビットのデータD1は、第2カラムデコーダ2bと、ビット線対BLおよび/BLとを介して、活性化された第2アドレスのシングルポートSRAMセル(図示せず)に書き込まれる。さらに次の第3サイクルでは、第2アドレスと異なる第3アドレスのシングルポートSRAMセル(図示せず)を活性化させるとともに、Lレベルのライトイネーブル信号WE2をデータD2を保持する3バイト目の入出力回路部10のラッチ回路L0a〜L7aに入力することにより、8ビットのデータD2が第3アドレスのシングルポートSRAMセル(図示せず)に書き込まれる。さらに次の第4サイクルでは、第3アドレスと異なる第4アドレスのシングルポートSRAMセル(図示せず)を活性化させるとともに、Lレベルのライトイネーブル信号WE3をデータD3を保持する4バイト目の入出力回路部10のラッチ回路L0a〜L7aに入力することにより、8ビットのデータD3が第4アドレスのシングルポートSRAMセル(図示せず)に書き込まれる。

このように、第2実施形態では、サイクル毎に異なるアドレスのシングルポートSRAMセルを活性化するとともに、1バイト目〜4バイト目の4つの入出力回路部10の各々のラッチ回路L0a〜L7aに、順次、Lレベルのライトイネーブル信号WE0〜WE3を入力することにより、SRAM−IP65に外部から同時に入力された所定の容量のデータをバイト単位毎に別サイクルで、かつ、別アドレスに書き込むことができる。

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範

囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

たとえば、上記第1実施形態では、本発明による半導体記憶装置をチップ内に組み込まれる機能ブロックとしてのSRAM−IPに適用した例について説明したが、本発明はこれに限らず、通常のSRAMチップに適用してもよい。

また、上記実施形態では、本発明による半導体記憶装置(SRAM−IP)を含むカードリーダについて説明したが、本発明はこれに限らず、本発明による半導体記憶装置(SRAM−IP)を、パソコンのUSBポートに直接差し込むことにより、パソコンからデータの書き込みおよび読み出しを行うことが可能な、いわゆるUSBメモリに含ませるようにしてもよい。

また、上記第1実施形態では、サブデコード回路5aとサブデコード回路5bとが、互いに、pチャネルトランジスタPT2とpチャネルトランジスタPT4とを共有するようにしたが、本発明はこれに限らず、ビット線の延びる方向に沿って隣接する2つのサブデコード回路が、互いに、サブデコード回路を構成するトランジスタの一部を共有しないように構成してもよい。

また、上記第2実施形態では、外部から同時に入力した所定の容量のデータをバイト単位毎に分割したデータD0〜D3を、それぞれ、別サイクルで、かつ、別アドレスのシングルポートSRAMセルに書き込む例について説明したが、本発明はこれに限らず、別々のサイクルで半導体記憶装置(SRAM−IP)に入力したデータを、同時にシングルポートSRAMセルに書き込むようにしてもよい。具体的には、まず、4つの入出力回路部10のラッチ回路L0a〜L7aに、それぞれ、Hレベルのライトイネーブル信号WE0〜WE3を入力する。この状態で、第1サイクルでは、1バイト目のデータD0を1つ目の入出力回路部10のラッチ回路L0a〜L7aに入力する。このとき、1バイト目の入出力回路部10のラッチ回路L0a〜L7aには、Hレベルのライトイネーブル信号WE0が入力されているので、第1サイクルでは、データD0は、1つ目の入出力回路部10のラッチ回路L0a〜L7aから対応するデータ線DL0〜DL7に出力されない。そして、次の第2サイクルでは、データD1を2バイト目の入出力回路部10のラッチ回路L0a〜L7aに入力する。このとき、2バイト目の入出力回路部10のラッチ回路L0a〜L7aには、Hレベルのライトイネーブル信号WE1が入力されているので、第2サイクルでは、データD1は、2バイト目の入出力回路部10のラッチ回路L0a〜L7aから対応するデータ線DL0〜DL7に出力されない。

そして、次の第3サイクルでは、データD2を3バイト目の入出力回路部10のラッチ回路L0a〜L7aに入力する。このとき、3バイト目の入出力回路部10のラッチ回路L0a〜L7aには、Hレベルのライトイネーブル信号WE2が入力されているので、第3サイクルでは、データD2は、3バイト目の入出力回路部10のラッチ回路L0a〜L7aから対応するデータ線DL0〜DL7に出力されない。そして、次の第4サイクルでは、データD3を4バイト目の入出力回路部10のラッチ回路L0a〜L7aに入力する。このとき、4バイト目の入出力回路部10のラッチ回路L0a〜L7aには、Hレベルのライトイネーブル信号WE3が入力されているので、第4サイクルでは、データD3は、4バイト目の入出力回路部10のラッチ回路L0a〜L7aから対応するデータ線DL0〜DL7に出力されない。そして、次の第5サイクルにおいて、1バイト目〜4バイト目の4つの入出力回路部10の各々のラッチ回路L0a〜L7aにLレベルのライトイネーブル信号WE0〜WE3を入力する。これにより、1バイト目〜4バイト目の4つの入出力回路部10のラッチ回路L0a〜L7aに保持されたデータD0〜D3は、それぞれ、対応するデータ線DL0〜DL7に同時に出力される。そして、対応するデータ線DL

0〜DL7に同時に出力されたデータD0〜D3は、第2カラムデコーダ2bと、ビット線対BLおよび/BLとを介して、所定の活性化されたシングルポートSRAMセルに書き込まれる。このように、別々のサイクルでSRAM−IPに入力したデータを、同時にシングルポートSRAMセルに書き込むことができる。

また、上記第2実施形態では、SRAM−IP65に入力された所定の容量のデータをバイト単位毎に分割して別サイクルで、かつ、別アドレスに書き込むために、4つの入出力回路部10の各々に8つの回路部11〜18を設けた例について説明したが、本発明はこれに限らず、4つの入出力回路部に8つ以外の任意の数の回路部を設けてもよい。これにより、外部からSRAM−IPに入力された所定の容量のデータを、8ビット以外の任意のビット単位毎に分割して別サイクルで、かつ、別アドレスに書き込むようにしてもよい。

また、上記第2実施形態では、4つ(4バイト分)の入出力回路部10の各々から個別に、別サイクルで、かつ、別アドレスにデータを書き込む例について説明したが、本発明はこれに限らず、4つの入出力回路部の内、たとえば、2バイト目と3バイト目の入出力回路部からシングルポートSRAMセルにデータの書き込みを行うのと同時に、1バイト目と4バイト目の入出力回路部を介してシングルポートSRAMセルからデータの読み出しを行うようにしてもよい。また、上記の場合において、バイト(8ビット)単位ではなく、1つの入出力回路部に8つ以外の任意の数の回路部を設けることによって、8ビット以外の任意のビット単位毎に、個別にデータの書き込みと読み出しを同時に行うようにしてもよい。