JP2008166330A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2008166330A JP2008166330A JP2006351039A JP2006351039A JP2008166330A JP 2008166330 A JP2008166330 A JP 2008166330A JP 2006351039 A JP2006351039 A JP 2006351039A JP 2006351039 A JP2006351039 A JP 2006351039A JP 2008166330 A JP2008166330 A JP 2008166330A

- Authority

- JP

- Japan

- Prior art keywords

- contact

- semiconductor device

- transistors

- gate

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/013—Manufacturing their source or drain regions, e.g. silicided source or drain regions

- H10D84/0133—Manufacturing common source or drain regions between multiple IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0149—Manufacturing their interconnections or electrodes, e.g. source or drain electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H10W20/069—

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

【課題】低抵抗コンタクトを維持しつつ、より微細化された半導体装置を提供する。

【解決手段】半導体装置は、トランジスタTr1、Tr2と、第1コンタクト13と、第2コンタクト10とを具備する。トランジスタTr1、Tr2は、半導体基板1上に設けられ隣接している。第1コンタクト13は、トランジスタTr1、Tr2間にセルフアライメント構造で設けられ、トランジスタTr1、Tr2の共通のソースに接続され、金属を含んでいる。第2コンタクト10は、トランジスタTr1,Tr2のドレインにそれぞれ接続され、金属を含んでいる。

【選択図】図2

【解決手段】半導体装置は、トランジスタTr1、Tr2と、第1コンタクト13と、第2コンタクト10とを具備する。トランジスタTr1、Tr2は、半導体基板1上に設けられ隣接している。第1コンタクト13は、トランジスタTr1、Tr2間にセルフアライメント構造で設けられ、トランジスタTr1、Tr2の共通のソースに接続され、金属を含んでいる。第2コンタクト10は、トランジスタTr1,Tr2のドレインにそれぞれ接続され、金属を含んでいる。

【選択図】図2

Description

本発明は、半導体装置に関し、特に微細化のための半導体装置に関する。

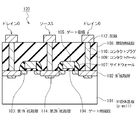

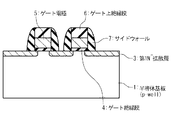

MOS(Metal−Oxide Semiconductor)トランジスタを有する半導体装置の微細化が進められている。図1は、従来の半導体装置の構成を示す断面図である。ここでは、N型のMOSトランジスタについて説明する。半導体基板(p−well)101の表面に、ソースドレインを構成するN型拡散層が配置されている。N型拡散層は、N+拡散層102、第1N−拡散層103、及び第2N−拡散層114を備える。ここで第2N−拡散層114は、コンタクト抵抗低減手段であるので、抵抗値に問題なければ省略可能である。ゲート絶縁膜104及びその上のゲート電極105が、N型拡散層に挟まれる形で半導体基板101上に配置されている。ゲート絶縁膜104及びゲート電極105の側面に、サイドウォール107が配置されている。ゲート絶縁膜104、サイドウォール107及びN型拡散層を覆うように、層間絶縁膜108が配置されている。層間絶縁膜108上の配線112とN型拡散層とを電気的に接続するためのコンタクトプラグ110が、層間絶縁膜108中に設けられたコンタクトホール109内に設けられている。

このように、従来の半導体装置では、ソース及びドレインのいずれに対しても通常のコンタクト(コンタクトプラグ110)を用いていた。ここで、コンタクトプラグ110は、通常、粒状(島状)コンタクトである。粒状コンタクトの場合、半導体装置の微細化に伴い、コンタクトサイズが小さくなり、線幅が細くなるので抵抗が上昇する。その結果、所望の電気特性を得ることが難しく、微細化が困難であった。

公知のセルフアライメント(self−alignment)構造を、微細化技術として用いることが考えられる。ゲート(ゲート電極105及びゲート絶縁膜104)同士の距離が近づくので、微細化に有効である。しかし、この場合、N+拡散層102の領域が狭くなり、ソースドレインにおけるドーパント濃度の比較的薄いN−拡散層103とコンタクトプラグ110とが接触することになる。すなわち、コンタクトプラグ110として金属プラグを用いている場合には、N−拡散層103と金属とが接触することになる。そうなると、接触部分で形成されるシリサイド層がウェルにまで到達して、ソースドレインとウェルとの間でリーク電流が発生してしまう。それを回避する方法として、金属プラグではなくポリシリコンのプラグを用いることが考えられる。しかし、その場合、ポリシリコンのプラグは金属プラグよりも抵抗値が高いので、MOSトランジスタの電気特性が悪くなる。加えて、CMOSの場合、N型のポリシリコンプラグとP型のポリシリコンプラグとを別々に形成する必要があり、工程が複雑でコスト上昇の原因となる。

関連する技術として特開平10−242419号公報に半導体装置の製造方法及び半導体装置が開示されている。この半導体装置の製造方法は、シリコン半導体基板の主表面に第1の絶縁膜を形成する工程と、この第1の絶縁膜の上に第1の導電層を形成する工程と、この第1の絶縁層の上にシリコン酸化膜を形成する工程と、上記シリコン酸化膜及び上記第1の導電層をパターニングして上面に酸化膜を有する複数のゲート電極を形成する工程と、上記ゲート電極の間の上記半導体基板の主表面に不純物を導入して複数の活性領域を形成する工程と、上記第1の絶縁膜及び上記ゲート電極を含む上記半導体基板の全面にシリコン窒化膜を形成する工程と、このシリコン窒化膜の上に第2の絶縁膜を形成する工程と、上記複数のゲート電極のうち選択された隣り合うゲート電極の間で上記第2の絶縁膜に開孔を設ける工程と、上記隣り合うゲート電極のそれぞれ側面のシリコン窒化膜の間において上記開孔から上記第1の絶縁膜の上のシリコン窒化膜及び上記第1の絶縁膜に開孔を設け、上記半導体基板の上記活性領域に至るコンタクトを形成する工程とを含むことを特徴とする。

また、特開2001−44380号公報に半導体装置およびその製造方法が開示されている。この半導体装置は、ビット線の上層にキャパシタを備えるキャパシタオーバービットライン構造を有する。半導体装置は、キャパシタと導通するソースドレイン領域を覆う下層絶縁膜と、前記下層絶縁膜の上層に形成される上層絶縁膜と、前記下層絶縁膜および前記上層絶縁膜を貫通して前記ソースドレイン領域に開口するストレージノードコンタクトとを備える。前記ソースドレイン領域は、前記ストレージノードコンタクトが開口する部分を含む全面において実質的に平坦である。

本発明の目的は、低抵抗コンタクトを維持しつつ、より微細化された半導体装置及びその製造方法を提供することにある。

また、本発明の他の目的は、コストを抑制しながら、トランジスタの集積度を向上することが可能な半導体装置及びその製造方法を提供することにある。

以下に、発明を実施するための最良の形態で使用される番号・符号を用いて、課題を解決するための手段を説明する。これらの番号・符号は、特許請求の範囲の記載と発明を実施するための最良の形態との対応関係を明らかにするために括弧付きで付加されたものである。ただし、それらの番号・符号を、特許請求の範囲に記載されている発明の技術的範囲の解釈に用いてはならない。

上記課題を解決するために、本発明の半導体装置は、二つのトランジスタ(Tr1、Tr2)と、第1コンタクト(13)と、二つの第2コンタクト(10)とを具備する。二つのトランジスタ(Tr1、Tr2)は、半導体基板(1)上に設けられ、隣接している。第1コンタクト(13)は、二つのトランジスタ(Tr1、Tr2)間にセルフアライメント構造で設けられ、二つのトランジスタ(Tr1、Tr2)の共通のソースに接続され、金属を含んでいる。二つの第2コンタクト(10)は、二つのトランジスタ(Tr1,Tr2)のドレインにそれぞれ接続され、金属を含んでいる。

本発明では、第1コンタクト(13)がセルフアライメント(自己整合型)構造を有している、すなわち、自己整合的に形成するので、低コストで二つのトランジスタ(Tr1、Tr2)の間隔を狭くすることが出来、半導体チップをより微細化することができる。

本発明では、第1コンタクト(13)がセルフアライメント(自己整合型)構造を有している、すなわち、自己整合的に形成するので、低コストで二つのトランジスタ(Tr1、Tr2)の間隔を狭くすることが出来、半導体チップをより微細化することができる。

上記の半導体装置において、第1コンタクト(13)の端部とトランジスタ(Tr1/Tr2)のゲートの端部との間隔は、第2コンタクト(10)の端部とトランジスタ(Tr1/Tr2)のゲートとの間隔よりも小さい。

本発明では、第1コンタクト(13)がセルフアライメント(自己整合型)構造を有しているので、第1コンタクト(13)端部とゲート端部との間隔は、第2コンタクト(10)端部とゲート端部との間隔と比較して小さくすることができる。それにより、半導体チップをより微細化することができる。

本発明では、第1コンタクト(13)がセルフアライメント(自己整合型)構造を有しているので、第1コンタクト(13)端部とゲート端部との間隔は、第2コンタクト(10)端部とゲート端部との間隔と比較して小さくすることができる。それにより、半導体チップをより微細化することができる。

第1コンタクト(13)は、少なくとも一つのコンタクトを有している。二つの第2コンタクト(10)の各々は、複数のコンタクトを有している。少なくとも一つのコンタクトにおける二つのトランジスタ(Tr1、Tr2)のゲート幅方向の長さは、複数のコンタクトの各々におけるゲート幅方向の長さ等しいか長い。

本発明では、第1コンタクト(13)のゲート幅方向の長さが、第2コンタクト(10)における個々のコンタクトのそれと比較して長くなっている。これにより、セルフアライメント構造によりソースにおいてN+拡散層と第1コンタクト(13)との接触幅(W)が第2コンタクト(10)と比較して小さくなっても、接触面積(接触長さL×接触幅W)を大きく保つことができ、高集積化をしながら接触抵抗の低抵抗化を実現することができる。

本発明では、第1コンタクト(13)のゲート幅方向の長さが、第2コンタクト(10)における個々のコンタクトのそれと比較して長くなっている。これにより、セルフアライメント構造によりソースにおいてN+拡散層と第1コンタクト(13)との接触幅(W)が第2コンタクト(10)と比較して小さくなっても、接触面積(接触長さL×接触幅W)を大きく保つことができ、高集積化をしながら接触抵抗の低抵抗化を実現することができる。

上記の半導体装置において、二つのトランジスタ(Tr1、Tr2)は、半導体基板(1)のウェル表面に設けられている。ソースとウェルとは略同電位であることが好ましい。

本発明では、ウェル(半導体装置1)とソースとが略同電位であるため、第1コンタクト(13)をセルフアライメント構造としたことでソースにおいてN−拡散層と第1コンタクト(13)とが接触するが、リーク電流の問題を原理的に発生しないいようにすることができる。それにより、コンタクトプラグ13として低抵抗な金属を用いることができる。略同電位とは、リーク電流の問題が発生しない程度に等しいということであり、誤差を含み得る。

本発明では、ウェル(半導体装置1)とソースとが略同電位であるため、第1コンタクト(13)をセルフアライメント構造としたことでソースにおいてN−拡散層と第1コンタクト(13)とが接触するが、リーク電流の問題を原理的に発生しないいようにすることができる。それにより、コンタクトプラグ13として低抵抗な金属を用いることができる。略同電位とは、リーク電流の問題が発生しない程度に等しいということであり、誤差を含み得る。

上記の半導体装置において、第1コンタクト(13)は、ゲート幅方向の長さがゲート長方向よりも長い形状を有することが好ましい。

これにより、接触面積(接触長さL×接触幅W)を大きく保つことができ、接触抵抗の低抵抗化を実現することができる。形状としては、ゲート幅方向に長径を有する楕円形状に例示される。

これにより、接触面積(接触長さL×接触幅W)を大きく保つことができ、接触抵抗の低抵抗化を実現することができる。形状としては、ゲート幅方向に長径を有する楕円形状に例示される。

上記の半導体装置において、第1コンタクト(13)は、矩形形状を有することが好ましい。

これにより、接触面積(接触長さL×接触幅W)をより確実に大きく保つことができ、接触抵抗の低抵抗化を実現することができる。

これにより、接触面積(接触長さL×接触幅W)をより確実に大きく保つことができ、接触抵抗の低抵抗化を実現することができる。

上記の半導体装置において、第1コンタクト(13)は、一つであることが好ましい。

これにより、

これにより、

上記課題を解決するために、本発明の半導体装置の製造方法は、(a)半導体基板(1)上に隣接する二つのトランジスタ(Tr1、Tr2)を形成する工程と、(b)半導体基板(1)と二つのトランジスタ(Tr1、Tr2)とを覆うように設けられた層間絶縁膜(8)に、二つのトランジスタ(Tr1,Tr2)の共通のソースに対応する場所に自己整合的に第1コンタクトホール(11)を、二つのトランジスタ(Tr1,Tr2)の各々のドレインに対応する場所に二つの第2コンタクトホール(9)を、それぞれ形成する工程と、(c)第1コンタクトホール(11)及び二つの第2コンタクトホール(9)を金属を含む物質で埋めるように、それぞれ第1コンタクト(13)及び二つの第2コンタクト(10)を形成する工程とを具備する。

本発明では、第1コンタクト(13)をセルフアライメント(自己整合型)的に形成するので、低コストで二つのトランジスタ(Tr1、Tr2)の間隔を狭くすることが出来、半導体チップをより微細化することができる。

本発明では、第1コンタクト(13)をセルフアライメント(自己整合型)的に形成するので、低コストで二つのトランジスタ(Tr1、Tr2)の間隔を狭くすることが出来、半導体チップをより微細化することができる。

上記の半導体装置の製造方法において、第1コンタクト(13)の端部とトランジスタ(Tr1/Tr2)のゲートの端部との間隔は、第2コンタクト(10)の端部とトランジスタ(Tr1/Tr2)のゲートとの間隔よりも小さい。

本発明では、第1コンタクト(13)がセルフアライメント(自己整合型)構造を有しているので、第1コンタクト(13)端部とゲート端部との間隔は、第2コンタクト(10)端部とゲート端部との間隔と比較して小さくすることができる。それにより、半導体チップをより微細化することができる。

本発明では、第1コンタクト(13)がセルフアライメント(自己整合型)構造を有しているので、第1コンタクト(13)端部とゲート端部との間隔は、第2コンタクト(10)端部とゲート端部との間隔と比較して小さくすることができる。それにより、半導体チップをより微細化することができる。

上記の半導体装置の製造方法において、第1コンタクト(13)は、少なくとも一つのコンタクトを有している。二つの第2コンタクト(10)の各々は、複数のコンタクトを有している。少なくとも一つのコンタクトの横断面は、複数のコンタクトの各々の横断面の和よりも大きい。

本発明では、第1コンタクト(13)の横断面が、第2コンタクト(10)の個々の横断面の和よりも大きくなっている。これにより、セルフアライメント構造によりソースにおいてN+拡散層と第1コンタクト(13)との接触幅(W)が第2コンタクト(10)と比較して小さくなっても、接触面積(接触長さL×接触幅W)を大きく保つことで、高集積化をしながら接触抵抗の低抵抗化を実現することができる。

本発明では、第1コンタクト(13)の横断面が、第2コンタクト(10)の個々の横断面の和よりも大きくなっている。これにより、セルフアライメント構造によりソースにおいてN+拡散層と第1コンタクト(13)との接触幅(W)が第2コンタクト(10)と比較して小さくなっても、接触面積(接触長さL×接触幅W)を大きく保つことで、高集積化をしながら接触抵抗の低抵抗化を実現することができる。

上記の半導体装置の製造方法において、(b)工程と(d)工程とは同時に行われ、(c)工程と(e)工程とは同時に行われることが好ましい。

これにより、コンタクトホール(11、9)を形成する工程とコンタクト(13、10)を径生成する工程をまとめることが出来、、工程にかかる時間を減少でき、コストも低減することが可能となる。

これにより、コンタクトホール(11、9)を形成する工程とコンタクト(13、10)を径生成する工程をまとめることが出来、、工程にかかる時間を減少でき、コストも低減することが可能となる。

本発明により、低抵抗コンタクトを維持しつつ、より微細化された半導体装置を提供することが可能となる。

以下、本発明の半導体装置の実施の形態に関して、添付図面を参照して説明する。ここでは、N型MOSトランジスタTr1、Tr2を有する半導体装置20に関して説明する。ただし、P型MOSトランジスタを有する場合にも、導電型を逆にすることで、同様に本発明を適用可能である。更に、N型及びP型の両方を有している場合にも、同様に本発明を適用可能である。

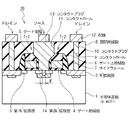

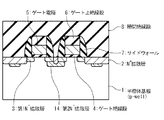

図2は、本発明の半導体装置の実施の形態の構成を示す断面図(縦断面)である。半導体装置20は、半導体基板1、N+拡散層2、第1N−拡散層3、第2N−拡散層14、ゲート絶縁膜4、ゲート電極5、ゲート上絶縁膜6、サイドウォール7、層間絶縁膜8、コンタクトホール9、コンタクトプラグ10、配線12、コンタクトホール11、コンタクトプラグ13を具備する。

半導体基板1は、P型半導体基板であり、ボロンドープP−シリコン基板に例示される。ただし、半導体基板の表面にボロンのようなP型不純物を注入することで設けられたP型ウェル(p−well)であっても良い。

ゲート絶縁膜4、及びゲート電極5は、MOSトランジスタTr1,Tr2のゲートを構成する。ゲート絶縁膜4は、半導体基板1表面のチャネル領域上に設けられている。絶縁膜であり、シリコン酸化膜に例示される。ゲート電極5は、ゲート絶縁膜4上に設けられている。電極であり、リンドープポリシリコンに例示される。ゲート上絶縁膜6は、ゲート電極5がコンタクト13と電気的に接続することを防止するためにセルフアライメント構造に必須であり、ゲート電極5上に設けられている。絶縁膜であり、シリコン窒化膜に例示される。サイドウォール7は、ゲート絶縁膜4、ゲート電極5及びゲート上絶縁膜6の側面に、それらを保護するように設けられている。絶縁膜であり、シリコン窒化膜に例示される。

N+拡散層2、第1N−拡散層3、及び第2N−拡散層14は、N型拡散層であり、MOSトランジスタTr1,Tr2のソースドレインを構成する。第1N−拡散層3は、半導体基板1表面のチャネル領域の両端部に設けられている。N+拡散層2は、チャネル領域から見て第1N−拡散層3の外側に設けられ、コンタクトプラグ10の一端と接続されている。第2N−拡散層14は、N+拡散層2の下側に設けられている。ここで、第2N−拡散層14はコンタクト形成後イオン注入で形成されるものであり、コンタクト抵抗低減手段であるので、コンタクト抵抗に問題なければ省略可能である。各N型拡散層のN型ドーパント濃度Cの大小関係は、C(N+拡散層2)>C(第1N−拡散層3)、C(N−拡散層14)である。

層間絶縁膜8は、N+拡散層2、サイドウォール7、及びゲート上絶縁膜6を覆うように設けられている。絶縁膜であり、低誘電率のシリコン酸化膜に例示される。

コンタクトホール9は、MOSトランジスタTr1,Tr2のドレインとしてのN+拡散層2と配線12とを繋ぐように層間絶縁膜8中に設けられた穴である。コンタクトプラグ10は、コンタクトホール9を充たすように設けられた配線であり、MOSトランジスタTr1,Tr2のドレインとしてのN+拡散層2と配線12とを電気的に接続する。コンタクトプラグ10は、通常(図1)のコンタクトの構造を有している。導体であり、W(タングステン)、Al(アルミニウム)、Cu(銅)のような金属膜に例示される。

配線12は、MOSトランジスタTr1,Tr2のソースドレインに関わる信号を供給又は送出する。

コンタクトホール11は、MOSトランジスタTr1,Tr2のソースとしてのN+拡散層2と配線12とを繋ぐように層間絶縁膜8中に設けられた穴である。コンタクトホール11の下部は、MOSトランジスタTr1,Tr2のゲート上絶縁膜6及びサイドウォール7により、自己整合的に形成されている。コンタクトプラグ13は、コンタクトホール11を充たすように設けられた配線であり、MOSトランジスタTr1,Tr2のソースとしてのN+拡散層2と配線12とを電気的に接続する。コンタクトプラグ13は、セルフアライメント構造を有している。導体であり、W(タングステン)、Al(アルミニウム)、Cu(銅)のような金属膜に例示される。

コンタクトホール11は、MOSトランジスタTr1,Tr2のソースとしてのN+拡散層2と配線12とを繋ぐように層間絶縁膜8中に設けられた穴である。コンタクトホール11の下部は、MOSトランジスタTr1,Tr2のゲート上絶縁膜6及びサイドウォール7により、自己整合的に形成されている。コンタクトプラグ13は、コンタクトホール11を充たすように設けられた配線であり、MOSトランジスタTr1,Tr2のソースとしてのN+拡散層2と配線12とを電気的に接続する。コンタクトプラグ13は、セルフアライメント構造を有している。導体であり、W(タングステン)、Al(アルミニウム)、Cu(銅)のような金属膜に例示される。

本実施の形態の半導体装置は、MOSトランジスタTr1とMOSトランジスタTr2との間にあるコンタクトプラグ13をセルフアライメント(self−alignment)構造としている。このようにすることで、MOSトランジスタTr1,Tr2間の距離を、通常のコンタクトの構造を用いるのに比べて短く縮めることができる。これにより、半導体装置の微細化、高集積化を図ることができる。

さらに、本実施の形態の半導体装置は、電気的には、MOSトランジスタTr1とMOSトランジスタTr2との間にあるN型拡散層をソースとし、両脇のN型拡散層をドレインとするように接続している。このとき、ウェル(半導体基板1)とソースとは、略同電位である。従って、コンタクトプラグ13をセルフアライメント構造としたことで、ソースにおいてN−拡散層3とコンタクトプラグ13とは接触するが、リーク電流の問題は原理的に発生しない。それにより、コンタクトプラグ13として低抵抗な金属を用いることができる。略同電位とは、リーク電流の問題が発生しない程度に等しいということであり、誤差を含み得る。

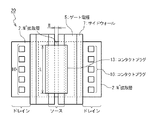

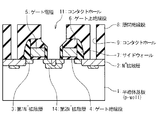

図3は、本発明の半導体装置の実施の形態の構成を示す平面図である。ただし、配線12及び層間絶縁膜8を省略している。ドレインのコンタクトプラグ10は、従来の通常のコンタクトと同様に、粒状(島状)の複数のプラグで構成されている。そのコンタクトプラグ10は、その横断面(半導体基板1表面に平行な面)の面積が、コンタクトプラグ13のそれと比較して相対的に小さい。また、そのコンタクトプラグ10は、MOSトランジスタTr1、Tr2のゲート幅方向の長さが、コンタクトプラグ13のそれと比較して相対的に等しいか小さい。

一方、ソースのコンタクトプラグ13は、従来の通常のコンタクトと異なり、少数で好ましくは一つのプラグで構成されている。そのコンタクトプラグ13は、その横断面の面積が、コンタクトプラグ10の個々のプラグのそれと比較して相対的に大きい。また、MOSトランジスタTr1、Tr2のゲート幅方向の長さ(L)がコンタクトプラグ10の個々のプラグのそれと比較して相対的に等しいか大きい。これにより、コンタクトプラグ13は、セルフアライン構造によりN+拡散層2とコンタクトプラグ13との接触幅(W)がコンタクトプラグ10に比較して小さくなっても、接触面積(接触長さL×接触幅W)を大きく保つことで、接触抵抗の低抵抗化を実現することができる。

また、コンタクトプラグ13は、その横断面の形状が、ゲート幅方向(図3における上下方向)に長いスリット形状(矩形形状)を有していることが好ましい。それにより、接触面積(接触長さL×接触幅W)をより確実に大きく保つことができる。ただし、接触長さLが十分に確保できる等の理由で抵抗値が十分に低ければ、端部や角部に丸みがついていたり、楕円形状を有していても良い。

なお、両脇のドレインのコンタクトプラグ10は、図示されるように、通常のコンタクトと同様の粒状(島状)であることが、スリット形状である場合に比較して、より好ましい。スリット形状にすると、リソグラフィーの特性上スリットの中央で開口幅が大きくなる可能性があり、不向きであるからである。これは以下の理由による。コンタクトプラグ13(ソース)の場合、接合リークを気にする必要がないので、セルフアラインメント構造を採用することができるので、中央で開口幅が大きくなったとしても問題がない。しかし、ドレインの場合、接合リークが発生しないように第1N−拡散層3とコンタクトプラブ10との接触を防止する必要がある。そのため、ゲートとコンタクトプラグ10との間隔を広げるか、中央が広がらない特別な技術を用いる必要があり、半導体チップの微細化に不適か、製造プロセスの高コスト化につながる。

このように、本発明の半導体装置は、ソース側のコンタクトプラグ(金属配線コンタクト)をスリット形状、且つセルフアライメント構造とし、ドレイン側のコンタクトプラグ(金属配線コンタクト)を通常の粒状(島状)コンタクトとする。これにより、リーク電流の問題を回避し、低抵抗コンタクト(低抵抗な金属使用、かつ低接触抵抗)を維持しながら、トランジスタ間の距離を縮めて半導体装置の微細化、高集積化を図ることが可能となる。

次に、本発明の半導体装置の製造方法における実施の形態について説明する。図4〜図7は、本発明の半導体装置の製造方法における実施の形態を示す断面図である。

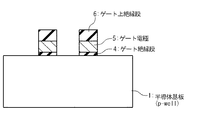

図4を参照して、半導体基板の表面に一般的な方法により素子分離領域(図示されず)を形成する。次に、半導体基板の表面にボロンを注入することでP型ウェルを形成する。図中の半導体基板1は、ボロンを注入された半導体基板の表面を示している。続いて、例えば、酸化を施すことにより、半導体基板1の表面を覆うように、厚さ5nmのゲート絶縁膜を形成する。その後、例えば、厚さ100nmのリンドープポリシリコン、及び厚さ100nmのシリコン窒化膜を、それぞれCVD法により成膜する。そして、リンドープポリシリコン及びシリコン窒化膜を所望のパターンにパターニングする。このとき、ゲート絶縁膜も一部エッチングされる。その結果、ゲート絶縁膜4、ゲート電極5およびゲート上絶縁膜6が形成される。この状態が図4である。

図4の状態において、次に、ゲート上絶縁膜6をマスクとして、例えば10keV、5×1013cm−2の条件で砒素をイオン注入し、第1N−拡散層3を形成する。続いて、例えば厚さ70nmのシリコン窒化膜をCVD法により成膜する。その後、異方性エッチバック技術を用いて、シリコン窒化膜をエッチバックして、サイドウォール7を形成する。この状態が図5である。

図5の状態において、次に、ゲート上絶縁膜6及びサイドウォール7をマスクとして、例えば20keV、3×1015cm−2の条件で砒素をイオン注入し、N+拡散層2を形成する。続いて、例えば、厚さ1000nmのシリコン酸化膜をCVD法により成膜し、必要に応じてCMP(Chemical Mechanical Polishing)技術などで平坦化し、表面を層間絶縁膜108で覆う。この状態が図6である。

図6の状態において、次に、MOSトランジスタTr1、Tr2のドレインに対応する層間絶縁膜8中の位置に、コンタクトホール9をエッチングにより開口する。そして、そのコンタクトホール9に金属材料からなるコンタクトプラグ10をCVD法とCMP技術により埋設する。また、コンタクトホール9の開口と同時に、ソースに対応する層間絶縁膜8中の位置に、コンタクトホール11をエッチングにより開口する。コンタクトホール11の下部の形状は、両側から迫るMOSトランジスタTr1,Tr2のゲート上絶縁膜6及びサイドウォール7の形状により自己整合的に決定される。そして、コンタクトプラグ10の埋設と同時に、そのコンタクトホール11に金属材料からなるコンタクトプラグ13をCVD法とCMP技術により埋設する。すなわち、コンタクトホール11及びコンタクトプラグ13は、セルフアライメント(self−alignment)構造を有している。さらに、例えば、10keV、5×1013cm−2の条件でリンをイオン注入して、第2N−拡散層14を形成する。この状態が図7である。

図7の状態において、金属材料から成る配線用の膜を成膜し、パターニングすることで配線12を形成する。これにより、図1に示される本発明の半導体装置を製造することができる。

本実施の形態では、コンタクトプラグ13をコンタクトプラグ11と同時に、同様に金属で形成することができる。それにより、例えば、コンタクトプラグ13としてポリシリコンのプラグを用いる場合に比較して、製造工程を簡略化することができ、工程にかかる時間を減少でき、コストも低減することが可能となる。

1、101 半導体基板(p−well)

2、102 N+拡散層

3、103 第1N−拡散層

4、104 ゲート絶縁膜

5、105 ゲート電極

6 ゲート上絶縁膜

7、107 サイドウォール

8、108 層間絶縁膜

9、109 コンタクトホール

10、110 コンタクトプラグ

11 コンタクトホール

12、112 配線

13 コンタクトプラグ

14、114 第2N−拡散層

2、102 N+拡散層

3、103 第1N−拡散層

4、104 ゲート絶縁膜

5、105 ゲート電極

6 ゲート上絶縁膜

7、107 サイドウォール

8、108 層間絶縁膜

9、109 コンタクトホール

10、110 コンタクトプラグ

11 コンタクトホール

12、112 配線

13 コンタクトプラグ

14、114 第2N−拡散層

Claims (11)

- 半導体基板上に設けられた隣接する二つのトランジスタと、

前記二つのトランジスタ間にセルフアライメント構造で設けられ、前記二つのトランジスタの共通のソースに接続された金属を含む第1コンタクトと、

前記二つのトランジスタのドレインにそれぞれ接続され、金属を含む二つの第2コンタクトと

を具備する

半導体装置。 - 請求項1に記載の半導体装置において、

前記第1コンタクトの端部と前記トランジスタのゲートの端部との間隔は、前記第2コンタクトの端部と前記トランジスタのゲートとの間隔よりも小さい

半導体装置。 - 請求項1又は2に記載の半導体装置において、

前記第1コンタクトは、少なくとも一つのコンタクトを有し、

前記二つの第2コンタクトの各々は、複数のコンタクトを有する

前記少なくとも一つのコンタクトにおける前記二つのトランジスタのゲート幅方向の長さは、前記複数のコンタクトの各々における前記ゲート幅方向の長さと等しいか長い

半導体装置。 - 請求項1乃至3のいずれか一項に記載の半導体装置において、

前記二つのトランジスタは、前記半導体基板のウェル表面に設けられ、

前記ソースと前記ウェルとは略同電位である

半導体装置。 - 請求項1乃至4のいずれか一項に記載の半導体装置において、

前記第1コンタクトは、前記ゲート幅方向の長さが前記ゲート長方向よりも長い形状を有する

半導体装置。 - 請求項5に記載の半導体装置において、

前記第1コンタクトは、矩形形状を有する

半導体装置。 - 請求項1乃至6のいずれか一項に記載の半導体装置において、

前記第1コンタクトは、一つである

半導体装置。 - (a)半導体基板上に隣接する二つのトランジスタを形成する工程と、

(b)前記半導体基板と前記二つのトランジスタとを覆うように設けられた層間絶縁膜に、前記二つのトランジスタの共通のソースに対応する場所に自己整合的に第1コンタクトホールを形成する工程と、

(c)前記第1コンタクトホールを金属を含む物質で埋めるように、第1コンタクトを形成する工程と、

(d)前記層間絶縁膜に、前記二つのトランジスタの各々のドレインに対応する場所に二つの第2コンタクトホールを形成する工程と、

(e)前記二つの第2コンタクトホールを金属を含む物質で埋めるように、二つの第2コンタクトを形成する工程と

を具備する

半導体装置の製造方法。 - 請求項8に記載の半導体装置の製造方法において、

前記第1コンタクトの端部と前記トランジスタのゲートの端部との間隔は、前記第2コンタクトの端部と前記トランジスタのゲートとの間隔よりも小さい

半導体装置の製造方法。 - 請求項8又は9に記載の半導体装置の製造方法において、

前記第1コンタクトは、少なくとも一つのコンタクトを有し、

前記二つの第2コンタクトの各々は、複数のコンタクトを有し、

前記少なくとも一つのコンタクトの横断面は、前記複数のコンタクトの各々の横断面の和よりも大きい

半導体装置の製造方法。 - 請求項8乃至10のいずれか一項に記載の半導体装置の製造方法において、

前記(b)工程と前記(d)工程とは同時に行われ、

前記(c)工程と前記(e)工程とは同時に行われる

半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006351039A JP2008166330A (ja) | 2006-12-27 | 2006-12-27 | 半導体装置 |

| US12/003,174 US20080157227A1 (en) | 2006-12-27 | 2007-12-20 | Semiconductor device and manufacturing process therefor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006351039A JP2008166330A (ja) | 2006-12-27 | 2006-12-27 | 半導体装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2008166330A true JP2008166330A (ja) | 2008-07-17 |

Family

ID=39582636

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006351039A Pending JP2008166330A (ja) | 2006-12-27 | 2006-12-27 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20080157227A1 (ja) |

| JP (1) | JP2008166330A (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4841106B2 (ja) * | 2003-08-28 | 2011-12-21 | ルネサスエレクトロニクス株式会社 | Mis型半導体装置及びその製造方法 |

| KR102268296B1 (ko) * | 2014-09-15 | 2021-06-24 | 삼성전자주식회사 | 불휘발성 메모리 장치 |

| US10510851B2 (en) * | 2016-11-29 | 2019-12-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Low resistance contact method and structure |

| KR102832732B1 (ko) * | 2021-02-16 | 2025-07-10 | 삼성전자주식회사 | 반도체 장치 |

-

2006

- 2006-12-27 JP JP2006351039A patent/JP2008166330A/ja active Pending

-

2007

- 2007-12-20 US US12/003,174 patent/US20080157227A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| US20080157227A1 (en) | 2008-07-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7728373B2 (en) | DRAM device with cell epitaxial layers partially overlap buried cell gate electrode | |

| US8895400B2 (en) | Methods of fabricating semiconductor devices having buried word line interconnects | |

| US5946558A (en) | Method of making ROM components | |

| KR100385408B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US8648415B2 (en) | Semiconductor device with impurity region with increased contact area | |

| US7675110B2 (en) | Semiconductor device and method of manufacturing the same | |

| US7977800B2 (en) | Semiconductor device and fabrication method for the same | |

| US9209192B2 (en) | Semiconductor device and method of fabricating the same | |

| US6399987B2 (en) | MOS transistor having self-aligned well bias area | |

| JPH1197649A (ja) | 半導体装置及びその製造方法 | |

| JPH11354749A (ja) | 半導体集積回路装置およびその製造方法 | |

| KR0139188B1 (ko) | 비 휘발성 반도체 기억장치 제조방법 | |

| US6858893B2 (en) | Semiconductor memory having a pillar type trench dram cell | |

| JP2008205379A (ja) | 不揮発性半導体メモリ及びその製造方法 | |

| JPWO2003069675A1 (ja) | 半導体装置の製造方法 | |

| US20080157227A1 (en) | Semiconductor device and manufacturing process therefor | |

| JP4822792B2 (ja) | 半導体装置およびその製造方法 | |

| US6642584B2 (en) | Dual work function semiconductor structure with borderless contact and method of fabricating the same | |

| JP5330899B2 (ja) | 半導体装置及びその製造方法 | |

| JP2004327517A (ja) | 半導体装置およびその製造方法 | |

| JP4564469B2 (ja) | 半導体装置 | |

| JP2001044138A (ja) | 半導体集積回路装置の製造方法および半導体集積回路装置 | |

| JP4470182B2 (ja) | 半導体装置の製造方法 | |

| JP2004006449A (ja) | 半導体集積回路装置 | |

| JP4031777B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080514 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090209 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090212 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090616 |