JP2006338024A - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP2006338024A JP2006338024A JP2006154072A JP2006154072A JP2006338024A JP 2006338024 A JP2006338024 A JP 2006338024A JP 2006154072 A JP2006154072 A JP 2006154072A JP 2006154072 A JP2006154072 A JP 2006154072A JP 2006338024 A JP2006338024 A JP 2006338024A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- liquid crystal

- gate

- drain electrode

- crystal display

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3659—Control of matrices with row and column drivers using an active matrix the addressing of the pixel involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependant on signal of two data electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0439—Pixel structures

- G09G2300/0443—Pixel structures with several sub-pixels for the same colour in a pixel, not specifically used to display gradations

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/028—Improving the quality of display appearance by changing the viewing angle properties, e.g. widening the viewing angle, adapting the viewing angle to the view direction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

- G09G3/3655—Details of drivers for counter electrodes, e.g. common electrodes for pixel capacitors or supplementary storage capacitors

Abstract

【解決手段】行列状に配列され第1及び第2副画素電極を有する複数の画素電極、複数の維持電極、第1及び第2画素電極にそれぞれ接続され維持電極と重畳する複数の第1及び第2ドレイン電極を備える。第1副画素電極の面積は、第2副画素電極の面積より大きく、第1ドレイン電極と維持電極が重畳する面積が第2ドレイン電極と維持電極が重畳する面積より大きいが、第1副画素電極に第2副画素電極より低いデータ電圧が印加されるときに対応して、第1ドレイン電極の下部に維持電極の延長部をさらに設けて、第1ストレージキャパシタの容量をより大きくする。

【選択図】図4

Description

垂直配向モード液晶表示装置で広視野角を実現するための手段としては、電界生成電極に切開部を形成する方法と、電界生成電極上に突起を形成する方法などがある。切開部と突起で液晶分子が傾く方向を決定できるので、これによって液晶分子の傾斜方向を複数方向に分散させて基準視野角を広くすることができる。

側面視認性を改善するために、一つの画素を二つの副画素に分割し、二つの副画素を容量性結合した後、一方の副画素には直接電圧を印加し、もう一方の副画素には容量性結合による電圧降下を生じさせ、二つの副画素の電圧を異にして透過率を異なるようにする方法が提示された。

前記保護膜上に形成され、前記第1電場生成電極に印加される電圧と異なる大きさの電圧が印加される第2電場生成電極をさらに備えることが望ましく、前記第1電場生成電極と第2電場生成電極とは容量性結合されることが望ましい。

前記第2ドレイン電極は、前記維持電極の本体部と重畳することができ、前記第2ドレイン電極と前記維持電極の本体部との重畳面積は、前記第1ドレイン電極と前記維持電極の本体部との重畳面積より小さくてもよく、前記維持電極の本体部において、前記第2ドレイン電極と重畳する部分の幅は、前記第1ドレイン電極と重畳する部分の幅より狭くてもよい。前記維持電極の本体部において、前記第2ドレイン電極と重畳する部分の長さは、前記第1ドレイン電極と重畳する部分の長さより短くてもよい。

前記第1電場生成電極には、所定の電圧に対し前記第2電場生成電極より低い電圧が印加されてもよく、前記第1電場生成電極の面積は、前記第2電場生成電極の面積より大きくてもよい。

また、前記第1及び第2ゲート電極に接続されるゲート線と、前記第1ソース電極に接続される第1データ線と、前記第2ソース電極に接続される第2データ線とをさらに備えることが望ましい。

前記第1ドレイン電極は、前記第1ゲート電極と重畳する端部、前記維持電極と重畳し該端部と離れている拡張部、及び該端部と該拡張部を接続する接続部を有し、前記維持電極の本体部は、前記第1ドレイン電極の拡張部及び前記第2ドレイン電極と重畳し、前記維持電極の延長部は、前記第1ドレイン電極の接続部と重畳することができる。

前記第1ドレイン電極の拡張部の境界は、前記維持電極の本体部の境界線内に位置し、前記維持電極の延長部の幅は、前記第1ドレイン電極の接続部の幅より広くてもよく、前記維持電極の本体部において前記第2ドレイン電極と重畳する部分の幅は、前記第1ドレイン電極の拡張部と重畳する部分の幅より狭くてもよい。

前記第1副画素電極の面積は前記第2副画素電極の面積より大きく、前記維持電極と前記第1ドレイン電極とが重畳する面積は、前記維持電極と前記第2ドレイン電極とが重畳する面積より大きくてもよい。

図面は、各種層及び領域を明確に表現するために、厚さを拡大して示している。明細書全体を通じて類似した部分については同一な参照符号を付けている。層、膜、領域、板などの部分が、他の部分の“上に”あるとする時、これは他の部分の“すぐ上に”ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上に”あるとする時、これは中間に他の部分がない場合を意味する。

図1乃至図3は、本発明の一実施形態による液晶表示装置のブロック図(その1〜その3)であり、図4は、本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図、図5は、本発明の一実施形態による液晶表示装置の一つの副画素に対する等価回路図である。

表示信号線(G1a−Gnb、D1−Dm)は下部表示板100に備えられ、ゲート信号(走査信号とも言う)を伝達する複数対のゲート線(G1a−Gnb)とデータ信号を伝達するデータ線(D1−Dm)を有する。ゲート線(G1a−Gnb)はほぼ行方向に延びて互いにほぼ平行であり、データ線(D1−Dm)はほぼ列方向に延びて互いにほぼ平行である。

各画素PXは一対の副画素PXa、PXbを有し、各副画素PXa、PXbはゲート線GLa、GLb及びデータ線DLに接続されているスイッチング素子Qa、Qbと、これに接続された液晶キャパシタCLCa、CLCb、並びにスイッチング素子Qa、Qb及び維持電極線SLに接続されているストレージキャパシタCSTa、CSTbを有する。

図5は、空間分割の一例であり、各画素PXが上部表示板200の領域に基本色のうちの一つを示すカラーフィルタCFを備えているものを示す。図5と異なり、カラーフィルタCFは下部表示板100の副画素電極PEの上または下に設けることもできる。

信号制御部600は、ゲート駆動部400及びデータ駆動部500などの動作を制御する。

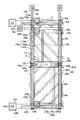

図6は、本発明の一実施形態による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図7は、本発明の一実施形態による共通電極表示板の配置図であり、図8は、図6及び図7の二つの表示板を備える液晶表示板組立体の配置図であり、図9及び図10は各々図8の液晶表示板組立体のVIIA−VIIA線及びVIIB−VIIB′−VIIB″線に沿った断面図である。

図6乃至図10に示すように、本発明の一実施形態による液晶表示板組立体は、薄膜トランジスタ表示板100、共通電極表示板200、これら二つの表示板100、200の間に挟持された液晶層3を備える。

透明なガラスまたはプラスチックなどからなる絶縁基板110上に、複数対の第1及び第2ゲート線121a、121bと複数の維持電極線131を有する複数のゲート導電体が形成されている。

第1及び第2ゲート線121a、121bはゲート信号を伝達し、主に横方向に延びており、それぞれ上側及び下側に位置する。

第2ゲート線121bは、上方に突出した複数の第2ゲート電極124bと他の層または外部駆動回路との接続のために、広い面積を有し左側に配置された端部129bを有する。

ゲート導電体121a、121b、131の側面は基板110面に対し傾斜しており、その傾斜角は約30°乃至約80゜であることが好ましい。

ゲート絶縁膜140上には、水素化非晶質シリコン(非晶質シリコンはa−Siと略称する。)または多結晶シリコンなどからなる複数の島状の半導体154a、154b、156a、157aが形成されている。半導体154a、154bは、それぞれ第1及び第2ゲート電極124a、124b上に位置する。半導体156a、157aは、第1及び第2ゲート線121a、121b、維持電極線131、維持電極137及び延長部139の境界を覆う。

半導体154a、154b、156a、157aとオーミック接触部材163a、163b、165a、165b、166aの側面も基板110面に対し傾斜しており、その傾斜角は30°乃至80°程度である。

オーミック接触部材163a、163b、165a、165b、166a及びゲート絶縁膜140上には、複数のデータ線171と複数対の第1及び第2ドレイン電極175a、175bを有するデータ導電体が形成されている。

第1ドレイン電極175aは、第1ゲート電極124aを中心に第1ソース電極173aと対向する棒状の端部176a、棒状の端部176aの反対側端にある広い長方形の拡張部177a、そして拡張部177aと端部176aを接続する線状の接続部176aaを有する。拡張部177aは維持電極137と重畳し、棒状の端部176aは第1ゲート電極124aと重畳し、C字状に折曲した第1ソース電極173aで一部覆われている。第1ドレイン電極175aの接続部176aaはほとんど延長部139上に位置し、延長部139と平行に延びており、延長部139の縦境界線内に位置する。

第1、第2ゲート電極124a、124b、第1、第2ソース電極173a、173b、及び第1、第2ドレイン電極175a、175bは、第1、第2半導体154a、154bと共に第1、第2薄膜トランジスタ(TFT)Qa、Qbを構成し、第1、第2薄膜トランジスタQa、Qbのチャンネルは、第1、第2ソース電極173a、173bと第1、第2ドレイン電極175a、175bとの間の第1、第2半導体154a、154bに形成される。

データ導電体171、175a、175bもその側面が基板110面に対し30°乃至80°程度の角度で傾斜していることが好ましい。

各画素電極191は、4つの角が面取りされた(chamfered)ほぼ四角形状であり、面取りされた斜辺は第1及び第2ゲート線121a、121bに対して約45度の角度をなしている。

これにより、画素電極191を横方向に二等分する維持電極線131を中心にした上半部と下半部は、切開部91−94cによりそれぞれ6個の領域に分けられる。

ここで、領域の数または切開部の数は、画素電極191の大きさ、画素電極191の横辺と縦辺の長さ比、液晶層3の種類や特性など、設計要素によって変化する。

遮蔽電極88は、共通電圧Vcomの印加を受け、データ線171と画素電極191の間及びデータ線171と共通電極270との間に形成される電界を遮断して、画素電極191の電圧歪曲及びデータ線171が伝達するデータ電圧の信号遅延が減少する。しかし、必要に応じて遮蔽電極88は省略してもよい。

透明なガラスまたはプラスチックなどからなる絶縁基板210上に、遮光部材220が形成されている。遮光部材220は、ブラックマトリックスとも言い、光漏洩を防ぐ。遮光部材220は、画素電極191と対向しており、画素電極191とほぼ同一形状の複数の開口部225を有している。これに対し、遮光部材220は、データ線171に対応する部分と、第1、第2薄膜トランジスタQa、Qbに対応する部分からなることもできる。遮光部材220は、画素電極191と薄膜トランジスタQa、Qb近傍の光漏洩を遮断するために様々な形状を有することができる。

オーバーコート膜250上には共通電極270が形成されている。共通電極270はITO、IZOなどの透明な導電体などからなり、複数の切開部群71、72、73、74a、74b、75a、75b、76a、76bを有する。

切開部71−76bの数及び方向も設計要素によって変わり、遮光部材220が切開部71〜76bと重畳して切開部71−76b近傍の光漏洩を遮断することができる。

下部及び上部表示板100、200の外側面には偏光子を有する偏光板12、22が備えられており、二つの偏光子を有する偏光板12、22の相互の偏光軸は直交し、このうちの一つの偏光軸は、第1及び第2ゲート線121a、121bに対して平行であることが望ましい。反射型液晶表示装置では、二つの偏光板12、22のうちの一つは省略してもよい。

液晶層3は負の誘電率異方性を有し、液晶層3の液晶分子は電場がない状態でその長軸が二つの表示板100、200の表面に対して垂直をなすように配向されている。このため、入射光は二つの偏光板12、22の直交する偏光子を通過できず遮断される。

信号制御部600は、外部のグラフィック制御部(図示せず)から入力映像信号R、G、B及びその表示を制御する入力制御信号、例えば、垂直同期信号Vsyncと水平同期信号Hsync、メインクロックMCLK、データイネーブル信号DEなどの提供を受ける。信号制御部600は、入力映像信号R、G、Bと入力制御信号に基づいて映像信号R、G、Bを液晶表示板組立体300の動作条件に合せて適切に処理し、ゲート制御信号CONT1及びデータ制御信号CONT2などを生成した後、ゲート制御信号CONT1をゲート駆動部400に送出し、データ制御信号CONT2と処理した映像信号DATはデータ駆動部500に送出する。

データ制御信号CONT2は、一つの画素行のデータ伝送を知らせる水平同期開始信号STH(図示せず)と、データ線(D1−Dm)に当該データ電圧の印加を指示するロード信号LOAD、及びデータクロック信号HCLK(共に図示せず)を有する。また、データ制御信号CONT2は、共通電圧Vcomに対するデータ電圧の極性(以下、共通電圧に対するデータ電圧の極性を略してデータ電圧の極性という。)を反転させる反転信号RVS(図示せず)を有することができる。

Vk=[Cgd/(CLC+CST+Cgd)]×ΔVg

ここで、ΔVgはゲートオン電圧Vonとゲートオフ電圧Voffの差電圧である。

なお、本発明の実施形態による液晶表示装置の第1及び第2副画素PXa、PXbのキックバック電圧Vka、Vkbの大きさは実質的に同一である。

図11は、本発明の他の実施形態による液晶表示装置用薄膜トランジスタ表示板の配置図である。

図11に示す実施形態の薄膜トランジスタ表示板の層状構造はほとんど図6に示した薄膜トランジスタ表示板の層状構造と同様である。

図6に示す薄膜トランジスタ表示板の多くの特徴は、図11に示す薄膜トランジスタ表示板にも適用できる。

図12は、本発明の他の実施形態による液晶表示装置のブロック図であり、図13は、本発明の他の実施形態による液晶表示装置の一つの画素に対する等価回路図である。

本発明の他の実施形態による液晶表示装置は、液晶表示板組立体301とこれに接続されたゲート駆動部403、及びデータ駆動部501、データ駆動部501に接続された階調電圧生成部801、並びにこれらを制御する信号制御部601を備える。

表示信号線(G1−Gn、D1−D2m)は、ゲート信号を伝達する複数のゲート線(G1−Gn)と、データ信号を伝達するデータ線(D1−D2m)を有する。ゲート線(G1−Gn)はほぼ行方向に延びて互いにほぼ平行であり、データ線(D1−D2m)はほぼ列方向に延びて互いにほぼ平行である。一つの画素PXの両側にそれぞれ一対のデータ線(D1−D2m)が配置されている。さらに、表示信号線は、ゲート線(G1−Gn)とデータ線(D1−D2m)以外にもゲート線(G1−Gn)とほぼ平行に延びた維持電極線を有することができる。

各画素PXは一対の副画素PXc、PXdを有し、各副画素PXc、PXdは、それぞれ当該ゲート線GL及びデータ線DLa、DLbに接続されているスイッチング素子Qc、Qdと、これらに接続された液晶キャパシタCLCc、CLCd及びストレージキャパシタCSTc、CSTdを有する。

階調電圧生成部801は、副画素PXc、PXdの透過率に関連する二組の複数階調電圧を生成する。二組のうちの一組は共通電圧Vcomに対してプラスの値を有し、もう一組はマイナスの値を有する。

データ駆動部501は、液晶表示板組立体301のデータ線(D1−D2m)に接続され、階調電圧生成部801からの階調電圧を選択してデータ信号として副画素PXc、PXdに印加する。

信号制御部601は、ゲート駆動部403及びデータ駆動部501などの動作を制御する。

図14は、本発明の他の実施形態による液晶表示板組立体の配置図であり、図15は、図14の液晶表示板組立体のXII−XII線に沿った断面図である。

図14及び図15の実施形態による液晶表示板組立体は、薄膜トランジスタ表示板101、共通電極表示板201、及びその間の液晶層3を備える。

透明なガラスまたはプラスチックなどからなる絶縁基板110上に、複数のゲート線121と複数の維持電極線131aを有する複数のゲート導電体が形成されている。

ゲート線121はゲート信号を伝達し、主に横方向に延びている。各ゲート線121は、上方に突出した第1及び第2ゲート電極124c、124dと、他の層または外部駆動回路との接続のために広い面積の端部129を有する。

ゲート絶縁膜140上には、水素化非晶質シリコンまたは多結晶シリコンなどからなる複数の島状の半導体154c、154d、156b、157bが形成されている。半導体154c、154dは、それぞれ第1及び第2ゲート電極124c、124d上に位置する。半導体156b、157bは、ゲート線121、維持電極線131aの境界を覆う。

データ線171a、171bはデータ信号を伝達し、主に縦方向に延びてゲート線121及び維持電極線131aと交差する。各データ線171a、171bは、第1及び第2ゲート電極124c、124dに向かって延びた複数の第1及び第2ソース電極173c、173dと他の層または外部駆動回路との接続のために広い面積の端部179a、179bを有する。

保護膜180には第1及び第2ドレイン電極175c、175dの拡張部177c、177dとデータ線171a、171bの端部179a、179bをそれぞれ露出させる複数のコンタクトホール185c、185d、182a、182bが形成されており、保護膜180とゲート絶縁膜140には、ゲート線121の端部129を露出させる複数のコンタクトホール181が形成されている。

保護膜180上には、第1及び第2副画素電極191a、191bを有する複数の画素電極191、複数の遮蔽電極88b及び複数の接触補助部材81、82a、82bが形成されている。

透明なガラスまたはプラスチックなどからなる絶縁基板210上に、遮光部材220、複数のカラーフィルタ230、オーバーコート膜250及び共通電極270が順に形成されている。

下部及び上部表示板101、201の内側面には配向膜11、21が塗布されており、外側面には偏光子を有する偏光板12、22が備えられている。

図14及び図15に示す実施形態による液晶表示装置の表示動作は、前記実施形態と実質的に同一であるのでこれに対する説明は省略する。

図1乃至図10の液晶表示板組立体の多くの特徴は、図12乃至図115の液晶表示板組立体にも適用できる。

図16は、本発明の他の実施形態による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図17は、図16の液晶表示装置用薄膜トランジスタ表示板のXIIIB−XIIIB線に沿った断面図である。

ゲート線121はゲート信号を伝達し、主に横方向に延びている。各ゲート線121は、上方に突出した複数のゲート電極124eと他の層または外部駆動回路との接続のために広い面積の端部129を有する。

ゲート絶縁膜140上には、水素化非晶質シリコンまたは多結晶シリコンなどからなる複数の島状の半導体154eが形成されている。半導体154eは、それぞれゲート電極124e上に位置する。半導体154eは、ゲート線121境界まで延びており、維持電極線131bの境界にも配置できる。半導体154eの上には複数の島状オーミック接触部材163e、165eが形成されている。オーミック接触部材163e、165eは対をなして半導体154e上に位置する。

データ線171はデータ信号を伝達し、主に縦方向に延びてゲート線121及び維持電極線131bと交差する。各データ線171は、ゲート電極124eに向かって延びた複数のソース電極173eと、他の層または外部駆動回路との接続のために広い面積の端部179を有する。

各拡張部177eは維持電極137bと重畳し、棒状の端部176eはゲート電極124eと重畳し、U字状に折曲したソース電極173eで一部覆われている。以下、拡張部177eを結合電極と称する。

一つのゲート電極124e、一つのソース電極173e及び一つのドレイン電極175eは、半導体154eと共に一つの薄膜トランジスタを構成し、薄膜トランジスタのチャンネルは、ソース電極173eとドレイン電極175eとの間の半導体154eに形成される。

保護膜180には結合電極177eとデータ線171の端部179をそれぞれ露出させる複数のコンタクトホール182、185eが形成されており、保護膜180とゲート絶縁膜140にはゲート線121の端部129を露出させる複数のコンタクトホール181が形成されている。

各画素電極191は、4つの角が面取りされたほぼ四角形状を有し、面取りされた斜辺はゲート線121に対して約45度の角度をなす。画素電極191はゲート線121と重畳し、このため開口率を大きくすることができる。

よって、第2副画素電極191dは、ほぼ直角に回転した二等辺台形状を有し、第1副画素電極191cは第2副画素電極191dの斜辺と対向し、ほぼ直角に回転した一対の台形部と第2副画素電極191dの右側辺と対向する縦部を有する。

この時、切開部の数または領域の数は、画素電極191の大きさ、画素電極191の横辺と縦辺の長さ比、液晶層の種類や特性など、設計要素によって異なる。

下部表示板100の外部面には偏光子を有する偏光板12が備えられている。

第2副画素電極191dは結合電極177eと重畳して結合キャパシタCcp(図示せず)を構成する。

Vf=Ve×[Ccp/(Ccp+CLCf)]

Ccp/(Ccp+CLCf)の値が1より小さいので、第2液晶キャパシタCLCfに充電された電圧Vfは、第1液晶キャパシタCLCeに充電された電圧Veに比べて常に小さい。この関係は、維持電極線131bの電圧が共通電圧Vcomでない場合にも同様に成立する。

接触補助部材81、82は、それぞれコンタクトホール181、182を介してゲート線121の端部129及びデータ線171の端部179に接続される。

図1乃至図10に示した液晶表示板組立体の多くの特徴は、図16及び図17の液晶表示装置用薄膜トランジスタ表示板にも適用できる。

図18は、本発明の他の実施形態による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図19は、図18の液晶表示装置用薄膜トランジスタ表示板のXIVB−XIVB線に沿った断面図である。

図18及び図19に示す実施形態による薄膜トランジスタ表示板の層状構造は、図116及び図17に示した薄膜トランジスタ表示板の層状構造とほとんど同様である。

これにより、画素電極191は、切開部91、92、93a、93b、94a、94b、95a、95bによって複数の領域に分割される。切開部91−95bは、維持電極線131bに対しほぼ反転対称をなす。

液晶分子の傾斜方向を決定するための切開部91−95bの形状及び配置は変更することができ、少なくとも一つの切開部91−95bは突起(図示せず)や陥没部(図示せず)で代替することができる。突起は有機物または無機物からなることができ、電場生成電極の上または下に配置できる。

図1乃至図10の液晶表示板組立体の多くの特徴は、図18及び図19の液晶表示装置用薄膜トランジスタ表示板にも適用できる。

12、22 偏光板

11、21 配向膜

71、72、73、73a、74a(図14、15)、 共通電極の中央切開部

74a(図7〜9)、75a、75c、76a、76c、77a、78a 共通電極の上部切開部

74b、75b、75d、76b、76d、77b、78b 共通電極の下部切開部

81、81a、81b、82、82a、82b 接触補助部材

88、88b 遮蔽電極

91、92(図16〜19)、92a 画素電極の中央切開部

92(図6、8、9、11)、93 画素電極のギャップ(切開部)

93a(図6、8、9、11)、93b、94a(図6、8、9、11、14、15)、94b、95b、96a、97a、 画素電極の上部切開部

93a(図18、19)、93c、94a(図16〜19)、94c、95a、96b、97b 画素電極の下部切開部

100、101 下部表示板(薄膜トランジスタ表示板)

110、210 基板(絶縁基板)

121 ゲート線(ゲート導電体)

121a 第1ゲート線(ゲート導電体)

121b 第2ゲート線(ゲート導電体)

124a、124c 第1ゲート電極

124b、124d 第2ゲート電極

124e ゲート電極

129 ゲート線の端部

129a 第1ゲート線の端部

129b 第2ゲート線の端部

131、131a、131b 維持電極線(ゲート導電体)

137、137a、137b 維持電極

139、139a、139b 維持電極の延長部

140 ゲート絶縁膜

154a 第1半導体

154b 第2半導体

154c、154d、154e、156a、156b、157a、157b 半導体

163a、163b、163c、163d、163e、165a、165b、165c、165d、165e、166a、166b、167b オーミック接触部材

171、171a、171b データ線(データ導電体)

173a、173c 第1ソース電極

173b、173d 第2ソース電極

173e ソース電極

175a、175c 第1ドレイン電極(データ導電体)

175b、175d 第2ドレイン電極(データ導電体)

175e ドレイン電極

176a、176c 第1ドレイン電極の端部

176b、176d 第2ドレイン電極の端部

176e ドレイン電極の端部

176aa、176cc 第1ドレイン電極の接続部

176bb、176dd 第2ドレイン電極の接続部

176ee ドレイン電極の接続部

177a、177c 第1ドレイン電極の拡張部(電極)

177b、177d 第2ドレイン電極の拡張部(電極)

177e、 ドレイン電極の拡張部(結合電極)

179、179a、179b データ線の端部

180 保護膜

181、181a、181b、182、182a、182b、185、185a、185b、185c、185d、185e コンタクトホール

191 画素電極(電場生成電極)

191a、191c 第1副画素電極

191b、191d 第2副画素電極

200、201 上部表示板(共通電極表示板)

220 遮光部材

225 遮光部材の開口部

230 カラーフィルタ

250 オーバーコート膜

270 共通電極(電場生成電極)

300、301 液晶表示板組立体

400、400a、400b、403 ゲート駆動部

500、501 データ駆動部

600、601 信号制御部

800、801 階調電圧生成部

Claims (20)

- 基板上に形成される第1ゲート電極と、

前記基板上に形成され、前記第1ゲート電極と分離されている維持電極と、

前記第1ゲート電極及び前記維持電極上に形成されるゲート絶縁膜と、

前記ゲート絶縁膜上に形成される第1半導体と、

前記第1半導体上に形成される第1ソース電極と、

前記第1半導体層上に形成され、前記第1ソース電極と分離され、前記第1ゲート電極と重畳する端部、前記維持電極と重畳して該端部と離れている拡張部、及び該端部と該拡張部を接続する接続部を有する第1ドレイン電極と、

前記第1ソース電極及び第1ドレイン電極上に形成され、前記第1ドレイン電極の拡張部を露出させるコンタクトホールを有する保護膜と、

前記コンタクトホールを介して前記第1ドレイン電極に接続される第1電場生成電極とを備え、

前記維持電極は、前記第1ドレイン電極の拡張部と重畳する本体部と、前記第1ドレイン電極の接続部と重畳する延長部と、を有することを特徴とする液晶表示装置。 - 前記第1ドレイン電極の拡張部の境界は、前記維持電極の本体部の境界線内に位置し、前記維持電極の延長部は、前記維持電極の一部から分岐することを特徴とする請求項1に記載の液晶表示装置。

- 前記維持電極の延長部の幅は、前記第1ドレイン電極の接続部の幅より広いことを特徴とする請求項2に記載の液晶表示装置。

- 前記保護膜上に形成され、前記第1電場生成電極に印加される電圧と異なる大きさの電圧が印加される第2電場生成電極をさらに備えることを特徴とする請求項1に記載の液晶表示装置。

- 前記第1電場生成電極と第2電場生成電極とは容量性結合されることを特徴とする請求項4に記載の液晶表示装置。

- 前記基板上に形成される第2ゲート電極と、

前記ゲート絶縁膜上に形成される第2半導体と、

前記第2半導体上に形成される第2ソース電極と、

前記第2半導体上に形成され、前記第2ソース電極と分離され、前記第2電場生成電極に接続される第2ドレイン電極とをさらに備え、

前記第1電場生成電極と前記第2電場生成電極とは、一つの映像情報から得られた互いに異なる大きさのデータ電圧の印加を受けることを特徴とする請求項4に記載の液晶表示装置。 - 前記第2ドレイン電極は、前記維持電極の本体部と重畳することを特徴とする請求項6に記載の液晶表示装置。

- 前記第2ドレイン電極と前記維持電極の本体部との重畳面積は、前記第1ドレイン電極と前記維持電極の本体部との重畳面積より小さいことを特徴とする請求項7に記載の液晶表示装置。

- 前記維持電極の本体部で前記第2ドレイン電極と重畳する部分の幅は、前記第1ドレイン電極と重畳する部分の幅より狭いことを特徴とする請求項8に記載の液晶表示装置。

- 前記維持電極の本体部で前記第2ドレイン電極と重畳する部分の長さは、前記第1ドレイン電極と重畳する部分の長さより短いことを特徴とする請求項8に記載の液晶表示装置。

- 前記第1電場生成電極には、所定の電圧に対し前記第2電場生成電極より低い電圧が印加されることを特徴とする請求項6に記載の液晶表示装置。

- 前記第1電場生成電極の面積は、前記第2電場生成電極の面積より大きいことを特徴とする請求項6に記載の液晶表示装置。

- 前記第1ゲート電極に接続される第1ゲート線と、

前記第2ゲート電極に接続される第2ゲート線と、

前記第1及び第2ソース電極に接続されるデータ線とをさらに備えることを特徴とする請求項6に記載の液晶表示装置。 - 前記第1及び第2ゲート電極に接続されるゲート線と、

前記第1ソース電極に接続される第1データ線と、

前記第2ソース電極に接続される第2データ線とをさらに備えることを特徴とする請求項6に記載の液晶表示装置。 - 行列状に配列され第1及び第2副画素を有する複数の画素と、

前記第1及び第2副画素に接続される複数の第1信号線と、

前記第1信号線と交差し第1副画素に接続される第2信号線と、

前記第1信号線と交差し第2副画素に接続される第3信号線とを備え、

前記第1副画素は、前記第1及び第2信号線に接続される第1スイッチング素子、及び該第1スイッチング素子に接続される第1液晶キャパシタと第1ストレージキャパシタとを有し、

前記第2副画素は、前記第1及び第3信号線に接続される第2スイッチング素子、及び該第2スイッチング素子に接続される第2液晶キャパシタと第2ストレージキャパシタとを有し、

前記第1及び第2液晶キャパシタに印加される電圧は一つの映像情報から得られ、

前記第1副画素には所定の電圧に対し前記第2副画素より低い電圧が印加され、

前記第1及び第2副画素に同一電圧が印加されるときに、前記第1及び第2副画素のキックバック電圧の大きさを実質的に同一にする第1及び第2ストレージキャパシタの静電容量を各々第1及び第2容量とする場合、

前記第1ストレージキャパシタの静電容量が前記第1容量より大きいか、前記第2ストレージキャパシタの容量が前記第2容量より小さいことを特徴とする液晶表示装置。 - 前記第1スイッチング素子は第1ゲート電極と第1ドレイン電極とを有し、

前記第2スイッチング素子は第2ゲート電極と第2ドレイン電極とを有し、

前記第1及び第2ストレージキャパシタは、前記第1及び第2ゲート電極と分離され、本体部とこれから分岐した延長部を有する維持電極を共通に有し、

前記第1ストレージキャパシタは前記維持電極と前記第1ドレイン電極との重畳からなり、

前記第2ストレージキャパシタは前記維持電極と前記第2ドレイン電極との重畳からなり、

前記第1液晶キャパシタは前記第1スイッチング素子に接続される第1副画素電極を有し、

前記第2液晶キャパシタは前記第2スイッチング素子に接続される第2副画素電極を有することを特徴とする請求項15に記載の液晶表示装置。 - 前記第1ドレイン電極は、前記第1ゲート電極と重畳する端部、前記維持電極と重畳し該端部と離れている拡張部、及び該端部と該拡張部を接続する接続部を有し、

前記維持電極の本体部は、前記第1ドレイン電極の拡張部及び前記第2ドレイン電極と重畳し、

前記維持電極の延長部は、前記第1ドレイン電極の接続部と重畳することを特徴とする請求項16に記載の液晶表示装置。 - 前記第1ドレイン電極の拡張部の境界は、前記維持電極の本体部の境界線内に位置し、前記維持電極の延長部の幅は、前記第1ドレイン電極の接続部の幅より広いことを特徴とする請求項17に記載の液晶表示装置。

- 前記維持電極の本体部で前記第2ドレイン電極と重畳する部分の幅は、前記第1ドレイン電極の拡張部と重畳する部分の幅より狭いことを特徴とする請求項17に記載の液晶表示装置。

- 前記第1副画素電極の面積は前記第2副画素電極の面積より大きく、

前記維持電極と前記第1ドレイン電極とが重畳する面積は、前記維持電極と前記第2ドレイン電極とが重畳する面積より大きいことを特徴とする請求項16に記載の液晶表示装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2005-0046911 | 2005-06-01 | ||

| KR1020050046911A KR101160831B1 (ko) | 2005-06-01 | 2005-06-01 | 액정 표시 장치 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006338024A true JP2006338024A (ja) | 2006-12-14 |

| JP5391435B2 JP5391435B2 (ja) | 2014-01-15 |

Family

ID=37493634

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006154072A Active JP5391435B2 (ja) | 2005-06-01 | 2006-06-01 | 液晶表示装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US7956942B2 (ja) |

| JP (1) | JP5391435B2 (ja) |

| KR (1) | KR101160831B1 (ja) |

| CN (1) | CN1892391B (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009042608A (ja) * | 2007-08-10 | 2009-02-26 | Casio Comput Co Ltd | アクティブマトリックス型表示装置 |

| JP2009139629A (ja) * | 2007-12-06 | 2009-06-25 | Sony Corp | 液晶表示装置およびその製造方法 |

| KR101471547B1 (ko) * | 2008-02-20 | 2014-12-11 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| JP2015031961A (ja) * | 2013-08-02 | 2015-02-16 | 三星ディスプレイ株式會社Samsung Display Co.,Ltd. | 液晶表示装置 |

| KR20150071772A (ko) * | 2013-12-18 | 2015-06-29 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20150080148A (ko) * | 2013-12-30 | 2015-07-09 | 삼성디스플레이 주식회사 | 표시 패널 |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20080000496A (ko) * | 2006-06-27 | 2008-01-02 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이 기판 및 그 제조방법 |

| KR101211087B1 (ko) * | 2006-11-30 | 2012-12-12 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이를 포함하는 표시 장치 |

| KR101430623B1 (ko) * | 2007-01-11 | 2014-08-14 | 삼성디스플레이 주식회사 | 액정표시장치 |

| TWI366174B (en) * | 2007-03-03 | 2012-06-11 | Au Optronics Corp | Pixel control device and display apparatus utilizing said pixel control device |

| KR101394434B1 (ko) * | 2007-06-29 | 2014-05-15 | 삼성디스플레이 주식회사 | 표시 장치 및 그의 구동 방법 |

| KR20100024639A (ko) * | 2008-08-26 | 2010-03-08 | 삼성전자주식회사 | 액정 표시 장치 |

| TW201021000A (en) * | 2008-11-26 | 2010-06-01 | Ind Tech Res Inst | Driving method and display utilizing the same |

| TW201042625A (en) * | 2009-05-27 | 2010-12-01 | Au Optronics Corp | Liquid crystal display device and liquid crystal display panel thereof |

| KR101781501B1 (ko) | 2010-12-15 | 2017-09-26 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 이를 이용한 액정 표시 장치 |

| KR20120126223A (ko) * | 2011-05-11 | 2012-11-21 | 삼성디스플레이 주식회사 | 표시 기판 |

| KR101964766B1 (ko) * | 2011-08-16 | 2019-04-03 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| US9047838B2 (en) | 2012-03-14 | 2015-06-02 | Apple Inc. | Systems and methods for liquid crystal display column inversion using 3-column demultiplexers |

| US9245487B2 (en) | 2012-03-14 | 2016-01-26 | Apple Inc. | Systems and methods for reducing loss of transmittance due to column inversion |

| US9047826B2 (en) | 2012-03-14 | 2015-06-02 | Apple Inc. | Systems and methods for liquid crystal display column inversion using reordered image data |

| US9047832B2 (en) | 2012-03-14 | 2015-06-02 | Apple Inc. | Systems and methods for liquid crystal display column inversion using 2-column demultiplexers |

| US9368077B2 (en) | 2012-03-14 | 2016-06-14 | Apple Inc. | Systems and methods for adjusting liquid crystal display white point using column inversion |

| KR102252044B1 (ko) * | 2013-12-04 | 2021-05-17 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20150077579A (ko) * | 2013-12-27 | 2015-07-08 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| KR102201109B1 (ko) | 2014-03-06 | 2021-01-11 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20160013366A (ko) | 2014-07-25 | 2016-02-04 | 삼성디스플레이 주식회사 | 곡면 표시 장치 |

| CN104536225B (zh) * | 2014-12-31 | 2018-09-18 | 深圳市华星光电技术有限公司 | 液晶显示面板及液晶显示装置 |

| CN105068348B (zh) * | 2015-09-11 | 2018-03-27 | 京东方科技集团股份有限公司 | 一种阵列基板及其制造方法、显示面板及其驱动方法 |

| KR20170123384A (ko) | 2016-04-28 | 2017-11-08 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102509111B1 (ko) * | 2018-05-17 | 2023-03-13 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20210085377A (ko) * | 2019-12-30 | 2021-07-08 | 엘지디스플레이 주식회사 | 표시 장치 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000002889A (ja) * | 1998-06-16 | 2000-01-07 | Mitsubishi Electric Corp | 液晶表示装置 |

| JP2001142097A (ja) * | 1999-09-01 | 2001-05-25 | Nec Corp | 液晶表示装置とその製造方法 |

| JP2004062146A (ja) * | 2002-06-06 | 2004-02-26 | Sharp Corp | 液晶表示装置 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3102819B2 (ja) | 1992-06-02 | 2000-10-23 | 富士通株式会社 | 液晶表示装置及びその駆動方法 |

| US5610739A (en) * | 1994-05-31 | 1997-03-11 | Matsushita Electric Industrial Co., Ltd. | Liquid crystal display unit with a plurality of subpixels |

| JPH08179341A (ja) | 1994-12-22 | 1996-07-12 | Matsushita Electric Ind Co Ltd | 液晶表示装置およびその駆動方法 |

| JP3551594B2 (ja) | 1996-01-10 | 2004-08-11 | セイコーエプソン株式会社 | アクティブマトリクス基板 |

| US5852485A (en) * | 1996-02-27 | 1998-12-22 | Sharp Kabushiki Kaisha | Liquid crystal display device and method for producing the same |

| US6028581A (en) * | 1997-10-21 | 2000-02-22 | Sony Corporation | Method and apparatus for a liquid crystal display (LCD) having an input function |

| TWI282457B (en) * | 2000-04-06 | 2007-06-11 | Chi Mei Optoelectronics Corp | Liquid crystal display component with defect restore ability and restoring method of defect |

| JP2002333870A (ja) | 2000-10-31 | 2002-11-22 | Matsushita Electric Ind Co Ltd | 液晶表示装置、el表示装置及びその駆動方法、並びに副画素の表示パターン評価方法 |

| US7071911B2 (en) * | 2000-12-21 | 2006-07-04 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device, driving method thereof and electric equipment using the light emitting device |

| GB0125019D0 (en) * | 2001-10-18 | 2001-12-12 | Koninkl Philips Electronics Nv | Active matrix display device |

| KR100859524B1 (ko) | 2002-07-11 | 2008-09-22 | 삼성전자주식회사 | 박막 트랜지스터 기판 |

| JP4373119B2 (ja) | 2003-02-26 | 2009-11-25 | 大林精工株式会社 | 広視野角高速応答液晶表示装置 |

| US20040109119A1 (en) * | 2002-12-05 | 2004-06-10 | Hannstar Display Corporation | In-plane switching liquid crystal display with high aperture ratio |

| KR100925459B1 (ko) * | 2002-12-24 | 2009-11-06 | 삼성전자주식회사 | 다중 도메인 액정 표시 장치 및 그에 사용되는 표시판 |

| KR100961941B1 (ko) | 2003-01-03 | 2010-06-08 | 삼성전자주식회사 | 다중 도메인 액정 표시 장치용 박막 트랜지스터 표시판 |

| KR100935667B1 (ko) | 2003-03-06 | 2010-01-07 | 삼성전자주식회사 | 액정 표시 장치 |

| KR100961945B1 (ko) | 2003-03-26 | 2010-06-08 | 삼성전자주식회사 | 액정 표시 장치 및 그에 사용되는 표시판 |

| KR20040105934A (ko) | 2003-06-10 | 2004-12-17 | 삼성전자주식회사 | 다중 도메인 액정 표시 장치 및 그에 사용되는 표시판 |

| KR101122226B1 (ko) * | 2003-08-14 | 2012-03-21 | 삼성전자주식회사 | 다중 도메인 액정 표시 장치 및 그에 사용되는 표시판 |

| JP4265788B2 (ja) * | 2003-12-05 | 2009-05-20 | シャープ株式会社 | 液晶表示装置 |

| KR101197044B1 (ko) * | 2004-12-02 | 2012-11-06 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| US7538828B2 (en) * | 2005-01-10 | 2009-05-26 | Advantech Global, Ltd | Shadow mask deposition system for and method of forming a high resolution active matrix liquid crystal display (LCD) and pixel structures formed therewith |

| US7453086B2 (en) * | 2005-01-14 | 2008-11-18 | Samsung Electronics Co., Ltd. | Thin film transistor panel |

| KR101188601B1 (ko) * | 2005-04-13 | 2012-10-08 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

-

2005

- 2005-06-01 KR KR1020050046911A patent/KR101160831B1/ko active IP Right Grant

-

2006

- 2006-05-31 CN CN2006101108911A patent/CN1892391B/zh active Active

- 2006-06-01 JP JP2006154072A patent/JP5391435B2/ja active Active

- 2006-06-01 US US11/445,412 patent/US7956942B2/en active Active

-

2011

- 2011-04-29 US US13/097,579 patent/US8174472B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000002889A (ja) * | 1998-06-16 | 2000-01-07 | Mitsubishi Electric Corp | 液晶表示装置 |

| JP2001142097A (ja) * | 1999-09-01 | 2001-05-25 | Nec Corp | 液晶表示装置とその製造方法 |

| JP2004062146A (ja) * | 2002-06-06 | 2004-02-26 | Sharp Corp | 液晶表示装置 |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009042608A (ja) * | 2007-08-10 | 2009-02-26 | Casio Comput Co Ltd | アクティブマトリックス型表示装置 |

| JP2009139629A (ja) * | 2007-12-06 | 2009-06-25 | Sony Corp | 液晶表示装置およびその製造方法 |

| JP4702355B2 (ja) * | 2007-12-06 | 2011-06-15 | ソニー株式会社 | 液晶表示装置の製造方法 |

| US8487847B2 (en) | 2007-12-06 | 2013-07-16 | Sony Corporation | Liquid crystal display and method of manufacturing the same |

| KR101471547B1 (ko) * | 2008-02-20 | 2014-12-11 | 삼성디스플레이 주식회사 | 액정 표시 장치 |

| JP2015031961A (ja) * | 2013-08-02 | 2015-02-16 | 三星ディスプレイ株式會社Samsung Display Co.,Ltd. | 液晶表示装置 |

| US10712596B2 (en) | 2013-08-02 | 2020-07-14 | Samsung Display Co., Ltd. | Liquid crystal display |

| KR20150071772A (ko) * | 2013-12-18 | 2015-06-29 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102185787B1 (ko) | 2013-12-18 | 2020-12-03 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20150080148A (ko) * | 2013-12-30 | 2015-07-09 | 삼성디스플레이 주식회사 | 표시 패널 |

| KR102250217B1 (ko) * | 2013-12-30 | 2021-05-10 | 삼성디스플레이 주식회사 | 표시 패널 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20110205462A1 (en) | 2011-08-25 |

| CN1892391A (zh) | 2007-01-10 |

| CN1892391B (zh) | 2012-09-05 |

| US20060274009A1 (en) | 2006-12-07 |

| KR20060125090A (ko) | 2006-12-06 |

| KR101160831B1 (ko) | 2012-06-28 |

| JP5391435B2 (ja) | 2014-01-15 |

| US8174472B2 (en) | 2012-05-08 |

| US7956942B2 (en) | 2011-06-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5391435B2 (ja) | 液晶表示装置 | |

| JP4969109B2 (ja) | 液晶表示装置 | |

| JP5027437B2 (ja) | 液晶表示装置 | |

| JP5379951B2 (ja) | 液晶表示装置 | |

| JP5371022B2 (ja) | 液晶表示装置 | |

| JP4928797B2 (ja) | 液晶表示装置 | |

| JP5143362B2 (ja) | 液晶表示装置 | |

| JP2006309239A (ja) | 液晶表示装置 | |

| KR101230301B1 (ko) | 액정 표시 장치 및 그 구동 방법 | |

| KR20070057388A (ko) | 액정 표시 장치 | |

| JP2007011377A (ja) | 液晶表示装置 | |

| KR20080028032A (ko) | 액정 표시 장치 | |

| KR20060122118A (ko) | 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치 | |

| KR20070101503A (ko) | 액정 표시 장치 | |

| KR20090131842A (ko) | 액정 표시 장치 | |

| JP2008033326A (ja) | 液晶表示装置 | |

| KR101197047B1 (ko) | 박막 트랜지스터 표시판 및 액정 표시 장치 | |

| KR20080025498A (ko) | 액정 표시 장치 | |

| KR20070101549A (ko) | 액정 표시 장치 | |

| KR20070051036A (ko) | 액정 표시 장치 | |

| KR20070016412A (ko) | 액정 표시 장치 | |

| KR20070020745A (ko) | 액정 표시 장치 | |

| KR20070003317A (ko) | 박막 트랜지스터 표시판 및 이를 포함하는 액정 표시 장치 | |

| KR20070101578A (ko) | 액정 표시 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090519 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100514 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120515 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120809 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20121213 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130219 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130612 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130620 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130723 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130726 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130925 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5391435 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |