JP2006038779A - パターン形状評価方法、評価装置、及び半導体装置の製造方法 - Google Patents

パターン形状評価方法、評価装置、及び半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2006038779A JP2006038779A JP2004222737A JP2004222737A JP2006038779A JP 2006038779 A JP2006038779 A JP 2006038779A JP 2004222737 A JP2004222737 A JP 2004222737A JP 2004222737 A JP2004222737 A JP 2004222737A JP 2006038779 A JP2006038779 A JP 2006038779A

- Authority

- JP

- Japan

- Prior art keywords

- pattern

- value

- series data

- total value

- roughness

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01B—MEASURING LENGTH, THICKNESS OR SIMILAR LINEAR DIMENSIONS; MEASURING ANGLES; MEASURING AREAS; MEASURING IRREGULARITIES OF SURFACES OR CONTOURS

- G01B15/00—Measuring arrangements characterised by the use of electromagnetic waves or particle radiation, e.g. by the use of microwaves, X-rays, gamma rays or electrons

- G01B15/08—Measuring arrangements characterised by the use of electromagnetic waves or particle radiation, e.g. by the use of microwaves, X-rays, gamma rays or electrons for measuring roughness or irregularity of surfaces

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01N—INVESTIGATING OR ANALYSING MATERIALS BY DETERMINING THEIR CHEMICAL OR PHYSICAL PROPERTIES

- G01N23/00—Investigating or analysing materials by the use of wave or particle radiation, e.g. X-rays or neutrons, not covered by groups G01N3/00 – G01N17/00, G01N21/00 or G01N22/00

- G01N23/22—Investigating or analysing materials by the use of wave or particle radiation, e.g. X-rays or neutrons, not covered by groups G01N3/00 – G01N17/00, G01N21/00 or G01N22/00 by measuring secondary emission from the material

- G01N23/225—Investigating or analysing materials by the use of wave or particle radiation, e.g. X-rays or neutrons, not covered by groups G01N3/00 – G01N17/00, G01N21/00 or G01N22/00 by measuring secondary emission from the material using electron or ion

- G01N23/2251—Investigating or analysing materials by the use of wave or particle radiation, e.g. X-rays or neutrons, not covered by groups G01N3/00 – G01N17/00, G01N21/00 or G01N22/00 by measuring secondary emission from the material using electron or ion using incident electron beams, e.g. scanning electron microscopy [SEM]

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/70—Microphotolithographic exposure; Apparatus therefor

- G03F7/70483—Information management; Active and passive control; Testing; Wafer monitoring, e.g. pattern monitoring

- G03F7/70605—Workpiece metrology

- G03F7/70616—Monitoring the printed patterns

- G03F7/70625—Dimensions, e.g. line width, critical dimension [CD], profile, sidewall angle or edge roughness

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/22—Treatment of data

- H01J2237/221—Image processing

- H01J2237/223—Fourier techniques

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/26—Electron or ion microscopes

- H01J2237/28—Scanning microscopes

- H01J2237/2813—Scanning microscopes characterised by the application

- H01J2237/2817—Pattern inspection

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Analytical Chemistry (AREA)

- Health & Medical Sciences (AREA)

- Life Sciences & Earth Sciences (AREA)

- Chemical & Material Sciences (AREA)

- Electromagnetism (AREA)

- Biochemistry (AREA)

- General Health & Medical Sciences (AREA)

- Immunology (AREA)

- Pathology (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Length-Measuring Devices Using Wave Or Particle Radiation (AREA)

Abstract

【解決手段】エッジラフネスのデータは十分長い領域に渡って取得し、パワースペクトル上で操作者が設定した空間周波数領域に対応する成分を積算し、測長SEM上で表示する。または、十分長い領域のエッジラフネスデータを分割し、統計処理と理論計算によるフィッティングを行って、任意の検査領域に対応する長周期ラフネスと短周期ラフネスを算出し測長SEM上で表示する。

【選択図】図9

Description

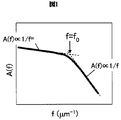

ラインエッジラフネスの空間周期の特徴を表すには、ラインエッジ位置あるいはライン幅を一定間隔で計測した系列データをフーリエ変換し、フーリエスペクトル(振幅スペクトルないしはパワースペクトル)を表示すればよい。これは前述の第二の課題を解決するものであるが、同時に第一の課題も解決できる。系列データの計測条件によらず、フーリエスペクトルの各周波数成分の大小を比較することで、ラフネスの大小関係を判定することができる。

また従来のCD計測は、ラインエッジラフネスの存在を前提としていない。例えばラインエッジラフネスの存在下では、ライン上のどこを計測するかによって、CD値も変わる。このためウエハ面内のCD均一性やウエハ間のCD変動量の計測値がランダムに発生するラインエッジラフネスに左右されるようになり、アニール温度のばらつきや下地膜厚ばらつきに起因するCDばらつきを正しく計測できなくなっている。CD計測方法自体にも対策が必要となりつつある。

本発明が解決しようとする課題は、ラインエッジラフネスの周波数分布の特徴や、ラインエッジラフネスの成分を除いたライン幅で表される、微細ラインパターン形状の特徴を求めるための方法及び装置を提供することである。

指標としては、sc 2、sc、2sc、3sc、6scが適当である。このうちsc 2は上記の計算により直接求めることができる、残りの量はsc 2の平方根を求め、各々それの1倍、2倍、3倍、6倍を求めればよい。尚、操作者がどの指標を用いるかは予め設定しておく。1つの系列データと、設定されたa,bの値から得られる指標の値は検査用の観測装置あるいはコンピュータ上に表示される。また自動的に電子ファイルとして記録することが可能である。

また、用いる対象パターンとしてはさまざまなパターンが可能であるが、特にラインパターンを用いるとよい。これは、データを取得する間隔が任意に設定できるためである。例えば密集ホールパターンの直径を系列データとして用いる場合は、データ間の間隔をパターンの周期と等しくとらねばならない。

周波数分布を反映したライン幅ラフネス評価方法としては、さらに次に示す方法がある。即ち、そのラインパターンから作成される典型的なサイズのトランジスタの、性能劣化を引き起こす短周期ラフネス成分即ち前述の第一のラフネスと、性能ばらつきを引き起こす長周期ラフネス成分即ち第二のラフネスとを算出するというものである。(この方法は狭義のラインエッジラフネスの評価方法ではない。)おおよその手順は以下のようなものである。

この系列データから、連続するM個のデータで構成されたグループを取り出す。グループの数をNとする。即ち、一番目のグループはw1, w2,・・・wM、二番目のグループはwM+1, wM+2, ・・・w2M、となる。ここでN及びMは

次に、各グループについてデータの平均値と標準偏差を算出する。これによって標準偏差の値がN個得られるので、これらの平均値を求め、s1と定義する。この値は、ゲート幅L2のトランジスタを作成したときに、トランジスタ領域内に発生するライン幅ラフネスの大きさの指標となる。平均ライン幅の値がN個得られるので、これらの標準偏差を求め、s2と定義する。この値は、ゲート幅L2のトランジスタを作成したときの、CD値のトランジスタ間ばらつきの指標となる。

次に、上記の手順で得られた3点、P(L1, s0)、Q(L2, s1)、R(L2, s2)を、以下のフィッティング曲線の組でフィッティングする。

さらにフーリエ振幅スペクトルを他の関数形で仮定することで、より適切なフィッティング関数g(L)、h(L)を得ることも可能である。

またこのとき、フィッティングの信頼性を高く保つためには第一に、十分長い領域の観測結果が必要であり、これには元の系列データを取得する領域の長さは2mm以上とすることが適当である。第二に、標準偏差を求めるという統計的処理をするにあたって十分なサンプル数が必要であり、これにはグループの数Nを6以上とすることが適切である。

本実施例で記述される半導体製造プロセスでは、短チャネル効果が生じにくい構造をもつトランジスタを生産していた。そのため、周期の短いライン幅ラフネスの影響は比較的小さかった。しかし周期の長いラフネスによるトランジスタ性能のばらつきは無視できず、致命的な歩留まり低下を招く恐れがあり、リソグラフィ工程終了後の寸法検査時に長周期ラフネスをモニターする必要があった。ラフネスの指標が一定値以下のウエハは次工程に回されるが、一定値を超えたウエハはレジスト剥離を経て再度リソグラフィを行う。

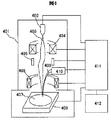

まずリソグラフィ工程を終えたウエハを図4に示す検査装置に投入した。ウエハ407はステージ408上に載せられ、電子線403を照射される。ウエハ上の、検査されるチップは図5の斜線部分に示されるように決められていた。このチップ上の同じ相対座標に存在する長さ5mm、幅約100nmのラインパターンが検査対象となるパターンである。これらの各パターン上のほぼ中心位置を視野中心とするよう、ステージ408や照射電子線403が移動して、各パターンに関して検査を行った。この検査の手順は図6に示される。

この図6に示された工程の検査が、図5に示されたチップ上の予定された全てのラインパターンに対して行われた。次に、ウエハの良否判定がなされた。

また上記の手順で得られたCD値はラインエッジラフネスの影響を殆ど受けない。そのため、ウエハ面内のCD均一性やウエハ間のCDばらつきを算出する際にこれらの値を用いて、より精確にこれらの量を算出することができた。

また上記の手順においてはディスプレイ上に表示されるスペクトルをフーリエ振幅スペクトルとしたが、パワースペクトルでもよい。実際に行う計算はパワースペクトル上の積分であることから、パワースペクトルを表示させるとより直感的に理解がしやすく、誤操作に気づきやすいという利点がある。

本実施例で記述される半導体製造プロセスでは、主としてゲート幅wgが300nm程度のトランジスタを作成しており、周期が300nmよりも長いラフネスによるトランジスタ性能のばらつきが、歩留まり低下を招く恐れがあった。同時に、周期100nm以下の細かいラフネスがレジストパターン上に存在すると、ドライエッチング時にその部分がダメージを受けて大きく削れてしまうという現象が見いだされた。このため、リソグラフィ工程終了後の寸法検査時に、周期300nm以上の長周期ラフネスと同時に周期100nm以下の短周期ラフネスをモニターする必要が生じた。

第一の実施例と同じように、まずリソグラフィ工程を終えたウエハを図4に示す検査装置に投入した。検査されるパターンやその位置は第一の実施例と同じであった。

各パターンに対して行われた検査内容を、図10を用いて説明する。

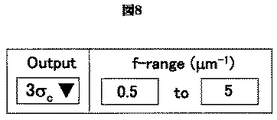

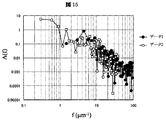

積算範囲が入力されると、工程1008に進み、f=0.5からf=3.3に相当する領域のパワースペクトルの積分値sc 2が計算され、この値から得られるラフネス指標3scが示された。

これらの数値を入力すると、工程1008に進み、短周期ラフネス指標が表示された。このパターンに対する検査はこれで終了したため工程1010に進み、上記全ての評価結果が検査装置の記憶領域に保存され、本パターンに関する検査は終了した。

この検査が、図5に示されたチップ上の予定された全てのラインパターンに対して行われた。次に、ウエハの良否判定がなされた。

このように本発明を実施することにより、早い段階で不良品になる可能性の高いウエハを取り除き、製造をやり直すことが可能になったため、歩留まりが向上するとともに廃棄ウエハが大幅に減少し環境への負荷が減らされた。

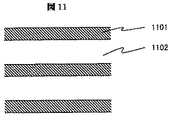

本実施例で記述される半導体製造プロセスでは、重要なラインパターンの層を加工するステップより前に、その下地層に、図11に示すようにゲート用のラインと垂直な方向に走る金属材料のラインパターンを形成していた。この金属パターンの上に絶縁材料を製膜し平坦になるよう加工した後、反射防止膜を形成し、レジスト膜を塗布形成し、このレジスト膜をライン状に加工する。

本検査では、第一の実施例で述べた各パターンに対する検査を行った。その手順は第一の実施例と同じく図6で表される。検査対象となるパターン上に視野を移し、工程601で二次元信号強度分布を取得した。観察倍率や視野のサイズは第一の実施例と同じであった。

次に工程602に進んでノイズを低減した後、工程603で検査領域を設定した。次に工程604でライン幅の系列データを取得した。ここでも計測パラメータは第一の実施例と全て同じであった。次に工程605でフーリエ変換を施した結果が工程606で積算範囲入力ウィンドウとともに検査装置モニター上に表示された。

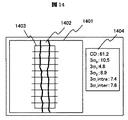

ここで工程607にて、積算範囲の下限を2、上限を3と入力し、この成分の抽出を行ったところ、全体のラフネス指標(3s)は10.2nmであるのに対し、この成分3scは4.7nmとなった。これらの数値は検査装置の記憶領域に保存された。

本実施例で記述される半導体製造プロセスでは、主としてゲート幅wgが500nm程度のトランジスタを作成しており、周期が500nmよりも長いラフネスによるトランジスタ性能のばらつきが、歩留まり低下を招く恐れがあった。同時に、トランジスタ性能の劣化に関係するトランジスタ領域内のラフネスも迅速に評価する必要があった。このため、リソグラフィ工程終了後の寸法検査時に、検査時間を増やさずに長周期ラフネスと短周期ラフネスをモニターする必要が生じた。

本実施例の半導体製造工程では、CD値は55から65nm、3sは12nm以下、短周期ラフネス3s_intra(wg)は9nm以下、長周期ラフネスの指標3s_inter(wg)は8nm以下を基準とし、検査されたチップのパターン合計10個について、全部がこの基準を満たしている場合にウエハを良品と判定、次工程に回していた。本ウエハでは全てのチップにおいてこれらの基準が満たされたため、本ウエハは次工程であるドライエッチングに回された。

また、上記の短・長周期ラフネス指標を用いて、例えば非特許文献1や非特許文献7に記されている手法でラフネス起因のトランジスタ性能劣化やばらつきを簡単に見積もることができる。具体的には3s_intraの結果から、トランジスタの内部のゲート長分布を中心値が設計値で分散がs_intra2となるガウス分布であると仮定し、しきい値電圧の低下や暗電流の増加を計算することができる。また3s_interの結果から、前述のゲート長分布の中心値がs_inter程度の幅をもったガウス分布になると仮定し、トランジスタが複数個あった場合のしきい値電圧の分布を算出することができる。

本実施例では、半導体素子生産工程を構築するための研究開発段階において、観察条件の異なる2枚のパターン画像に対して本発明を適用し、ラフネスの大小を判定した例を示す。

本実施例では、実施例1で用いた装置を用いた。本例を実施した際には装置にウエハサンプルはロードされておらず、装置は、コンピュータ内部の記憶領域に保存されている2枚の画像を解析する目的で用いられた。これら2枚の観察画像に写っているパターンは1本のラインパターンであり、画像のほぼ中央にあった。

402 電子銃

403 電子線

404 収束レンズ

405 偏向器

406 対物レンズ

407 観察ウエハ

408 ステージ

409 二次電子

410 検出器

411 走査型電子線顕微鏡の制御系

412 検査を行うコンピュータ

501 パターンが形成されたウエハ

601 二次元信号強度分布の取得

602 ノイズ低減

603 検査領域設定

604 系列データ取得

605 フーリエ変換

606 フーリエスペクトルと積算範囲入力ウィンドウの表示

607 積算範囲の設定

608 計算、計算結果の表示及び結果の保存

1001 二次元信号強度分布の取得

1002 ノイズ低減

1003 検査領域設定

1004 系列データ取得

1005 フーリエ変換

1006 フーリエスペクトルと積算範囲入力ウィンドウの表示

1007 積算範囲の設定

1008 計算及び計算結果の表示

1009 現状データの評価を終了するか続けるかの選択

1010 計算結果の保存

1101 金属材料から成るラインパターン

1102 絶縁材料から成るラインパターン

1201 レジスト膜下層の金属材料から成るラインパターン

1202 レジストパターン

1301 二次元信号強度分布の取得

1302 ノイズ低減

1303 検査領域設定

1304 系列データ取得

1305 s0の計算

1306 系列データの分割

1307 s1及びs2の計算

1308 計算結果の画面上への表示

1309 理論曲線によるフィッティング

1310 Wg設定

1311 ラフネス指標の計算

1312 全結果の表示と保存

1401 取得した観察画像

1402 検査対象のラインパターン

1403 検査領域を表す枠線

1404 結果表示領域。

Claims (16)

- 被測定物に荷電粒子線を照射しながら走査して、被測定物から放出される二次電子または反射電子を検出して、その強度の2次元分布を濃淡画像化する工程と、

前記画像内の評価対象パターンの境界となる点の位置を、基準直線に沿って一定間隔で計測して、パターンエッジの系列データを生成する工程と、

前記系列データをフーリエ変換する工程と、

特定の周波数領域の指定入力、または予め設定された特定の周波数領域に従い、前記特定の領域の周波数に対するフーリエ係数の絶対値の二乗の値を全て足し合わせて合計値を算出する工程と、及び

前記評価対象パターン形状の特徴を表す指標として、前記合計値、前記合計値の平方根、前記合計値の平方根の2倍、前記合計値の平方根の3倍、および前記合計値の平方根の6倍の少なくとも一つ以上の値を表示する工程とを含むことを特徴とするパターン形状評価方法。 - 被測定物に荷電粒子線を照射しながら走査して、被測定物から放出される二次電子または反射電子を検出して、その強度の2次元分布を濃淡画像化する工程と、

前記画像内の評価対象パターンを、基準直線に沿って一定間隔で前記基準直線と垂直方向の前記評価対象パターンの寸法を計測して、パターン寸法の系列データを生成する工程と、

前記系列データをフーリエ変換する工程と、

特定の周波数領域の指定入力、または予め設定された特定の周波数領域に従い、前記特定の領域の周波数に対するフーリエ係数の絶対値の二乗の値を全て足し合わせて合計値を算出する工程と、及び

前記評価対象パターン形状の特徴を表す指標として、前記合計値、前記合計値の平方根、前記合計値の平方根の2倍、前記合計値の平方根の3倍、および前記合計値の平方根の6倍の少なくとも一つ以上の値を表示する工程とを含むことを特徴とするパターン形状評価方法。 - 前記評価対象パターンがラインパターンであることを特徴とする請求項1、または請求項2に記載のパターン形状評価方法。

- 前記基準直線に沿って計測を行う間隔が10nm以下の値であり、前記計測された領域の前記基準直線に沿った長さが2mm以上であることを特徴とする請求項1、または請求項2に記載のパターン形状評価方法。

- 前記特定の領域の周波数に対するフーリエ係数の絶対値の二乗の値を全て足し合わせて合計値を算出する工程は、

前記指定入力される、または前記予め設定される特定の周波数領域の下限が0.5mm-1、上限が1 mm-1から10 mm-1の間のある値である場合について前記合計値を算出する工程であることを特徴とする請求項1、または請求項2に記載のパターン形状評価方法。 - 前記特定の領域の周波数に対するフーリエ係数の絶対値の二乗の値を全て足し合わせて合計値を算出する工程は、

前記指定入力される、または前記予め設定される特定の周波数領域の下限が

指定される特定の周波数領域の下限が1 mm-1から10 mm-1の間のある値で、上限が100 mm-1である場合について前記合計値を算出する工程であることを特徴とする請求項1、または請求項2に記載のパターン形状評価方法。 - 前記指定入力される、または前記予め設定される特定の周波数領域の上限あるいは下限が、作成される物品上のパターン長の逆数であることを特徴とする請求項1、または請求項2に記載のパターン形状評価方法。

- 前記指定入力される、または前記予め設定される特定の周波数領域の上限あるいは下限が、作成されるトランジスタのゲート幅の逆数であることを特徴とする請求項1、または請求項2に記載のパターン形状評価方法。

- 前記系列データをフーリエ変換する工程に続いて、

前記パターン寸法の系列データから寸法のゆらぎの成分を取り除いたパターン寸法を、前記系列データをフーリエ変換して得られるフーリエ係数の絶対値のうち、空間周波数が0の場合の値から算出することを特徴とする請求項2に記載のパターン形状評価方法。 - 微細パターンの寸法を、基準直線に沿って一定間隔で計測して、前記パターン寸法の系列データを生成する工程と、

前記系列データの分布の標準偏差s0を算出する工程と、

前記系列データを連続するM個のデータずつN個のグループに分ける工程と、

前記各グループ内のM個のデータの平均値と標準偏差を算出する工程と、

前記工程で得られたN個の標準偏差の平均値s1を得るとともに、前記工程で得られたN個の平均値の標準偏差s2を算出する工程と、

前記s0、s1、およびs2の値を予め求めておいた基準曲線でフィッティングする工程と、

前記得られたフィッティング曲線と、設定された寸法Lとから、長さLの領域内のパターン寸法のばらつきの予測値と、長さLの領域の代表寸法値を複数領域について求めたときの代表寸法値間のばらつきの予測値とを算出する工程とを含むことを特徴とするパターン形状評価方法。 - 前記計測されたパターン領域の基準となる直線に沿った長さが2mm以上であり、Nが6以上であることを特徴とする請求項10に記載のパターン形状評価方法。

- 前記系列データをフーリエ変換して得られるフーリエ係数の絶対値もしくはフーリエ係数の絶対値の二乗を周波数に対してプロットした図を表示する工程をさらに含むことを特徴とする請求項1、または請求項2に記載のパターン形状評価方法。

- 操作者が指定入力した特定の周波数領域を、前記の図の上に表示する工程をさらに含むことを特徴とする請求項12に記載のパターン形状評価方法。

- 前記評価対象パターン形状の特徴を表す指標として、前記パターンエッジの系列データまたは前記パターン寸法の系列データをフーリエ変換して得られるフーリエ級数の絶対値の二乗すなわちパワースペクトルP(f)を求め、空間周波数fの特定の積算範囲(a mm-1からb mm-1まで)を満たす全てのP(f)の和であるsc 2、sc、2sc、3sc、または6scのいずれかを選択するように、メニューを提示して、操作者に選択を促す工程をさらに含むことを特徴とする請求項1、または請求項2に記載のパターン形状評価方法。

- 荷電粒子線源と、

前記荷電粒子線源より放出された荷電粒子線を収束レンズ及び対物レンズを通して試料に照射し走査する光学系と、

前記試料を載置するステージと、

前記荷電粒子線の照射によって試料から放出される二次電子ないしは反射電子の強度を検出する検出器と、

前記走査によって得られる二次電子ないしは反射電子の二次元強度分布から、ラインパターンのエッジ位置ないしは寸法の変動のうち任意の周波数領域の空間周波数をもつ成分、ないしは任意の周波数を境界としそれよりも低い空間周波数をもつ成分と高い空間周波数をもつ成分、ないしは空間周波数が0となる成分を抽出し表示する手段とを有することを特徴とするパターン形状評価装置。 - パターンが形成された半導体ウエハを検査ステージに載置する工程と、

前記パターンを視野に収めるように荷電粒子線を照射しながら走査して、前記ウエハから放出される二次電子または反射電子を検出して、その強度の2次元分布を濃淡画像化する工程と、

前記画像内の前記評価対象パターンを、基準直線に沿って一定間隔で前記基準直線と垂直方向の前記評価対象パターンの寸法を計測して、パターン寸法の系列データを生成する工程と、

前記系列データのCD値、および標準偏差を算出する工程と、

前記系列データをフーリエ変換して、予め設定された特定の領域の周波数に対するフーリエ係数の絶対値の二乗の値を全て足し合わせて合計値を求め、前記合計値、前記合計値の平方根、前記合計値の平方根の2倍、前記合計値の平方根の3倍、または前記合計値の平方根の6倍の値のいずれかを評価指標として算出する工程と、

前記CD値、前記標準偏差、および前記評価指標のそれぞれの値が、予め設定されたそれぞれの基準値を満たす場合に、前記半導体ウエハを合格と判定して、次の半導体プロセスへ投入する工程と、および

前記CD値、前記標準偏差、および前記評価指標の少なくとも1つの値が、予め設定されたそれぞれの基準値を満たさない場合に、前記半導体ウエハを不合格と判定して、前記半導体ウエハを前記形成されたパターンを再度形成し直す半導体プロセスへ投入する工程とを含むことを特徴とする半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004222737A JP2006038779A (ja) | 2004-07-30 | 2004-07-30 | パターン形状評価方法、評価装置、及び半導体装置の製造方法 |

| US11/185,852 US7366620B2 (en) | 2004-07-30 | 2005-07-21 | Evaluation method of fine pattern feature, its equipment, and method of semiconductor device fabrication |

| US12/078,840 US7684937B2 (en) | 2004-07-30 | 2008-04-07 | Evaluation method of fine pattern feature, its equipment, and method of semiconductor device fabrication |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004222737A JP2006038779A (ja) | 2004-07-30 | 2004-07-30 | パターン形状評価方法、評価装置、及び半導体装置の製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007196889A Division JP2007333745A (ja) | 2007-07-30 | 2007-07-30 | パターン形状評価方法、評価装置、及び半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006038779A true JP2006038779A (ja) | 2006-02-09 |

| JP2006038779A5 JP2006038779A5 (ja) | 2008-12-04 |

Family

ID=35801063

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004222737A Withdrawn JP2006038779A (ja) | 2004-07-30 | 2004-07-30 | パターン形状評価方法、評価装置、及び半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7366620B2 (ja) |

| JP (1) | JP2006038779A (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008020735A (ja) * | 2006-07-13 | 2008-01-31 | Toshiba Corp | フォトマスクの評価方法及び半導体装置の製造方法 |

| WO2010052855A1 (ja) * | 2008-11-05 | 2010-05-14 | 株式会社日立ハイテクノロジーズ | パターン寸法計測方法及びそれを用いた走査電子顕微鏡 |

| JP2011163991A (ja) * | 2010-02-12 | 2011-08-25 | Hitachi High-Technologies Corp | 寸法計測装置およびこれを用いた半導体装置の製造方法 |

| JP2015176873A (ja) * | 2014-03-12 | 2015-10-05 | 株式会社東芝 | シミュレーション方法、シミュレーション装置、及び、コンピュータ読み取り可能な記録媒体 |

| WO2020066128A1 (ja) * | 2018-09-25 | 2020-04-02 | 株式会社日立ハイテクノロジーズ | パターン形状評価装置、パターン形状評価システム及びパターン形状評価方法 |

| JP2020519902A (ja) * | 2017-05-17 | 2020-07-02 | アプライド マテリアルズ イスラエル リミテッド | 製造プロセス欠陥を検出するための方法、コンピュータプログラム製品およびシステム |

| CN114359112A (zh) * | 2022-03-11 | 2022-04-15 | 领伟创新智能系统(浙江)有限公司 | 基于加工表面图像Hoyer系数的表面粗糙度评估方法 |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4385139B2 (ja) * | 2006-02-01 | 2009-12-16 | 国立大学法人電気通信大学 | 変位検出方法、及び、変位検出装置、変位検出プログラム、並びに、位相特異点マッチング処理方法、位相特異点マッチング処理プログラム |

| US8284394B2 (en) | 2006-02-09 | 2012-10-09 | Kla-Tencor Technologies Corp. | Methods and systems for determining a characteristic of a wafer |

| CN101567048B (zh) * | 2008-04-21 | 2012-06-06 | 夏普株式会社 | 图像辨别装置及图像检索装置 |

| KR101647010B1 (ko) * | 2008-06-19 | 2016-08-10 | 케이엘에이-텐코어 코오포레이션 | 웨이퍼의 하나 이상의 특성들을 결정하기 위한 컴퓨터-구현 방법들, 컴퓨터-판독 가능 매체, 및 시스템들 |

| US8298958B2 (en) * | 2008-07-17 | 2012-10-30 | Lam Research Corporation | Organic line width roughness with H2 plasma treatment |

| JP2010034402A (ja) * | 2008-07-30 | 2010-02-12 | Toshiba Corp | パターン形状予測方法 |

| US7879727B2 (en) * | 2009-01-15 | 2011-02-01 | Infineon Technologies Ag | Method of fabricating a semiconductor device including a pattern of line segments |

| KR20120006492A (ko) * | 2009-04-27 | 2012-01-18 | 아사히 가라스 가부시키가이샤 | SiC 피막을 갖는 반도체 열처리 부재 |

| JP5802997B2 (ja) * | 2010-05-05 | 2015-11-04 | ディジマーク コーポレイション | 隠された画像のシグナリング |

| JP2014055789A (ja) * | 2012-09-11 | 2014-03-27 | Nuflare Technology Inc | パターン評価方法およびパターン評価装置 |

| US9311640B2 (en) | 2014-02-11 | 2016-04-12 | Digimarc Corporation | Methods and arrangements for smartphone payments and transactions |

| JP6129651B2 (ja) * | 2013-06-11 | 2017-05-17 | 株式会社日立ハイテクノロジーズ | ラインパターンの形状評価方法及びその装置 |

| US10656532B2 (en) | 2017-04-13 | 2020-05-19 | Fractilia, Llc | Edge detection system and its use for optical proximity correction |

| US11521825B2 (en) | 2017-04-13 | 2022-12-06 | Fractilia, Llc | System and method for predicting stochastic-aware process window and yield and their use for process monitoring and control |

| US11508546B2 (en) | 2017-04-13 | 2022-11-22 | Fractilia, Llc | System and method for low-noise edge detection and its use for process monitoring and control |

| US11355306B2 (en) | 2017-04-13 | 2022-06-07 | Fractilia, Llc | System and method for generating and analyzing roughness measurements and their use for process monitoring and control |

| US10176966B1 (en) | 2017-04-13 | 2019-01-08 | Fractilia, Llc | Edge detection system |

| US10648801B2 (en) | 2017-04-13 | 2020-05-12 | Fractilia, Llc | System and method for generating and analyzing roughness measurements and their use for process monitoring and control |

| US11361937B2 (en) | 2017-04-13 | 2022-06-14 | Fractilia, Llc | System and method for generating and analyzing roughness measurements and their use for process monitoring and control |

| US11380516B2 (en) | 2017-04-13 | 2022-07-05 | Fractilia, Llc | System and method for generating and analyzing roughness measurements and their use for process monitoring and control |

| US10664955B2 (en) | 2017-04-13 | 2020-05-26 | Fractilia, Llc | Edge detection system and its use for machine learning |

| US10488188B2 (en) | 2017-04-13 | 2019-11-26 | Fractilia, Llc | System and method for removing noise from roughness measurements |

| US10522322B2 (en) | 2017-04-13 | 2019-12-31 | Fractilia, Llc | System and method for generating and analyzing roughness measurements |

| US10731979B2 (en) * | 2018-01-12 | 2020-08-04 | Applied Materials Israel Ltd. | Method for monitoring nanometric structures |

| CN114674858B (zh) * | 2022-03-14 | 2024-08-27 | 中南大学 | 一种三元正极材料性能指标综合评价方法及装置 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000117483A (ja) * | 1998-10-15 | 2000-04-25 | Kobe Steel Ltd | 溶接用ワイヤ |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4040809B2 (ja) * | 1999-09-22 | 2008-01-30 | 株式会社東芝 | 微細パターン測定方法、微細パターン測定装置及び微細パターン測定プログラムを記録した記録媒体 |

| JP2002243428A (ja) | 2001-02-13 | 2002-08-28 | Hitachi Ltd | パターン検査方法およびその装置 |

| JP3870044B2 (ja) | 2001-07-25 | 2007-01-17 | 株式会社日立製作所 | パターン検査方法及びパターン検査装置 |

| DE10160172B4 (de) * | 2001-12-07 | 2016-06-09 | Carl Zeiss Microscopy Gmbh | Laserscanningmikroskop und Laserscanningmikroskopieverfahren |

| JP4364524B2 (ja) | 2003-02-20 | 2009-11-18 | 株式会社日立製作所 | パターン検査方法 |

| CN1906478B (zh) * | 2003-12-10 | 2011-02-16 | 以色列商·应用材料以色列公司 | 先进的粗糙度测量方法 |

-

2004

- 2004-07-30 JP JP2004222737A patent/JP2006038779A/ja not_active Withdrawn

-

2005

- 2005-07-21 US US11/185,852 patent/US7366620B2/en active Active

-

2008

- 2008-04-07 US US12/078,840 patent/US7684937B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000117483A (ja) * | 1998-10-15 | 2000-04-25 | Kobe Steel Ltd | 溶接用ワイヤ |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7477406B2 (en) | 2006-07-13 | 2009-01-13 | Kabushiki Kaisha Toshiba | Photomask evaluation method and manufacturing method of semiconductor device |

| JP2008020735A (ja) * | 2006-07-13 | 2008-01-31 | Toshiba Corp | フォトマスクの評価方法及び半導体装置の製造方法 |

| WO2010052855A1 (ja) * | 2008-11-05 | 2010-05-14 | 株式会社日立ハイテクノロジーズ | パターン寸法計測方法及びそれを用いた走査電子顕微鏡 |

| JP5386502B2 (ja) * | 2008-11-05 | 2014-01-15 | 株式会社日立ハイテクノロジーズ | パターン寸法計測方法及びそれを用いた走査電子顕微鏡 |

| JP2011163991A (ja) * | 2010-02-12 | 2011-08-25 | Hitachi High-Technologies Corp | 寸法計測装置およびこれを用いた半導体装置の製造方法 |

| JP2015176873A (ja) * | 2014-03-12 | 2015-10-05 | 株式会社東芝 | シミュレーション方法、シミュレーション装置、及び、コンピュータ読み取り可能な記録媒体 |

| JP2020519902A (ja) * | 2017-05-17 | 2020-07-02 | アプライド マテリアルズ イスラエル リミテッド | 製造プロセス欠陥を検出するための方法、コンピュータプログラム製品およびシステム |

| JP7159212B2 (ja) | 2017-05-17 | 2022-10-24 | アプライド マテリアルズ イスラエル リミテッド | 製造プロセス欠陥を検出するための方法、コンピュータプログラム製品およびシステム |

| WO2020066128A1 (ja) * | 2018-09-25 | 2020-04-02 | 株式会社日立ハイテクノロジーズ | パターン形状評価装置、パターン形状評価システム及びパターン形状評価方法 |

| TWI733184B (zh) * | 2018-09-25 | 2021-07-11 | 日商日立全球先端科技股份有限公司 | 圖案形狀評價裝置、圖案形狀評價系統及圖案形狀評價方法 |

| JP2020051771A (ja) * | 2018-09-25 | 2020-04-02 | 株式会社日立ハイテクノロジーズ | パターン形状評価装置、パターン形状評価システム及びパターン形状評価方法 |

| US11713963B2 (en) | 2018-09-25 | 2023-08-01 | Hitachi High-Tech Corporation | Pattern shape evaluation device, pattern shape evaluation system, and pattern shape evaluation method |

| CN114359112A (zh) * | 2022-03-11 | 2022-04-15 | 领伟创新智能系统(浙江)有限公司 | 基于加工表面图像Hoyer系数的表面粗糙度评估方法 |

| CN114359112B (zh) * | 2022-03-11 | 2022-06-14 | 领伟创新智能系统(浙江)有限公司 | 基于加工表面图像Hoyer统计值的表面粗糙度评估方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7684937B2 (en) | 2010-03-23 |

| US7366620B2 (en) | 2008-04-29 |

| US20080215274A1 (en) | 2008-09-04 |

| US20060036409A1 (en) | 2006-02-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2006038779A (ja) | パターン形状評価方法、評価装置、及び半導体装置の製造方法 | |

| JP4801427B2 (ja) | パターン形状評価方法 | |

| US7049589B2 (en) | Pattern inspection method | |

| US7095884B2 (en) | Method and apparatus for circuit pattern inspection | |

| CN111443094B (zh) | 样本检验的方法及其系统 | |

| JP5400882B2 (ja) | 半導体検査装置及びそれを用いた半導体検査方法 | |

| JP2006215020A5 (ja) | ||

| JP4787673B2 (ja) | パターン検査装置および方法 | |

| KR101810436B1 (ko) | 라인 패턴의 형상 평가 방법 및 그 장치 | |

| TW201913230A (zh) | 圖案測定方法、及圖案測定裝置 | |

| TW202046246A (zh) | 圖像處理程式、圖像處理裝置及圖像處理方法 | |

| KR102483920B1 (ko) | Cd-sem 주사 전자 현미경에 의한 특성화에 대한 방법 | |

| JP5321775B2 (ja) | パターン検査方法およびパターン検査装置 | |

| JP2007333745A (ja) | パターン形状評価方法、評価装置、及び半導体装置の製造方法 | |

| Kenslea et al. | CD-TEM: Characterizing impact of TEM sample preparation on CD metrology | |

| JP4961500B2 (ja) | パターン形状評価装置 | |

| US8526708B2 (en) | Measurement of critical dimensions of semiconductor wafers | |

| US11455715B2 (en) | Epitaxy metrology in fin field effect transistors | |

| JP2006234808A (ja) | 計測システム | |

| JP2008116472A (ja) | パターン検査方法 | |

| US20240219313A1 (en) | Measurement deviation analysis for a semiconductor specimen | |

| US11921063B2 (en) | Lateral recess measurement in a semiconductor specimen | |

| JP2006319351A (ja) | パターン検査方法及びパターン検査装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060509 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070730 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070730 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070730 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081017 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100316 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100513 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100713 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101008 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101008 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20101029 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101214 |

|

| A313 | Final decision of rejection without a dissenting response from the applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A313 Effective date: 20110321 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20110415 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20110426 |