従来、例えばCCD型イメージセンサやMOS型イメージセンサなどの半導体イメージセンサは、量産性に優れているため、例えばビデオカメラ、デジタルカメラ、カメラ付き携帯電話装置などの携帯型電子情報機器において画像入力デバイスとして利用されている。このような携帯型電子情報機器では、電池で駆動するため、駆動電力の低電圧化および低消費電力化が重要であり、さらに、低コスト化およびモジュールサイズの縮小化が重要である。このため、この分野において、MOS型イメージセンサは、CCD型イメージセンサに比べて、消費電力が少なく、従来のCMOSプロセス技術を利用することにより低コスト化が可能で、センサ素子と周辺回路素子とを同一チップ上に作製することによりモジュールサイズの縮小化が可能となることから、MOS型イメージセンサが見直されている。

このようなMOS型イメージセンサとして、例えば特許文献1および特許文献2には、閾値電圧変調方式のMOS型イメージセンサが開示されている。以下に、このMOS型イメージセンサについて、図9および図10を用いて詳細に説明する。

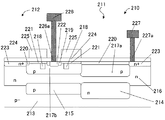

図9は、従来の閾値電圧変調方式のMOS型イメージセンサにおける単位画素部の構成例を示す平面図であり、図10は図9の単位画素部のAA’線断面図である。なお、ここでは図示していないが、このMOS型イメージセンサは、複数の単位画素部が行方向および列方向に2次元状でマトリックス状に配置されている。

図9および図10に示すように、単位画素部210には、光電変換用の受光部を持つ受光ダイオード211と、光信号検出用のMOSトランジスタ212とが隣接して設けられている。単位画素部210の図中の上下には、列方向に並ぶ複数の単位画素部210に接続されて、ドレイン配線227およびゲート配線228が設けられている。また、MOSトランジスタ212上を通るように、行方向に並ぶ複数の単位画素部210に接続されてソース配線226が設けられている。

シリコン基板またはシリコン基板上のエピタキシャル半導体層213(以下、p型基板213という)内には、受光ダイオード211の形成領域および光信号検出用MOSトランジスタ212の形成領域にわたってn型層216が設けられ、このn型層216上の受光ダイオード211領域にp型ウェル領域217aが設けられ、MOSトランジスタ212の領域にはp型ウェル領域217bが設けられている。また、n型層216下の受光ダイオード211の形成領域にはn型層214が設けられ、n型層216下の光信号検出用MOSトランジスタ212の形成領域にはp型埋め込み層215が設けられている。

受光ダイオード211は、光電変換された信号電荷の発生領域であるp型ウェル領域217aと、そのp型ウェル領域217aの表面側に設けられたn型領域220とを有している。

MOSトランジスタ212は、平面視リング状のゲート電極225と、ゲート電極225で囲まれた中央部のn型ソース領域219と、n型ドレイン領域220と、電流担体が移動可能とするチャネル領域221と、キャリアポケット領域218と、n型ソースコンタクト層222と、n型ドレインコンタクト層223とを有している。

ゲート電極225は、p型ウェル領域217bの上方にゲート絶縁膜224を介して平面視リング状に形成されており、ゲートコンタクトホール228aを介してゲート配線228と接続されている。

n型ソース領域219は、このリング状のゲート電極225の内側中央部(平面視)でp型ウェル領域217bの表層部に設けられている。

n型ドレイン領域220は、リング状のゲート電極225の外周側を更に囲むようにp型ウェル領域217aの表層部に設けられている。受光ダイオード211において、このn型ドレイン領域220に対して、光発生電荷が得られるp型ウェル領域217aが埋め込み構造になっている。

n型ソース領域219およびドレイン領域220はMOSトランジスタ212の低濃度ソース/ドレインとして働くため、表面付近での不純物濃度は約3.0×1018cm−3程度に設定されている。

ソースコンタクト層222は、n型ソース領域219の更に中央部に設けられており、ソースコンタクトホール226aを介してソース配線(ソース電極)226が接続されている。

ドレインコンタクト層223は、ドレイン領域220外周端部に接して、受光ダイオード211のp型ウェル領域217aおよびMOSトランジスタ212のp型ウェル領域217bを囲むようにn型層216の表層部に設けられており、このドレインコンタクト層223とドレインコンタクトホール227aを介してドレイン領域220とドレイン配線(ドレイン電極)227とが接続されている。

ソースコンタクト層222およびドレインコンタクト層223の表面不純物濃度は、金属界面とのコンタクト抵抗を減らすため、通常、シリコン中の不純物固溶度限界付近である約3.0×1020cm−3程度に設定されている。

チャネル領域221は、ゲート電極225下にゲート絶縁膜224を介して、n型ソース領域219とn型ドレイン領域220との間のp型ウェル領域217b上の表層部に、n型チャネルドープ層として設けられている。

キャリアポケット領域218(電荷蓄積領域;例えばホールポケット領域)は、チャネル領域221下であって、n型ソース領域219近傍のp型ウェル領域217b内にソース領域219を囲むようにリング状に形成されている。このホールポケット領域218は、p型ウェル領域217bよりも不純物濃度が高い高濃度埋込層として形成されている。このホールポケット領域218に、受光ダイオード211で光照射により発生した正孔(ホール;光信号キャリア)が蓄積され、このホールポケット領域218内の光信号キャリアの蓄積量に比例してMOSトランジスタ212の閾値が変化するようになっている。

さらに、MOSイメージセンサを駆動する駆動回路などの周辺回路をCMOSプロセスによりp型基板213上に作製することも可能である。

図11は、この固体撮像素子において、周辺回路領域に設けられるCMOS回路の構成例を示す断面図である。

図11に示すように、このCMOS回路は、p型基板213上に、n−MOS領域231とp−MOS領域232とが隣接して設けられており、フィールド酸化膜244によって互いに素子分離されている。

n−MOS領域231は、p型基板213上に設けられたp型層233の表層部に低濃度n型ソース領域およびドレイン領域235が所定の間隔を開けて設けられている。また、低濃度n型ソース領域およびドレイン領域235間の外側表層部にはそれぞれ、高濃度n型(n+)ソースコンタクト層およびドレインコンタクト層237がそれぞれ設けられており、各コンタクトホール245aをそれぞれ介してソース配線およびドレイン配線245とそれぞれ接続されている。

また、低濃度n型ソース領域およびドレイン領域235の間のp型層233上には、ゲート絶縁膜241を介してゲート電極242が設けられており、その側壁はサイドウォール243で覆われている。チャネル領域236は、ゲート電極242の下方で、低濃度n型ソース領域およびドレイン領域235間のp型層233の表層部に低濃度p型層として形成される。

p−MOS領域232は、p型基板213上に設けられたn型層234の表層部に低濃度p型ソース領域およびドレイン領域238が所定の間隔を開けて設けられている。また、低濃度p型ソース領域およびドレイン領域238間の外側表層部にはそれぞれ、高濃度p型(p+)ソースコンタクト層およびドレインコンタクト層240がそれぞれ設けられており、各コンタクトホール245aをそれぞれ介してソース配線およびドレイン配線245とそれぞれ接続されている。

また、低濃度p型ソース領域およびドレイン領域238の間のn型層234上には、ゲート絶縁膜241を介してゲート電極242が設けられており、その側壁はサイドウォール243で覆われている。チャネル領域239は、低濃度p型ソース領域およびドレイン領域238間のn型層234の表層部に低濃度p型層として形成される。

上記構成により、この固体撮像装置(例えばMOS型イメージセンサ)の基本動作について説明する。なお、この固体撮像装置の単位画素部においては、その一連の撮像動作として、初期化(リセット)動作、電荷蓄積動作および信号読み出し動作という各動作が繰り返して行われる。

まず、初期化期間には、ゲート電極225、ソース配線226およびドレイン配線227に正の高電圧が印加されてホールポケット領域218に残存する光信号キャリアがp型埋め込み層215を介して基板213側に排出される。

次に、電荷蓄積期間には、受光ダイオード211への光照射により発生した光信号キャリアである正孔(ホール)が、ホールポケット領域218内に蓄積される。

さらに、信号読み出し期間には、ホールポケット領域218への光信号キャリアの蓄積量に比例した信号がn型ソース領域219から出力されて検出される。

図12は、上記単位画素部210が行方向および列方向に2次元状でマトリクス状に複数配列されたMOS型イメージセンサの撮像動作時における入出力タイミングを示すタイミング図である。ここでは、ある行(選択行)のゲート電位、ドレイン電位およびソース電位と、他の行(非選択行)のゲート電位およびドレイン電位を示している。

図12に示すように、まず、初期化期間には、選択行においてゲート電極225のゲート電位およびドレイン配線227のドレイン電位として6V程度の高電圧が印加される。これにより、ゲート電極225下ではチャネル領域が形成され、n型ソース領域219のソース電位も6V程度となる。ホールポケット領域218に残存する信号電荷(ホール)がp型埋め込み層215を介して基板213側に排出される。このとき、非選択行では、ゲート電極225のゲート電位が接地電位付近に固定されている。

次に、電荷蓄積期間には、選択行においてドレイン配線227のドレイン電位が3Vに下げられ、受光ダイオード211のp型ウェル領域217a内にて光電変換により信号電荷が生成され、ホールポケット領域218に信号電荷(ホール)が蓄積される。このとき、ゲート電位は3V程度に下げられて、光信号検出用トランジスタ212は飽和領域で動作しており、ソース電位は1.5V程度となっている。

さらに、信号読み出し期間には、ソース配線226に定電流源が接続され、ドレイン領域220、ゲート電極225およびn型ソース領域219によってソースフォロワ回路が構成される。この状態でゲート電位Vgに3V程度の電位を印加してMOSトランジスタ212を飽和領域で動作させることにより、ホールポケット領域218に蓄積された信号電荷量に応じてソース電位が変調されて信号電荷が検出される。

ここで、単位画素部210が行方向および列方向に複数配列されたMOS型イメージセンサでは、ソース配線226が行方向に接続されている。このため、行毎に順次画素信号を出力させる場合、ある行(選択行)の電荷蓄積期間中に他の行(非選択行)の初期化動作(非選択初期化)および読み出し動作(非選択読み出し)が行われる。

これにより、例えば非選択行の初期化動作時には、ソース配線226に6V程度の高電圧が印加される。しかしながら、図12に示すように選択行のゲート電極225のゲート電位を接地電位(0V)付近に保つことにより、チャネルドープ層(チャネル領域221)の電位が接地電位付近に固定され、ホールポケット領域218のポテンシャルは低い状態に保たれる。これにより、選択行のホールポケット領域218に蓄積された信号電荷(ホール)は基板213側に排出されることなく保存される。この期間が非選択初期化期間である。

また、非選択行の信号読み出し動作時にも、選択行のゲート電極225の電圧を接地電位付近に保つことにより、ソース配線226に選択行の信号が出力されることを防いでいる。この期間が非選択信号読み出し期間である。

次に、上記MOS型イメージセンサの製造方法について、図13(a)〜図13(d)を用いて説明する。

図13(a)〜図13(d)は、従来のMOS型イメージセンサの製造工程について説明するための各製造工程の基板部の断面図である。ここでも、単位画素部210の右側に受光ダイオード211の形成領域、左側に光信号検出用MOSトランジスタ212の形成領域が示されている。

図13(a)は、ゲート電極225が形成された直後の状態を示している。ここでは、p型半導体基板または半導体基板上のp型エピタキシャル成長半導体層(p型基板)213上にn型層216が形成されている。

受光ダイオード211の形成領域には、p型基板213およびn型層216に接するようにn型埋め込み層214が形成されている。その上方のn型層216内に、n型埋め込み層214とほぼ同じ寸法を有するp型ウェル領域217aが形成されている。これらのn型埋め込み層214とp型ウェル領域217aは、共に第1のマスク層を通してイオン注入により形成されている。

また、MOSトランジスタ212の形成領域にはp型基板213およびn型層216に接するようにp型埋め込み層215が形成されている。その上方のn型層216内に、p型埋め込み層215とほぼ同じ寸法を有するp型ウェル領域217bが形成されている。これらのp型埋め込み層215とp型ウェル領域217bとは、共に第2のマスクを通してイオン注入により形成されている。

p型ウェル領域217bの表層部側には、n型チャネルドープ層(チャネル領域221)が形成されている。また、このチャネルドープ層(チャネル領域221)下に接してp型ウェル領域217b内にp型高濃度埋め込み層(ホールポケット領域218)が形成されている。このp型高濃度埋め込み層(ホールポケット領域218)は第3のマスクを通してイオン注入により形成されている。

このように、ゲート電極225が形成された状態で、図13(b)に示すように、ゲート電極225をマスクとして、ゲート絶縁膜224を通してn型不純物をイオン注入することにより、ゲート電極225の両側に低濃度のn型ソース領域219およびドレイン領域220を形成する。この固体撮像素子において、p型基板213上に図11に示すようなCMOS回路を形成する場合には、この製造工程と同時に、例えばn−CMOS領域231のゲート電極242の両側に低濃度n型ソース領域およびドレイン領域235を形成する。

さらに、上記基板部上に、CVD(Chemical Vapor Deposition)法などにより絶縁膜を形成し、異方性エッチングを行って、図13(c)に示すように、ゲート電極225の側面にその絶縁膜からなるサイドウォール229を形成する。

図13(d)に示すように、受光ダイオード211の受光領域を覆うようにレジストマスク230を形成した後、ゲート電極225、サイドウォール229およびレジストマスク230をマスクとしてn型不純物をイオン注入する。これにより、n型ソース領域219の中央部およびn型ドレイン領域220の周辺部にはそれぞれ、高濃度n型ソースコンタクト層222および高濃度n型ドレインコンタクト層223がそれぞれ形成される。

この固体撮像素子において、p型基板213上に図11に示すようなCMOS回路を形成する場合には、この工程と同時に、例えばn−CMOS領域231のゲート電極の両側であって、低濃度n型ソース領域およびドレイン領域235の外側に高濃度n型ソースコンタクト層およびドレインコンタクト層237を形成する。

以降、図示は省略するが、レジストマスク230を除去した後、層間絶縁膜を形成し、コンタクトホール226a〜228aをそれぞれ形成し、ゲート配線228、ソース配線226およびドレイン配線227を形成することにより、図9および図10に示すようなMOS型イメージセンサが作製される。

特開平11−195778号公報

特開2001−22335号公報

上記従来のMOS型イメージセンサでは、受光ダイオード211および光信号検出用MOSトランジスタ212が、光発生電荷(この場合にはホール)に対して埋込構造を有しているため、光発生電荷以外の電荷による雑音や暗電流を低く維持することができるとされている。

しかしながら、本願発明者らが上記従来のMOS型イメージセンサを試作したところ、初期化動作電圧に比例した暗電流ノイズの発生が見られた。以下に、この暗電流発生のメカニズムについて、図14を用いて詳細に説明する。

図14は、従来のMOS型イメージセンサにおけるソースコンタクト部近傍の構造、対応する基板表面付近のn型不純物濃度分布、および非選択初期化動作時の電界分布を示す図である。ここでは、横軸にソースコンタクト部(ソース領域とソース配線とのコンタクト部)からの距離(μm)を示し、縦軸は非選択初期化動作時の電界強度(V/cm)と基板表面付近のn型不純物濃度(cm−3)を示している。

図14の基板表面付近のn型不純物濃度分布に示すように、MOSトランジスタのソース/ゲート領域では高濃度ソースコンタクト層222からチャネルドープ層221にかけて急激に不純物濃度が低下している。一般に、高濃度ソースコンタクト層の表面不純物濃度は、金属−半導体界面のコンタクト抵抗を可能な限り低くし、かつ、オームの法則に従うオーミック接触を得ることが可能なように、約3.0×1020cm−3程度まで高められている。また、低濃度ドレイン領域220は、図13に示す従来の製造方法によれば、受光ダイオード211におけるp型ウェル領域217aの表層側のn型不純物層と同程度の表面不純物濃度であり、その値は約3.0×1018cm−3程度である。また、チャネルドープ層221の表面不純物濃度は約3.0×1017cm−3程度である。

非選択初期化動作時には、図12に示すように、ソース配線226を通じてソース領域219および高濃度ソースコンタクト層222に正の高電圧が印加され、同時にチャネルドープ層221の電位が接地電位付近に保たれる。このような状態では、図14の非選択初期化動作時の電界強度分布に示すように、高濃度ソースコンタクト層222からチャネルドープ層221にかけて急激に電界が高くなる。

暗電流の発生原因は、半導体基板中の結晶構造の乱れや不純物によってミドルギャップに生じた準位が電子−ホール対の発生中心として働き、そこに高電界が働くことにより発生した電子−ホール対が電流となることである。よって、図14に示すように、高濃度ソースコンタクト層222からチャネルドープ層221にかけて急激に電界が高くなった領域に、このような電子−ホール対の発生中心が存在したことにより暗電流が発生したものと考えられる。

このような電子−ホール対の発生中心の生成要因としては、良好な金属−半導体結合を形成するために形成された高濃度ソースコンタクト層222への不純物イオン注入が考えられる。実際に本願発明者らが上記従来のMOS型イメージセンサを試作して高濃度ソースコンタクト層222を透過型電子顕微鏡にて観察したところ、大規模な結晶欠陥の発生が見られた。

これらの考察から、初期化動作電圧に比例した暗電流の発生は、高濃度ソースコンタクト層222とチャネルドープ層221の遷移領域に結晶欠陥が達したことにより存在した電子−ホール対の発生中心が、非選択初期化動作時に発生する高電界状態と結びついたことによるものと考えられる。

上記従来のMOS型イメージセンサにおいては、信号読み出し時以外にソース/ドレイン電極に殆ど電流が流れることはなく、信号読み出し時においても、その読み出し電流値はソース配線226に接続された定電流源により制御され、大きく変動することはない。したがって、ソース/ドレインコンタクト部において非オーミック接触であることは、動作上問題ではない。

そこで、本願発明者らは、高濃度イオン注入による結晶欠陥の導入を回避するため、高濃度ソースコンタクト層222を設けない構造についても試作したが、従来技術と同様に、初期化動作電圧に比例した暗電流ノイズの発生が見られた。以下に、この暗電流発生のメカニズムについて、図15を用いて詳細に説明する。

図15は、高濃度ソースコンタクト層を設けないMOS型イメージセンサにおけるソースコンタクト部近傍の構造、対応する基板表面付近のn型不純物濃度分布、および非選択初期化動作時の電界分布を示す図である。ここでは、横軸にソースコンタクト部(ソース領域とソース配線とのコンタクト部)からの距離(μm)を示し、縦軸は非選択初期化動作時の電界強度(V/cm)と基板表面付近のn型不純物濃度(cm−3)を示している。

図15の基板表面付近のn型不純物濃度分布に示すように、ソースコンタクトホール226aと半導体基板との接触領域の不純物濃度は低濃度ソース領域であり、その不純物濃度は約3.0×1018cm−3程度である。また、チャネルドープ層221の表面不純物濃度は約3.0×1017cm−3程度である。

ここで、図15の非選択初期化動作時の電界強度分布に着目すると、図14に示す従来の構造と比較して、ソースコンタクトホール226aを介してソース配線226と接触する領域の電界強度が大幅に上昇し、1.0×104V/cm以上となっていることが分かる。

ソース領域219の表面には、サイドウォールエッチング時のエッチングダメージにより界面準位が発生する。また、ソースコンタクトホール形成のためのドライエッチングにより、コンタクトホール226aの周辺にも界面準位が発生する。図14に示す従来の構造では、これらの界面準位の発生領域は、高濃度不純物注入によって、その電界が十分低くなっていたのに対して、図15に示すように、高濃度ソースコンタクト層222を設けない構造では、これらの界面準位の存在領域において電界強度が強くなり、暗電流が発生したものと考えられる。

以上ではソースコンタクト部について説明したが、ソースコンタクト部と同時に作製されるドレインコンタクト部(ドレイン領域とドレイン配線とのコンタクト部)についてもソースコンタクト部と同様の問題が生じる。

本発明は、上記従来の課題を解決するもので、コンタクト部近傍の結晶欠陥発生を抑制し、かつ、非選択初期化動作時にコンタクト部近傍の電界強度を低減して、暗電流が少なく、初期化動作時の電圧に依存する白点欠陥の発生を抑制し、安定した高い感度特性が得られる固体撮像素子およびその製造方法、これを撮像部に用いた電子情報機器を提供することを目的とする。

本発明の固体撮像素子は、光照射により電荷を発生可能とする受光部と、該受光部からの電荷を蓄積可能とする電荷蓄積領域とを有し、該電荷蓄積領域の蓄積電荷量に応じた信号読み出しを可能とする信号検出用トランジスタ手段を備えた単位画素部が複数配列された固体撮像素子において、該信号検出用トランジスタ手段には、ソース領域およびドレイン領域が所定間隔を置いて設けられ、該ソース領域に所定電位を印加するためのソース配線と該ソース領域間に設けられ、該ソース領域よりも高い不純物濃度のソースコンタクト層と、該ドレイン領域に所定電位を印加するためのドレイン配線と該ドレイン領域間に設けられ、該ドレイン領域よりも高い不純物濃度のドレインコンタクト層とのうち少なくとも該ソースコンタクト層は、その界面準位により暗電流の発生が抑えられると共に不純物導入による結晶欠陥が回避されるように、該コンタクト層表面近傍の不純物濃度が設定されており、そのことにより上記目的が達成される。

また、好ましくは、本発明の固体撮像素子におけるドレインコンタクト層およびソースコンタクト層のうち少なくとも該ソースコンタクト層は、該コンタクト層表面近傍の不純物濃度が4×1019cm−3以上9×1019cm−3以下に設定されている。

さらに、好ましくは、本発明の固体撮像素子におけるドレインコンタクト層およびソースコンタクト層のうち少なくとも該ソースコンタクト層は、該コンタクト層表面近傍の不純物濃度が6×1019cm−3以上8×1019cm−3以下に設定されている。

さらに、好ましくは、本発明の固体撮像素子における受光部と電荷蓄積領域は、第1導電型半導体基板上の第2導電型ウェル領域内に設けられた第1導電型ウェル領域内に設けられ、前記信号検出用トランジスタ手段は、該第1導電型ウェル領域の表面上に所定の間隔を開けて設けられた第2導電型ソース領域および第2導電型ドレイン領域を有する。

さらに、好ましくは、本発明の固体撮像素子における第1導電型がp型であり、前記第2導電型がn型である。

さらに、好ましくは、本発明の固体撮像素子における第1導電型がn型であり、前記第2導電型がp型である。

さらに、好ましくは、本発明の固体撮像素子におけるソースコンタクト層は、前記第1導電型ウェル領域の表面に沿って前記ソース領域に隣接する該第1導電型ウェル領域の表層部に形成されている。

さらに、好ましくは、本発明の固体撮像素子におけるドレインコンタクト層は、前記ドレイン領域の外周端部に接して、前記受光部および信号検出用トランジスタ手段を囲むように、前記第2導電型ウェル領域の表層部に形成されている。

さらに、好ましくは、本発明の固体撮像素子における電荷蓄積領域は、高濃度第1導電型半導体領域からなり、前記第1導電型ウェル領域内で該第2導電型ソース領域近傍位置に該第2導電型ソース領域を囲むように平面視リング状に設けられた高濃度埋込層であり、 該高濃度埋込層は、前記ドレイン領域から該第2導電型ソース領域に至る経路を構成するチャネル領域の直下に設けられている。

さらに、好ましくは、本発明の固体撮像素子における高濃度埋込層は、チャネル幅方向全域にわたって形成されている。

さらに、好ましくは、本発明の固体撮像素子における光信号検出用トランジスタ手段は、前記第1導電型ウェル領域上にゲート絶縁膜を介して設けられた平面視リング状のゲート電極を有し、前記ソース領域は該ゲート電極に囲まれた該第1導電型ウェル領域の表層部に形成されている。

さらに、好ましくは、本発明の固体撮像素子におけるドレイン領域は前記ゲート電極を囲むように前記第1導電型ウェル領域の表層部に形成されている。

さらに、好ましくは、本発明の固体撮像素子における基板上に、前記複数の単位画素部が設けられた画素領域と、該複数の画素領域を駆動する駆動回路が設けられた駆動回路領域とを有し、該駆動回路を構成するCMOS回路は、前記光信号検出用トランジスタ手段のソースコンタクト層およびドレインコンタクト層よりも高い不純物濃度のソースコンタクト層およびドレインコンタクト層を有する。

本発明の固体撮像素子の製造方法は、請求項1〜13のいずれかに記載の固体撮像素子を製造する固体撮像素子の製造方法であって、前記光信号検出用トランジスタ手段のゲート電極の形成後に、該ゲート電極をマスクとして低濃度の第2導電型不純物を表面側から導入することによりソース領域およびドレイン領域を形成するトランジスタ駆動領域形成工程と、該トランジスタ駆動領域形成工程の後に、該ゲート電極の側壁にサイドウォールを形成するサイドウォール形成工程と、該サイドウォール形成工程の後に、該第1導電型ウェル領域に形成された受光部を覆うようにマスクパターンを形成するマスクパターン形成工程と、該マスクパターン形成工程の後に、該ゲート電極、該ゲート電極のサイドウォールおよび該マスクパターンをそれぞれマスクとして該ソース領域およびドレイン領域よりもそれぞれ狭い範囲に第2導電型不純物を、コンタクト層の界面準位により暗電流の発生が抑えられると共に不純物導入による結晶欠陥が回避される該コンタクト層表面近傍の不純物濃度で導入することにより、前記コンタクト層を形成するコンタクト層形成工程とを有し、そのことにより上記目的が達成される。

また、好ましくは、本発明の固体撮像素子の製造方法において、請求項14に記載の画素領域のソースコンタクト層およびドレインコンタクト層を第2導電型不純物導入により形成する前記コンタクト層形成工程とは別に、前記CMOS回路を構成する第2導電型CMOS領域のソース領域およびドレイン領域を第2導電型不純物導入により形成する工程を更に有する。

本発明の電子情報機器は、請求項1〜13のいずれかに記載の固体撮像素子と、該固体撮像素子からの撮像信号を信号処理する画像処理部とを有し、そのことにより上記目的が達成される。

上記構成により、以下に、本発明の作用について説明する。

本発明においては、ゲート電極やサイドウォール部を形成後に、これらをマスクとして用いて、第1導電型高濃度埋込層(キャリアポケット領域;電荷蓄積領域)に隣接したソース領域の表層部に第2導電型不純物を更に導入することにより、表面近傍の不純物濃度(ピーク不純物濃度)が4×1019cm−3以上9×1019cm−3以下であるソースコンタクト層を形成する。また同様に、ゲート電極やサイドウォール部を形成後に、受光部にマスクパターンを形成し、これらをマスクとして用いて、ドレイン領域に接して受光部と光信号検出用トランジスタ手段とを囲むように第2導電型半導体層の表層部に第2導電型不純物を導入することにより、ピーク不純物濃度が4×1019cm−3以上9×1019cm−3以下であるドレインコンタクト層を形成する。

ソースコンタクト層のピーク不純物濃度を、通常良好な半導体/金属界面コンタクト特性を得るために設定される3×1020cm−3よりも低く、9×1019cm−3以下に設定することにより、例えばイオン注入法などによる不純物導入に伴う結晶欠陥や非晶質化が回避される。これにより、高濃度不純物層であるソースコンタクト層と低濃度不純物層である低濃度ソース領域やチャネルドープ層との界面に、結晶欠陥により導かれた暗電流発生中心が存在することを回避して、暗電流の発生を回避することができる。

また、ソースコンタクト層の不純物濃度がピーク不純物濃度を、4×1019cm−3以上に設定することにより、固体撮像素子の撮像動作サイクル中、ソース電極(ソース配線)とチャネルドープ層の電位差が最大となる非選択初期化動作時において、サイドウォールエッチング時のエッチングダメージにより界面準位により暗電流が発生するソース領域表面、およびソースコンタクトホール形成のためのドライエッチングにより界面準位により暗電流が発生するコンタクト電極周辺部などの電界強度を2×103V/cm以下に抑制し、暗電流の発生を回避することができる。

さらに、周辺回路(駆動回路)領域を構成するCMOS回路のソースコンタクト層およびドレインコンタクト層については、光信号検出用トランジスタ手段のソースコンタクト層およびドレインコンタクト層と異なる不純物導入工程で形成することにより、ピーク不純物濃度を高くして、良好な半導体/金属界面コンタクト特性(オーミックコンタクト)を得るための3×1020cm−3程度に設定することができる。

以上説明したように、本発明によれば、周辺回路の特性劣化を招くことなく、固体撮像素子を構成する単位画素部のソースコンタクト層のピーク不純物濃度を4×1019cm−3以上9×1019cm−3以下に設定することにより、暗電流が少なく、初期化動作時の電圧に依存する白点欠陥の発生を抑制し、安定して高い感度特性が得られる固体撮像素子を作製し、これを撮像部に用いた携帯型電子機器などの電子情報機器を実現することが可能となる。

以下に、本発明の固体撮像素子を閾値電圧変調方式のMOS型イメージセンサに適用した場合の実施形態について、図面を参照しながら説明する。なお、本発明の固体撮像素子は、MOS型イメージセンサに限定されるものではない。

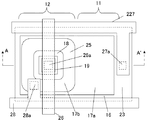

図1は、本発明の固体撮像素子の一実施形態であるMOS型イメージセンサの構成例を模式的に示す一部平面図であり、図2は図1の単位画素部の構成例を示す平面図であり、図3は図2の単位画素部のAA’線断面図である。なお、図2および図3では、一つの単位画素部の構造について示しているが、他の単位画素部についても同様の構造を有している。

図1に示すように、固体撮像素子100は、閾値電圧変調方式のMOS型イメージセンサとして機能し、複数の単位画素部10が行方向および列方向に2次元上でマトリックス状に配置されている。複数の単位画素部10は、行方向にソース配線26によって接続され、列方向にドレイン配線27およびゲート配線28によって接続されている。

図2および図3に示すように、単位画素部10には、図9および図10に示した従来の固体撮像素子の単位画素部210の場合と同様に、光電変換用の受光ダイオード11と、光信号検出用トランジスタ手段としてのMOSトランジスタ12とが隣接して設けられている。

単位画素部10の図中の上下位置には、列方向に並ぶ複数の単位画素部10に接続されて、ドレイン配線27およびゲート配線28が設けられている。また、MOSトランジスタ12の上を通るように、行方向に並ぶ複数の単位画素部10に接続されて、ソース配線26が設けられている。

シリコン基板またはシリコン基板上のエピタキシャル半導体層13(以下、p型基板13という)上には、受光ダイオード11の形成領域および光信号検出用MOSトランジスタ12の形成領域にわたってn型層16が設けられ、このn型層16上の受光ダイオード11の領域にp型ウェル領域17aが設けられ、n型層16上のMOSトランジスタ12の領域にはp型ウェル領域17bが設けられている。

また、n型層16下の受光ダイオード11の形成領域側には、p型基板13との間にn型層14が設けられ、n型層16下の光信号検出用MOSトランジスタ12側の形成領域には、p型基板13との間にp型埋め込み層15が設けられている。

受光ダイオード11は、光電変換された信号電荷の発生領域であるp型ウェル領域17aと、そのp型ウェル領域17aの表面側に設けられたn型領域20とを有している。

MOSトランジスタ12は、p型ウェル領域17a内で光電変換された信号電荷を蓄積可能とするキャリアポケット領域18と、n型ソース領域19と、受光ダイオード11のn型領域20と一体的に形成されたn型ドレイン領域20と、電流担体が移動するためのチャネル領域21と、n型ソース領域19とソース配線26の先端部間に設けられたn型ソースコンタクト層22と、n型ドレイン領域20とドレイン配線27の先端部間に設けられたn型ドレインコンタクト層23と、チャネル領域21の上方にゲート絶縁膜24を介して設けられた平面視リング状のゲート電極25とを有している。

キャリアポケット領域18(電荷蓄積領域;例えばホールポケット領域)は、チャネル領域21下にあって、n型ソース領域19の近傍のp型ウェル領域17b内にソース領域19を囲むように平面視リング状に形成されている。このホールポケット領域18は、p型ウェル領域17bよりも不純物濃度が高い高濃度埋込層として形成されている。このホールポケット領域18に、受光ダイオード11で光照射により発生した正孔(ホール;光信号キャリア)が蓄積され、このホールポケット領域18内の光信号キャリアの蓄積量に比例してMOSトランジスタ12の閾値が変化するようになっている。

n型ソース領域19は、平面視リング状のゲート電極25の内側中央でp型ウェル領域17bの表層部に設けられている。

n型ドレイン領域20は、平面視リング状のゲート電極25の外周を囲むようにp型ウェル領域17bの表層部に設けられている。このn型ドレイン領域20は、受光ダイオード11部において、p型ウェル領域17aの表面側に設けられたn型領域20と一体的に形成されており、これによって光発生電荷に対する埋め込み構造が形成されている。

ソース領域19およびドレイン領域20はMOSトランジスタ12の低濃度ソース/ドレインとして働くため、表面付近での不純物濃度は約3.0×1018cm−3程度に設定されている。

チャネル領域21は、ゲート電極25下にゲート絶縁膜24を介して、n型ソース領域19とn型ドレイン領域20との間のp型ウェル領域17bの表層部に、n型チャネルドープ層として設けられている。

ソースコンタクト層22はソース領域19の表層部に設けられており、このソースコンタクト層22およびソースコンタクトホール26aを介してソース領域19とソース配線(ソース電極)26とが接続されている。

ドレインコンタクト層23は、ドレイン領域20の外周端部に接して、受光ダイオード11のp型ウェル領域17aおよびMOSトランジスタ12のp型ウェル領域17bを囲むようにn型層16の表層部に設けられており、このドレインコンタクト層23およびドレインコンタクトホール27aを介してドレイン領域20とドレイン配線27(ドレイン電極)とが接続されている。

これらのソースコンタクト層22およびドレインコンタクト層23の表面不純物濃度は、本実施形態では4×1019cm−3以上9×1019cm−3以下に設定されている。これは本発明の特徴構成であり、その理由について説明すると、4×1019cm−3以上に設定することにより、サイドウォールエッチング時やコンタクトホール形成時にエッチングダメージにより界面準位により暗電流が生じるソース領域表面やコンタクト部の周辺部において、不純物注入により電界を低くすることができるため、非選択初期化動作時に電界強度を2×103V/cm以下に抑制して暗電流を防ぐことができる。また、9×1019cm−3以下に設定することにより、不純物導入に伴う結晶欠陥や非晶質化が回避され、ソースコンタクト層22とソース領域19やチャネルドープ層(チャネル領域21)との界面に結晶欠陥による暗電流発生中心が生じるのを防ぐことができる。以下に詳細に説明する。

ゲート電極25は、p型ウェル領域17bの上方にゲート絶縁膜24を介してリング状に形成されており、ゲートコンタクトホール28aを介してゲート配線28と接続されている。なお、ここでは特に図示していないが、ゲート電極25の側壁はサイドウォールで覆われていてもよい。

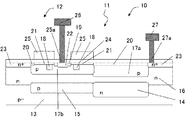

さらに、図1には示していないが、p型基板13上に、図2および図3に示すような単位画素部10が複数設けられた画素領域を駆動する駆動回路などの周辺回路領域(駆動回路領域)をCMOSプロセスにより設ける構成も可能である。この場合のCMOS回路について図4を用いて説明する。

図4は、本実施形態の固体撮像素子(MOS型イメージセンサ)100において、周辺回路領域に設けられるCMOS回路の構成例を示す断面図である。

図4に示すように、このCMOS回路は、図11に示す従来の固体撮像素子のCMOS回路の場合と同様に、p型基板13上に、n−MOS領域31とp−MOS領域32とが互いに隣接して設けられており、フィールド酸化膜44によって素子分離されている。

n−MOS領域31は、p型基板13上に設けられたp型層33の表層部に低濃度n型ソース領域およびドレイン領域35が所定の間隔を開けて設けられている。また、低濃度n型ソース領域およびドレイン領域35に隣接する表層部にはそれぞれ、高濃度n型(n+)ソースコンタクト層およびドレインコンタクト層37がそれぞれ設けられており、各コンタクトホール45aをそれぞれ介してソース配線およびドレイン配線45とそれぞれ接続されている。また、低濃度n型ソース領域およびドレイン領域35の間のp型層33上には、ゲート絶縁膜41を介してゲート電極42が設けられており、その側壁はサイドウォール43で覆われている。チャネル領域36は、ゲート電極42の下方にあって、低濃度n型ソース領域およびドレイン領域35間のp型層33の表層部に低濃度n型層として形成されている。

p−MOS領域32は、p型基板13上に設けられたn型層34の表層部に低濃度p型ソース領域およびドレイン領域38が所定の間隔を開けて設けられている。また、低濃度p型ソース領域およびドレイン領域38に隣接する表層部にはそれぞれ、高濃度p型(p+)ソースコンタクト層およびドレインコンタクト層40がそれぞれ設けられており、各コンタクトホール45aをそれぞれ介してソース配線およびドレイン配線45とそれぞれ接続されている。また、低濃度p型ソース領域およびドレイン領域39の間のn型層34上には、ゲート絶縁膜41を介してゲート電極42が設けられており、その側壁はサイドウォール43で覆われている。チャネル領域39は、ゲート電極42の下方にあって、低濃度p型ソース領域およびドレイン領域38間のn型層34の表層部に低濃度p型層として形成されている。

以下に、上記構成の固体撮像素子100(例えばMOS型イメージセンサ)の基本動作について説明する。なお、この固体撮像装置100の単位画素部10においては、その一連の撮像動作として、初期化(リセット)動作、電荷蓄積動作および信号読み出し動作という各動作が繰り返して行われる。

まず、初期化期間には、ゲート電極25、ソース配線26およびドレイン配線27に正の高電圧が印加されてホールポケット領域18に残存する光信号キャリアがp型埋め込み層15を介して基板13側に排出される。

次に、電荷蓄積期間には、受光ダイオード11への光照射により発生した光信号キャリアである正孔(ホール)が、ホールポケット領域18内に蓄積される。

さらに、信号読み出し期間には、ホールポケット領域18への光信号キャリアの蓄積量に比例した信号がソース領域19から出力されて検出される。

図5は、上記単位画素部10が行方向および列方向に複数配列されたMOS型イメージセンサの撮像動作時における入出力タイミングを示すタイミング図である。ここでは、選択行のゲート電位、ドレイン電位およびソース電位と、非選択行のゲート電位およびドレイン電位を示している。

図5に示すように、まず、初期化期間には、選択行においてゲート電極25のゲート電位およびドレイン配線27のドレイン電位として6V程度の高電圧が印加される。これにより、ゲート電極25下ではチャネル領域21が形成され、ソース領域19のソース電位も6V程度となる。ホールポケット領域18に残存する信号電荷(ホール)がp型埋め込み層15を介して基板13側に排出される。このとき、非選択行では、ゲート電極25のゲート電位が0Vとされている。

次に、電荷蓄積期間には、選択行においてドレイン配線27のドレイン電位が3Vに下げられ、受光ダイオード11のp型ウェル領域17a内にて光電変換により信号電荷が生成されて、ホールポケット領域18に信号電荷(ホール)が蓄積される。このとき、ゲート電位は3V程度に下げられて、光信号検出用トランジスタ12は飽和領域で動作しており、ソース電位は1.5V程度となっている。

さらに、信号読み出し期間には、ソース配線26に定電流源が接続され、ドレイン領域20、ゲート電極25およびソース領域19によってソースフォロワ回路が構成される。この状態でゲート電位Vgに3V程度の電位を印加してMOSトランジスタ12を飽和領域で動作させることにより、ホールポケット領域18に蓄積された信号電荷量に応じてソース電位が変調されて信号電荷が検出される。

ここで、単位画素部10が行方向および列方向に2次元状に複数配列されたMOS型イメージセンサでは、ソース配線26が行方向に接続されている。このため、行毎に順次画素信号を出力させる場合、ある行(選択行)の電荷蓄積期間中に他の行(非選択行)の初期化動作(非選択初期化)および読み出し動作(非選択読み出し)が行われる。これにより、非選択行の初期化動作時には、ソース配線26に6V程度の正の高電圧(例えば6V程度)が印加される。

しかしながら、図5に示すように選択行のゲート電極25のゲート電位を接地電位(0V)付近に保つことにより、チャネルドープ層(チャネル領域21)の電位が接地電位付近に固定され、ホールポケット領域18のポテンシャルは低い状態に保たれる。これにより、選択行のホールポケット領域18に蓄積された信号電荷(ホール)は基板13側に排出されることなく保存される。この期間が非選択初期化期間であり、撮像動作期間においてp型基板13の表面付近の電位差および電界強度が最大となる。

また、非選択行の信号読み出し動作時にも、選択行のゲート電極25の電圧を接地電位付近に保つことにより、ソース配線26に選択行の信号が出力されることを防いでいる。この期間が非選択信号読み出し期間である。

次に、本実施形態の固体撮像素子(MOS型イメージセンサ)100の製造方法について、図6(a)〜図6(d)を用いて詳細に説明する。

図6(a)〜図6(d)は、本実施形態の固体撮像素子100の製造工程について説明するための各製造工程における単位画素部の断面図である。ここでは、単位画素部10の右側に受光ダイオード11の形成領域、左側に光信号検出用MOSトランジスタ12の形成領域が示されている。

図6(a)では、ゲート電極25が形成された直後の状態を示している。ここでは、不純物濃度約1×1015cm−3のp型半導体基板または半導体基板上のp型エピタキシャル成長半導体層13(p型基板)上に、ピーク位置約0.55μmで、ピーク不純物濃度約3×1016cm−3のn型層16が形成されている。

受光ダイオード11の形成領域にはp型基板13およびn型層16間にそれらに接するように、ピーク位置約1.5μm、ピーク不純物濃度約1×1017cm−3のn型埋め込み層14が形成されている。その上方のn型層16内に、n型埋め込み層14とほぼ同じ寸法を有し、ピーク位置約0.3μm、ピーク不純物濃度約6×1016cm−3およびピーク位置約0.55μm、ピーク不純物濃度約2×1016cm−3のp型ウェル領域17aが形成されている。これらのn型埋め込み層14とp型ウェル領域17aは、ともに第1のマスク層を通してイオン注入により形成される。

また、MOSトランジスタ12の形成領域にはp型基板13およびn型層16間にそれらに接するように、ピーク位置約1.2μm、ピーク不純物濃度約5×1016cm−3のp型埋め込み層15が形成されている。その上方のn型層16内に、p型埋め込み層15とほぼ同じ寸法を有し、ピーク位置約0.3μm、ピーク不純物濃度約6×1016cm−3のp型ウェル領域17bが形成されている。これらのp型埋め込み層15とp型ウェル領域17bは、ともに第2のマスクを通してイオン注入により形成されている。

p型ウェル領域17bの表層部には、ピーク不純物濃度約2×1017cm−3のn型チャネルドープ層(チャネル領域21)が形成されている。また、チャネルドープ層21下に接してp型ウェル領域17bにピーク位置約0.2μm、ピーク不純物濃度約1×1017cm−3のp型高濃度埋め込み層(ホールポケット領域18)が形成されている。p型高濃度埋め込み層(ホールポケット領域18)は第3のマスクを通してイオン注入により形成される。

このように、ゲート電極25が形成された状態で、図6(b)に示すように、ゲート電極25をマスクとして、ゲート絶縁膜24を通してn型不純物をイオン注入する。これにより、ゲート電極25の両側にピーク不純物濃度約3×1018cm−3の低濃度n型ソース領域19およびドレイン領域20を形成する。この固体撮像素子において、p型基板13上に図4に示すような駆動回路領域を構成するCMOS回路を形成する場合には、この工程と同時に、n−CMOS領域31のゲート電極42の両側に低濃度n型ソース領域およびドレイン領域35を形成する。

さらに、CVD(Chemical Vapor Deposition)法などにより厚み約140nmの絶縁膜を形成し、異方性エッチングを行って、図6(c)に示すように、ゲート電極25の側面にその絶縁膜からなるサイドウォール29を形成する。

さらに、図6(d)に示すように、受光ダイオード11の受光領域を覆うようにレジストマスク(パターンマスク)30を形成した後、ゲート電極25、サイドウォール29およびレジストマスク30をマスクとしてn型不純物をイオン注入する。これにより、ソース領域19の中央部およびドレイン領域20の周辺部にピーク不純物濃度約8×1019cm−3の高濃度n型ソースコンタクト層22および高濃度n型ドレインコンタクト層23が形成される。

この固体撮像素子において、p型基板13上に図4に示すような駆動回路領域を構成するCMOS回路を形成する場合には、レジストマスク30はCMOS回路も覆うように形成する。このレジストマスク30を除去した後、単位画素部10およびp−CMOS領域32を覆うようにレジストマスク(マスクパターン)を形成し、n型不純物イオンを注入することによって、n−CMOS領域31のゲート電極の両側であって、低濃度n型ソース領域およびドレイン領域35の外側にピーク不純物濃度約3×1020cm−3の高濃度n型ソースコンタクト層およびドレインコンタクト層37を形成することができる。

以降、図示は省略するが、レジストマスクを除去した後、層間絶縁膜を形成し、コンタクトホール26a〜28aを形成し、ゲート配線28、ソース配線26およびドレイン配線27を形成することにより、図1〜図3に示すMOS型イメージセンサ(および図4に示す周辺回路)が作製される。

ここで、周辺回路領域(駆動回路領域)を構成するCMOS回路では、ソース/ドレイン領域とソース/ドレイン電極(配線)とのコンタクト部において、金属−半導体界面におけるコンタクト抵抗を可能な限り低くし、かつ、オームの法則に従うオーミック接触を得ることが必要である。したがって、ソースコンタクト層およびドレインコンタクト層37の不純物濃度として、固溶度限界付近の約3.0×1020cm−3程度が必要とされる。

しかしながら、単位画素部10のソースコンタクト層22およびドレインコンタクト層23と、その周辺回路領域のn−CMOS領域におけるソース/ドレインコンタクト層37とを同時に形成する従来の固体撮像素子の製造方法では、周辺回路領域を構成するCMOS回路に合わせて単位画素部10のソースコンタクト層22およびドレインコンタクト層23の不純物濃度も約3.0×1020cm−3程度となる。ピーク不純物濃度を約3.0×1020cm−3程度とするためには、イオン注入法において約2.0×1015ions/cm−2程度以上のドーズ量が必要とされるが、この場合には、p型基板13の表面およびイオン注入領域への欠陥導入を回避することが不可能である。

これに対して、本実施形態では、単位画素部10のソースコンタクト層22およびドレインコンタクト層23と、周辺回路領域のn−CMOS領域におけるソース/ドレインコンタクト層37とを異なるイオン注入工程で形成するため、単位画素部10のソースコンタクト層22およびドレインコンタクト層23を形成する際に、イオン注入ドーズ量を約6.0×1014ions/cm−2程度とし、ピーク不純物濃度を約8.0×1019cm−3程度とすることが可能になる。これにより、p型基板13の表面およびイオン注入領域への欠陥導入を大幅に抑制することができる。

半導体−金属界面のピーク不純物濃度が約8.0×1019cm−3程度まで低下すると、周辺回路領域で必要とされるオーミックなコンタクト特性は得られなくなる。しかしながら、単位画素部10では、信号読み出し時以外にソース/ドレイン電極(ソース配線26およびドレイン配線27)に殆ど電流が流れることはない。また、信号読み出し時においても、読み出し電流値はソース配線26に接続された定電流源により制御され、大きく変動することはない。したがって、単位画素部10の動作において、ソースコンタクト層22とソース配線26との接続および、ドレインコンタクト層23とドレイン配線27との接続が非オーミック接触であることは問題とならない。

以上により、本実施形態によれば、周辺駆動回路の特性劣化を招くことなく、固体撮像素子100を構成する単位画素部10のソースコンタクト層22およびドレインコンタクト層23のピーク不純物濃度を4×1019cm−3以上9×1019cm−3以下に設定することが可能となる。この単位画素部10のソースコンタクト層22およびドレインコンタクト層23のピーク不純物濃度を4×1019cm−3以上9×1019cm−3以下に設定することにより、以下のような効果が得られる。

まず、ソースコンタクト層22の不純物濃度が9×1019cm−3以下であることにより、p型基板13の表面およびイオン注入領域への欠陥導入を大幅に抑制することができる。これにより、ソースコンタクト層22と低濃度ソース領域19との界面に結晶欠陥が達することにより存在する電子−ホール対の発生中心が、非選択初期化動作時に発生する高電界状態と結びつくことにより暗電流が発生する現象を、回避することが可能となる。

図7は、本実施形態の固体撮像素子(MOS型イメージセンサ)100におけるソースコンタクト部22近傍の積層構造、対応する基板表面付近のn型不純物濃度分布、および非選択初期化動作時の電界分布を示す図である。ここでは、横軸にソースコンタクト部22(ソース領域19とソース配線26とのコンタクト部)からの距離(μm)を示し、縦軸は非選択初期化動作時の電界強度(V/cm)と基板表面付近のn型不純物濃度(cm−3)を示している。

非選択初期化動作時には、図5に示すように、ソース配線26を通じてソース領域19および高濃度ソースコンタクト層22に正の高電圧が印加され、同時にチャネルドープ層21の電位が接地電位付近に保たれる。このような状態では、図7の非選択初期化動作時の電界強度分布に示すように、高濃度ソースコンタクト層22からチャネルドープ層21にかけて急激に電界が高くなる。

また、図7の基板表面付近のn型不純物濃度分布に示すように、MOSトランジスタ12のソース/ゲート領域では高濃度ソースコンタクト層22からチャネルドープ層21にかけて不純物濃度が低下しており、高濃度ソースコンタクト層22の表面不純物濃度は、従来と同様に約3.0×1020cm−3程度である。また、低濃度ドレイン領域20の表面不純物濃度は、4×1019cm−3以上(例えば約8.0×1019cm−3程度)である。また、チャネルドープ層21の表面不純物濃度は、従来と同様に約3.0×1017cm−3程度である。

このように、ソースコンタクト層22の不純物濃度が4×1019cm−3以上であることにより、固体撮像素子100の撮像動作サイクル中、ソース電極(ソース配線26)とチャネルドープ層21(チャネル領域)との電位差が最大となる非選択初期化動作時において、サイドウォールエッチング時のエッチングダメージによりソース領域表面に発生する界面準位およびソースコンタクトホール形成のためのドライエッチングにより発生するコンタクト部の周辺部の界面準位などが存在する領域において、図7に示すように電界強度が2×103V/cm以下に抑制され、暗電流の発生が回避される。

なお、上記実施形態では特に説明しなかったが、本実施形態の固体撮像素子100を、その製品として携帯型電話装置などの携帯型電子機器の撮像部に用いることができる。これについて図8を用いて説明する。

図8は、本実施形態の固体撮像素子100を用いた携帯型電子機器の構成例を示すブロック図である。

図8に示すように、この携帯型電子機器150は、上述した本実施形態の固体撮像素子100と、この固体撮像素子100から得られる撮像信号を信号処理する画像処理部151と、ユーザからの入力操作命令を受け取る操作部152と、ワークメモリとして機能するRAM153と、コンピュータプログラムメモリとして機能するコンピュータ読み出し可能な可読記録媒体としてのROM154と、画像を表示可能とする表示部155と、これらの画像処理部151、操作部152、RAM153、ROM154および表示部155をそれぞれ制御可能とする制御部156とを備えている。なお、制御部156は、各携帯型電子機器150間などで画像を通信可能とする通信部(図示せず)を備えていてもよい。

制御部156は、CPU(中央演算処理装置)を有しており、操作部152からの入力操作指令に基づいて、画像を表示部155にて画像表示させたり、通信部によって画像を別のデバイスに通信させたりする。ROM154およびRAM153には、制御プログラムおよびデータが格納されており、制御部156は、ROM154およびRAM153の制御プログラムおよびそのデータに基づいて、画像処理部151および表示部155などを制御することができる。

この携帯型電子機器150によれば、本実施形態の固体撮像素子100において、暗電流が少なく、初期化動作時の電圧に依存する白点欠陥が抑制され、安定した高い感度特性の撮像信号が得られるため、良好な表示品位の画像を表示部155に画像表示させたり、通信部によって別のデバイスに通信させたりすることができる。

このように、例えばビデオカメラ、デジタルカメラ、画像入力カメラ、スキャナ、ファクシミリ、カメラ付き携帯電話機などの画像入力デバイス装置や、このような画像入力デバイス装置を搭載したパーソナルコンピュータなどの各種デバイス(電子情報機器)としての携帯型電子機器150の撮像部に本実施形態の固体撮像素子100を広く利用することができる。

以上のように、本発明の好ましい実施形態を用いて本発明を例示してきたが、本発明は、この実施形態に限定して解釈されるべきものではない。本発明は、特許請求の範囲によってのみその範囲が解釈されるべきであることが理解される。当業者は、本発明の具体的な好ましい実施形態の記載から、本発明の記載および技術常識に基づいて等価な範囲を実施することができることが理解される。本明細書において引用した特許、特許出願および文献は、その内容自体が具体的に本明細書に記載されているのと同様にその内容が本明細書に対する参考として援用されるべきであることが理解される。