JP2005291725A - プローブユニット及びその製造方法 - Google Patents

プローブユニット及びその製造方法 Download PDFInfo

- Publication number

- JP2005291725A JP2005291725A JP2004102723A JP2004102723A JP2005291725A JP 2005291725 A JP2005291725 A JP 2005291725A JP 2004102723 A JP2004102723 A JP 2004102723A JP 2004102723 A JP2004102723 A JP 2004102723A JP 2005291725 A JP2005291725 A JP 2005291725A

- Authority

- JP

- Japan

- Prior art keywords

- sacrificial

- substrate

- probe unit

- layer

- manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000000523 sample Substances 0.000 title claims abstract description 130

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 57

- 238000000034 method Methods 0.000 claims abstract description 31

- 239000011810 insulating material Substances 0.000 claims abstract description 6

- 239000000758 substrate Substances 0.000 claims description 165

- 239000004020 conductor Substances 0.000 claims description 18

- 239000000463 material Substances 0.000 claims description 18

- 239000010410 layer Substances 0.000 description 97

- 238000010586 diagram Methods 0.000 description 10

- 238000005530 etching Methods 0.000 description 8

- 238000007747 plating Methods 0.000 description 8

- 238000012360 testing method Methods 0.000 description 8

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 238000004544 sputter deposition Methods 0.000 description 7

- 229920002120 photoresistant polymer Polymers 0.000 description 6

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 238000011161 development Methods 0.000 description 5

- WABPQHHGFIMREM-UHFFFAOYSA-N lead(0) Chemical compound [Pb] WABPQHHGFIMREM-UHFFFAOYSA-N 0.000 description 5

- 238000012545 processing Methods 0.000 description 4

- 229910001030 Iron–nickel alloy Inorganic materials 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 238000002844 melting Methods 0.000 description 3

- 230000008018 melting Effects 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 229920002430 Fibre-reinforced plastic Polymers 0.000 description 2

- SECXISVLQFMRJM-UHFFFAOYSA-N N-Methylpyrrolidone Chemical compound CN1CCCC1=O SECXISVLQFMRJM-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 238000007772 electroless plating Methods 0.000 description 2

- 239000011151 fibre-reinforced plastic Substances 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 238000007689 inspection Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 238000003825 pressing Methods 0.000 description 2

- 229910052703 rhodium Inorganic materials 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 238000010998 test method Methods 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 1

- 229910003266 NiCo Inorganic materials 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000003754 machining Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 229910052702 rhenium Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 238000005488 sandblasting Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 238000000992 sputter etching Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

Images

Landscapes

- Measuring Leads Or Probes (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

Abstract

【解決手段】 凹部を有する犠牲基板を形成する犠牲基板形成工程と、前記凹部の内壁に沿って前記凹部を横断する導線を前記犠牲基板上に形成する導線形成工程と、前記導線の前記凹部を横断する部分を覆う犠牲層を前記導線上に形成する犠牲層形成工程と、前記犠牲基板上に絶縁材料からなる支持基板を形成して前記支持基板と前記犠牲基板との間に前記犠牲層と前記導線とを埋没させる支持基板形成工程と、前記犠牲基板と前記犠牲層とを除去する除去工程と、を含む。

【選択図】 図1

Description

つまり、本発明に係るプローブユニットの製造方法によれば、支持基板から離れる方向に一部が突出する導線を有し、導線の支持基板から突出する部分と支持基板との間に空隙を有し、導線が支持基板に埋設されるプローブユニットを製造することができる。

本発明に係るプローブユニットの製造方法で製造されたプローブユニットは、導線の突出する部分で検体と導通させることができる。オーバードライブをかけたときに、導線の突出する部分が支持基板との間に形成される空隙に沈み込むことができるため、検体に凹凸があっても適切な接触圧で検体と確実に導通させることができる。また、導線が支持基板に埋設されるため、導線が支持基板から剥がれにくい。

(プローブユニットの第一実施例)

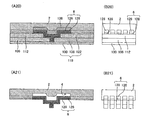

図1は、プローブユニットの第一実施例に係るプローブユニット1の構成を表す模式図である。

支持基板2は、板状であり、溝部4が形成されている。

導線としてのプローブ6は、溝部4の上方に架設されているブリッジ部8と、図示しない検査装置本体に接続され検査信号を送受信するリード部10とからなる。ブリッジ部8は、導通試験の際に検体の電極に接触する部分である。ブリッジ部8の両端はリード部10に接続され、中央に突部11が形成されている。リード部10は、支持基板2に埋設されている。プローブ6には、例えばNi、Fe、Co、Cu、Ag、Ru、Rh、Pd、Mo、Nb、Pt、Au、Os、Ir、W、Re、Ta、Hfなどのうち少なくとも一つの金属を含む材料を用い、単一の金属からなる材料を用いてもよいし、複数の金属を用いた合金または積層物を用いてもよい。

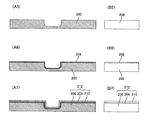

まず図2(A1)、(B1)に示すように、各プローブ6と検体12の各電極14が一対一で対応するように、プローブユニット1を検体12に対して配置する。

次に図2(A2)、(B2)に示すように、プローブユニット1を検体12に接近させて各プローブ6のブリッジ部8の突部11を各電極14に接触させ、さらにプローブユニット1を検体12に接近させる(すなわち、オーバードライブをかける)。オーバードライブをかけることにより、各プローブ6のブリッジ部8がそれぞれに撓む。これにより、各プローブ6のブリッジ部8の突部11と各電極14との接触圧が増大するため、各プローブ6と検体12の各電極14とを確実に導通させることができる。

導通試験の終了後に、検体12とプローブユニット1を離間させると、ブリッジ部8は弾力により試験前の状態に復元する。

また、リード部10が支持基板2に埋設されているため、プローブ6が支持基板2から剥がれにくい。

また、ブリッジ部8の突部11が支持基板2から突出しているため、突部11以外の部位が検体12に接触して検体12を破損するおそれがない。

また、溝部4は形成されていなくてもよい。具体的には例えば、図3に示すように、プローブユニット16のブリッジ部8が支持基板2から離れて突出し、支持基板2との間に空隙を有していればよい。

また、図4に示すようにプローブユニット17のリード部10の一部が支持基板2に埋設されていてもよい。

また、図5に示すようにプローブユニット18ブリッジ部8に突部11がなくてもよい。

図6は、本発明のプローブユニットの第二実施例に係るプローブユニット20である。尚、プローブユニットの第二実施例ではプローブユニットの第一実施例と実質的に同一な部分については同一の符号を付して説明を省略する。

(製造方法の第一実施例)

図7から12は、プローブユニット1の製造方法の第一実施例を説明する図である。図7から12の(A1)から(A21)は、図1(A)のa1−a1線断面図に対応し、図7から12の(B1)から(B21)は、図1(A)の側面図に対応する。

次に、所定形状のマスクを配置し、露光現像処理を行って不要な第一レジスト膜102を除去し、棒状の第一レジストパターン104を形成する(図7(A3)、(B3)参照)。尚、第一レジスト膜102等のフォトレジストの除去には、例えばN−メチル−2−ピロリドン等の液剤を用いる。

次に、第一基板100上にCuをめっきすることにより、第一層106を形成する(図7(A4)、(B4)参照)。

次に、第一レジストパターン104を除去して、溝状の第一凹部108を形成する(図7(A5)、(B5)参照)。

次に、所定形状のマスクを配置し、露光現像処理を行って不要な第二レジスト膜109を除去し、第一凹部108とその周縁の第一層106上を被覆する第二レジストパターン110を形成する(図8(A7)、(B7)参照)。

次に、第一層106上にCuをめっきすることにより、第二層112を形成する(図8(A8)、(B8)参照)。第二層112はスパッタ等で形成してもよい。

次に、第二レジストパターン110を除去して、第二凹部114を形成する(図8(A9)、(B9)参照)。第二凹部114の底面には、第一凹部108が形成されている。第一凹部108および第二凹部114が、特許請求の範囲に記載の凹部に相当する。以下第一凹部108と第二凹部114とを、単に凹部116という。第一実施例では、第一基板100上にめっきで第一層106を形成しているが、これに変えてスパッタ法で形成してもよい。このときは、めっきのように選択的に成長せず全面に形成されるため、第一レジストパターン104上にも第一層106が形成される。その後の第一レジストパターン104の除去の際、リフトオフにより不要な第一層106も除去される。なお、リフトオフに先立って、全面研磨等により、第一層106を除去すると、第一レジストパターンの除去時間を短縮できる。

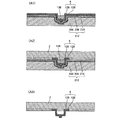

まず、第二層112上および凹部116の内壁に第一シード層120を形成する(図9(A10)、(B10)参照)。第一シード層120には、例えばNi(膜厚0.1μm)の単層、Ti(膜厚0.05μm)とNi(膜厚0.1μm)の複層、Cr(膜厚0.05μm)とNiFe合金(0.1μm)の複層などを用いる。第一シード層120の形成方法は、スパッタ、蒸着、CVD(Chemical Vapor Deposition)、無電解めっき等である。

次に、所定形状のマスクを配置し、露光現像処理を行って不要な第三レジスト膜122を除去することにより、第一開口部125を形成し、第一シード層120上に凹部116の内壁に沿って凹部116を横断する第三レジストパターン124を形成する(図9(A12)、(B12)参照)。

次に、第三レジストパターン124を除去する(図10(A14)、(B14)参照)。

次に、第一導線126により被覆されていない第一シード層120を除去し、第二導線128を形成する(図10(A15)、(B15)参照)。第一シード層120の除去には、イオンミリング等の方法を用いる。

まず、フォトレジストを塗布して、プローブ6を埋没させるように第二層112上に第四レジスト膜132を形成する(図11(A16)、(B16)参照)。

次に、所定形状のマスクを配置し、露光現像処理を行って不要な第四レジスト膜132を除去することにより、第二開口部134を形成する(図11(A17)、(B17)参照)。

次に、第二開口部134から露出するプローブ6および第二層112上にCuをめっきすることにより、プローブ6を埋没させるように犠牲層138を形成する(図11(A18)、(B18)参照)。犠牲層138は、スパッタ等の他の方法で形成してもよい。

次に、第四レジストパターン136を除去する(図11(A19)、(B19)参照)。

まず、第二層112上に犠牲層138およびプローブ6を埋没されるように絶縁材料を成型し、支持基板2を形成する(図12(A20)、(B20)参照)。絶縁材料は、ポリイミド、エポキシ等の有機材料でもよいし、ガラス等の無機材料でもよいし、FRP(Fiber Reinforced Plastics)等の有機材料と無機材料との混合材料でもよい。

次に、犠牲層138、第一基板100、第一層106、および第二層112をエッチング等により除去する(図12(A21)、(B21)参照)。

また、第一基板100、第一層106、および第二層112をCuで形成するため、除去工程において犠牲基板118をエッチングにより除去できる。

また、犠牲基板118と犠牲層138とを同一材料のCuで形成するため、除去工程において犠牲基板118および犠牲層138を同一工程で除去できる。

尚、第一層106および第二層112は、第一基板100と異なる材料で形成してもよい。

製造方法の第二実施例によるプローブユニット1の製造方法では、犠牲基板118と犠牲層138とを別工程で除去する。尚、製造方法の第二実施例では製造方法の第一実施例と実質的に同一な部分については同一の符号を付して説明を省略する。

まず、犠牲基板118を除去する(図13(A2)、(B2)参照)。

次に、犠牲層138を除去する(図13(A3)、(B3)参照)。

尚、除去工程において犠牲基板118を除去した後に、犠牲層138を除去することとして説明したが、犠牲層138を先に除去してもよい。

製造方法の第三実施例によるプローブユニット18の製造方法では、除去工程においてプローブユニット18と犠牲基板212とを分離して除去する。尚、製造方法の第三実施例では製造方法の第一実施例と実質的に同一な部分については同一の符号を付して説明を省略する。

まず、第二基板200の表面上にフォトレジストを塗布し、第五レジスト膜202を形成する(図14(A2)、(B2)参照)。

次に、所定形状のマスクを配置し、露光現像処理を行って不要な第五レジスト膜202を除去し、第二基板200の表面を露出させる第三開口部204を形成する(図14(A3)、(B3)参照)。

次に、第三開口部204から露出する第二基板200をエッチング等により所定の深さまで除去し、第三凹部206を形成する(図14(A4)、(B4)参照)。第三凹部206は、切削加工、溝入れ、サンドブラスト、放電加工(第二基板200が導電性である場合)等により形成してもよい。

次に、第五レジスト膜202を除去する(図15(A5)、(B5)参照)。

次に、めっきにより第二シード層208上に犠牲膜210を形成する(図15(A7)、(B7)参照)。犠牲膜210は、第二基板200に対して選択的に除去可能な材料である。尚、犠牲膜210は、スパッタ等により形成してもよい。そのときは、第二シード層208を形成せず、第二基板200上に犠牲膜210を形成すればよい。

製造方法の第一実施例と同様にして、犠牲基板212上にプローブ6、犠牲層138、および支持基板2を形成(図16(A8)、(B8)参照)した後に、第二シード層208が露出まで第二基板200の犠牲膜210が形成されていない側を研磨等により除去する(図16(A9)、(B9)参照)。

次に、エッチング等により犠牲膜210、第二シード層208および犠牲層138を除去する。犠牲膜210および第二シード層208を除去することにより、プローブ6および支持基板2からなるプローブユニット18と第二基板200とを分離できる(図16(A10)、(B10)参照)。

また、第二シード層208を第二基板200から露出させた後に、エッチング等により犠牲膜210および第二シード層208を除去するため、犠牲膜210および第二シード層208を短時間で除去できる。犠牲膜210が露出するまで、第二基板200を除去してもよいし、第二基板200を除去せずに犠牲膜210および第二シード層208を除去してもよい。

Claims (7)

- 凹部を有する犠牲基板を形成する犠牲基板形成工程と、

前記凹部の内壁に沿って前記凹部を横断する導線を前記犠牲基板上に形成する導線形成工程と、

前記導線の前記凹部を横断する部分を覆う犠牲層を前記導線上に形成する犠牲層形成工程と、

前記犠牲基板上に絶縁材料からなる支持基板を形成して前記支持基板と前記犠牲基板との間に前記犠牲層と前記導線とを埋没させる支持基板形成工程と、

前記犠牲基板と前記犠牲層とを除去する除去工程と、

を含むことを特徴とするプローブユニットの製造方法。 - 前記犠牲基板形成工程において、前記犠牲基板を溶融可能な材料で形成し、

前記除去工程において、前記犠牲基板を溶融して除去することを特徴とする請求項1に記載のプローブユニットの製造方法。 - 前記犠牲基板形成工程において、前記凹部を有する面に犠牲膜が形成されている前記犠牲基板を形成し、

前記導線形成工程において、前記犠牲膜上に前記導線を形成し、

前記除去工程において、前記犠牲膜を除去して前記犠牲基板と前記導線とを分離することにより、前記犠牲基板を除去することを特徴とする請求項1に記載のプローブユニットの製造方法。 - 前記犠牲基板形成工程と前記犠牲層形成工程とにおいて、前記犠牲基板と前記犠牲層とを、選択的に除去可能な互いに異なる材料で形成し、

前記除去工程において、前記犠牲基板と前記犠牲層とを別工程で除去することを特徴とする請求項1から3のいずれか一項に記載のプローブユニットの製造方法。 - 前記犠牲基板形成工程と前記犠牲層形成工程とにおいて、前記犠牲基板と前記犠牲層とを、前記除去工程において同一工程で除去可能な材料で形成し、

前記除去工程において、前記犠牲基板と前記犠牲層とを同一工程で除去することを特徴とする請求項1から3のいずれか一項に記載のプローブユニットの製造方法。 - 支持基板と、

両端が前記支持基板に接合され中間が前記支持基板から突出して前記支持基板との間に空隙を有し検体と接触するブリッジ部と、前記ブリッジ部に接続され少なくとも一部が前記支持基板に埋設されるリード部とを有する導線と、

を備えることを特徴とするプローブユニット。 - 前記リード部が曲折していることを特徴とする請求項6に記載のプローブユニット。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004102723A JP2005291725A (ja) | 2004-03-31 | 2004-03-31 | プローブユニット及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004102723A JP2005291725A (ja) | 2004-03-31 | 2004-03-31 | プローブユニット及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005291725A true JP2005291725A (ja) | 2005-10-20 |

Family

ID=35324838

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004102723A Pending JP2005291725A (ja) | 2004-03-31 | 2004-03-31 | プローブユニット及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005291725A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009513986A (ja) * | 2005-10-31 | 2009-04-02 | カプレス・アクティーゼルスカブ | 試験試料の電気的性質を試験するプローブ |

| JP2021092450A (ja) * | 2019-12-11 | 2021-06-17 | 石福金属興業株式会社 | Rh基合金からなるプローブピン用材料およびプローブピン |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08316270A (ja) * | 1995-05-23 | 1996-11-29 | Hitachi Ltd | テープキャリアおよびそれを用いた半導体装置 |

| JP2001284421A (ja) * | 2000-01-20 | 2001-10-12 | Advantest Corp | コンタクトストラクチャ |

| JP2002071720A (ja) * | 2000-09-01 | 2002-03-12 | Kobe Steel Ltd | 接続装置の製造方法 |

| JP2002350467A (ja) * | 2001-03-21 | 2002-12-04 | Mitsui Chemicals Inc | 電気検査用プローブの製造方法 |

-

2004

- 2004-03-31 JP JP2004102723A patent/JP2005291725A/ja active Pending

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08316270A (ja) * | 1995-05-23 | 1996-11-29 | Hitachi Ltd | テープキャリアおよびそれを用いた半導体装置 |

| JP2001284421A (ja) * | 2000-01-20 | 2001-10-12 | Advantest Corp | コンタクトストラクチャ |

| JP2002071720A (ja) * | 2000-09-01 | 2002-03-12 | Kobe Steel Ltd | 接続装置の製造方法 |

| JP2002350467A (ja) * | 2001-03-21 | 2002-12-04 | Mitsui Chemicals Inc | 電気検査用プローブの製造方法 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009513986A (ja) * | 2005-10-31 | 2009-04-02 | カプレス・アクティーゼルスカブ | 試験試料の電気的性質を試験するプローブ |

| US8310258B2 (en) | 2005-10-31 | 2012-11-13 | Capres A/S | Probe for testing electrical properties of a test sample |

| JP2021092450A (ja) * | 2019-12-11 | 2021-06-17 | 石福金属興業株式会社 | Rh基合金からなるプローブピン用材料およびプローブピン |

| JP7300677B2 (ja) | 2019-12-11 | 2023-06-30 | 石福金属興業株式会社 | Rh基合金からなるプローブピン用材料およびプローブピン |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TW201007169A (en) | MEMS probe fabrication on a reusable substrate for probe card application | |

| JP5681213B2 (ja) | プローブカード及びその製造方法 | |

| TWI439187B (zh) | 可撓性印刷配線板薄片及其製造方法 | |

| CN101562170A (zh) | 带电路的悬挂基板及其制造方法 | |

| JPH081978B2 (ja) | 基板に導電線を付加する方法、導電線キャリアおよびその製造方法 | |

| JP2005291725A (ja) | プローブユニット及びその製造方法 | |

| WO2013084874A1 (ja) | プローブカード用のバンプ付きメンブレンシート、プローブカード及びプローブカード用のバンプ付きメンブレンシートの製造方法 | |

| JP4849861B2 (ja) | プローブカード | |

| EP1903340A1 (en) | Probe substrate for test and manufacturing method thereof | |

| KR100955597B1 (ko) | 반도체나 평판표시소자 검사에 사용되는 프로브의 제조방법 | |

| JP2009042012A (ja) | プローブカード | |

| KR100977289B1 (ko) | 반도체나 평판표시소자 검사에 사용되는 프로브 | |

| JP2009097984A (ja) | プローブコンタクトの製造方法およびプローブコンタクト | |

| JP2005037199A (ja) | プローブユニット、導通試験方法及びその製造方法 | |

| JP5351453B2 (ja) | コンタクトプローブ複合体 | |

| KR100968445B1 (ko) | 접속소자의 제조방법 | |

| JP2016001197A (ja) | プローブカード用のバンプ付きメンブレンシート、プローブカード及びプローブカード用のバンプ付きメンブレンシートの製造方法 | |

| EP1898223A1 (en) | Probe substrate for test and manufacturing method thereof | |

| JP5203136B2 (ja) | コンタクトプローブの製造方法 | |

| KR20090009663A (ko) | 프로브 구조물과 형성 방법 | |

| JP4074287B2 (ja) | プローブユニットの製造方法 | |

| JP2011145200A (ja) | 電気的試験用プローブ及びその製造方法、並びに電気的接続装置及びその製造方法 | |

| JP2006071405A (ja) | プローブユニット | |

| JP6548963B2 (ja) | プローブの製造方法、プローブ、プローブ積層体、プローブ組立体およびプローブ組立体の製造方法 | |

| JP2004233128A (ja) | プローブユニット及びプローブユニットの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060628 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061003 |

|

| A711 | Notification of change in applicant |

Effective date: 20061213 Free format text: JAPANESE INTERMEDIATE CODE: A711 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070402 |

|

| A977 | Report on retrieval |

Effective date: 20090121 Free format text: JAPANESE INTERMEDIATE CODE: A971007 |

|

| A131 | Notification of reasons for refusal |

Effective date: 20090202 Free format text: JAPANESE INTERMEDIATE CODE: A131 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090402 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091203 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100326 |