JP2005184029A - 不揮発性記憶素子及び半導体集積回路装置 - Google Patents

不揮発性記憶素子及び半導体集積回路装置 Download PDFInfo

- Publication number

- JP2005184029A JP2005184029A JP2005041612A JP2005041612A JP2005184029A JP 2005184029 A JP2005184029 A JP 2005184029A JP 2005041612 A JP2005041612 A JP 2005041612A JP 2005041612 A JP2005041612 A JP 2005041612A JP 2005184029 A JP2005184029 A JP 2005184029A

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- region

- semiconductor

- silicon nitride

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 116

- 238000003860 storage Methods 0.000 title abstract description 23

- 229910044991 metal oxide Inorganic materials 0.000 claims abstract description 7

- 150000004706 metal oxides Chemical class 0.000 claims abstract description 7

- 230000015654 memory Effects 0.000 claims description 237

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 106

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 106

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 51

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 51

- 239000000758 substrate Substances 0.000 claims description 22

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 21

- 230000014759 maintenance of location Effects 0.000 claims description 21

- 229910052710 silicon Inorganic materials 0.000 claims description 21

- 239000010703 silicon Substances 0.000 claims description 21

- 125000006850 spacer group Chemical group 0.000 claims description 7

- 238000002513 implantation Methods 0.000 abstract description 4

- 230000000717 retained effect Effects 0.000 abstract description 2

- 238000007599 discharging Methods 0.000 abstract 1

- 239000010408 film Substances 0.000 description 562

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 69

- 229920005591 polysilicon Polymers 0.000 description 69

- 238000003949 trap density measurement Methods 0.000 description 33

- 238000002347 injection Methods 0.000 description 25

- 239000007924 injection Substances 0.000 description 25

- 238000000034 method Methods 0.000 description 22

- 238000004519 manufacturing process Methods 0.000 description 15

- 150000004767 nitrides Chemical class 0.000 description 15

- 239000002784 hot electron Substances 0.000 description 13

- 230000001133 acceleration Effects 0.000 description 12

- -1 phosphorus ions Chemical class 0.000 description 12

- 238000005229 chemical vapour deposition Methods 0.000 description 11

- 230000006866 deterioration Effects 0.000 description 10

- 229910052698 phosphorus Inorganic materials 0.000 description 10

- 239000011574 phosphorus Substances 0.000 description 10

- 230000006870 function Effects 0.000 description 9

- 230000000694 effects Effects 0.000 description 8

- 230000002093 peripheral effect Effects 0.000 description 8

- 230000005641 tunneling Effects 0.000 description 8

- 229910052796 boron Inorganic materials 0.000 description 6

- 239000012535 impurity Substances 0.000 description 6

- 230000005527 interface trap Effects 0.000 description 6

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- 238000009825 accumulation Methods 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 229910052785 arsenic Inorganic materials 0.000 description 4

- 230000005524 hole trap Effects 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 230000004044 response Effects 0.000 description 4

- PBCFLUZVCVVTBY-UHFFFAOYSA-N tantalum pentoxide Inorganic materials O=[Ta](=O)O[Ta](=O)=O PBCFLUZVCVVTBY-UHFFFAOYSA-N 0.000 description 4

- 238000000151 deposition Methods 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 230000001360 synchronised effect Effects 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000010893 electron trap Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 239000003574 free electron Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 239000002243 precursor Substances 0.000 description 2

- 238000001289 rapid thermal chemical vapour deposition Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910010413 TiO 2 Inorganic materials 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 125000001475 halogen functional group Chemical group 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- 238000006386 neutralization reaction Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Landscapes

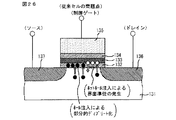

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005041612A JP2005184029A (ja) | 2005-02-18 | 2005-02-18 | 不揮発性記憶素子及び半導体集積回路装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005041612A JP2005184029A (ja) | 2005-02-18 | 2005-02-18 | 不揮発性記憶素子及び半導体集積回路装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001257698A Division JP2003068893A (ja) | 2001-08-28 | 2001-08-28 | 不揮発性記憶素子及び半導体集積回路 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008008964A Division JP2008172251A (ja) | 2008-01-18 | 2008-01-18 | 不揮発性記憶素子及び半導体集積回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005184029A true JP2005184029A (ja) | 2005-07-07 |

| JP2005184029A5 JP2005184029A5 (enExample) | 2008-03-06 |

Family

ID=34792800

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005041612A Pending JP2005184029A (ja) | 2005-02-18 | 2005-02-18 | 不揮発性記憶素子及び半導体集積回路装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005184029A (enExample) |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007067412A (ja) * | 2005-08-31 | 2007-03-15 | Samsung Electronics Co Ltd | 電荷トラップ絶縁体の製造方法及びsonos型の不揮発性半導体装置の製造方法 |

| JP2008084977A (ja) * | 2006-09-26 | 2008-04-10 | Denso Corp | 不揮発性半導体記憶装置のデータ書き換え方法 |

| KR100933905B1 (ko) * | 2006-11-20 | 2009-12-28 | 매크로닉스 인터내셔널 컴퍼니 리미티드 | 터널링 배리어 상부에 전계 분산층을 구비하는 전하 트래핑소자 |

| US8068370B2 (en) | 2008-04-18 | 2011-11-29 | Macronix International Co., Ltd. | Floating gate memory device with interpoly charge trapping structure |

| US8320191B2 (en) | 2007-08-30 | 2012-11-27 | Infineon Technologies Ag | Memory cell arrangement, method for controlling a memory cell, memory array and electronic device |

| US8987098B2 (en) | 2012-06-19 | 2015-03-24 | Macronix International Co., Ltd. | Damascene word line |

| US9099538B2 (en) | 2013-09-17 | 2015-08-04 | Macronix International Co., Ltd. | Conductor with a plurality of vertical extensions for a 3D device |

| US9379126B2 (en) | 2013-03-14 | 2016-06-28 | Macronix International Co., Ltd. | Damascene conductor for a 3D device |

| US9559113B2 (en) | 2014-05-01 | 2017-01-31 | Macronix International Co., Ltd. | SSL/GSL gate oxide in 3D vertical channel NAND |

-

2005

- 2005-02-18 JP JP2005041612A patent/JP2005184029A/ja active Pending

Cited By (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007067412A (ja) * | 2005-08-31 | 2007-03-15 | Samsung Electronics Co Ltd | 電荷トラップ絶縁体の製造方法及びsonos型の不揮発性半導体装置の製造方法 |

| JP2008084977A (ja) * | 2006-09-26 | 2008-04-10 | Denso Corp | 不揮発性半導体記憶装置のデータ書き換え方法 |

| KR100933905B1 (ko) * | 2006-11-20 | 2009-12-28 | 매크로닉스 인터내셔널 컴퍼니 리미티드 | 터널링 배리어 상부에 전계 분산층을 구비하는 전하 트래핑소자 |

| KR100942928B1 (ko) * | 2006-11-20 | 2010-02-22 | 매크로닉스 인터내셔널 컴퍼니 리미티드 | 터널링 배리어 상부에 전계 분산층을 구비하는 전하 트래핑소자 |

| US8889509B2 (en) | 2006-11-20 | 2014-11-18 | Macronix International Co., Ltd. | Charge trapping devices with field distribution layer over tunneling barrier |

| US8101989B2 (en) | 2006-11-20 | 2012-01-24 | Macronix International Co., Ltd. | Charge trapping devices with field distribution layer over tunneling barrier |

| US8320191B2 (en) | 2007-08-30 | 2012-11-27 | Infineon Technologies Ag | Memory cell arrangement, method for controlling a memory cell, memory array and electronic device |

| US9030877B2 (en) | 2007-08-30 | 2015-05-12 | Infineon Technologies Ag | Memory cell arrangement, method for controlling a memory cell, memory array and electronic device |

| US8068370B2 (en) | 2008-04-18 | 2011-11-29 | Macronix International Co., Ltd. | Floating gate memory device with interpoly charge trapping structure |

| US8987098B2 (en) | 2012-06-19 | 2015-03-24 | Macronix International Co., Ltd. | Damascene word line |

| US9379126B2 (en) | 2013-03-14 | 2016-06-28 | Macronix International Co., Ltd. | Damascene conductor for a 3D device |

| US9099538B2 (en) | 2013-09-17 | 2015-08-04 | Macronix International Co., Ltd. | Conductor with a plurality of vertical extensions for a 3D device |

| US9559113B2 (en) | 2014-05-01 | 2017-01-31 | Macronix International Co., Ltd. | SSL/GSL gate oxide in 3D vertical channel NAND |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101420352B1 (ko) | 메모리 소자 및 그 동작방법 | |

| US9847343B2 (en) | Charge trapping nonvolatile memory devices, methods of fabricating the same, and methods of operating the same | |

| CN101079426B (zh) | 使用besonos元件的次栅and架构的结构及方法 | |

| US7864582B2 (en) | Nonvolatile memory devices and methods of operating same to inhibit parasitic charge accumulation therein | |

| US7773429B2 (en) | Non-volatile memory device and driving method thereof | |

| EP2416367A2 (en) | Multi-state memory cell with asymetric charge trapping | |

| US20080048239A1 (en) | Semiconductor memory device having DRAM cell mode and non-volatile memory cell mode and operation method thereof | |

| JP5259918B2 (ja) | 反転ビット線、電荷をトラップする不揮発性メモリ、およびその動作方法 | |

| US7471563B2 (en) | Semiconductor memory device | |

| TW201931579A (zh) | 用於在非揮發性記憶體中之字元程式化及抑制干擾減少的偏壓方式 | |

| US7177192B2 (en) | Method of operating a flash memory device | |

| US9825186B2 (en) | Read performance of a non-volatile memory device, in particular a non-volatile memory device with buried selection transistor | |

| CN108028061A (zh) | 非易失性存储器的非对称传输场效应晶体管 | |

| JP2005005513A (ja) | 不揮発性半導体メモリ装置およびその読み出し方法 | |

| TW584943B (en) | Nonvolatile storage device and semiconductor integrated circuit | |

| CN101438351B (zh) | 用于擦除内存器件的方法以及多级程序化内存器件 | |

| TW201933363A (zh) | 利用位元線路和選擇閘極電壓調節進行程式干擾的抑制 | |

| CN108110009B (zh) | 电介质界面中具有电荷俘获的紧凑型非易失性存储器器件 | |

| TW201301485A (zh) | 具有雙功能的非揮發性半導體記憶單元 | |

| JP2005184029A (ja) | 不揮発性記憶素子及び半導体集積回路装置 | |

| JP4670187B2 (ja) | 不揮発性半導体メモリ装置 | |

| CN1287463C (zh) | 包含个别可寻址存储单元之存储单元阵列及其制造方法 | |

| JP4522879B2 (ja) | 不揮発性半導体記憶装置 | |

| US6839278B1 (en) | Highly-integrated flash memory and mask ROM array architecture | |

| JP2004214506A (ja) | 不揮発性半導体メモリ装置の動作方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080118 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080118 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090120 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090526 |