JP2005039067A - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP2005039067A JP2005039067A JP2003274728A JP2003274728A JP2005039067A JP 2005039067 A JP2005039067 A JP 2005039067A JP 2003274728 A JP2003274728 A JP 2003274728A JP 2003274728 A JP2003274728 A JP 2003274728A JP 2005039067 A JP2005039067 A JP 2005039067A

- Authority

- JP

- Japan

- Prior art keywords

- impurity diffusion

- floating gate

- region

- semiconductor substrate

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 114

- 238000009792 diffusion process Methods 0.000 claims abstract description 138

- 239000012535 impurity Substances 0.000 claims abstract description 136

- 239000000758 substrate Substances 0.000 claims abstract description 79

- 238000002955 isolation Methods 0.000 claims description 17

- 230000015572 biosynthetic process Effects 0.000 claims description 5

- 238000009413 insulation Methods 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 34

- 239000000969 carrier Substances 0.000 description 12

- 230000005641 tunneling Effects 0.000 description 12

- 239000002356 single layer Substances 0.000 description 7

- 230000000694 effects Effects 0.000 description 6

- 239000002784 hot electron Substances 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

- 230000014616 translation Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- E—FIXED CONSTRUCTIONS

- E04—BUILDING

- E04G—SCAFFOLDING; FORMS; SHUTTERING; BUILDING IMPLEMENTS OR AIDS, OR THEIR USE; HANDLING BUILDING MATERIALS ON THE SITE; REPAIRING, BREAKING-UP OR OTHER WORK ON EXISTING BUILDINGS

- E04G17/00—Connecting or other auxiliary members for forms, falsework structures, or shutterings

- E04G17/14—Bracing or strutting arrangements for formwalls; Devices for aligning forms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/788—Field effect transistors with field effect produced by an insulated gate with floating gate

- H01L29/7881—Programmable transistors with only two possible levels of programmation

- H01L29/7883—Programmable transistors with only two possible levels of programmation charging by tunnelling of carriers, e.g. Fowler-Nordheim tunnelling

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/60—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the control gate being a doped region, e.g. single-poly memory cell

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B69/00—Erasable-and-programmable ROM [EPROM] devices not provided for in groups H10B41/00 - H10B63/00, e.g. ultraviolet erasable-and-programmable ROM [UVEPROM] devices

Abstract

【課題】 電気的にデータを消去可能で、かつ低電圧でのデータの書き込みが容易な不揮発性半導体装置を提供する。

【解決手段】 本発明の不揮発性半導体記憶装置は、主表面を有する半導体基板1と、半導体基板1の主表面に形成されたソース/ドレインとなる1対のp型不純物拡散領域3、3と、1対のp型不純物拡散領域3、3に挟まれる半導体基板1の領域の上にトンネル絶縁層4aを介して形成されたフローティングゲート5と、半導体基板1の主表面に形成された、フローティングゲート5の電位を制御するための制御用不純物拡散領域6とを備えている。

【選択図】 図2

【解決手段】 本発明の不揮発性半導体記憶装置は、主表面を有する半導体基板1と、半導体基板1の主表面に形成されたソース/ドレインとなる1対のp型不純物拡散領域3、3と、1対のp型不純物拡散領域3、3に挟まれる半導体基板1の領域の上にトンネル絶縁層4aを介して形成されたフローティングゲート5と、半導体基板1の主表面に形成された、フローティングゲート5の電位を制御するための制御用不純物拡散領域6とを備えている。

【選択図】 図2

Description

本発明は、不揮発性半導体記憶装置に関し、特に、単層ゲート構造のメモリセルを有する不揮発性半導体記憶装置に関するものである。

従来のフラッシュメモリのメモリセルは、チャネル領域上にトンネル酸化膜を介してフローティングゲートが形成され、さらに絶縁膜を介してフローティングゲート上にコントロールゲートが形成された積層ゲート構造を有している。しかし、このような積層ゲート構造では構成および製造工程が複雑となる。

これに対して、構成および製造工程を簡易にするために、チャネル領域上のゲートをフローティングゲートのみとした単層ゲート構造のメモリセルが提案されている。

従来の単層ゲート構造のメモリセルでは、基板とフローティングゲートとが容量結合をしているため、基板に電圧を与えるとフローティングゲートの電位も自動的に基板の電位と近い値となってしまう。このため、基板とフローティングゲートとの間に大きな電位差を与えることが困難であった。

このため、電気的に消去を行うことがほぼ不可能であり、紫外線照射による消去のみが可能であるため、従来の単層ゲート構造のメモリセルはOTPROM(One Time Programmable Read-Only Memory)などのほとんど書き換えを行なわない用途にしか使用できなかった。

また、単層ゲート構造のメモリセルにおいて、電気的に消去可能な構成が、たとえば特表平8−506693号公報、特開平3−57280号公報などに開示されている。

この構成によれば、半導体基板の表面に形成された不純物拡散領域をフローティングゲートに対向させることにより、この不純物拡散領域によるフローティングゲートの電位の制御が可能とされている。

特表平8−506693号公報

特開平3−57280号公報

しかしながら、上記2つの公報に開示されたメモリトランジスタはnチャネルMOS(Metal Oxide Semiconductor)トランジスタであり、低電圧でのデータの書き込みが困難であるという問題点があった。以下、そのことについて説明する。

メモリトランジスタがnチャネルMOSトランジスタの場合、書き込み動作においてはドレインに高い正の電圧を印加することにより、ソースから引き出された電子が半導体基板表面のチャネル内をドレインに向って高速で走り、ドレイン近傍でホットエレクトロンと呼ばれる高エネルギー状態となる。このホットエレクトロンが、フローティングゲートに注入されて、データの書き込まれた状態となる。

この場合、ドレインに高い正の電圧が印加されているため、ホットエレクトロンは、半導体基板とフローティングゲートとの間に大きな電位差を与えないと、ドレイン側へ注入されるだけでフローティングゲートに注入され難くなる。このため、メモリトランジスタがnチャネルMOSトランジスタの場合には、書き込み動作時において高電圧を印加しなければならず、低電圧でのデータの書き込みが困難であるという問題点があった。

特に、単層ゲート構造の場合には、フローティングゲート上にコントロールゲートがないため、フローティングゲートと半導体基板との間の容量結合による電位差でホットエレクトロンをフローティングゲートに注入しなければならない。このように高電圧を与えないとデータの書き込みが困難であるが、単層ゲート構造においては高電位を与えることも難しいため、データの書き込み動作が困難になるという問題があった。

それゆえ本発明の目的は、電気的にデータを消去可能で、かつ低電圧でのデータの書き込みが容易な不揮発性半導体装置を提供することを目的とする。

本発明の不揮発性半導体記憶装置は、半導体基板と、ソース/ドレインとなる1対のp型不純物拡散領域と、フローティングゲートと、制御用不純物拡散領域とを備えている。半導体基板は、主表面を有している。ソース/ドレインとなる1対のp型不純物拡散領域は、半導体基板の主表面に形成されている。フローティングゲートは、1対のp型不純物拡散領域に挟まれる半導体基板の領域の上にトンネル絶縁層を介して形成されている。制御用不純物拡散領域は、半導体基板の主表面に形成されており、フローティングゲートの電位を制御するためのものである。

本発明の不揮発性半導体装置によれば、フローティングゲートの電位を制御するための制御用不純物拡散領域が半導体基板の主表面に形成されているため、基板とフローティングゲートとの間に大きな電位差を与えることが容易となる。これにより、フローティングゲートの電子を引き抜くことが容易となり、電気的な消去が可能となる。

また、ソース/ドレインがp型の不純物拡散領域であるため、メモリトランジスタはpチャネルのトランジスタである。このpチャネルのトランジスタの場合、書き込み動作時においてはドレインに負側の電圧を印加することにより、ソースから供給された正孔が半導体基板表面のチャネル内をドレインに向って高速で走り、ドレイン近傍で原子と衝突して電子−正孔対を生じさせる。そして、その電子−正孔対の電子が、フローティングゲートに注入されて、データの書き込まれた状態となる。

この場合、ドレインに印加される電圧は負側の電圧であるため、電子はドレイン側に注入され難く、ゲート側に注入され易くなる。このため、半導体基板とフローティングゲートとの間にそれほど大きな電位差を与えなくとも、電子をフローティングゲートに注入することができ、低電圧でのデータの書き込みが可能となる。

以下、本発明の実施の形態について図に基づいて説明する。

(実施の形態1)

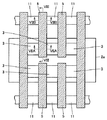

図1は、本発明の実施の形態1における半導体記憶装置の構成を概略的に示す平面図である。図2(a)および図2(b)は、図1のIIA−IIA線に沿う概略断面図および図1のIIB−IIB線に沿う概略断面図である。図3は、図1のIII−III線に沿う概略断面図である。

図1は、本発明の実施の形態1における半導体記憶装置の構成を概略的に示す平面図である。図2(a)および図2(b)は、図1のIIA−IIA線に沿う概略断面図および図1のIIB−IIB線に沿う概略断面図である。図3は、図1のIII−III線に沿う概略断面図である。

なお、本来、メモリセルはビット毎に選択用のトランジスタを有しているが、選択用のトランジスタは本実施の形態の動作原理と無関係であるため、図1以外では図示せず、その説明も省略する。また、選択用のトランジスタの取扱いについては他の実施の形態についても同様である。

図1〜図3を参照して、本実施の形態のメモリセルは、フローティングゲートトランジスタ10と、フローティングゲート5をコントロールする部分とを主に有している。

図2(a)を参照して、フローティングゲートトランジスタ形成領域においては、p型の半導体基板1の主表面にn型ウェル領域2aが形成されており、n型ウェル領域2aにpチャネルMOSトランジスタであるフローティングゲートトランジスタ10が形成されている。フローティングゲートトランジスタ10は、ソース/ドレインとなる1対のp型不純物拡散領域3、3と、トンネル絶縁層4aと、フローティングゲート5とを有している。ソース/ドレインとなる1対のp型不純物拡散領域3、3は、n型ウェル領域2a内の半導体基板1の主表面に形成されている。フローティングゲート5は、1対のp型不純物拡散領域3、3に挟まれる半導体基板1の領域の上にトンネル絶縁層4aを介して形成されている。

図2(b)を参照して、フローティングゲート5は、フローティングゲートトランジスタ形成領域からフローティングゲートコントロール領域まで延在している。このフローティングゲートコントロール領域においては、フローティングゲート5の電位を制御するための制御用不純物拡散領域6が形成されている。この制御用不純物拡散領域6は、半導体基板1の主表面に形成されたp型の不純物拡散領域より構成されており、フローティングゲート5と絶縁層4bを介して対向している。この制御用不純物拡散領域6は、半導体基板1の主表面に形成されたn型ウェル領域2b内に形成されている。

図3を参照して、フローティングゲートトランジスタ形成領域とフローティングゲートコントロール領域との間の半導体基板1の主表面には、フィールド絶縁層7が形成されている。このフィールド絶縁層7の直下は、半導体基板1のp型領域が位置している。

次に、本実施の形態におけるメモリセルの書き込みおよび消去の動作について説明する。

なお、本実施の形態におけるメモリセルの「書き込み」状態とはフローティングゲート5に電子が蓄積された状態のことを言い、「消去」状態とはフローティングゲート5から電子が引抜かれた状態のことを言う。

図2(a)および図2(b)を参照して、メモリセルへの書き込みは、フローティングゲートトランジスタ10でのインパクトイオン化により発生するホットキャリアをフローティングゲート5に注入することにより行なわれる。ホットキャリアの発生は、表1に示した電圧を各領域に与えることにより起こる。

この際、制御用不純物拡散領域6は、フローティングゲート5の電位をコントロールする役割を担っている。具体的には、ホットキャリアの発生はフローティングゲート5の(一方のp型不純物拡散領域3から見た)電位が−1V程度の時に最も多くなるため、そのような電位になるように制御用不純物拡散領域6に電圧が与えられてフローティングゲート5の電位がコントロールされる。

また、メモリセルの消去は、フローティングゲート5に蓄積された電子を一方のp型不純物拡散領域3、他方のp型不純物拡散領域3およびn型ウェル領域2aのそれぞれに高電位を与えてFN(Fowler-Nordheim)トンネリングによって引き抜くことで行なわれる。FNトンネリングを起こすために、一方のp型不純物拡散領域3、他方のp型不純物拡散領域3およびn型ウェル領域2aのそれぞれに表2に示すような正の電位が与えられる。

この際、制御用不純物拡散領域6にも表2に示すような負の電圧を与えて、フローティングゲート5の(一方のp型不純物拡散領域3から見た)電位が下げられている。効率よく消去を行うためには、フローティングゲート5と一方のp型不純物拡散領域3、他方のp型不純物拡散領域3およびn型ウェル領域2aのそれぞれとの間の接合容量比をできるだけ小さくして電位差を大きくすることが望ましい。

本実施の形態のよれば、制御用不純物拡散領域6によりフローティングゲート5の電位をコントロールすることができるため、半導体基板1とフローティングゲート5との間に大きな電位差を与えることが可能となる。これにより、フローティングゲート5内の電子をFNトンネリングで引き抜くことが可能となるため、データの電気的な消去が可能となる。

また、フローティングゲートトランジスタ10がpチャネルMOSトランジスタよりなっている。このため、書き込み動作時においてはドレインに負側の電圧を印加することにより、ソースから供給された正孔が半導体基板1表面のチャネル内をドレインに向って高速で走り、ドレイン近傍で原子と衝突して電子−正孔対を生じさせる。そして、その電子−正孔対の電子が、フローティングゲート5に注入されて、データの書き込まれた状態となる。

この場合、ドレインに印加される電圧は負側の電圧であるため、電子はドレイン側に注入され難く、フローティングゲート5側に注入され易くなる。このため、半導体基板1とフローティングゲート5との間にそれほど大きな電位差を与えなくとも、電子をフローティングゲート5に注入することができ、低電圧でのデータの書き込みが可能となる。

(実施の形態2)

図4は、本発明の実施の形態2における半導体記憶装置の構成を概略的に示す平面図である。図5は、図4のV−V線に沿う概略断面図である。

図4は、本発明の実施の形態2における半導体記憶装置の構成を概略的に示す平面図である。図5は、図4のV−V線に沿う概略断面図である。

図4および図5を参照して、本実施の形態のメモリセルの構成は、実施の形態1の構成と比較して、素子分離用のp型不純物拡散領域8を有している点において異なる。

この素子分離用のp型不純物拡散領域8は、フローティングゲートトランジスタ領域とフローティングゲートコントロール領域との間の半導体基板1の主表面に形成されたフィールド絶縁層7の直下の半導体基板1に形成されている。この素子分離用のp型不純物拡散領域8は、半導体基板1よりも高いキャリア濃度を有している。

なお、上記以外の構成については実施の形態1の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

本実施の形態によれば、以下の効果が得られる。

書き込みおよび消去時には表1および表2に示すような電圧がn型ウェル領域2a、2bに印加されるが、この際、p型半導体基板1とn型ウェル領域2a、2bのそれぞれとのpn接合部には空乏層が生じている。この空乏層の延びが大きくなるにつれて、パンチスルーに伴うリーク電流が増加する。

本実施の形態によれば、素子分離用のp型不純物拡散領域8は半導体基板1よりも高いキャリア濃度を有しているため、この空乏層の延びを抑えることができる。これにより、n型ウェル領域2aとn型ウェル領域2bとの間隔を小さくすることができ、結果として実施の形態1よりもメモリセルサイズを小さくすることができる。

(実施の形態3)

図6は、本発明の実施の形態3における半導体記憶装置の構成を概略的に示す平面図である。図7(a)および図7(b)は、図6のVIIA−VIIA線に沿う概略断面図および図6のVIIB−VIIB線に沿う概略断面図である。図8は、図6のVIII−VIII線に沿う概略断面図である。

図6は、本発明の実施の形態3における半導体記憶装置の構成を概略的に示す平面図である。図7(a)および図7(b)は、図6のVIIA−VIIA線に沿う概略断面図および図6のVIIB−VIIB線に沿う概略断面図である。図8は、図6のVIII−VIII線に沿う概略断面図である。

図6〜図8を参照して、本実施の形態のメモリセルの構成は、実施の形態1の構成と比較して、フローティングゲートコントロール領域内の制御用不純物拡散領域の構成において異なる。

本実施の形態における制御用不純物拡散領域は、1対のn型のソース/ドレイン用不純物拡散領域11、11により構成されている。1対のソース/ドレイン用不純物拡散領域11、11は、フローティングゲート5の下側に位置する半導体基板1の領域を挟むようにp型の半導体基板1の主表面に形成されている。この1対のソース/ドレイン用不純物拡散領域11、11と、絶縁層4bと、フローティングゲート5とにより、nチャネルMOSトランジスタよりなるコントロールトランジスタ20が構成されている。

なお、上記以外の構成については実施の形態1の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

次に、本実施の形態におけるメモリセルの書き込みおよび消去の動作について説明する。

図7(a)および図7(b)を参照して、メモリセルへの書き込みは、フローティングゲートトランジスタ10でのインパクトイオン化により発生するホットキャリアをフローティングゲート5に注入することにより行なわれる。ホットキャリアの発生は、表3に示した電圧を各領域に与えることにより起こる。

この際、コントロールトランジスタ20の1対のソース/ドレイン用不純物拡散領域11、11は、フローティングゲート5の電位をコントロールする役割を担っている。具体的には、ホットキャリアの発生はフローティングゲート5の(一方のp型不純物拡散領域3から見た)電位が−1V程度の時に最も多くなるため、そのような電位になるように1対のソース/ドレイン用不純物拡散領域11、11に電圧が与えられてフローティングゲート5の電位がコントロールされる。

また、メモリセルの消去は、フローティングゲート5に蓄積された電子を一方のp型不純物拡散領域3(もしくは他方のp型不純物拡散領域3)に高電位を与えてFN(Fowler-Nordheim)トンネリングによって引き抜くことで行なわれる。FNトンネリングを起こすために、一方のp型不純物拡散領域3(もしくは他方のp型不純物拡散領域3)には表4に示すような正の電位が与えられる。

この際、1対のp型不純物拡散領域3、3にも表4に示すような負の電圧を与えて、フローティングゲート5の(一方のp型不純物拡散領域3から見た)電位が下げられている。効率よく消去を行うためには、フローティングゲート5と一方のソース/ドレイン用不純物拡散領域11(もしくは他方のソース/ドレイン用不純物拡散領域11)との間の接合容量比をできるだけ小さくして電位差を大きくすることが望ましい。

本実施の形態のよれば、1対のソース/ドレイン用不純物拡散領域11、11によりフローティングゲート5の電位をコントロールすることができるため、半導体基板1とフローティングゲート5との間に大きな電位差を与えることが可能となる。これにより、フローティングゲート5内の電子をFNトンネリングで引き抜くことが可能となるため、データの電気的な消去が可能となる。

また、フローティングゲートトランジスタ10がpチャネルMOSトランジスタよりなっているため、実施の形態1と同様、nチャネルMOSトランジスタを用いる場合よりも低電圧で書き込みを行うことが可能となる。

(実施の形態4)

図9は、本発明の実施の形態4における半導体記憶装置の構成を概略的に示す平面図である。図10(a)および図10(b)は、図9のXA−XA線に沿う概略断面図および図9のXB−XB線に沿う概略断面図である。図11は、図9のXI−XI線に沿う概略断面図である。

図9は、本発明の実施の形態4における半導体記憶装置の構成を概略的に示す平面図である。図10(a)および図10(b)は、図9のXA−XA線に沿う概略断面図および図9のXB−XB線に沿う概略断面図である。図11は、図9のXI−XI線に沿う概略断面図である。

図9〜図11を参照して、本実施の形態のメモリセルの構成は、実施の形態3の構成と比較して、フローティングゲートコントロール領域内にp型ウェル領域12が追加されている点において異なる。

p型ウェル領域12は半導体基板1の主表面に形成されている。p型ウェル領域12内に、1対のソース/ドレイン用不純物拡散領域11、11が形成されている。p型ウェル領域12は、半導体基板1よりも高いキャリア濃度を有している。

なお、上記以外の構成については実施の形態3の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

本実施の形態によれば、以下の効果が得られる。

書き込みおよび消去時には表3および表4に示すような電圧がn型ウェル領域2aと一方のソース/ドレイン用不純物拡散領域11(もしくは他方のソース/ドレイン用不純物拡散領域11)に印加されるが、この際、n型ウェル領域2aとp型半導体基板1とのpn接合部および一方のソース/ドレイン用不純物拡散領域11(もしくは他方のソース/ドレイン用不純物拡散領域11)とp型領域とのpn接合部には空乏層が生じている。この空乏層の延びが大きくなるにつれて、パンチスルーに伴うリーク電流が増加する。

本実施の形態によれば、p型ウェル領域12は半導体基板1よりも高いキャリア濃度を有しているため、この空乏層の延びを抑えることができる。これにより、n型ウェル領域2aと一方のソース/ドレイン用不純物拡散領域11(もしくは他方のソース/ドレイン用不純物拡散領域11)との間隔を小さくすることができ、結果として実施の形態3よりもメモリセルサイズを小さくすることができる。

(実施の形態5)

図12は、本発明の実施の形態5における半導体記憶装置の構成を概略的に示す平面図である。図13は、図12のXIII−XIII線に沿う概略断面図である。

図12は、本発明の実施の形態5における半導体記憶装置の構成を概略的に示す平面図である。図13は、図12のXIII−XIII線に沿う概略断面図である。

図12および図13を参照して、本実施の形態のメモリセルの構成は、実施の形態4の構成と比較して、素子分離用のp型不純物拡散領域8を有している点において異なる。

この素子分離用のp型不純物拡散領域8は、フローティングゲートトランジスタ領域とフローティングゲートコントロール領域との間の半導体基板1の主表面に形成されたフィールド絶縁層7の直下の半導体基板1に形成されている。この素子分離用のp型不純物拡散領域8は、半導体基板1よりも高いキャリア濃度を有している。

なお、上記以外の構成については実施の形態1の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

本実施の形態によれば、以下の効果が得られる。

書き込みおよび消去時には表3および表4に示すような電圧がn型ウェル領域2aと一方のソース/ドレイン用不純物拡散領域11(もしくは他方のソース/ドレイン用不純物拡散領域11)とに印加されるが、この際、n型ウェル領域2aとp型半導体基板1とのpn接合部および一方のソース/ドレイン用不純物拡散領域11(もしくは他方のソース/ドレイン用不純物拡散領域11)とp型領域とのpn接合部には空乏層が生じている。この空乏層の延びが大きくなるにつれて、パンチスルーに伴うリーク電流が増加する。

本実施の形態によれば、素子分離用のp型不純物拡散領域8は半導体基板1よりも高いキャリア濃度を有しているため、この空乏層の延びを抑えることができる。これにより、n型ウェル領域2aと一方のソース/ドレイン用不純物拡散領域11(もしくは他方のソース/ドレイン用不純物拡散領域11)との間隔を小さくすることができ、結果として実施の形態4よりもメモリセルサイズを小さくすることができる。

(実施の形態6)

図14は、本発明の実施の形態6における半導体記憶装置の構成を概略的に示す平面図である。図15(a)および図15(b)は、図14のXVA−XVA線に沿う概略断面図および図14のXVB−XVB線に沿う概略断面図である。

図14は、本発明の実施の形態6における半導体記憶装置の構成を概略的に示す平面図である。図15(a)および図15(b)は、図14のXVA−XVA線に沿う概略断面図および図14のXVB−XVB線に沿う概略断面図である。

図14および図15を参照して、本実施の形態のメモリセルの構成は、実施の形態1の構成と比較して、フローティングゲートコントロール領域内の制御用不純物拡散領域などの構成において異なる。

本実施の形態における制御用不純物拡散領域は、1対のp型のソース/ドレイン用不純物拡散領域22、22により構成されている。また、p型の半導体基板1の主表面にはn型ウェル領域21が形成されている。1対のソース/ドレイン用不純物拡散領域22、22は、フローティングゲート5の下側に位置する半導体基板1の領域を挟むようにn型ウェル領域21内でp型の半導体基板1の主表面に形成されている。この1対のソース/ドレイン用不純物拡散領域22、22と、絶縁層4bと、フローティングゲート5とにより、pチャネルMOSトランジスタよりなるコントロールトランジスタ30が構成されている。

なお、上記以外の構成については実施の形態1の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

次に、本実施の形態におけるメモリセルの書き込みおよび消去の動作について説明する。

図15(a)および図15(b)を参照して、メモリセルへの書き込みは、フローティングゲートトランジスタ10でのインパクトイオン化により発生するホットキャリアをフローティングゲート5に注入することにより行なわれる。ホットキャリアの発生は、表5に示した電圧を各領域に与えることにより起こる。

この際、コントロールトランジスタ30の1対のソース/ドレイン用不純物拡散領域22、22は、フローティングゲート5の電位をコントロールする役割を担っている。具体的には、ホットキャリアの発生はフローティングゲート5の(一方のp型不純物拡散領域3から見た)電位が−1V程度の時に最も多くなるため、そのような電位になるように1対のソース/ドレイン用不純物拡散領域22、22およびn型ウェル領域21に電圧が与えられてフローティングゲート5の電位がコントロールされる。

また、メモリセルの消去は、フローティングゲート5に蓄積された電子を一方のソース/ドレイン用不純物拡散領域22、他方のソース/ドレイン用不純物拡散領域22およびn型ウェル領域21に高電位を与えてFNトンネリングによって引き抜くことで行なわれる。FNトンネリングを起こすために、一方のソース/ドレイン用不純物拡散領域22(もしくは他方のソース/ドレイン用不純物拡散領域22)およびn型ウェル領域21には表6に示すような正の電位が与えられる。

この際、1対のp型不純物拡散領域3、3にも表6に示すような負の電圧を与えて、フローティングゲート5の(一方のp型不純物拡散領域3から見た)電位が下げられている。効率よく消去を行うためには、フローティングゲート5と一方のソース/ドレイン用不純物拡散領域22、他方のソース/ドレイン用不純物拡散領域22およびn型ウェル領域21との間の接合容量比をできるだけ小さくして電位差を大きくすることが望ましい。

本実施の形態によれば、1対のソース/ドレイン用不純物拡散領域22、22によりフローティングゲート5の電位をコントロールすることができるため、半導体基板1とフローティングゲート5との間に大きな電位差を与えることが可能となる。これにより、フローティングゲート5内の電子をFNトンネリングで引き抜くことが可能となるため、データの電気的な消去が可能となる。

また、フローティングゲートトランジスタ10がpチャネルMOSトランジスタよりなっているため、実施の形態1と同様、nチャネルMOSトランジスタを用いる場合よりも低電圧で書き込みを行うことが可能となる。

(実施の形態7)

図16は、本発明の実施の形態7における半導体記憶装置の構成を概略的に示す平面図である。図17は、図16のXVII−XVII線に沿う概略断面図である。

図16は、本発明の実施の形態7における半導体記憶装置の構成を概略的に示す平面図である。図17は、図16のXVII−XVII線に沿う概略断面図である。

図16および図17を参照して、本実施の形態のメモリセルの構成は、実施の形態6の構成と比較して、素子分離用のp型不純物拡散領域8を有している点において異なる。

この素子分離用のp型不純物拡散領域8は、フローティングゲートトランジスタ領域とフローティングゲートコントロール領域との間の半導体基板1の主表面に形成されたフィールド絶縁層7の直下の半導体基板1に形成されている。この素子分離用のp型不純物拡散領域8は、半導体基板1よりも高いキャリア濃度を有している。

なお、上記以外の構成については実施の形態1の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

本実施の形態によれば、以下の効果が得られる。

書き込みおよび消去時には表5および表6に示すような電圧がn型ウェル領域21に印加されるが、この際、p型半導体基板1とn型ウェル領域21とのpn接合部には空乏層が生じている。この空乏層の延びが大きくなるにつれて、パンチスルーに伴うリーク電流が増加する。

本実施の形態によれば、素子分離用のp型不純物拡散領域8は半導体基板1よりも高いキャリア濃度を有しているため、この空乏層の延びを抑えることができる。これにより、n型ウェル領域2aとn型ウェル領域21との間隔を小さくすることができ、結果として実施の形態6よりもメモリセルサイズを小さくすることができる。

(実施の形態8)

図18は、本発明の実施の形態8における半導体記憶装置の構成を概略的に示す平面図である。図19(a)および図19(b)は、図18のXIXA−XIXA線に沿う概略断面図および図18のXIXB−XIXB線に沿う概略断面図である。図20は、図18のXX−XX線に沿う概略断面図である。

図18は、本発明の実施の形態8における半導体記憶装置の構成を概略的に示す平面図である。図19(a)および図19(b)は、図18のXIXA−XIXA線に沿う概略断面図および図18のXIXB−XIXB線に沿う概略断面図である。図20は、図18のXX−XX線に沿う概略断面図である。

図18〜図20を参照して、本実施の形態のメモリセルの構成は、実施の形態1の構成と比較して、フローティングゲートコントロール領域内の制御用不純物拡散領域の構成において異なる。

本実施の形態における制御用不純物拡散領域は、n型の不純物拡散領域31により構成されている。n型の不純物拡散領域31は、p型の半導体基板1の主表面に形成されており、フローティングゲート5と絶縁層4bを介して対向している。

なお、上記以外の構成については実施の形態1の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

次に、本実施の形態におけるメモリセルの書き込みおよび消去の動作について説明する。

図19(a)および図19(b)を参照して、メモリセルへの書き込みは、フローティングゲートトランジスタ10でのインパクトイオン化により発生するホットキャリアをフローティングゲート5に注入することにより行なわれる。ホットキャリアの発生は、表7に示した電圧を各領域に与えることにより起こる。

この際、制御用不純物拡散領域(n型不純物拡散領域)31は、フローティングゲート5の電位をコントロールする役割を担っている。具体的には、ホットキャリアの発生はフローティングゲート5の(一方のp型不純物拡散領域3から見た)電位が−1V程度の時に最も多くなるため、そのような電位になるように制御用不純物拡散領域31に電圧が与えられてフローティングゲート5の電位がコントロールされる。

また、メモリセルの消去は、フローティングゲート5に蓄積された電子を制御用不純物拡散領域31に高電位を与えてFNトンネリングによって引き抜くことで行なわれる。FNトンネリングを起こすために、制御用不純物拡散領域31に表8に示すような正の電位が与えられる。

この際、1対のp型不純物拡散領域3、3にも表6に示すような負の電圧を与えて、フローティングゲート5の(一方のp型不純物拡散領域3から見た)電位が下げられている。効率よく消去を行うためには、フローティングゲート5と一方のp型不純物拡散領域3、他方のp型不純物拡散領域3およびn型ウェル領域2aのそれぞれとの間の接合容量比をできるだけ小さくして電位差を大きくすることが望ましい。

本実施の形態のよれば、制御用不純物拡散領域31によりフローティングゲート5の電位をコントロールすることができるため、半導体基板1とフローティングゲート5との間に大きな電位差を与えることが可能となる。これにより、フローティングゲート5内の電子をFNトンネリングで引き抜くことが可能となるため、データの電気的な消去が可能となる。

また、フローティングゲートトランジスタ10がpチャネルMOSトランジスタよりなっているため、実施の形態1と同様、nチャネルMOSトランジスタを用いる場合よりも低電圧で書き込みを行うことが可能となる。

(実施の形態9)

図21は、本発明の実施の形態9における半導体記憶装置の構成を概略的に示す平面図である。図22(a)および図22(b)は、図21のXXIIA−XXIIA線に沿う概略断面図および図21のXXIIB−XXIIB線に沿う概略断面図である。図23は、図21のXXIII−XXIII線に沿う概略断面図である。

図21は、本発明の実施の形態9における半導体記憶装置の構成を概略的に示す平面図である。図22(a)および図22(b)は、図21のXXIIA−XXIIA線に沿う概略断面図および図21のXXIIB−XXIIB線に沿う概略断面図である。図23は、図21のXXIII−XXIII線に沿う概略断面図である。

図21〜図23を参照して、本実施の形態のメモリセルの構成は、実施の形態8の構成と比較して、フローティングゲートコントロール領域内にp型ウェル領域32が追加されている点において異なる。

p型ウェル領域32は半導体基板1の主表面に形成されている。p型ウェル領域32内に、制御用不純物拡散領域(n型不純物拡散領域)31が形成されている。p型ウェル領域12は、半導体基板1よりも高いキャリア濃度を有している。

なお、上記以外の構成については実施の形態3の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

本実施の形態によれば、以下の効果が得られる。

書き込みおよび消去時には表7および表8に示すような電圧がn型ウェル領域2aと制御用不純物拡散領域(n型不純物拡散領域)31に印加されるが、この際、n型ウェル領域2aとp型半導体基板1とのpn接合部および制御用不純物拡散領域(n型不純物拡散領域)31とp型領域とのpn接合部には空乏層が生じている。この空乏層の延びが大きくなるにつれて、パンチスルーに伴うリーク電流が増加する。

本実施の形態によれば、p型ウェル領域32は半導体基板1よりも高いキャリア濃度を有しているため、この空乏層の延びを抑えることができる。これにより、n型ウェル領域2aと制御用不純物拡散領域(n型不純物拡散領域)31との間隔を小さくすることができ、結果として実施の形態8よりもメモリセルサイズを小さくすることができる。

(実施の形態10)

図24は、本発明の実施の形態10における半導体記憶装置の構成を概略的に示す平面図である。図25は、図24のXXV−XXV線に沿う概略断面図である。

図24は、本発明の実施の形態10における半導体記憶装置の構成を概略的に示す平面図である。図25は、図24のXXV−XXV線に沿う概略断面図である。

図24および図25を参照して、本実施の形態のメモリセルの構成は、実施の形態9の構成と比較して、素子分離用のp型不純物拡散領域8を有している点において異なる。

この素子分離用のp型不純物拡散領域8は、フローティングゲートトランジスタ領域とフローティングゲートコントロール領域との間の半導体基板1の主表面に形成されたフィールド絶縁層7の直下の半導体基板1に形成されている。この素子分離用のp型不純物拡散領域8は、半導体基板1よりも高いキャリア濃度を有している。

なお、上記以外の構成については実施の形態1の構成とほぼ同じであるため、同一の構成要素については同一の符号を付し、その説明を省略する。

本実施の形態によれば、以下の効果が得られる。

書き込みおよび消去時には表7および表8に示すような電圧がn型ウェル領域2aに印加されるが、この際、p型半導体基板1とn型ウェル領域2aとのpn接合部には空乏層が生じている。この空乏層の延びが大きくなるにつれて、パンチスルーに伴うリーク電流が増加する。

本実施の形態によれば、素子分離用のp型不純物拡散領域8は半導体基板1よりも高いキャリア濃度を有しているため、この空乏層の延びを抑えることができる。これにより、n型ウェル領域2aとn型ウェル領域31との間隔を小さくすることができ、結果として実施の形態9よりもメモリセルサイズを小さくすることができる。

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

1 p型半導体基板、2a,2b n型ウェル領域、3 p型不純物拡散領域(ソース/ドレイン)、4a トンネル絶縁層、4b 絶縁層、5 フローティングゲート、6 p型制御用不純物拡散領域、7 フィールド絶縁層、8 p型不純物拡散領域、10 フローティングゲートトランジスタ、11 n型ソース/ドレイン用不純物拡散領域、12 p型ウェル領域、20 nチャネルコントロールトランジスタ、21 n型ウェル領域、22 p型ソース/ドレイン用不純物拡散領域、30 pチャネルコントロールトランジスタ、31 n型ウェル領域、31 n型制御用不純物拡散領域、32 p型ウェル領域。

Claims (10)

- 主表面を有する半導体基板と、

前記半導体基板の主表面に形成されたソース/ドレインとなる1対のp型不純物拡散領域と、

前記1対のp型不純物拡散領域に挟まれる前記半導体基板の領域の上にトンネル絶縁層を介して形成されたフローティングゲートと、

前記半導体基板の主表面に形成された、前記フローティングゲートの電位を制御するための制御用不純物拡散領域とを備えた、不揮発性半導体記憶装置。 - 前記制御用不純物拡散領域は、p型の導電型を有し、かつ前記フローティングゲートと絶縁層を介して対向することを特徴とする、請求項1に記載の不揮発性半導体記憶装置。

- 前記制御用不純物拡散領域は、前記フローティングゲートの下側に位置する前記半導体基板の領域を挟むように前記半導体基板の主表面に形成された1対のソース/ドレイン用不純物拡散領域であることを特徴とする、請求項1に記載の不揮発性半導体記憶装置。

- 前記1対のソース/ドレイン用不純物拡散領域はn型の導電型を有することを特徴とする、請求項3に記載の不揮発性半導体記憶装置。

- 前記半導体基板の主表面に形成されたp型ウェル領域をさらに備え、

n型の前記1対のソース/ドレイン用不純物拡散領域は前記p型ウェル領域内に形成されていることを特徴とする、請求項4に記載の不揮発性半導体記憶装置。 - 前記1対のソース/ドレイン用不純物拡散領域はp型の導電型を有することを特徴とする、請求項3に記載の不揮発性半導体記憶装置。

- 前記半導体基板の主表面に形成されたn型ウェル領域をさらに備え、

p型の前記1対のソース/ドレイン用不純物拡散領域は前記n型ウェル領域内に形成されていることを特徴とする、請求項6に記載の不揮発性半導体記憶装置。 - 前記制御用不純物拡散領域は、n型の導電型を有し、かつ前記フローティングゲートと絶縁層を介して対向することを特徴とする、請求項1に記載の不揮発性半導体記憶装置。

- 前記半導体基板の主表面に形成されたp型ウェル領域をさらに備え、

n型の前記制御用不純物拡散領域は前記p型ウェル領域内に形成されていることを特徴とする、請求項8に記載の不揮発性半導体記憶装置。 - 前記1対のp型不純物拡散領域の形成領域と前記制御用不純物拡散領域の形成領域との間の前記半導体基板の主表面に形成されたフィールド絶縁層と、

前記フィールド絶縁層の直下の前記半導体基板に形成された素子分離用p型不純物拡散領域とをさらに備えたことを特徴とする、請求項1〜9のいずれかに記載の不揮発性半導体記憶装置。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003274728A JP2005039067A (ja) | 2003-07-15 | 2003-07-15 | 不揮発性半導体記憶装置 |

| TW092136678A TWI239640B (en) | 2003-07-15 | 2003-12-24 | Nonvolatile semiconductor memory device |

| US10/757,438 US20050012138A1 (en) | 2003-07-15 | 2004-01-15 | Nonvolatile semiconductor memory device |

| DE102004003597A DE102004003597A1 (de) | 2003-07-15 | 2004-01-23 | Nichtflüchtige Halbleiterspeichervorrichtung |

| KR1020040016375A KR20050008459A (ko) | 2003-07-15 | 2004-03-11 | 불휘발성 반도체 기억장치 |

| CNA2004100304643A CN1577868A (zh) | 2003-07-15 | 2004-03-15 | 非易失性半导体存储器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003274728A JP2005039067A (ja) | 2003-07-15 | 2003-07-15 | 不揮発性半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005039067A true JP2005039067A (ja) | 2005-02-10 |

| JP2005039067A5 JP2005039067A5 (ja) | 2006-08-17 |

Family

ID=34056086

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003274728A Withdrawn JP2005039067A (ja) | 2003-07-15 | 2003-07-15 | 不揮発性半導体記憶装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20050012138A1 (ja) |

| JP (1) | JP2005039067A (ja) |

| KR (1) | KR20050008459A (ja) |

| CN (1) | CN1577868A (ja) |

| DE (1) | DE102004003597A1 (ja) |

| TW (1) | TWI239640B (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005252267A (ja) * | 2004-03-05 | 2005-09-15 | Programmable Microelectron Corp | シングルポリ・pフラッシュ技術を使用した不揮発性メモリソリューション |

| JP2006344736A (ja) * | 2005-06-08 | 2006-12-21 | Seiko Epson Corp | 半導体装置 |

| JP2006344668A (ja) * | 2005-06-07 | 2006-12-21 | Seiko Epson Corp | 半導体装置 |

| JP2006344735A (ja) * | 2005-06-08 | 2006-12-21 | Seiko Epson Corp | 半導体装置 |

| JP2007149943A (ja) * | 2005-11-28 | 2007-06-14 | Nec Electronics Corp | 不揮発性メモリセル及びeeprom |

| JP2007250948A (ja) * | 2006-03-17 | 2007-09-27 | Seiko Epson Corp | 半導体装置 |

| JP2008085230A (ja) * | 2006-09-28 | 2008-04-10 | Toshiba Corp | エージングデバイス及びその製造方法 |

| JP2013191826A (ja) * | 2012-03-12 | 2013-09-26 | Ememory Technology Inc | 消去可能なプログラマブル単一ポリ不揮発性メモリの製造方法 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7709307B2 (en) | 2006-08-24 | 2010-05-04 | Kovio, Inc. | Printed non-volatile memory |

| CN108257963A (zh) * | 2016-12-29 | 2018-07-06 | 北京同方微电子有限公司 | 一种闪存存储单元 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3919711A (en) * | 1973-02-26 | 1975-11-11 | Intel Corp | Erasable floating gate device |

| NL7500550A (nl) * | 1975-01-17 | 1976-07-20 | Philips Nv | Halfgeleider-geheugeninrichting. |

| US4035820A (en) * | 1975-12-29 | 1977-07-12 | Texas Instruments Incorporated | Adjustment of avalanche voltage in DIFMOS memory devices by control of impurity doping |

| JPH08506693A (ja) * | 1992-06-19 | 1996-07-16 | ラティス・セミコンダクター・コーポレイション | 単層の多結晶シリコン層を有するフラッシュe▲上2▼promセル |

| US5761121A (en) * | 1996-10-31 | 1998-06-02 | Programmable Microelectronics Corporation | PMOS single-poly non-volatile memory structure |

| US5841165A (en) * | 1995-11-21 | 1998-11-24 | Programmable Microelectronics Corporation | PMOS flash EEPROM cell with single poly |

| US6628544B2 (en) * | 1999-09-30 | 2003-09-30 | Infineon Technologies Ag | Flash memory cell and method to achieve multiple bits per cell |

| US6329240B1 (en) * | 1999-10-07 | 2001-12-11 | Monolithic System Technology, Inc. | Non-volatile memory cell and methods of fabricating and operating same |

| EP1091408A1 (en) * | 1999-10-07 | 2001-04-11 | STMicroelectronics S.r.l. | Non-volatile memory cell with a single level of polysilicon |

| US6617637B1 (en) * | 2002-11-13 | 2003-09-09 | Ememory Technology Inc. | Electrically erasable programmable logic device |

-

2003

- 2003-07-15 JP JP2003274728A patent/JP2005039067A/ja not_active Withdrawn

- 2003-12-24 TW TW092136678A patent/TWI239640B/zh not_active IP Right Cessation

-

2004

- 2004-01-15 US US10/757,438 patent/US20050012138A1/en not_active Abandoned

- 2004-01-23 DE DE102004003597A patent/DE102004003597A1/de not_active Ceased

- 2004-03-11 KR KR1020040016375A patent/KR20050008459A/ko active IP Right Grant

- 2004-03-15 CN CNA2004100304643A patent/CN1577868A/zh active Pending

Cited By (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005252267A (ja) * | 2004-03-05 | 2005-09-15 | Programmable Microelectron Corp | シングルポリ・pフラッシュ技術を使用した不揮発性メモリソリューション |

| JP2006344668A (ja) * | 2005-06-07 | 2006-12-21 | Seiko Epson Corp | 半導体装置 |

| US7626225B2 (en) | 2005-06-07 | 2009-12-01 | Seiko Epson Corporation | Semiconductor device including nonvolatile memory having a floating gate electrode |

| JP4591691B2 (ja) * | 2005-06-07 | 2010-12-01 | セイコーエプソン株式会社 | 半導体装置 |

| JP2006344736A (ja) * | 2005-06-08 | 2006-12-21 | Seiko Epson Corp | 半導体装置 |

| JP2006344735A (ja) * | 2005-06-08 | 2006-12-21 | Seiko Epson Corp | 半導体装置 |

| JP4548603B2 (ja) * | 2005-06-08 | 2010-09-22 | セイコーエプソン株式会社 | 半導体装置 |

| JP2007149943A (ja) * | 2005-11-28 | 2007-06-14 | Nec Electronics Corp | 不揮発性メモリセル及びeeprom |

| JP2007250948A (ja) * | 2006-03-17 | 2007-09-27 | Seiko Epson Corp | 半導体装置 |

| JP4622902B2 (ja) * | 2006-03-17 | 2011-02-02 | セイコーエプソン株式会社 | 不揮発性半導体記憶装置 |

| JP2008085230A (ja) * | 2006-09-28 | 2008-04-10 | Toshiba Corp | エージングデバイス及びその製造方法 |

| JP2013191826A (ja) * | 2012-03-12 | 2013-09-26 | Ememory Technology Inc | 消去可能なプログラマブル単一ポリ不揮発性メモリの製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20050008459A (ko) | 2005-01-21 |

| TW200503251A (en) | 2005-01-16 |

| US20050012138A1 (en) | 2005-01-20 |

| DE102004003597A1 (de) | 2005-02-17 |

| TWI239640B (en) | 2005-09-11 |

| CN1577868A (zh) | 2005-02-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5007017B2 (ja) | 半導体装置の製造方法 | |

| TWI413261B (zh) | 半導體裝置 | |

| JPH07193150A (ja) | 不揮発性半導体記憶装置およびその動作方法 | |

| JP2009054707A (ja) | 半導体記憶装置およびその製造方法 | |

| JP2009525591A (ja) | Nrom用2次注入 | |

| JP2010278314A (ja) | 半導体装置およびその製造方法 | |

| JP2011103332A (ja) | 半導体装置およびその製造方法 | |

| TW461094B (en) | A new single poly EEPROM cell structure, operations, and array architecture | |

| US9893208B2 (en) | Nonvolatile memory device | |

| JP2005039067A (ja) | 不揮発性半導体記憶装置 | |

| JP4622902B2 (ja) | 不揮発性半導体記憶装置 | |

| US20100039868A1 (en) | Low voltage, low power single poly EEPROM | |

| JP2002184879A (ja) | 半導体装置およびその製造方法 | |

| JP2008141150A (ja) | メモリセル、このメモリセルに記録された情報の消去方法、及びこのメモリセルを備える不揮発性半導体記憶装置 | |

| TW451482B (en) | Flash memory cell using n+/p-well diode with double poly floating gate | |

| JP2006165451A (ja) | 半導体装置及びその製造方法 | |

| JP3288099B2 (ja) | 不揮発性半導体記憶装置及びその書き換え方法 | |

| JP2004047889A (ja) | 不揮発性半導体メモリ装置およびその製造方法 | |

| JPH07193200A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| JPH06177360A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| JP2006339554A (ja) | 不揮発性半導体記憶装置及びその動作方法 | |

| JP2008270364A (ja) | 不揮発性半導体記憶素子 | |

| TW200534361A (en) | A split-gate p-channel flash memory cell with programming by band-to-band hot electron method | |

| US9966476B2 (en) | Semiconductor memory device having first and second floating gates of different polarity | |

| Park et al. | Depletion-enhanced body-isolation (DEBI) array on SOI for highly scalable and reliable NAND flash memories |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060705 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060705 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20060824 |