JP2004246793A - カード型デバイス - Google Patents

カード型デバイス Download PDFInfo

- Publication number

- JP2004246793A JP2004246793A JP2003038365A JP2003038365A JP2004246793A JP 2004246793 A JP2004246793 A JP 2004246793A JP 2003038365 A JP2003038365 A JP 2003038365A JP 2003038365 A JP2003038365 A JP 2003038365A JP 2004246793 A JP2004246793 A JP 2004246793A

- Authority

- JP

- Japan

- Prior art keywords

- data

- type device

- card

- fifo memory

- oscillator

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Abstract

【課題】発振器の停止による十分な低消費電力化が可能なカード型デバイスを提供する。

【解決手段】データが受信FIFOメモリ21に書き込まれていないときに、受信FIFOメモリ21からのライト信号RXRDYがローレベルとなって、発振制御部17からの発振イネーブル信号がローレベルとなり、水晶発振器14が停止される。これにより、CPU16や他の論理回路の動作が停止される。このとき、カード型デバイス10の消費電力が殆ど無く、パワーダウンモードとなっている。データが受信FIFOメモリ21に書き込まれて格納されると、受信FIFOメモリ21からのライト信号RXRDYがハイレベルとなって、発振制御部17からの発振イネーブル信号がハイレベルとなり、水晶発振器14が起動され、CPU16が割り込みをかけられて動作状態となる。

【選択図】図1

【解決手段】データが受信FIFOメモリ21に書き込まれていないときに、受信FIFOメモリ21からのライト信号RXRDYがローレベルとなって、発振制御部17からの発振イネーブル信号がローレベルとなり、水晶発振器14が停止される。これにより、CPU16や他の論理回路の動作が停止される。このとき、カード型デバイス10の消費電力が殆ど無く、パワーダウンモードとなっている。データが受信FIFOメモリ21に書き込まれて格納されると、受信FIFOメモリ21からのライト信号RXRDYがハイレベルとなって、発振制御部17からの発振イネーブル信号がハイレベルとなり、水晶発振器14が起動され、CPU16が割り込みをかけられて動作状態となる。

【選択図】図1

Description

【0001】

【発明の属する技術分野】

本発明は、外部の情報端末装置との間でデータを送受するカード型デバイスに関する。

【0002】

【従来の技術】

この種のカード型デバイスは、PC(Personal Computer)カード、CFカード、モデムカード等であり、ノート型パーソナルコンピュータやPDA(Personal Digital Assistants)等の情報端末装置のスロットに挿入されて用いられる。このカード型デバイスでは、外部の情報端末装置との間でデータを送受するためのインターフェースを備えており、データの送受、演算処理、データの記憶等を行なう。

【0003】

図7に従来のカード型デバイスの一例を示す。このカード型デバイス101は、UART(Universal Asynchronous Receiver Transmitter)である汎用のインターフェース102、LSI103、ROM104、RAM105、及びクロック信号を供給する発振器106等を備えている。LSI103は、シリアルインターフェース107、CPU108、及びクロック制御部109等を含んでいる。

【0004】

UARTのインターフェース102は、データを外部の情報端末装置との間で送受し、受信データをパラレルシリアル変換したり、送信データをシリアルパラレル変換する。CPU108は、シリアルインターフェース107を通じて、データをUARTのインターフェース102との間で送受し、データの処理や、RAM105に対するデータの読み書き等を行なう。

【0005】

一方、この様なカード型デバイスは、携帯型情報端末装置のスロットに挿入されて用いられることが多く、携帯情報端末装置の電源から電力を供給されて動作する。そして、カード型デバイスでは、携帯型情報端末装置の電源の容量が限られることから、消費電流の節減が重要視され、パワーダウンモード等が付与されている。例えば、クロック制御部109は、データの書き込み等の処理が行なわれないときに発振器106からCPU108及び他の論理回路等へのクロックの供給を停止したり、クロックの周波数を低くしたりして、消費電力を低減させている。

【0006】

ただし、カード型デバイスを外部の情報端末装置に接続した状態では、UARTのインターフェース102によるデータの受信及びパラレルシリアル変換が何時でもできる様にするため、UARTのインターフェース102へのクロックの供給を中断することはない。

【0007】

【発明が解決しようとする課題】

ところで、LSIの消費電力は、クロック周波数とクロックが供給される回路規模で決まることから、低消費電力化のためには、発振器を停止させて、クロックの供給を完全に中断することが理想的である。

【0008】

しかしながら、従来は、UARTのインターフェースを用いているので、データを受信する可能性があるときには、クロックをインターフェースに常に供給する必要があり、発振器を停止させることができなかった。

【0009】

従って、発振器を停止させたときの消費電力を考慮するならば、低消費電力化の余地が十分に残っているといえる。

【0010】

そこで、本発明は、上記従来の問題点に鑑みてなされたものであり、発振器の停止による十分な低消費電力化が可能なカード型デバイスを提供することを目的とする。

【0011】

【課題を解決するための手段】

上記課題を解決するために本発明は、外部の情報端末装置との間でデータを送受するカード型デバイスにおいて、外部の情報端末装置から受信された処理すべきデータがない非受信状態を判別する判別手段と、判別手段により非受信状態が判別されたときには、該カード型デバイスに動作クロックを供給する発振器を停止させる発振制御手段とを備えている。

【0012】

この様な構成の本発明によれば、外部の情報端末装置から受信された処理すべきデータがない非受信状態のときに、発振器が停止されて、クロックの供給が中断される。カード型デバイスは、データを受信したときに動作すれば良いので、データの非受信状態のときに発振器を停止させて、クロックの供給を中断し、その動作を中断しても構わない。これにより、発振器の停止による十分な低消費電力化が可能になる。

【0013】

発振器の停止はCPUの制御により行うことができ、これは例えばCPUのHALT命令の実行により制御される。

【0014】

更に、本発明においては、外部の情報端末装置からのデータが受信されると、発振器を起動している。

【0015】

この様にデータが受信されたときに、発振器が起動されれば、データの処理のためにカード型デバイスの動作を再開させることができる。

【0016】

また、本発明においては、発振器が停止された状態で、データを受信するファーストインファーストアウトのインターフェースを備え、発振制御手段は、インターフェースからの信号に応答して発振器を起動している。

【0017】

この様なファーストインファーストアウトのインターフェースを採用すれば、発振器が停止された状態で、データを受信することができる。また、データを受信したときには、インターフェースからの信号に応答して発振器を起動し、該データの処理のためにカード型デバイスの動作を再開することができる。

【0018】

次に、本発明は、外部の情報端末装置との間でデータを送受するカード型デバイスにおいて、該カード型デバイスに動作クロックを供給する発振器が停止された状態で、データを受信するファーストインファーストアウトのインターフェースと、外部の情報端末装置から受信された処理すべきデータがない非受信状態を判別する判別手段と、判別手段により非受信状態が判別されたときには、発振器から該カード型デバイスの少なくとも一部に対する動作クロックの供給を停止させ、インターフェースからの信号に応答して発振器を起動する発振制御手段とを備えている。

【0019】

この様に外部の情報端末装置から受信された処理すべきデータがない非受信状態のときに、発振器から該カード型デバイスの少なくとも一部に対する動作クロックの供給を停止させるだけでも、十分な低消費電力化が可能である。また、データを受信したときには、インターフェースからの信号に応答して発振器を起動し、該データの処理のためにカード型デバイスの動作を再開することができる。

【0020】

【発明の実施の形態】

以下、本発明の実施形態を添付図面を参照して詳細に説明する。

【0021】

図1は、本発明のカード型デバイスの一実施形態を示すブロック図である。本実施形態のカード型デバイス10は、PCカードであって、ノート型パーソナルコンピュータやPDA等の情報端末装置のスロットに挿入されて用いられるものであり、LSI11、ROM12、RAM13、及び水晶発振器14等を備えている。LSI11は、DTEインターフェース15、CPU16、及び発振制御部17等を含んでいる。

【0022】

発振制御部17は、発振イネーブル信号を水晶発振器14に加えて、水晶発振器14を制御する。発振制御部17により発振イネーブル信号がハイレベルにされると、水晶発振器14が起動され、発振制御部17により発振イネーブル信号がローレベルにされると、水晶発振器14が停止される。

【0023】

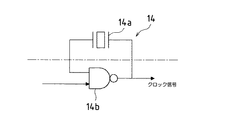

水晶発振器14は、図2に示す様にクロック信号を発生する水晶振動子14aとナンド回路14bを備えており、発振イネーブル信号がハイレベルのときに、クロック信号を出力して、クロック信号をカード型デバイス10の各所に供給する。また、発振イネーブル信号がローレベルのときに、クロック信号の出力を停止する。

【0024】

CPU16は、DTEインターフェース15を通じて、データを外部の情報端末装置との間で送受し、データの処理やRAM13に対するデータの読み書き等を行なう。

【0025】

DTEインターフェース15は、受信FIFO(First In First Out)メモリ21及び送信FIFOメモリ22を含むパラレルインターフェースであり、外部の情報端末装置との間で送受されるデータを一時的に格納する。また、DTEインターフェース15は、アドレスバス及びデータバスを通じて、外部の情報端末装置に接続され、外部の情報端末装置からのIOWR(書き込み)命令及びIORD(読み出し)命令を受けて制御され、外部の情報端末装置によりデータが受信FIFOメモリ21に書き込まれ、外部の情報端末装置によりデータが送信FIFOメモリ22から読み出される。従って、受信FIFOメモリ21への書き込み及び送信FIFOメモリ22からの読み出しは、水晶発振器14からの動作用のクロック信号とは非同期で行われる。

【0026】

さて、この様な構成において、受信FIFOメモリ21は、データが書き込まれていないときに、ライト信号RXRDYをローレベルに設定する。発振制御部17は、ライト信号RXRDYがローレベルのときに、発振イネーブル信号をローレベルに設定して、水晶発振器14を停止させる。これにより、CPU16や他の論理回路にクロック信号が供給されず、CPU16や他の論理回路の動作が停止される。このとき、カード型デバイス10の消費電力が殆ど無く、パワーダウンモードとなっている。

【0027】

次に、受信FIFOメモリ21は、外部の情報端末装置によりデータが書き込まれて格納されると、ライト信号RXRDYをローレベルからハイレベルに切り換える。発振制御部17は、ライト信号RXRDYがハイレベルになると、発振イネーブル信号をハイレベルに切り換えて、水晶発振器14を起動させる。この水晶発振器14の起動により、動作用のクロック信号の供給が開始される。そして、クロック信号が安定化すると、発振制御部17によりCPU16に対する割り込みがかけられ、CPU16や他の論理回路の動作が開始される。

【0028】

CPU16は、動作状態になると、データを受信FIFOメモリ21から読み出して、このデータをRAM13内のデータ受信バッファ領域に格納する。このとき、受信FIFOメモリ21が空となり、ライト信号RXRDYがローレベルに戻る。

【0029】

引き続いて、CPU16は、データ受信バッファ領域内のデータを処理する。例えば、データ受信バッファ領域内のデータが命令であれば、この命令がCPU16により実行される。

【0030】

仮に、カード型デバイス10がモデムカードであって、「AT+CR(キャリッジリターン)」という文字列(命令)が受信FIFOメモリ21に書き込まれれば、この命令がデータ受信バッファ領域内に転送され、この命令がCPU16により実行されて、「OK+CR」という文字列が送信FIFOメモリ22に書き込まれて外部の情報端末装置へと返される。

【0031】

また、CPU16は、データ受信バッファ領域内のデータが意味不明であれば、新たなデータが受信FIFOメモリ21に書き込まれるのを待機する。そして、新たなデータが受信FIFOメモリ21に書き込まれず、ライト信号RXRDYがローレベルのままで、一定時間が経過する。CPU16は、発振停止信号を発振制御部17に加える。これに応答して発振制御部17は、発振イネーブル信号をローレベルに切り換えて、水晶発振器14を停止させる。これにより、CPU16や他の論理回路の動作が停止されて、パワーダウンモードとなる。

【0032】

以降同様に、新たなデータが受信FIFOメモリ21に書き込まれて格納されると、受信FIFOメモリ21からのライト信号RXRDYがハイレベルとなって、発振制御部17からの発振イネーブル信号がハイレベルとなり、水晶発振器14が起動され、CPU16が割り込みをかけられて動作状態となる。また、新たなデータが受信FIFOメモリ21に書き込まれず、ライト信号RXRDYがローレベルのままで、一定時間が経過すると、発振停止信号が発振制御部17に加えられて、水晶発振器14が停止され、パワーダウンモードとなる。

【0033】

この様に本実施形態のカード型デバイス10では、パワーダウンモードに際し、水晶発振器14を停止させて、CPU16や他の論理回路の動作を停止させているので、消費電力を十分に低減することができる。

【0034】

図3は、本発明のカード型デバイスの他の実施形態を示すブロック図である。また、図4は、本実施形態のカード型デバイスの使用状態を示す図である。

【0035】

本実施形態のカード型デバイス30は、PCカードであり、ケーブル31を介して携帯電話機32に接続され、かつノート型パーソナルコンピュータ33のスロットに挿入されて用いられ、携帯電話機32とノート型パーソナルコンピュータ33間を中継する。

【0036】

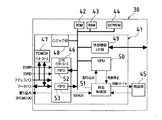

カード型デバイス30は、LSI41、ROM42、RAM43、EEPROM44、及び水晶発振器45等を備えている。LSI41は、DTEインターフェース46、PCMCIAインターフェース47、ロジック部48、通信インターフェース49、CPU50、及び発振制御部51等を含んでいる。

【0037】

発振制御部51は、発振イネーブル信号を水晶発振器45に加えて、水晶発振器45を制御する。例えば、ノート型パーソナルコンピュータ33によりデータがDTEインターフェース46の受信FIFOメモリ52に書き込まれたり、携帯電話機32からの着信が通信インターフェース49で検出されたりしたときに、発振制御部51により発振イネーブル信号がハイレベルにされて、水晶発振器45が起動される。また、CPU50からの発振停止信号に応答して、発振制御部51により発振イネーブル信号がローレベルにされて、水晶発振器45が停止される。水晶発振器45は、動作時に、動作用のクロック信号をカード型デバイス30の各所に供給する。

【0038】

また、発振制御部51は、発振イネーブル信号をハイレベルにして、水晶発振器45を起動させた後で、水晶発振器45からのクロック信号を計数し、この計数値が予め設定された値になると、CPU50に対して割り込みをかける。

【0039】

CPU50は、ROM42内のプログラムに従って動作し、DTEインターフェース46を通じて、データをノート型パーソナルコンピュータ33との間で送受し、データの処理やRAM43に対するデータの読み書き等を行なう。また、CPU50は、通信インターフェース49を通じて、データを携帯電話機32との間で送受する。

【0040】

DTEインターフェース46は、受信FIFOメモリ52及び送信FIFOメモリ53を含むパラレルインターフェースであり、ノート型パーソナルコンピュータ33との間で送受されるデータを一時的に格納する。また、DTEインターフェース46は、アドレスバス及びデータバスを通じて、ノート型パーソナルコンピュータ33に接続され、ノート型パーソナルコンピュータ33からのIOWR命令及びIORD命令を受けて制御され、データを受信FIFOメモリ52に書き込まれたり、データを送信FIFOメモリ53から読み出されたりする。受信FIFOメモリ52への書き込み及び送信FIFOメモリ53からの読み出しは、水晶発振器45からの動作用のクロック信号とは非同期で行われる。また、ノート型パーソナルコンピュータ33は、受信FIFOメモリ52が満杯になるまで、データを受信FIFOメモリ52に書き込むことができる。

【0041】

PCMCIAインターフェース47は、このカード型デバイス30をI/Oカードとして動作させるためのアトリビュートメモリやコンフィグレーションレジスタ等からなる。

【0042】

通信インターフェース49は、携帯電話機32に対する発着信や切断の制御を行なうシリアルインターフェースやデータ送受信のための回路等を含む。

【0043】

ロジック部48は、タイマーやメモリの管理等を行なう。

【0044】

EEPROM44は、読み書き可能なROMであり、このカード型デバイス30の使用者により設定されたPCカードの情報を記憶するSレジスタを含む。

【0045】

次に、図5のフローチャート及び図6のタイミングチャートを参照しつつ、カード型デバイス30の動作の一例を説明する。

【0046】

まず、カード型デバイス30の起動時には(ステップS61)、HALT命令がCPU50により実行されて、ホールド状態が設定される(ステップS62)。ホールド状態とは、カード型デバイス30の動作を停止して、電源を切ることが可能な状態のことである。ただし、ノート型パーソナルコンピュータ33による受信FIFOメモリ52及び送信FIFOメモリ53の読み出し及び書き込み、及び通信インターフェース49による着信検出は可能である。

【0047】

また、このときには、発振制御部51からの発振イネーブル信号がローレベルであり、水晶発振器45が停止されている。このため、CPU50やロジック部48等にクロック信号が供給されず、CPU50やロジック部48等の動作が停止される。このとき、カード型デバイス30の消費電力が殆ど無く、パワーダウンモードとなる。

【0048】

このパワーダウンモードの状態で、受信FIFOメモリ52は、ノート型パーソナルコンピュータ33によりデータがに書き込まれると、ライト信号RXRDYをローレベルからハイレベルに切り換える。あるいは、通信インターフェース49は、携帯電話機32からの着信を検出すると、発振制御部51に対して割り込みをかける。発振制御部51は、ライト信号RXRDYがハイレベルになったり、通信インターフェース49により割り込みがかけられたりすると、発振イネーブル信号をハイレベルにして、水晶発振器45を起動し、動作用のクロック信号をカード型デバイス30の各所に供給する。そして、発振制御部51は、水晶発振器45からのクロック信号を計数し、この計数値が予め設定された値になると、つまり一定時間が経過すると、CPU50に対して割り込みをかける(ステップS63)。この一定時間の待機により、クロック信号の安定化の後に、CPU50の動作が開始される。

【0049】

CPU50は、割り込みを受けると、この割り込みの要因を判定する(ステップS64)。そして、この割り込みの要因が携帯電話機32からの着信であれば(ステップS65で「No」)、CPU50は、HALT命令を解除してから、着信に応じた処理を行なう(ステップS66)。例えば、CPU50は、「RING」という文字列を送信FIFOメモリ53に書き込む。この「RING」という文字列は、ノート型パーソナルコンピュータ33により読み出される。この後、CPU50は、発振停止信号を発振制御部51に加えてから、HALT命令を実行して、パワーダウン状態を再び設定する(ステップS62)。発振制御部51は、発振停止信号に応答して発振イネーブル信号をローレベルに切り換え、水晶発振器45を停止させる。これにより、CPU50やロジック部48等の動作が停止されて、パワーダウンモードとなる。

【0050】

また、割り込みの要因がノート型パーソナルコンピュータ33から受信FIFOメモリ52へのデータの書き込みであれば(ステップS65で「Yes」)、CPU50は、HALT命令を解除してから、データを受信FIFOメモリ52から読み出す(ステップS67)。

【0051】

例えば、図6のタイミングチャートに示す様に時点t1で、ノート型パーソナルコンピュータ33によりデータが受信FIFOメモリ52に書き込まれて、受信FIFOメモリ52からのライト信号RXRDYがハイレベルになると、発振制御部51により発振イネーブル信号がハイレベルにされ、水晶発振器45が起動されて、クロック信号の供給が開始され、一定時間が経過した時点t2で、発振制御部51によりCPU50に対する割り込みがかけられ(ステップS63)、各ステップS64,65が行われ、パワーダウン状態が解除されて、データが受信FIFOメモリ52から読み出される(ステップS67)。

【0052】

そして、CPU50は、受信FIFOメモリ52から読み出したデータが「CR」という文字列であるか否かを判定する(ステップS68)。「CR」という文字列は、1つの命令の最後に付けられる。従って、「CR」という文字列が受信されなければ、引き続く次の文字列が受信されることになり、また「CR」という文字列が受信されれば、1つの命令の受信が完了したことになる。

【0053】

ここで、読み出したデータが「CR」でなければ(ステップS68で「No」)、CPU50は、この読み出したデータをRAM43内のデータ受信バッファ領域に格納してから(ステップS69)、一定時間待機する(ステップS70)。この待機中に、ノート型パーソナルコンピュータ33により新たなデータが受信FIFOメモリ52に書き込まれなければ(ステップS71で「No」)、CPU50は、発振停止信号を発振制御部51に加えてから、HALT命令を実行して、パワーダウン状態を再び設定する(ステップS62)。これにより、水晶発振器45が停止されて、CPU50やロジック部48等の動作が停止され、パワーダウンモードとなる。

【0054】

例えば、図6のタイミングチャートに示す様にデータが受信FIFOメモリ52から読み出されてRAM43内のデータ受信バッファ領域に格納されてから、更に一定時間待機した時点t3で(ステップS70)、新たなデータが受信FIFOメモリ52に書き込まれなければ(ステップS71で「No」)、HALT命令が実行される(ステップS62)。

【0055】

また、一定時間の待機中に(ステップS70)、ノート型パーソナルコンピュータ33により新たなデータが受信FIFOメモリ52に書き込まれれば(ステップS71で「Yes」)、ステップS67に戻る。

【0056】

例えば、図6のタイミングチャートに示す様に時点t4で、ノート型パーソナルコンピュータ33によりデータが受信FIFOメモリ52に書き込まれ、この後にデータが受信FIFOメモリ52から読み出されてRAM43内のデータ受信バッファ領域に格納され、引き続いて一定時間が経過するまでに(ステップS70)、新たなデータが受信FIFOメモリ52に書き込まれれば(ステップS71で「Yes」)、HALT命令が実行されずに、ステップS67に戻る。

【0057】

従って、ノート型パーソナルコンピュータ33によるデータの書き込み間隔が一定時間以内であれば、HALT命令が実行されることなく、データが受信FIFOメモリ52から順次読み出されてRAM43内のデータ受信バッファ領域に逐次格納される。また、ノート型パーソナルコンピュータ33によるデータの書き込み間隔が一定時間を超えると、その度にHALT命令が実行されて、パワーダウンモードとなり、ノート型パーソナルコンピュータ33による新たなデータの書き込みが待機されることになる。

【0058】

ステップS70で一定時間待機するのは、ステップS62に頻繁に戻って、その度にHALT命令が実行され、水晶発振器45が停止されることを防止するためである。水晶発振器45の起動に際しては、クロック信号が安定化するまでの一定時間を待機する必要があることから、仮に水晶発振器45が頻繁に停止されると、待機時間が長くなり、一連のデータを受信して処理するための時間も長くなってしまう。

【0059】

こうしてノート型パーソナルコンピュータ33による受信FIFOメモリ52へのデータの書き込み、及び受信FIFOメモリ52からのデータの読み出しが繰り返され、1つの命令の最後に付けられる「CR」という文字列の書き込みと読み出しも行われる。

【0060】

このとき、CPU50は、受信FIFOメモリ52から読み出したデータが「CR」という文字列であることから(ステップS68で「Yes」)、この文字列をRAM43内のデータ受信バッファ領域に格納してから、データ受信バッファ領域内の一連の文字列を読み出して(ステップS72)、この一連の文字列からなる命令が有効であるか否かを判定する(ステップS73)。

【0061】

そして、データ受信バッファ領域内の一連の文字列からなる命令が有効であれば(ステップS73で「Yes」)、CPU50は、この命令を実行する。例えば、一連の文字列が「ATS0?+CR」という有効な命令であれば、この命令を実行する(ステップS74)。この「ATS0?+CR」という命令は、EEPROM44内のSレジスタの情報の問い合わせを意味する。このため、CPU50は、Sレジスタの情報を送信FIFOメモリ53に書き込んでノート型パーソナルコンピュータ33へと返す。更に、CPU50は、送信FIFOメモリ53のデータが読み出されたことを確認してから(ステップS75)、ステップS70に移る。

【0062】

また、データ受信バッファ領域内の一連の文字列からなる命令が有効でなければ(ステップS73で「No」)、CPU50は、「ERROR+CR」という文字列を送信FIFOメモリ53に書き込んでノート型パーソナルコンピュータ33へと返す(ステップS76)。そして、CPU50は、送信FIFOメモリ53のデータが読み出されたことを確認してから(ステップS75)、ステップS70に移る。

【0063】

ステップS75で送信FIFOメモリ53のデータの読み出しを確認するのは、この読み出しが完了する前に、HALT命令が実行され、水晶発振器45が停止されると、この読み出しが不完全な状態で終了する可能性があるためである。

【0064】

ノート型パーソナルコンピュータ33による送信FIFOメモリ53のデータの読み出しは、DTEインターフェース46の割り込み端子がローレベルになると行われる。そして、この割り込み端子のローレベルは、一定バイト数以上のデータが該送信FIFOメモリ53に格納されるか、あるいはロジック部48内のタイマーがタイムアウトするかにより設定される。更に、ロジック部48内のタイマーによる計数は、水晶発振器45からのクロック信号に同期して行われる。従って、送信FIFOメモリ53のデータの読み出しが完了する前に、HALT命令が実行され、水晶発振器45が停止されると、ロジック部48内のタイマーが停止して、DTEインターフェース46の割り込み端子がローレベルに設定されない可能性があり、送信FIFOメモリ53のデータの読み出しが不完全な状態で終了する可能性がある。

【0065】

この様に本実施形態のカード型デバイス30では、クロック信号の供給がなくても、データを受信可能な受信FIFOメモリ52を採用しており、受信FIFOメモリ52にデータが書き込まれ、受信FIFOメモリ52からのライト信号RXRDYがハイレベルになったときに、水晶発振器45を起動して、クロック信号の供給を開始している。従って、受信FIFOメモリ52にデータが書き込まれない限り、水晶発振器45を停止して、クロック信号の供給を停止していることになる。これに伴い、CPU50やロジック部48等の動作も停止され、この結果として、消費電力を十分に低減することができる。

【0066】

尚、本発明は、上記各実施形態に限定されるものではなく、多様に変形することができる。例えば、本発明のカード型デバイスは、PCカードだけではなく、他の種類のカードにも適用することができる。

【0067】

また、PHS無線通信カードの様に無線制御部のタイミングをクロックにより保持しなければならず、クロックを完全に停止することができなくても、受信FIFOメモリにデータが書き込まれていないときに、タイミングを保持する必要がないLSI等の部分へのクロックの供給を停止するだけでも、従来の装置よりも低消費電力化される。

【0068】

【発明の効果】

以上説明した様に本発明によれば、外部の情報端末装置から受信された処理すべきデータがない非受信状態のときに、発振器が停止されて、クロックの供給が中断される。カード型デバイスは、データを受信したときに動作すれば良いので、データの非受信状態のときに発振器を停止させて、クロックの供給を中断し、その動作を中断しても構わない。これにより、発振器の停止による十分な低消費電力化が可能になる。

【0069】

また、外部の情報端末装置から受信された処理すべきデータがない非受信状態のときに、発振器から該カード型デバイスの少なくとも一部に対する動作クロックの供給が停止されて、低消費電力化がなされている。更に、データを受信したときには、インターフェースからの信号に応答して発振器を起動し、該データの処理のためにカード型デバイスの動作を再開している。

【図面の簡単な説明】

【図1】本発明のカード型デバイスの一実施形態を示すブロック図である。

【図2】図1のカード型デバイスにおける水晶発振器を示す回路図である。

【図3】本発明のカード型デバイスの他の実施形態を示すブロック図である。

【図4】図3のカード型デバイスの使用状態を示す図である。

【図5】図3のカード型デバイスによる処理過程を示すフローチャートである。

【図6】図3のカード型デバイスにおける各信号を示すタイミングチャートである。

【図7】従来のカード型デバイスを例示するブロック図である。

【符号の説明】

10,30 カード型デバイス

11,41 LSI

12,42 ROM

13,43 RAM

14,45 水晶発振器

15,46 DTEインターフェース

16 CPU

17 発振制御部

21,52 受信FIFOメモリ

22,53 送信FIFOメモリ

31 ケーブル

32 携帯電話機

33 ノート型パーソナルコンピュータ

44 EEPROM

47 PCMCIAインターフェース

48 ロジック部

49 通信インターフェース

50 CPU

51 発振制御部

【発明の属する技術分野】

本発明は、外部の情報端末装置との間でデータを送受するカード型デバイスに関する。

【0002】

【従来の技術】

この種のカード型デバイスは、PC(Personal Computer)カード、CFカード、モデムカード等であり、ノート型パーソナルコンピュータやPDA(Personal Digital Assistants)等の情報端末装置のスロットに挿入されて用いられる。このカード型デバイスでは、外部の情報端末装置との間でデータを送受するためのインターフェースを備えており、データの送受、演算処理、データの記憶等を行なう。

【0003】

図7に従来のカード型デバイスの一例を示す。このカード型デバイス101は、UART(Universal Asynchronous Receiver Transmitter)である汎用のインターフェース102、LSI103、ROM104、RAM105、及びクロック信号を供給する発振器106等を備えている。LSI103は、シリアルインターフェース107、CPU108、及びクロック制御部109等を含んでいる。

【0004】

UARTのインターフェース102は、データを外部の情報端末装置との間で送受し、受信データをパラレルシリアル変換したり、送信データをシリアルパラレル変換する。CPU108は、シリアルインターフェース107を通じて、データをUARTのインターフェース102との間で送受し、データの処理や、RAM105に対するデータの読み書き等を行なう。

【0005】

一方、この様なカード型デバイスは、携帯型情報端末装置のスロットに挿入されて用いられることが多く、携帯情報端末装置の電源から電力を供給されて動作する。そして、カード型デバイスでは、携帯型情報端末装置の電源の容量が限られることから、消費電流の節減が重要視され、パワーダウンモード等が付与されている。例えば、クロック制御部109は、データの書き込み等の処理が行なわれないときに発振器106からCPU108及び他の論理回路等へのクロックの供給を停止したり、クロックの周波数を低くしたりして、消費電力を低減させている。

【0006】

ただし、カード型デバイスを外部の情報端末装置に接続した状態では、UARTのインターフェース102によるデータの受信及びパラレルシリアル変換が何時でもできる様にするため、UARTのインターフェース102へのクロックの供給を中断することはない。

【0007】

【発明が解決しようとする課題】

ところで、LSIの消費電力は、クロック周波数とクロックが供給される回路規模で決まることから、低消費電力化のためには、発振器を停止させて、クロックの供給を完全に中断することが理想的である。

【0008】

しかしながら、従来は、UARTのインターフェースを用いているので、データを受信する可能性があるときには、クロックをインターフェースに常に供給する必要があり、発振器を停止させることができなかった。

【0009】

従って、発振器を停止させたときの消費電力を考慮するならば、低消費電力化の余地が十分に残っているといえる。

【0010】

そこで、本発明は、上記従来の問題点に鑑みてなされたものであり、発振器の停止による十分な低消費電力化が可能なカード型デバイスを提供することを目的とする。

【0011】

【課題を解決するための手段】

上記課題を解決するために本発明は、外部の情報端末装置との間でデータを送受するカード型デバイスにおいて、外部の情報端末装置から受信された処理すべきデータがない非受信状態を判別する判別手段と、判別手段により非受信状態が判別されたときには、該カード型デバイスに動作クロックを供給する発振器を停止させる発振制御手段とを備えている。

【0012】

この様な構成の本発明によれば、外部の情報端末装置から受信された処理すべきデータがない非受信状態のときに、発振器が停止されて、クロックの供給が中断される。カード型デバイスは、データを受信したときに動作すれば良いので、データの非受信状態のときに発振器を停止させて、クロックの供給を中断し、その動作を中断しても構わない。これにより、発振器の停止による十分な低消費電力化が可能になる。

【0013】

発振器の停止はCPUの制御により行うことができ、これは例えばCPUのHALT命令の実行により制御される。

【0014】

更に、本発明においては、外部の情報端末装置からのデータが受信されると、発振器を起動している。

【0015】

この様にデータが受信されたときに、発振器が起動されれば、データの処理のためにカード型デバイスの動作を再開させることができる。

【0016】

また、本発明においては、発振器が停止された状態で、データを受信するファーストインファーストアウトのインターフェースを備え、発振制御手段は、インターフェースからの信号に応答して発振器を起動している。

【0017】

この様なファーストインファーストアウトのインターフェースを採用すれば、発振器が停止された状態で、データを受信することができる。また、データを受信したときには、インターフェースからの信号に応答して発振器を起動し、該データの処理のためにカード型デバイスの動作を再開することができる。

【0018】

次に、本発明は、外部の情報端末装置との間でデータを送受するカード型デバイスにおいて、該カード型デバイスに動作クロックを供給する発振器が停止された状態で、データを受信するファーストインファーストアウトのインターフェースと、外部の情報端末装置から受信された処理すべきデータがない非受信状態を判別する判別手段と、判別手段により非受信状態が判別されたときには、発振器から該カード型デバイスの少なくとも一部に対する動作クロックの供給を停止させ、インターフェースからの信号に応答して発振器を起動する発振制御手段とを備えている。

【0019】

この様に外部の情報端末装置から受信された処理すべきデータがない非受信状態のときに、発振器から該カード型デバイスの少なくとも一部に対する動作クロックの供給を停止させるだけでも、十分な低消費電力化が可能である。また、データを受信したときには、インターフェースからの信号に応答して発振器を起動し、該データの処理のためにカード型デバイスの動作を再開することができる。

【0020】

【発明の実施の形態】

以下、本発明の実施形態を添付図面を参照して詳細に説明する。

【0021】

図1は、本発明のカード型デバイスの一実施形態を示すブロック図である。本実施形態のカード型デバイス10は、PCカードであって、ノート型パーソナルコンピュータやPDA等の情報端末装置のスロットに挿入されて用いられるものであり、LSI11、ROM12、RAM13、及び水晶発振器14等を備えている。LSI11は、DTEインターフェース15、CPU16、及び発振制御部17等を含んでいる。

【0022】

発振制御部17は、発振イネーブル信号を水晶発振器14に加えて、水晶発振器14を制御する。発振制御部17により発振イネーブル信号がハイレベルにされると、水晶発振器14が起動され、発振制御部17により発振イネーブル信号がローレベルにされると、水晶発振器14が停止される。

【0023】

水晶発振器14は、図2に示す様にクロック信号を発生する水晶振動子14aとナンド回路14bを備えており、発振イネーブル信号がハイレベルのときに、クロック信号を出力して、クロック信号をカード型デバイス10の各所に供給する。また、発振イネーブル信号がローレベルのときに、クロック信号の出力を停止する。

【0024】

CPU16は、DTEインターフェース15を通じて、データを外部の情報端末装置との間で送受し、データの処理やRAM13に対するデータの読み書き等を行なう。

【0025】

DTEインターフェース15は、受信FIFO(First In First Out)メモリ21及び送信FIFOメモリ22を含むパラレルインターフェースであり、外部の情報端末装置との間で送受されるデータを一時的に格納する。また、DTEインターフェース15は、アドレスバス及びデータバスを通じて、外部の情報端末装置に接続され、外部の情報端末装置からのIOWR(書き込み)命令及びIORD(読み出し)命令を受けて制御され、外部の情報端末装置によりデータが受信FIFOメモリ21に書き込まれ、外部の情報端末装置によりデータが送信FIFOメモリ22から読み出される。従って、受信FIFOメモリ21への書き込み及び送信FIFOメモリ22からの読み出しは、水晶発振器14からの動作用のクロック信号とは非同期で行われる。

【0026】

さて、この様な構成において、受信FIFOメモリ21は、データが書き込まれていないときに、ライト信号RXRDYをローレベルに設定する。発振制御部17は、ライト信号RXRDYがローレベルのときに、発振イネーブル信号をローレベルに設定して、水晶発振器14を停止させる。これにより、CPU16や他の論理回路にクロック信号が供給されず、CPU16や他の論理回路の動作が停止される。このとき、カード型デバイス10の消費電力が殆ど無く、パワーダウンモードとなっている。

【0027】

次に、受信FIFOメモリ21は、外部の情報端末装置によりデータが書き込まれて格納されると、ライト信号RXRDYをローレベルからハイレベルに切り換える。発振制御部17は、ライト信号RXRDYがハイレベルになると、発振イネーブル信号をハイレベルに切り換えて、水晶発振器14を起動させる。この水晶発振器14の起動により、動作用のクロック信号の供給が開始される。そして、クロック信号が安定化すると、発振制御部17によりCPU16に対する割り込みがかけられ、CPU16や他の論理回路の動作が開始される。

【0028】

CPU16は、動作状態になると、データを受信FIFOメモリ21から読み出して、このデータをRAM13内のデータ受信バッファ領域に格納する。このとき、受信FIFOメモリ21が空となり、ライト信号RXRDYがローレベルに戻る。

【0029】

引き続いて、CPU16は、データ受信バッファ領域内のデータを処理する。例えば、データ受信バッファ領域内のデータが命令であれば、この命令がCPU16により実行される。

【0030】

仮に、カード型デバイス10がモデムカードであって、「AT+CR(キャリッジリターン)」という文字列(命令)が受信FIFOメモリ21に書き込まれれば、この命令がデータ受信バッファ領域内に転送され、この命令がCPU16により実行されて、「OK+CR」という文字列が送信FIFOメモリ22に書き込まれて外部の情報端末装置へと返される。

【0031】

また、CPU16は、データ受信バッファ領域内のデータが意味不明であれば、新たなデータが受信FIFOメモリ21に書き込まれるのを待機する。そして、新たなデータが受信FIFOメモリ21に書き込まれず、ライト信号RXRDYがローレベルのままで、一定時間が経過する。CPU16は、発振停止信号を発振制御部17に加える。これに応答して発振制御部17は、発振イネーブル信号をローレベルに切り換えて、水晶発振器14を停止させる。これにより、CPU16や他の論理回路の動作が停止されて、パワーダウンモードとなる。

【0032】

以降同様に、新たなデータが受信FIFOメモリ21に書き込まれて格納されると、受信FIFOメモリ21からのライト信号RXRDYがハイレベルとなって、発振制御部17からの発振イネーブル信号がハイレベルとなり、水晶発振器14が起動され、CPU16が割り込みをかけられて動作状態となる。また、新たなデータが受信FIFOメモリ21に書き込まれず、ライト信号RXRDYがローレベルのままで、一定時間が経過すると、発振停止信号が発振制御部17に加えられて、水晶発振器14が停止され、パワーダウンモードとなる。

【0033】

この様に本実施形態のカード型デバイス10では、パワーダウンモードに際し、水晶発振器14を停止させて、CPU16や他の論理回路の動作を停止させているので、消費電力を十分に低減することができる。

【0034】

図3は、本発明のカード型デバイスの他の実施形態を示すブロック図である。また、図4は、本実施形態のカード型デバイスの使用状態を示す図である。

【0035】

本実施形態のカード型デバイス30は、PCカードであり、ケーブル31を介して携帯電話機32に接続され、かつノート型パーソナルコンピュータ33のスロットに挿入されて用いられ、携帯電話機32とノート型パーソナルコンピュータ33間を中継する。

【0036】

カード型デバイス30は、LSI41、ROM42、RAM43、EEPROM44、及び水晶発振器45等を備えている。LSI41は、DTEインターフェース46、PCMCIAインターフェース47、ロジック部48、通信インターフェース49、CPU50、及び発振制御部51等を含んでいる。

【0037】

発振制御部51は、発振イネーブル信号を水晶発振器45に加えて、水晶発振器45を制御する。例えば、ノート型パーソナルコンピュータ33によりデータがDTEインターフェース46の受信FIFOメモリ52に書き込まれたり、携帯電話機32からの着信が通信インターフェース49で検出されたりしたときに、発振制御部51により発振イネーブル信号がハイレベルにされて、水晶発振器45が起動される。また、CPU50からの発振停止信号に応答して、発振制御部51により発振イネーブル信号がローレベルにされて、水晶発振器45が停止される。水晶発振器45は、動作時に、動作用のクロック信号をカード型デバイス30の各所に供給する。

【0038】

また、発振制御部51は、発振イネーブル信号をハイレベルにして、水晶発振器45を起動させた後で、水晶発振器45からのクロック信号を計数し、この計数値が予め設定された値になると、CPU50に対して割り込みをかける。

【0039】

CPU50は、ROM42内のプログラムに従って動作し、DTEインターフェース46を通じて、データをノート型パーソナルコンピュータ33との間で送受し、データの処理やRAM43に対するデータの読み書き等を行なう。また、CPU50は、通信インターフェース49を通じて、データを携帯電話機32との間で送受する。

【0040】

DTEインターフェース46は、受信FIFOメモリ52及び送信FIFOメモリ53を含むパラレルインターフェースであり、ノート型パーソナルコンピュータ33との間で送受されるデータを一時的に格納する。また、DTEインターフェース46は、アドレスバス及びデータバスを通じて、ノート型パーソナルコンピュータ33に接続され、ノート型パーソナルコンピュータ33からのIOWR命令及びIORD命令を受けて制御され、データを受信FIFOメモリ52に書き込まれたり、データを送信FIFOメモリ53から読み出されたりする。受信FIFOメモリ52への書き込み及び送信FIFOメモリ53からの読み出しは、水晶発振器45からの動作用のクロック信号とは非同期で行われる。また、ノート型パーソナルコンピュータ33は、受信FIFOメモリ52が満杯になるまで、データを受信FIFOメモリ52に書き込むことができる。

【0041】

PCMCIAインターフェース47は、このカード型デバイス30をI/Oカードとして動作させるためのアトリビュートメモリやコンフィグレーションレジスタ等からなる。

【0042】

通信インターフェース49は、携帯電話機32に対する発着信や切断の制御を行なうシリアルインターフェースやデータ送受信のための回路等を含む。

【0043】

ロジック部48は、タイマーやメモリの管理等を行なう。

【0044】

EEPROM44は、読み書き可能なROMであり、このカード型デバイス30の使用者により設定されたPCカードの情報を記憶するSレジスタを含む。

【0045】

次に、図5のフローチャート及び図6のタイミングチャートを参照しつつ、カード型デバイス30の動作の一例を説明する。

【0046】

まず、カード型デバイス30の起動時には(ステップS61)、HALT命令がCPU50により実行されて、ホールド状態が設定される(ステップS62)。ホールド状態とは、カード型デバイス30の動作を停止して、電源を切ることが可能な状態のことである。ただし、ノート型パーソナルコンピュータ33による受信FIFOメモリ52及び送信FIFOメモリ53の読み出し及び書き込み、及び通信インターフェース49による着信検出は可能である。

【0047】

また、このときには、発振制御部51からの発振イネーブル信号がローレベルであり、水晶発振器45が停止されている。このため、CPU50やロジック部48等にクロック信号が供給されず、CPU50やロジック部48等の動作が停止される。このとき、カード型デバイス30の消費電力が殆ど無く、パワーダウンモードとなる。

【0048】

このパワーダウンモードの状態で、受信FIFOメモリ52は、ノート型パーソナルコンピュータ33によりデータがに書き込まれると、ライト信号RXRDYをローレベルからハイレベルに切り換える。あるいは、通信インターフェース49は、携帯電話機32からの着信を検出すると、発振制御部51に対して割り込みをかける。発振制御部51は、ライト信号RXRDYがハイレベルになったり、通信インターフェース49により割り込みがかけられたりすると、発振イネーブル信号をハイレベルにして、水晶発振器45を起動し、動作用のクロック信号をカード型デバイス30の各所に供給する。そして、発振制御部51は、水晶発振器45からのクロック信号を計数し、この計数値が予め設定された値になると、つまり一定時間が経過すると、CPU50に対して割り込みをかける(ステップS63)。この一定時間の待機により、クロック信号の安定化の後に、CPU50の動作が開始される。

【0049】

CPU50は、割り込みを受けると、この割り込みの要因を判定する(ステップS64)。そして、この割り込みの要因が携帯電話機32からの着信であれば(ステップS65で「No」)、CPU50は、HALT命令を解除してから、着信に応じた処理を行なう(ステップS66)。例えば、CPU50は、「RING」という文字列を送信FIFOメモリ53に書き込む。この「RING」という文字列は、ノート型パーソナルコンピュータ33により読み出される。この後、CPU50は、発振停止信号を発振制御部51に加えてから、HALT命令を実行して、パワーダウン状態を再び設定する(ステップS62)。発振制御部51は、発振停止信号に応答して発振イネーブル信号をローレベルに切り換え、水晶発振器45を停止させる。これにより、CPU50やロジック部48等の動作が停止されて、パワーダウンモードとなる。

【0050】

また、割り込みの要因がノート型パーソナルコンピュータ33から受信FIFOメモリ52へのデータの書き込みであれば(ステップS65で「Yes」)、CPU50は、HALT命令を解除してから、データを受信FIFOメモリ52から読み出す(ステップS67)。

【0051】

例えば、図6のタイミングチャートに示す様に時点t1で、ノート型パーソナルコンピュータ33によりデータが受信FIFOメモリ52に書き込まれて、受信FIFOメモリ52からのライト信号RXRDYがハイレベルになると、発振制御部51により発振イネーブル信号がハイレベルにされ、水晶発振器45が起動されて、クロック信号の供給が開始され、一定時間が経過した時点t2で、発振制御部51によりCPU50に対する割り込みがかけられ(ステップS63)、各ステップS64,65が行われ、パワーダウン状態が解除されて、データが受信FIFOメモリ52から読み出される(ステップS67)。

【0052】

そして、CPU50は、受信FIFOメモリ52から読み出したデータが「CR」という文字列であるか否かを判定する(ステップS68)。「CR」という文字列は、1つの命令の最後に付けられる。従って、「CR」という文字列が受信されなければ、引き続く次の文字列が受信されることになり、また「CR」という文字列が受信されれば、1つの命令の受信が完了したことになる。

【0053】

ここで、読み出したデータが「CR」でなければ(ステップS68で「No」)、CPU50は、この読み出したデータをRAM43内のデータ受信バッファ領域に格納してから(ステップS69)、一定時間待機する(ステップS70)。この待機中に、ノート型パーソナルコンピュータ33により新たなデータが受信FIFOメモリ52に書き込まれなければ(ステップS71で「No」)、CPU50は、発振停止信号を発振制御部51に加えてから、HALT命令を実行して、パワーダウン状態を再び設定する(ステップS62)。これにより、水晶発振器45が停止されて、CPU50やロジック部48等の動作が停止され、パワーダウンモードとなる。

【0054】

例えば、図6のタイミングチャートに示す様にデータが受信FIFOメモリ52から読み出されてRAM43内のデータ受信バッファ領域に格納されてから、更に一定時間待機した時点t3で(ステップS70)、新たなデータが受信FIFOメモリ52に書き込まれなければ(ステップS71で「No」)、HALT命令が実行される(ステップS62)。

【0055】

また、一定時間の待機中に(ステップS70)、ノート型パーソナルコンピュータ33により新たなデータが受信FIFOメモリ52に書き込まれれば(ステップS71で「Yes」)、ステップS67に戻る。

【0056】

例えば、図6のタイミングチャートに示す様に時点t4で、ノート型パーソナルコンピュータ33によりデータが受信FIFOメモリ52に書き込まれ、この後にデータが受信FIFOメモリ52から読み出されてRAM43内のデータ受信バッファ領域に格納され、引き続いて一定時間が経過するまでに(ステップS70)、新たなデータが受信FIFOメモリ52に書き込まれれば(ステップS71で「Yes」)、HALT命令が実行されずに、ステップS67に戻る。

【0057】

従って、ノート型パーソナルコンピュータ33によるデータの書き込み間隔が一定時間以内であれば、HALT命令が実行されることなく、データが受信FIFOメモリ52から順次読み出されてRAM43内のデータ受信バッファ領域に逐次格納される。また、ノート型パーソナルコンピュータ33によるデータの書き込み間隔が一定時間を超えると、その度にHALT命令が実行されて、パワーダウンモードとなり、ノート型パーソナルコンピュータ33による新たなデータの書き込みが待機されることになる。

【0058】

ステップS70で一定時間待機するのは、ステップS62に頻繁に戻って、その度にHALT命令が実行され、水晶発振器45が停止されることを防止するためである。水晶発振器45の起動に際しては、クロック信号が安定化するまでの一定時間を待機する必要があることから、仮に水晶発振器45が頻繁に停止されると、待機時間が長くなり、一連のデータを受信して処理するための時間も長くなってしまう。

【0059】

こうしてノート型パーソナルコンピュータ33による受信FIFOメモリ52へのデータの書き込み、及び受信FIFOメモリ52からのデータの読み出しが繰り返され、1つの命令の最後に付けられる「CR」という文字列の書き込みと読み出しも行われる。

【0060】

このとき、CPU50は、受信FIFOメモリ52から読み出したデータが「CR」という文字列であることから(ステップS68で「Yes」)、この文字列をRAM43内のデータ受信バッファ領域に格納してから、データ受信バッファ領域内の一連の文字列を読み出して(ステップS72)、この一連の文字列からなる命令が有効であるか否かを判定する(ステップS73)。

【0061】

そして、データ受信バッファ領域内の一連の文字列からなる命令が有効であれば(ステップS73で「Yes」)、CPU50は、この命令を実行する。例えば、一連の文字列が「ATS0?+CR」という有効な命令であれば、この命令を実行する(ステップS74)。この「ATS0?+CR」という命令は、EEPROM44内のSレジスタの情報の問い合わせを意味する。このため、CPU50は、Sレジスタの情報を送信FIFOメモリ53に書き込んでノート型パーソナルコンピュータ33へと返す。更に、CPU50は、送信FIFOメモリ53のデータが読み出されたことを確認してから(ステップS75)、ステップS70に移る。

【0062】

また、データ受信バッファ領域内の一連の文字列からなる命令が有効でなければ(ステップS73で「No」)、CPU50は、「ERROR+CR」という文字列を送信FIFOメモリ53に書き込んでノート型パーソナルコンピュータ33へと返す(ステップS76)。そして、CPU50は、送信FIFOメモリ53のデータが読み出されたことを確認してから(ステップS75)、ステップS70に移る。

【0063】

ステップS75で送信FIFOメモリ53のデータの読み出しを確認するのは、この読み出しが完了する前に、HALT命令が実行され、水晶発振器45が停止されると、この読み出しが不完全な状態で終了する可能性があるためである。

【0064】

ノート型パーソナルコンピュータ33による送信FIFOメモリ53のデータの読み出しは、DTEインターフェース46の割り込み端子がローレベルになると行われる。そして、この割り込み端子のローレベルは、一定バイト数以上のデータが該送信FIFOメモリ53に格納されるか、あるいはロジック部48内のタイマーがタイムアウトするかにより設定される。更に、ロジック部48内のタイマーによる計数は、水晶発振器45からのクロック信号に同期して行われる。従って、送信FIFOメモリ53のデータの読み出しが完了する前に、HALT命令が実行され、水晶発振器45が停止されると、ロジック部48内のタイマーが停止して、DTEインターフェース46の割り込み端子がローレベルに設定されない可能性があり、送信FIFOメモリ53のデータの読み出しが不完全な状態で終了する可能性がある。

【0065】

この様に本実施形態のカード型デバイス30では、クロック信号の供給がなくても、データを受信可能な受信FIFOメモリ52を採用しており、受信FIFOメモリ52にデータが書き込まれ、受信FIFOメモリ52からのライト信号RXRDYがハイレベルになったときに、水晶発振器45を起動して、クロック信号の供給を開始している。従って、受信FIFOメモリ52にデータが書き込まれない限り、水晶発振器45を停止して、クロック信号の供給を停止していることになる。これに伴い、CPU50やロジック部48等の動作も停止され、この結果として、消費電力を十分に低減することができる。

【0066】

尚、本発明は、上記各実施形態に限定されるものではなく、多様に変形することができる。例えば、本発明のカード型デバイスは、PCカードだけではなく、他の種類のカードにも適用することができる。

【0067】

また、PHS無線通信カードの様に無線制御部のタイミングをクロックにより保持しなければならず、クロックを完全に停止することができなくても、受信FIFOメモリにデータが書き込まれていないときに、タイミングを保持する必要がないLSI等の部分へのクロックの供給を停止するだけでも、従来の装置よりも低消費電力化される。

【0068】

【発明の効果】

以上説明した様に本発明によれば、外部の情報端末装置から受信された処理すべきデータがない非受信状態のときに、発振器が停止されて、クロックの供給が中断される。カード型デバイスは、データを受信したときに動作すれば良いので、データの非受信状態のときに発振器を停止させて、クロックの供給を中断し、その動作を中断しても構わない。これにより、発振器の停止による十分な低消費電力化が可能になる。

【0069】

また、外部の情報端末装置から受信された処理すべきデータがない非受信状態のときに、発振器から該カード型デバイスの少なくとも一部に対する動作クロックの供給が停止されて、低消費電力化がなされている。更に、データを受信したときには、インターフェースからの信号に応答して発振器を起動し、該データの処理のためにカード型デバイスの動作を再開している。

【図面の簡単な説明】

【図1】本発明のカード型デバイスの一実施形態を示すブロック図である。

【図2】図1のカード型デバイスにおける水晶発振器を示す回路図である。

【図3】本発明のカード型デバイスの他の実施形態を示すブロック図である。

【図4】図3のカード型デバイスの使用状態を示す図である。

【図5】図3のカード型デバイスによる処理過程を示すフローチャートである。

【図6】図3のカード型デバイスにおける各信号を示すタイミングチャートである。

【図7】従来のカード型デバイスを例示するブロック図である。

【符号の説明】

10,30 カード型デバイス

11,41 LSI

12,42 ROM

13,43 RAM

14,45 水晶発振器

15,46 DTEインターフェース

16 CPU

17 発振制御部

21,52 受信FIFOメモリ

22,53 送信FIFOメモリ

31 ケーブル

32 携帯電話機

33 ノート型パーソナルコンピュータ

44 EEPROM

47 PCMCIAインターフェース

48 ロジック部

49 通信インターフェース

50 CPU

51 発振制御部

Claims (4)

- 外部の情報端末装置との間でデータを送受するカード型デバイスにおいて、

外部の情報端末装置から受信された処理すべきデータがない非受信状態を判別する判別手段と、

判別手段により非受信状態が判別されたときには、該カード型デバイスに動作クロックを供給する発振器を停止させる発振制御手段と

を備えることを特徴とするカード型デバイス。 - 発振制御手段は、外部の情報端末装置からのデータが受信されると、発振器を起動することを特徴とする請求項1に記載のカード型デバイス。

- 発振器が停止された状態で、データを受信するファーストインファーストアウトのインターフェースを備え、

発振制御手段は、インターフェースからの信号に応答して発振器を起動することを特徴とする請求項2に記載のカード型デバイス。 - 外部の情報端末装置との間でデータを送受するカード型デバイスにおいて、

該カード型デバイスに動作クロックを供給する発振器が停止された状態で、データを受信するファーストインファーストアウトのインターフェースと、

外部の情報端末装置から受信された処理すべきデータがない非受信状態を判別する判別手段と、

判別手段により非受信状態が判別されたときには、発振器から該カード型デバイスの少なくとも一部に対する動作クロックの供給を停止させ、インターフェースからの信号に応答して発振器を起動する発振制御手段と

を備えることを特徴とするカード型デバイス。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003038365A JP2004246793A (ja) | 2003-02-17 | 2003-02-17 | カード型デバイス |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003038365A JP2004246793A (ja) | 2003-02-17 | 2003-02-17 | カード型デバイス |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2004246793A true JP2004246793A (ja) | 2004-09-02 |

Family

ID=33022910

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003038365A Pending JP2004246793A (ja) | 2003-02-17 | 2003-02-17 | カード型デバイス |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2004246793A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007058347A (ja) * | 2005-08-22 | 2007-03-08 | Kenwood Corp | 受信装置及びその制御方法 |

| JP2009182622A (ja) * | 2008-01-30 | 2009-08-13 | Nippon Dempa Kogyo Co Ltd | 電子カード用の温度補償発振器 |

| JP2012009011A (ja) * | 2010-05-21 | 2012-01-12 | Renesas Electronics Corp | マイクロコントローラ及びその制御方法 |

| JP2015135700A (ja) * | 2010-05-21 | 2015-07-27 | ルネサスエレクトロニクス株式会社 | マイクロコントローラ |

-

2003

- 2003-02-17 JP JP2003038365A patent/JP2004246793A/ja active Pending

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007058347A (ja) * | 2005-08-22 | 2007-03-08 | Kenwood Corp | 受信装置及びその制御方法 |

| JP2009182622A (ja) * | 2008-01-30 | 2009-08-13 | Nippon Dempa Kogyo Co Ltd | 電子カード用の温度補償発振器 |

| JP2012009011A (ja) * | 2010-05-21 | 2012-01-12 | Renesas Electronics Corp | マイクロコントローラ及びその制御方法 |

| US8751842B2 (en) | 2010-05-21 | 2014-06-10 | Renesas Electronics Corporation | Microcontroller and method of controlling the same |

| JP2015135700A (ja) * | 2010-05-21 | 2015-07-27 | ルネサスエレクトロニクス株式会社 | マイクロコントローラ |

| US9342097B2 (en) | 2010-05-21 | 2016-05-17 | Renesas Electronics Corporation | Microcontroller and method of controlling the same |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3923715B2 (ja) | メモリカード | |

| JP5801436B2 (ja) | 集積化埋込型フラッシュ及びsramメモリを有する移動通信装置 | |

| JP2842750B2 (ja) | Icカード | |

| US20090204834A1 (en) | System and method for using inputs as wake signals | |

| JP5388864B2 (ja) | クロック制御装置、クロック制御方法、クロック制御プログラム及び集積回路 | |

| EP1423789A2 (en) | Data processing system having an on-chip background debug system and method therefor | |

| JP2007536667A (ja) | 集積回路を備えるモバイル装置およびそのような回路をパワーダウンする方法 | |

| JPH08202469A (ja) | ユニバーサル非同期送受信回路を備えたマイクロ・コントローラユニット | |

| JP3552213B2 (ja) | Sdメモリカードホストコントローラ及びクロック制御方法 | |

| US7373134B2 (en) | Multiple-CPU portable terminal with communication function and control method | |

| JP3070527B2 (ja) | 無線携帯端末 | |

| WO2023035427A1 (zh) | 基于fifo存储器的信息生成方法、装置、设备及介质 | |

| CN100476693C (zh) | 处理器的空闲状态 | |

| JP2004246793A (ja) | カード型デバイス | |

| US5428765A (en) | Method and apparatus for disabling and restarting clocks | |

| JP3558404B2 (ja) | データバッファ | |

| CN1937075B (zh) | 数据传送操作完成检测电路和包含其的半导体存储器件 | |

| JP2003023469A (ja) | 通信端末装置およびそのデータ送信方法 | |

| US6751689B2 (en) | Interface circuit and method for transmitting data between a serial interface and a processor | |

| JP2010055265A (ja) | システムlsi、システムlsiの制御方法、プログラム、及び記憶媒体 | |

| JP2003256791A (ja) | Pcカード装置 | |

| US20040003145A1 (en) | Method and apparatus to transfer information | |

| JP4057360B2 (ja) | 多機能icカード及びその制御方法 | |

| JPH02196390A (ja) | Icカード | |

| KR100501847B1 (ko) | 유사 이중 포트 메모리 제어 장치 및 그 제어 방법 |