JP2004040711A - A/dコンバータ - Google Patents

A/dコンバータ Download PDFInfo

- Publication number

- JP2004040711A JP2004040711A JP2002198636A JP2002198636A JP2004040711A JP 2004040711 A JP2004040711 A JP 2004040711A JP 2002198636 A JP2002198636 A JP 2002198636A JP 2002198636 A JP2002198636 A JP 2002198636A JP 2004040711 A JP2004040711 A JP 2004040711A

- Authority

- JP

- Japan

- Prior art keywords

- group

- comparator

- outputs

- converter

- comparators

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Analogue/Digital Conversion (AREA)

Abstract

【解決手段】複数個のグループに分割したコンパレータのうちから比較電位と入力電圧の比較結果が反転するコンパレータを含むグループを除くグループを順次選択するスイッチマトリクス211と、選択されたグループの全てのコンパレータの出力が同一であることを検出する排他的論理和回路212と、選択されたグループの全てのコンパレータの出力が同一でないことが検出された場合に当該グループのコンパレータを不良と判定するロジック回路213とを備える。

【選択図】 図2

Description

【発明の属する技術分野】

本発明は内蔵コンパレータの不良判定を行うテスト機能を備えたA/Dコンバータに関する。

【0002】

【従来の技術】

図5は一般的なA/Dコンバータのファンクションテストを行う従来の技術を説明するブロック図である。図5において、A/Dコンバータ500のアナログ回路には、アナログ電源端子501を介して第1の電源511から電位AVDDが供給される。また、A/Dコンバータ500のデジタル回路にはデジタル電源端子502を介して第2の電源512からDVDDが供給される。A/Dコンバータ500内のラダー抵抗において、最高の基準電位が与えられる点には、上部基準電源端子503を介して第3の電源513から電位VRTが与えられ、最低の基準電位が与えられる点には、下部基準電源端子504を介して第4の電源514から電位VRBが与えられる。

【0003】

さらに図5において、A/Dコンバータ500にはアナログ電圧入力端子505を介してアナログソース源515からアナログ入力電圧VINが供給される。A/Dコンバータ500から得られるデジタルコード507は外部に出力され、これがLSIテスタに取り込まれて検査が行われる。ここではA/Dコンバータ500は8ビットのデジタルコード507を出力するものとする。また、A/Dコンバータ500は接地508に接続され、さらに、クロック入力端子506を介してクロック源516からA/Dコンバータのサンプリングクロックが入力される。

【0004】

通常の検査方法では、まず、第1から第4までの電源を投入し、アナログ電源端子501、デジタル電源端子502、上部基準電源端子503、下部基準電源端子504に、それぞれAVDD、DVDD、VRT、VRBを印加する。次に、クロック源516からサンプリングクロックをクロック入力端子506に印加する。また、アナログソース源515から出力されるアナログ入力電圧VINの分解能を別途設定しておき、アナログ入力電圧VINを設定された分解能ずつステップ状に増加させてアナログ入力電圧端子505に供給する。このようにして出力されるデジタルコード507をLSIテスタに取り込み、あらかじめプログラムされた処理により良否判定が行われる。

【0005】

【発明が解決しようとする課題】

nビットのA/Dコンバータには2n―1個のコンパレータが内蔵され、その出力結果を後段に配置したロジック回路でnビットのデジタルコードに変換して出力する。しかし、このロジック回路の構成上、ある1つもしくは複数のコンパレータが誤った比較結果を出力してもミスコードにならないケースが存在する。

【0006】

ここでは説明の便宜上3ビットのA/Dコンバータを例にとりn=3とする。そのためコンパレータの数は7個となる。コンパレータに入力するVINと比較する電圧値がVRTとVRBの間のどこに位置するかにより、それぞれのコンパレータの出力が決まる。すなわち、比較電圧値がVINとVRTの間に位置するコンパレータは1を出力し、VINとVRBの間に位置するコンパレータは0を出力する。

【0007】

図6はA/Dコンバータの出力をデジタルコードに変換する回路を説明する回路図である。この回路では、上記7個のコンパレータの出力が1から0に変化する点を後段のロジック回路によって演算し、3ビットのデジタルコード出力を得る。

【0008】

図6において、7個のコンパレータの出力C6〜C0に加えて、比較電圧がVRTに相当しC6の上位に位置付けられる信号overと、比較電圧がVRBに相当しC0の下位に位置付けられる信号underの合計9本の信号が8個の2入力排他的論理和回路601に入力する。

【0009】

排他的論理和回路601はコンパレータ出力の変化点を検出するための回路であり、互いに隣り合う位置の2つの信号をそれぞれ入力し、入力の不一致を示す信号E7〜E0を出力する。論理和回路602は排他的論理和回路601の出力E7〜E0をエンコードして3ビットのデジタルコードを出力する。

【0010】

例えば、仮にoverの比較出力信号が1となり、C6からunderまでの比較出力信号が0となった場合は、排他的論理和回路601の出力E7が1となりエンコードされた出力は111となる。

【0011】

ここで、仮にVINとVRBの間に位置付けられて全て0を出力するはずのコンパレータの中に1を出力したコンパレータが存在したとすると、排他的論理和回路601の出力のE6からE0のうちで1になるものがあるが、出力されるデジタルコードは111で結果は変わらない。従来のテストではこのような不良を検出できない問題があり、このような不良を検出するためには高価なアナログテストシステムを用いる必要があった。

【0012】

本発明は上記従来の問題点を解決するもので、A/Dコンバータに内蔵されるコンパレータが誤った比較結果を出力した場合に、高価なアナログテストシステムを用いずに、これを検出して不良判定を行うことができる簡易なテスト機能を有するA/Dコンバータを提供することを目的とする。

【0013】

【課題を解決するための手段】

この課題を解決するために、本発明の請求項1に係るA/Dコンバータは、上部基準電位と下部基準電位から生成される比較電位を入力電圧と比較するコンパレータ群を内蔵するA/Dコンバータであって、複数個のグループに分割した前記コンパレータ群のうち前記比較電位と入力電圧の比較結果が反転するコンパレータを含むグループを除くグループを順次選択するグループ選択手段(スイッチマトリックス211)と、前記グループ選択手段により選択されたグループの全てのコンパレータの出力が同一であることを検出するグループ判定手段(排他的論理和回路212)と、前記グループ判定手段において選択されたグループの全てのコンパレータの出力が同一でないことが検出された場合に当該グループのコンパレータを不良と判定する不良判定手段(ロジック回路213)とを備えたものである。

【0014】

上記構成によれば、グループ選択手段によりコンパレータを複数個のグループに分割し、グループ判定手段により比較結果が反転するコンパレータを含むグループ以外のグループについて、選択されたグループの全てのコンパレータの出力が同一であるか否かに応じて当該グループの良否を判定できるので、比較的分解能の荒いアナログ入力電圧を与えるだけでコンパレータグループの不良を判定することができる。

【0015】

本発明の請求項2に係るA/Dコンバータは、請求項1記載のA/Dコンバータにおいて、前記グループ判定手段は、選択されたそれぞれのグループに含まれる個々のコンパレータの出力を順次選択する手段と、この順次選択された個々のコンパレータの出力が全て特定の値であることを検出する手段とから構成されるものである。

【0016】

上記構成によれば、選択されたグループにおける個々のコンパレータの出力を順次選択して特定の値であるか否かを確認することができるので、前記グループ判定手段を容易に実現することができ、比較的分解能の荒いアナログ入力電圧を与えるだけでコンパレータグループの不良を判定することができる。

【0017】

本発明の請求項3に係るA/Dコンバータは、請求項1記載のA/Dコンバータにおいて、前記グループ判定手段は、選択されたそれぞれのグループに含まれる全てのコンパレータの出力を加算する手段と、この加算手段により加算された値が前記グループ選択手段により選択されたグループに含まれるコンパレータ数と一致するかまたは0であることを検出する手段とから構成されるものである。

【0018】

上記構成によれば、選択されたグループに含まれる全てのコンパレータの出力の加算値が特定の値であるか否かを確認することができるので、前記グループ判定手段を容易に実現することができ、比較的分解能の荒いアナログ入力電圧を与えるだけでコンパレータグループの不良を判定することができる。

【0019】

本発明の請求項4に係るA/Dコンバータは、上部基準電位と下部基準電位から生成される比較電位を入力電圧と比較するコンパレータ群を内蔵するA/Dコンバータであって、前記コンパレータ群の全ての出力を一時記憶する手段と、あらかじめ設定した値を保持する比較テープルと、一時記憶されたコンパレータの出力を比較テープルに保持された設定値と比較する手段とを具備するものである。

【0020】

上記構成によれば、一時記憶されたコンパレータの出力を比較テープルに保持された設定値と比較することができるので、比較的分解能の荒いアナログ入力電圧を与えるだけでコンパレータグループの不良を判定することができる。

【0021】

【発明の実施の形態】

以下、本発明の実施の形態について図面を参照しながら説明する。図1は本発明の実施の形態に係るA/Dコンバータの構成例を示すブロック図である。図1の構成例においては、説明の便宜のためA/Dコンバータは8ビットとしている。

【0022】

図1において、A/Dコンバータのアナログ回路にはアナログ電源端子101を介して電位AVDDが、デジタル回路にはデジタル電源端子102を介してDVDDが、A/Dコンバータの最高の基準電位が与えられる点には上部基準電源端子103を介して電位VRTが、最低の基準電位が与えられる点には下部基準電源端子104を介して電位VRBがそれぞれ供給される。また、A/Dコンバータにはアナログ電圧入力端子105を介してアナログ入力電圧VINが入力される。

【0023】

A/Dコンバータの内部には、VRTとVRBから255段階の比較電圧を発生するラダー抵抗111と、255個のコンパレータ群112と、コンパレータ群の出力を変換してデジタルコード107を出力するエンコーダ113を備え、さらに、A/Dコンバータのコンパレータ出力の不良判定を行い不良判定信号109を出力する不良判定ロジック回路114を備えている。

【0024】

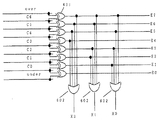

図2は本発明の実施の形態1に係る、A/Dコンバータに内蔵されるコンパレータの不良判定を行う不良判定ロジック回路の構成を示す回路図である。図2において、255本のコンパレータ出力201は、スイッチマトリクス211の前段によって32本ずつ8つのグループに分割され、分割された32本ずつのコンパレータ出力は、さらにスイッチマトリクス211の後段によって1本ずつ選択される。スイッチマトリクスの出力202は排他的論理和回路212で1または0と比較され、その出力は不良判定を行うロジック回路213に入力する。

【0025】

アナログ電圧入力端子105にあらかじめ設定されたアナログ入力電圧VINが入力されると、これがコンパレータ群112においてラダー抵抗111が発生する255段階の比較電圧と比較され、255本のコンパレータ出力201がスイッチマトリクス211に入力される。スイッチマトリクス211は上位から順にコンパレータグループを選択し、選択されたコンパレータグループの出力に対応してロジック回路213が排他的論理和回路212の比較入力を決定する。

【0026】

ここで、仮に入力されたアナログ入力電圧VINが、コンパレータグループの上位5グループまでは全て1、下位の2グループは全て0、上位から6番目のグループに変化点が存在するような値であったとする。スイッチマトリクス211は上位のコンパレータグループから順に選択していき、出力は排他的論理和回路212で比較入力と比較される。このとき上位5グループまでは排他的論理和回路212の比較入力は1に固定される。

【0027】

上位5グループまで比較した後、変化点の存在する6番目のグループをとばし、下位の2グループを選択する。このとき排他的論理和回路212の比較入力は0に固定される。このようにして、排他的論理和回路212の出力が常に0となるようにスイッチマトリクス211は動作し、ロジック回路213は排他的論理和回路212の出力に1が検出されたときに不良判定信号203を出力する。

【0028】

コンパレータグループのいずれか1つのグループに変化点が存在するようにアナログ入力電圧VINを設定して、上述した動作を8回行うことにより、比較的分解能の荒いアナログ入力電圧をVINに与えるだけで、8個のコンパレータグループの不良を判定する簡易なテストが可能となる。

【0029】

図3は本発明の実施の形態2に係る、A/Dコンバータに内蔵されるコンパレータの不良判定を行う不良判定ロジック回路の構成を示す回路図である。図3において、255本のコンパレータ出力301は、スイッチマトリクス311によって32本ずつ8つのグループに分割され、上位のグループから順に選択された1グループのコンパレータ出力がスイッチマトリクスの出力302として後段の加算器312に入力する。加算器312は入力した32本のコンパレータ出力を加算する。

【0030】

ここで、仮に入力されたアナログ入力電圧VINが、コンパレータグループの上位5グループまでは全て1、下位の2グループは全て0、上位から6番目のグループに変化点が存在するような値であったとすると、上位5グループまでの加算結果は常に32となり、下位2グループの加算結果は常に0となる。このようにして、変化点が存在するグループを除くグループについて、加算器312の出力に32か0でない値が検出されたときにロジック回路313は不良判定信号303を出力する。

【0031】

コンパレータグループのいずれか1つのグループに変化点が存在するようにアナログ入力電圧VINを設定して、上述した動作を8回行うことにより、比較的分解能の荒いアナログ入力電圧をVINに与えるだけで、8個のコンパレータグループの不良を判定する簡易なテストが可能となる。

【0032】

図4は本発明の実施の形態3に係る、A/Dコンバータに内蔵されるコンパレータの不良判定を行う不良判定ロジック回路の構成を示す回路図である。図4において、コンパレータの不良判定を行うロジック回路は、フリップフロップ群411と、あらかじめ設定される比較テーブル412を有するロジック回路413で構成される。

【0033】

フリップフロップ群411はクロック入力端子402から与えられるA/Dコンバータのサンプリングクロックで動作し、255本のコンパレータ出力401を記憶する。比較テーブル412は最上位から適当な箇所までが全て1、それ以下最下位までが全て0となるように構成され、1と0の変化点を変えたものを数種類備える。また変化点の誤差を考慮し、比較テーブル412の変化点部分は一定の範囲で1でも0でも良いように構成される。

【0034】

A/Dコンバータのテストにおいては、比較テーブル412の設定に対応する数種類のアナログ入力電圧VINを入力し、255本のコンパレータ出力401をフリップフロップ群411に記憶する。次に、ロジック回路413がフリップフロップ群411の出力を比較テーブル412に設定された値と比較し、不一致を検出すると不良判定信号403を出力する。

【0035】

このように、適当な変化点が存在するような比較テーブルの設定値を数種類用意し、これに対応するアナログ入力電圧VINをA/Dコンバータに印加し、コンパレータ出力を比較テーブルの設定値と比較することにより、比較的分解能の荒いアナログ入力電圧をVINに与えるだけで、コンパレータの不良を判定する簡易なテストが可能となる。

【0036】

【発明の効果】

以上説明したように、本発明によれば、グループ選択手段によりコンパレータを複数個のグループに分割し、グループ判定手段により比較結果が反転するコンパレータを含むグループ以外のグループについて、全てのコンパレータの出力が同一であるか否かに応じて当該グループの良否を判定できるので、比較的分解能の荒いアナログ入力電圧を与えるだけでコンパレータグループの不良を判定することができる。

【0037】

さらに本発明によれば、一時記憶されたコンパレータの出力を比較テープルに保持された設定値と比較することができるので、比較的分解能の荒いアナログ入力電圧を与えるだけでコンパレータグループの不良を判定することができる。

【0038】

したがって本発明によれば、高い入力電圧分解能を持つ高価なアナログテストシステムを必要とせずに、安価なロジックテストシステムを用いて簡易なA/Dコンバータのテストを行うことが可能となり、またプローブ検査時にテストを実施することも可能となる。

【0039】

このように本発明によれば、安価なロジックテストシステムを用いてプローブ検査時に本発明による簡易テストを実施し、詳細なテストは高価なアナログテストシステムを用いてファイナル検査にて実施する方法を採用すれば、テストコストの削減およびファイナル検査での歩留向上に効果を発揮することができる。

【図面の簡単な説明】

【図1】本発明の実施の形態に係るA/Dコンバータの構成例を示すブロック図。

【図2】本発明の実施の形態1に係る、A/Dコンバータに内蔵されるコンパレータの不良判定ロジック回路の構成を示す回路図。

【図3】本発明の実施の形態2に係る、A/Dコンバータに内蔵されるコンパレータの不良判定ロジック回路の構成を示す回路図。

【図4】本発明の実施の形態3に係る、A/Dコンバータに内蔵されるコンパレータの不良判定ロジック回路の構成を示す回路図。

【図5】従来の一般的なA/Dコンバータのファンクションテストを説明するブロック図。

【図6】従来のA/Dコンバータにおけるコンパレータの出力をデジタルコードに変換する回路図。

【符号の説明】

101、501 アナログ電源端子

102、502 デジタル電源端子

103、503 上部基準電源端子

104、504 下部基準電源端子

105、505 アナログ入力電圧端子

107、507 デジタルコード

109、203、303、403 不良判定信号

111 ラダー抵抗

112 コンパレータ群

113 エンコーダ

114 不良判定ロジック回路

201、301、401 コンパレータ出力 202、302 スイッチマトリクスの出力

211、311 スイッチマトリクス

212、601 排他的論理和回路

213、313、413 ロジック回路

312 加算器

402、506 クロック入力端子

411 フリップフロップ

412 比較テーブル

500 A/Dコンバータ

508 接地

511、512、513、514 電源

515 アナログソース源

516 クロック源

602 論理和回路

Claims (4)

- 上部基準電位と下部基準電位から生成される比較電位を入力電圧と比較するコンパレータ群を内蔵するA/Dコンバータであって、

複数個のグループに分割した前記コンパレータ群のうち前記比較電位と入力電圧の比較結果が反転するコンパレータを含むグループを除くグループを順次選択するグループ選択手段と、

前記グループ選択手段により選択されたグループの全てのコンパレータの出力が同一であることを検出するグループ判定手段と、

前記グループ判定手段において選択されたグループの全てのコンパレータの出力が同一でないことが検出された場合に当該グループのコンパレータを不良と判定する不良判定手段と、

を具備したことを特徴とするA/Dコンバータ。 - 前記グループ判定手段は、前記順次選択されたそれぞれのグループに含まれる個々のコンパレータの出力を順次選択する手段と、前記順次選択された個々のコンパレータの出力が全て特定の値であることを検出する手段と、から構成されることを特徴とする請求項1記載のA/Dコンバータ。

- 前記グループ判定手段は、前記順次選択されたそれぞれのグループに含まれる全てのコンパレータの出力を加算する手段と、前記加算手段により加算された値が前記グループ選択手段により選択されたグループに含まれるコンパレータ数と一致するかまたは0であることを検出する手段と、から構成されることを特徴とする請求項1記載のA/Dコンバータ。

- 上部基準電位と下部基準電位から生成される比較電位を入力電圧と比較するコンパレータ群を内蔵するA/Dコンバータであって、

前記コンパレータ群の全ての出力を一時記憶する手段と、

あらかじめ設定した値を保持する比較テープルと、

前記一時記憶されたコンパレータの出力を前記比較テープルに保持された設定値と比較する手段と、

を具備したことを特徴とするA/Dコンバータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002198636A JP3591730B2 (ja) | 2002-07-08 | 2002-07-08 | A/dコンバータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002198636A JP3591730B2 (ja) | 2002-07-08 | 2002-07-08 | A/dコンバータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004040711A true JP2004040711A (ja) | 2004-02-05 |

| JP3591730B2 JP3591730B2 (ja) | 2004-11-24 |

Family

ID=31706036

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002198636A Expired - Fee Related JP3591730B2 (ja) | 2002-07-08 | 2002-07-08 | A/dコンバータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3591730B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113227806A (zh) * | 2018-12-28 | 2021-08-06 | 微芯片技术股份有限公司 | 基于比较器偏置对比较器进行分类 |

| US12134713B2 (en) | 2018-12-28 | 2024-11-05 | Microchip Technology Incorporated | Classifying comparators based on comparator offsets |

-

2002

- 2002-07-08 JP JP2002198636A patent/JP3591730B2/ja not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN113227806A (zh) * | 2018-12-28 | 2021-08-06 | 微芯片技术股份有限公司 | 基于比较器偏置对比较器进行分类 |

| US12134713B2 (en) | 2018-12-28 | 2024-11-05 | Microchip Technology Incorporated | Classifying comparators based on comparator offsets |

Also Published As

| Publication number | Publication date |

|---|---|

| JP3591730B2 (ja) | 2004-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9030346B2 (en) | Method and apparatus for self-test of successive approximation register (SAR) A/D converter | |

| US7924205B2 (en) | Successive approximation type analog/digital converter and operation method of successive approximation type analog/digital converter | |

| US4978957A (en) | High-speed analog-to-digital converter | |

| KR930004772Y1 (ko) | 아날로그/디지탈 변환기의 테스트장치 | |

| JPH08149006A (ja) | アナログ・ディジタル変換器 | |

| JPWO2007122950A1 (ja) | 半導体装置、半導体試験装置、及び半導体装置の試験方法 | |

| CN105657297A (zh) | 摄像装置、摄像装置的驱动方法和检查方法以及摄像系统 | |

| JP4999955B2 (ja) | アナログ−デジタル変換器の動作試験方法、アナログ−デジタル変換器およびアナログ−デジタル変換器の動作試験装置 | |

| JP2011041231A (ja) | 逐次比較型AD(AnalogDigital)コンバータ及びそのテスト方法 | |

| JP4526919B2 (ja) | A/d変換装置 | |

| JP3591730B2 (ja) | A/dコンバータ | |

| CN101682332A (zh) | 具有逐次逼近模数转换器的电路 | |

| JP2007285764A (ja) | 半導体装置及びその自己試験故障検出方法 | |

| CN101065678A (zh) | 对集成电路的物理工作参数进行监视 | |

| JPH10209870A (ja) | A/dコンバート方法 | |

| JPH03206728A (ja) | 自己校正方式adコンバータおよびそのテスト方法 | |

| US20040189505A1 (en) | Analog-to-digital converter | |

| CN113890536A (zh) | 用于测试连续逼近寄存器模数转换器的方法和装置 | |

| CN118944669B (zh) | 模拟数字转换器,及用于检测其中缺陷的方法和电路 | |

| JP2013183411A (ja) | Ad変換器の検査回路及びad変換器の検査方法 | |

| JP4525706B2 (ja) | A/d変換回路の試験方法 | |

| JPH0746129A (ja) | D/aコンバータおよびd/aコンバータの試験方法 | |

| JP2001203575A (ja) | A/d変換器 | |

| JP2013005185A (ja) | A/d変換回路及びそのテスト方法 | |

| JP3206295B2 (ja) | アナログ/デジタル変換器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040625 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040707 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040802 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040818 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040819 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080903 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080903 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090903 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090903 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100903 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |