EP2255389B1 - Stacked image sensor with shared diffusion regions - Google Patents

Stacked image sensor with shared diffusion regions Download PDFInfo

- Publication number

- EP2255389B1 EP2255389B1 EP09721716.0A EP09721716A EP2255389B1 EP 2255389 B1 EP2255389 B1 EP 2255389B1 EP 09721716 A EP09721716 A EP 09721716A EP 2255389 B1 EP2255389 B1 EP 2255389B1

- Authority

- EP

- European Patent Office

- Prior art keywords

- positions

- array

- image sensor

- photosensitive elements

- wafer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000009792 diffusion process Methods 0.000 title claims description 76

- 238000012545 processing Methods 0.000 claims description 17

- 238000000034 method Methods 0.000 claims description 9

- 235000012431 wafers Nutrition 0.000 description 58

- 239000002184 metal Substances 0.000 description 13

- 238000006243 chemical reaction Methods 0.000 description 10

- 239000004020 conductor Substances 0.000 description 9

- 238000003384 imaging method Methods 0.000 description 8

- 238000001465 metallisation Methods 0.000 description 8

- 239000004065 semiconductor Substances 0.000 description 7

- 238000012546 transfer Methods 0.000 description 7

- 238000003491 array Methods 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 239000000969 carrier Substances 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 230000035945 sensitivity Effects 0.000 description 5

- 238000010586 diagram Methods 0.000 description 4

- 239000000758 substrate Substances 0.000 description 4

- 206010034960 Photophobia Diseases 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 208000013469 light sensitivity Diseases 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 238000005070 sampling Methods 0.000 description 3

- 238000001429 visible spectrum Methods 0.000 description 3

- QNRATNLHPGXHMA-XZHTYLCXSA-N (r)-(6-ethoxyquinolin-4-yl)-[(2s,4s,5r)-5-ethyl-1-azabicyclo[2.2.2]octan-2-yl]methanol;hydrochloride Chemical compound Cl.C([C@H]([C@H](C1)CC)C2)CN1[C@@H]2[C@H](O)C1=CC=NC2=CC=C(OCC)C=C21 QNRATNLHPGXHMA-XZHTYLCXSA-N 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 230000007935 neutral effect Effects 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 230000003595 spectral effect Effects 0.000 description 2

- WXPZDDCNKXMOMC-AVGNSLFASA-N (2s)-1-[(2s)-2-[[(2s)-1-(2-aminoacetyl)pyrrolidine-2-carbonyl]amino]-5-(diaminomethylideneamino)pentanoyl]pyrrolidine-2-carboxylic acid Chemical compound NCC(=O)N1CCC[C@H]1C(=O)N[C@@H](CCCNC(N)=N)C(=O)N1[C@H](C(O)=O)CCC1 WXPZDDCNKXMOMC-AVGNSLFASA-N 0.000 description 1

- UVLMBMAKGAUBDU-OALUTQOASA-N (2s)-1-[2-[[(2s)-2-benzamido-3-phenylpropanoyl]amino]acetyl]pyrrolidine-2-carboxylic acid Chemical compound OC(=O)[C@@H]1CCCN1C(=O)CNC(=O)[C@@H](NC(=O)C=1C=CC=CC=1)CC1=CC=CC=C1 UVLMBMAKGAUBDU-OALUTQOASA-N 0.000 description 1

- 108010025123 N-benzoylphenylalanyl-glycyl-proline Proteins 0.000 description 1

- 230000003044 adaptive effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000037361 pathway Effects 0.000 description 1

- 235000010958 polyglycerol polyricinoleate Nutrition 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- 238000000638 solvent extraction Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B3/00—Simple or compound lenses

- G02B3/0006—Arrays

- G02B3/0037—Arrays characterized by the distribution or form of lenses

- G02B3/0056—Arrays characterized by the distribution or form of lenses arranged along two different directions in a plane, e.g. honeycomb arrangement of lenses

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B5/00—Optical elements other than lenses

- G02B5/20—Filters

- G02B5/201—Filters in the form of arrays

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/10—Circuitry of solid-state image sensors [SSIS]; Control thereof for transforming different wavelengths into image signals

- H04N25/11—Arrangement of colour filter arrays [CFA]; Filter mosaics

- H04N25/13—Arrangement of colour filter arrays [CFA]; Filter mosaics characterised by the spectral characteristics of the filter elements

- H04N25/133—Arrangement of colour filter arrays [CFA]; Filter mosaics characterised by the spectral characteristics of the filter elements including elements passing panchromatic light, e.g. filters passing white light

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/10—Circuitry of solid-state image sensors [SSIS]; Control thereof for transforming different wavelengths into image signals

- H04N25/11—Arrangement of colour filter arrays [CFA]; Filter mosaics

- H04N25/13—Arrangement of colour filter arrays [CFA]; Filter mosaics characterised by the spectral characteristics of the filter elements

- H04N25/135—Arrangement of colour filter arrays [CFA]; Filter mosaics characterised by the spectral characteristics of the filter elements based on four or more different wavelength filter elements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/778—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising amplifiers shared between a plurality of pixels, i.e. at least one part of the amplifier must be on the sensor array itself

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/011—Manufacture or treatment of image sensors covered by group H10F39/12

- H10F39/018—Manufacture or treatment of image sensors covered by group H10F39/12 of hybrid image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/802—Geometry or disposition of elements in pixels, e.g. address-lines or gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/809—Constructional details of image sensors of hybrid image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

- H10F39/182—Colour image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/805—Coatings

- H10F39/8053—Colour filters

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/811—Interconnections

Definitions

- the present invention relates generally to electronic image sensors for use in digital cameras and other image capture devices, and more particularly to image sensors comprising sensor and circuit wafers arranged in a stack.

- a typical electronic image sensor comprises a number of light sensitive picture elements ("pixels") arranged in a two-dimensional array. Such an image sensor may be configured to produce a color image by forming a color filter array (CFA) over the pixels.

- CFA color filter array

- One commonly used type of CFA pattern is the Bayer pattern, disclosed in U.S. Patent No. 3,971,065 , entitled “Color Imaging Array”.

- the Bayer CFA pattern provides each pixel with color photoresponse exhibiting a predominant sensitivity to one of three designated portions of the visible spectrum.

- the three designated portions may be, for example, red, green and blue, or cyan, magenta and yellow.

- a given CFA pattern is generally characterized by a minimal repeating unit in the form of a subarray of contiguous pixels that acts as a basic building block for the pattern. Multiple copies of the minimal repeating unit are juxtaposed to form the complete pattern.

- first and second semiconductor die or layers are examples of what are more generally referred to herein as sensor and circuit wafers, respectively.

- a problem that arises in conventional stacked image sensors relates to the manner in which the photosensitive elements in the sensor wafer are interconnected with the associated circuitry in the circuit wafer.

- the typical conventional approach generally calls for such interconnects to be formed on a per-pixel basis, that is, with a separate inter-wafer interconnect provided for each pixel. It is clear that such an approach can significantly increase the cost and complexity of the stacked image sensor. It can also have a negative impact on sensor performance.

- EP 1453097 discloses a solid-state image sensor and its production method.

- the solid-state image sensor has a chip-size package, which can be easily fabricated.

- US 2008/0062290 discloses a color image sensor including an array of pixels arranged in a plurality of pixel groups, each pixel group including a floating diffusion that is shared by four pixels disposed in a 2x2 arrangement.

- CMOS image sensor cell including a first pixel area in which at least one first photodiode is disposed for generating a first sense signal in response to a photo-signal of a first color; a second pixel area neighboring the first pixel area, in which at least one second photodiode is disposed for generating a second sense signal in response to a photo-signal of the second color; and a third pixel area neighboring the first and second pixel areas, in which at least one third photodiode is disposed for generating a third sense signal in response to a photo-signal of a third color.

- US2007/0210239 discloses an image sensor comprising an array of photoelectric conversion elements in a substrate, the photoelectric conversion element being arranged in rows and columns extending in a first direction and a second direction respectively; a plurality of first junction isolation regions in the substrate that each isolate side portions of neighboring photoelectric conversion elements of a common row, and a plurality of second junction isolation regions in the substrate that each isolate side portions of neighboring photoelectric conversion elements of a common column; and a plurality of dialelectric isolation regions in the substrate, that each isolate corner portions of neighboring photoelectric conversion elements.

- US 2007/0215912 discloses a solid-state imaging device.

- plural unit areas, each having a photoelectric conversion region converting incident light into electric signals are provided adjacently, which each photoelectric conversion region is provided being deviated from the central position of each unit area to a boundary position between the plural unit areas, a high refractive index material layer is arranged over the deviated photoelectric conversion region, and a low refractive index material layer is provided over the photoelectric conversion regions at the inverse side of the deviated direction being adjacent to the high refractive index material layer, and optical paths of the incident light are changed by the high refractive index material layer and the low refractive index material layer, and the incident light enters the photoelectic conversion region.

- the invention provides an image sensor as set out in claim 1 and a method as set out in claim 15.

- Illustrative embodiments of the invention provide stacked image sensors in which shared diffusion regions are arranged in designated array positions that would normally include photosensitive elements.

- the techniques of the invention generally involve dropping the photosensitive elements from these designated array positions and instead utilizing the positions to facilitate the formation of diffusion regions that are shared by multiple photosensitive elements in adjacent positions of the array.

- an image sensor comprises a sensor wafer and an underlying circuit wafer.

- the sensor wafer comprises a plurality of photodiodes or other photosensitive elements arranged in respective positions of a two-dimensional array of positions in which a subset of the array positions do not include photosensitive elements but instead include diffusion regions each of which is shared by two or more of the photosensitive elements.

- the diffusion regions may be, for example, floating diffusion regions.

- the sensor wafer is interconnected with the circuit wafer utilizing a plurality of inter-wafer interconnects coupled to respective ones of the shared diffusion regions in respective ones of the array positions that do not include photosensitive elements.

- the two-dimensional array comprises repeating groups of multiple positions with a given such group comprising a plurality of positions that include photosensitive elements arranged around a central dropped pixel position that does not include a photosensitive element.

- a given one of the shared diffusion regions is arranged in the central position of the given group and is shared by the photosensitive elements in at least a subset of the positions arranged around that central position.

- Each of the photosensitive elements that shares a given one of the shared diffusion regions may be coupled to that shared diffusion region via a corresponding transfer gate of the sensor wafer.

- the array of positions comprises a rectangular array of rows and columns of positions.

- the given group may comprise four positions that include photosensitive elements and are arranged around a single central dropped pixel position that does not include a photosensitive element but instead includes one of the shared diffusion regions.

- the photosensitive elements in the four positions that include photosensitive elements may be panchromatic elements in accordance with a CFA pattern of the image sensor, or may comprise same-color pairs of two different colors of the CFA pattern.

- the given group may comprise six positions that include photosensitive elements and are arranged around a single central dropped pixel position that does not include a photosensitive element but instead includes one of the shared diffusion regions.

- FIG. 1 For example, the given group referred to above in the case of a hexagonal array may also comprise six positions that include photosensitive elements and are arranged around a single central dropped pixel position that does not include a photosensitive element but instead includes one of the shared diffusion regions.

- the photosensitive elements in two adjacent ones of the six positions that include photosensitive elements are same-color elements, while the remaining ones of the six positions are panchromatic elements.

- An image sensor in accordance with the invention may be advantageously implemented in a digital camera or other type of image capture device.

- the techniques disclosed herein considerably facilitate the manufacture of stacked image sensors, at reduced cost and complexity, particularly for those image sensors having sparse CFA patterns.

- FIG. 1 shows a digital camera in which an image sensor having shared inter-wafer interconnects is implemented in an illustrative embodiment of the invention.

- the imaging stage 11 comprises lens 12, neutral density (ND) filter 13, iris 14 and shutter 18.

- the light 10 is focused by lens 12 to form an image on an image sensor 20.

- the amount of light reaching the image sensor 20 is regulated by iris 14, ND filter 13 and the time that shutter 18 is open.

- Image sensor 20 converts the incident light to an electrical signal for each pixel.

- the image sensor 20 may be, for example, a charge coupled device (CCD) type or active pixel sensor (APS) type image sensor, although other types of image sensors may be used in implementing the invention.

- CMOS complementary metal-oxide-semiconductor

- the image sensor 20 generally has a two-dimensional array of pixels configured in accordance with a designated CFA pattern.

- CFA patterns that may be used with the image sensor 20 include the panchromatic checkerboard patterns disclosed in U.S. Patent Application Publication No. 2007/0024931 , entitled "Image Sensor with Improved Light Sensitivity". These panchromatic checkerboard patterns provide certain of the pixels with a panchromatic photoresponse, and are also generally referred to herein as "sparse" CFA patterns.

- a panchromatic photoresponse has a wider spectral sensitivity than those spectral sensitivities represented in the selected set of color photoresponses and may, for example, have high sensitivity across substantially the entire visible spectrum.

- Image sensors configured with panchromatic checkerboard CFA patterns exhibit greater light sensitivity and are thus well-suited for use in applications involving low scene lighting, short exposure time, small aperture, or other restrictions on the amount of light reaching the image sensor.

- Other types of CFA patterns may be used in other embodiments of the invention.

- An analog signal from image sensor 20 is processed by analog signal processor 22 and applied to analog to digital (A/D) converter 24.

- Timing generator 26 produces various clocking signals to select particular rows and columns of the pixel array for processing, and synchronizes the operation of analog signal processor 22 and A/D converter 24.

- the image sensor 20, analog signal processor 22, A/D converter 24, and timing generator 26 collectively form an image sensor stage 28 of the digital camera.

- the components of image sensor stage 28 may comprise separately fabricated integrated circuits, or they may be fabricated as a single integrated circuit as is commonly done with CMOS image sensors.

- the A/D converter 24 outputs a stream of digital pixel values that are supplied via a bus 30 to a memory 32 associated with a digital signal processor (DSP) 36.

- Memory 32 may comprise any type of memory, such as, for example, synchronous dynamic random access memory (SDRAM).

- SDRAM synchronous dynamic random access memory

- the DSP 36 is one of a plurality of processing elements of the digital camera that are indicated as collectively comprising a processing stage 38.

- the other processing elements of the processing stage 38 include exposure controller 40 and system controller 50. Although this partitioning of digital camera functional control among multiple processing elements is typical, these elements may be combined in various ways without affecting the functional operation of the camera and the application of the present invention.

- a given one of the processing elements of processing stage 38 can comprise one or more DSP devices, microcontrollers, programmable logic devices, or other digital logic circuits. Although a combination of three separate processing elements is shown in the figure, alternative embodiments may combine the functionality of two or more of these elements into a single processor, controller or other processing element. Techniques for sampling and readout of the pixel array of the image sensor 20 may be implemented at least in part in the form of software that is executed by one or more such processing elements.

- the exposure controller 40 is responsive to an indication of an amount of light available in the scene, as determined by brightness sensor 42, and provides appropriate control signals to the ND filter 13, iris 14 and shutter 18 of the imaging stage 11.

- the system controller 50 is coupled via a bus 52 to DSP 36 and to program memory 54, system memory 56, host interface 57 and memory card interface 60.

- the system controller 50 controls the overall operation of the digital camera based on one or more software programs stored in program memory 54, which may comprise Flash electrically erasable programmable read-only memory (EEPROM) or other nonvolatile memory. This memory is also used to store image sensor calibration data, user setting selections and other data which must be preserved when the camera is turned off.

- System controller 50 controls the sequence of image capture by directing exposure controller 40 to operate the lens 12, ND filter 13, iris 14, and shutter 18 as previously described, directing the timing generator 26 to operate the image sensor 20 and associated elements, and directing DSP 36 to process the captured image data.

- DSP 36 manipulates the digital image data in its memory 32 according to one or more software programs stored in program memory 54 and copied to memory 32 for execution during image capture.

- the resulting image file stored in memory 32 may be, for example, transferred via host interface 57 to an external host computer, transferred via memory card interface 60 and memory card socket 62 to removable memory card 64, or displayed for the user on an image display 65.

- the image display 65 is typically an active matrix color liquid crystal display (LCD), although other types of displays may be used.

- the digital camera further comprises a user control and status interface 68 including a viewfinder display 70, an exposure display 72, user inputs 74 and status display 76. These elements may be controlled by a combination of software programs executed on exposure controller 40 and system controller 50.

- the user inputs 74 typically include some combination of buttons, rocker switches, joysticks, rotary dials or touchscreens.

- Exposure controller 40 operates light metering, exposure mode, autofocus and other exposure functions.

- the system controller 50 manages a graphical user interface (GUI) presented on one or more of the displays, e.g., on image display 65.

- the GUI typically includes menus for making various option selections and review modes for examining captured images.

- Processed images may be copied to a display buffer in system memory 56 and continuously read out via video encoder 80 to produce a video signal.

- This signal may be output directly from the camera for display on an external monitor, or processed by display controller 82 and presented on image display 65.

- the digital camera as shown in FIG. 1 may comprise additional or alternative elements of a type known to those skilled in the art. Elements not specifically shown or described herein may be selected from those known in the art.

- the present invention may be implemented in a wide variety of other types of digital cameras or image capture devices. For example, the present invention can be implemented in imaging applications involving mobile phones and automotive vehicles.

- certain aspects of the embodiments described herein may be implemented at least in part in the form of software executed by one or more processing elements of an image capture device. Such software can be implemented in a straightforward manner given the teachings provided herein, as will be appreciated by those skilled in the art.

- the two-dimensional pixel array of image sensor 20 comprises an array of light sensitive pixels, fabricated using stacked sensor and circuit wafers, that provide a way of converting incoming light at each pixel into an electrical signal that is measured.

- free carriers are generated and captured within the photosensitive element at each pixel. Capturing these free carriers for some period of time and then measuring the number of carriers captured, or measuring the rate at which free carriers are generated, allows the light level at each pixel to be measured. In the former case, accumulated carriers may be shifted out of a given photosensitive element and onto an input node of a charge to voltage measurement circuit as in a CMOS image sensor.

- Sampling and readout circuitry in a given embodiment may encompass switches or other elements that are formed integrally with the pixel array.

- Such sampling and readout circuitry is generally implemented within the sensor array 20, for example, as in the case of a CMOS image sensor.

- image sensor 20 Whenever general reference is made to an image sensor in the following description, it is understood to be representative of the image sensor 20 from FIG. 1 . It is further understood that all examples and their equivalents of image sensor architectures and pixel patterns of the present invention disclosed in this specification are used for image sensor 20.

- a pixel may refer to a discrete light sensing area and charge shifting or charge measurement circuitry associated with the light sensing area.

- the term pixel commonly refers to a particular location in the image having associated color values.

- FIG. 2 shows a portion of a pixel array 100 in the image sensor 20 of the digital camera of FIG. 1 in an illustrative embodiment.

- the CFA pattern is omitted from this plan view for clarity.

- the view shown is looking down on the upper surface of the sensor in the same direction in which the light 10 from the subject scene would be incident on that surface.

- the sensor is a stacked image sensor having a sensor wafer overlying a circuit wafer.

- the view of FIG. 2 therefore shows the upper surface of the sensor wafer.

- the sensor wafer comprises a plurality of photodiodes 102 arranged in respective positions of the two-dimensional array.

- positions of the array that would also normally include photodiodes in a conventional implementation do not include such elements in the present embodiment. Instead, these positions are utilized for shared diffusion regions 103 that are shared by multiple photodiodes in adjacent positions of the array.

- the array positions utilized for the shared diffusion regions 103 in this embodiment are examples of what are generally referred to herein as "dropped pixel" positions, as the corresponding pixel locations in the array do not include photodiodes.

- the particular sharing arrangement in the FIG. 2 embodiment is one in which a given diffusion region 103 is shared by four of the photodiodes 102.

- one of the diffusion regions 103 is shared by four photodiodes denoted A1, A2, A3 and A4. These four photodiodes occupy array positions adjacent to the array position that includes the corresponding shared diffusion region.

- the four photodiodes B1, B2, B3 and B4 share a common diffusion region, as do the four photodiodes C1, C2, C3 and C4, and the four photodiodes D1, D2, D3 and D4. This sharing arrangement is repeated with other sets of four photodiodes throughout the pixel array.

- the pixel array 100 of FIG. 2 comprises repeating groups of multiple array positions with a given such group comprising multiple positions that include respective photodiodes 102 and are arranged around a central position that does not include a photodiode but is instead utilized for a diffusion region 103 shared by the surrounding photodiodes.

- Each of the photodiodes that shares a given diffusion region 103 is coupled thereto via a corresponding transfer gate of the sensor wafer, as can be seen more clearly in FIGS. 3 and 4 .

- four photodiodes share a diffusion region in the FIG. 2 arrangement, other embodiments of the invention may utilize different sharing arrangements.

- FIGS. 5 , 6 and 7 Examples of arrangements in which six photodiodes share a given diffusion region and associated inter-wafer interconnect will be described below with reference to FIGS. 5 , 6 and 7 . Other examples with different sharing arrangements will be described with reference to FIGS. 8 and 9 .

- Each of the shared floating diffusion regions 103 of the sensor wafer as shown in FIG. 2 is associated with a corresponding inter-wafer interconnect 104 that serves to couple the sensor wafer to the underlying circuit wafer, as can be seen with reference to FIGS. 3 and 4 .

- the shared diffusion regions in the illustrative embodiments are assumed to be floating diffusion regions, but other types of diffusion regions, in any combination, may be used in alternative embodiments.

- a wide variety of diffusion region implementations are well known to those skilled in the art. See, for example, PCT International Publication No. WO 2006/130518 , entitled "CMOS Image Sensor Pixel with Selectable Binning".

- FIG. 3 shows a cross-sectional view of the pixel array 100 of FIG. 2 along the section line Z-Z' of the latter figure.

- CFA pattern 105 is formed on the upper surface of sensor wafer 106, and circuit wafer 108 underlies the sensor wafer 106.

- Light 10 from the subject scene is filtered by the CFA pattern 105 of the pixel array 100 such that designated portions of the visible spectrum are incident on respective ones of the photodiodes 102. For example, certain photodiodes may receive predominantly red, green or blue light, while others receive panchromatic light, in accordance with the particular CFA pattern that is utilized.

- each of four photodiodes 102 1 , 102 2 , 102 3 and 102 4 that share a common diffusion region 103 has an associated transfer gate 110.

- the diffusion region 103 of the sensor wafer 106 is illustratively a floating diffusion region.

- the four transfer gates 110 also denoted TG1, TG2, TG3 and TG4, couple the respective photodiodes to the shared diffusion region 103.

- This floating diffusion region is coupled via metal conductors 114, 115 of interconnect 104 to a corresponding floating diffusion region 116 in the circuit wafer 108.

- the floating diffusion regions 103, 116 of the sensor and circuit wafers are also denoted FD_SW and FD_CW, respectively.

- Metal conductors 114, 115 of interconnect 104 are located in the sensor and circuit wafers, respectively.

- the floating diffusion region 116 of the circuit wafer 108 is coupled to additional circuitry for processing signals generated by the photodiodes 102.

- This additional circuitry comprises a reset gate (RG) 120, a source follower (SF) 122, and a row select (RSEL) gate 124.

- This additional circuitry is coupled between a supply voltage VDD and an output voltage (VOUT) signal line 128.

- Each of the gates 110, 120, 122 and 124 in this embodiment is implemented as an N-type metal-oxide-semiconductor (NMOS) transistor, although other types of circuitry may be used, such as a P-type metal-oxide-semiconductor (PMOS) transistor. It is apparent from FIG.

- the circuit wafer includes a similar set of such circuitry for each of the sets of four photodiodes 102 in the sensor wafer that share a common floating diffusion region 103.

- the photodiodes A1, A3, B4, C2, D1 and D3 that lie along the section line Z-Z' in FIG. 2 are seen to be formed in silicon portion 130 of the sensor wafer 106. Also formed in this silicon portion of the sensor wafer is the floating diffusion region A, also denoted 103A, which is associated with the four photodiodes A1, A2, A3 and A4, and the floating diffusion region D, also denoted 103D, which is associated with the four photodiodes D1, D2, D3 and D4. It should be noted that the CFA pattern 105 in this embodiment has a black filter element over each of the floating diffusion regions 103A, 103D.

- such an arrangement serves to improve color uniformity for different pixels of the same color.

- the black filter elements may be eliminated, and the adjacent color filter elements extended over the floating diffusion regions 103A, 103D.

- Corresponding microlenses may be similarly extended. Arrangements of this type advantageously allow the neighboring photodiodes to "steal the light" from the corresponding dropped pixel positions of the pixel array, thereby improving sensitivity.

- a silicon portion 132 of the circuit wafer 108 includes corresponding floating diffusion regions A and D, also denoted 116A and 116D, respectively.

- the floating diffusion region 103A of the sensor wafer 106 is coupled via an interconnect 104A to the corresponding floating diffusion region 116A in the underlying circuit wafer 108.

- the interconnect 104A comprises metal conductors 114A formed in a metallization portion 140 of the sensor wafer and metal conductors 115A formed in a metallization portion 142 of the circuit wafer.

- the floating diffusion region 103D of the sensor wafer 106 is coupled via an interconnect 104D to a corresponding floating diffusion region 116D in the underlying circuit wafer 108.

- the interconnect 104D comprises metal conductors 114D formed in the metallization portion 140 of the sensor wafer 106 and metal conductors 115D formed in the metallization portion 142 of the circuit wafer 108.

- the metallization portion 140 of the sensor wafer comprises a single metal layer denoted "metal 1.”

- the metallization portion 142 of the circuit wafer 108 comprises multiple metal layers including layers denoted "metal 1" through “metal 8" as shown.

- the metal conductors 114, 115 of the inter-wafer interconnects 104 provide wafer-to-wafer electrical interconnection of the sensor and circuit wafers as indicated. It should be noted that the particular multi-layer metal interconnects shown in this example are not requirements of the invention. Numerous other types of inter-wafer interconnects may be used in alternative embodiments.

- row select gate 124 shown in the schematic diagram of FIG. 4 is omitted from the cross-sectional view of FIG. 3 for simplicity and clarity of illustration. Those skilled in the art will be familiar with the manner in which row select gates and other similar elements can be formed in a circuit wafer. In other embodiments, row select gates may be eliminated through the use of appropriate timing sequences that are known in the art.

- the dropped pixel positions that is, the array positions that do not include photodiodes but instead include shared diffusion regions, generally correspond to respective designated elements of the CFA pattern 105.

- FIGS. 5A and 5B a portion of the array 100 is shown, illustrating one possible implementation of the CFA pattern 105 as modified to include dropped pixel positions in accordance with an embodiment of the present invention.

- the CFA pattern in this example is a panchromatic checkerboard pattern of a type disclosed in the above-cited U.S. Patent Application Publication No. 2007/0024931 .

- FIG. 5A shows a larger portion of the pixel array 100

- FIG. 5B is a more detailed view of a smaller portion of the array as shown in FIG. 5A .

- the pixel array 100 as shown in these figures comprises a rectangular array of positions arranged in rows and columns.

- the array positions that include photodiodes are denoted as either red (R), green (G), blue (B) or panchromatic (P), in accordance with the corresponding elements of the particular CFA pattern 105.

- the array positions that do not include photodiodes, referred to as the dropped pixel positions of the array, are identified in FIG. 5A by an "x.”

- the pixel array 100 implements a four-pixel sharing arrangement in which four of the array positions that include photodiodes are arranged around a single central dropped pixel position, with the dropped pixel position being utilized for a diffusion region shared by the four photodiodes.

- This exemplary sharing arrangement is more clearly shown in FIG. 5B , where it can be seen that one of the dropped pixel positions 150-1 is associated with four surrounding panchromatic pixels.

- Another of the dropped pixel positions 150-2 is associated with two pairs of same-color pixels, with the same-color pixels of a given one of the pairs being arranged on opposite sides of that dropped pixel position. More specifically, dropped pixel position 150-2 is associated with a pair of blue pixels and a pair of green pixels.

- Other groups of array positions in the array 100 are configured in a similar manner, to include either four panchromatic pixels around a dropped pixel position, or two different pairs of same-color pixels arranged around a dropped pixel position.

- FIG. 6 Another example is shown in FIG. 6 , where a pixel array 600 has a different panchromatic checkerboard CFA pattern than that used in FIG. 5 , and utilizes a six-pixel sharing arrangement rather than the four-pixel sharing arrangement of FIGS. 2 through 5 .

- the array 600 comprises blue/green row pairs 602 which include only blue, green and panchromatic pixels.

- the blue/green row pairs 602 alternate with red/green row pairs 604 that include only red, green and panchromatic pixels.

- 6 example comprises 16 contiguous pixels and may be viewed as being arranged as follows: PBPG BPGP PGPR GPRP Patterns with other minimal repeating units, such as minimal repeating units of at least 12 pixels as described in the above-cited U.S. Patent Application Publication No. 2007/0024931 , may be used. Also, colors other than red, green and blue may be used, such as, for example, cyan, magenta and yellow.

- a given group of array positions in this example comprises six positions that include photodiodes arranged around a single central dropped pixel position 610 that does not include a photodiode but instead includes a shared diffusion region.

- the location of the dropped pixel position varies in a regular manner from row to row within the pixel array 600. More specifically, in this example, every eighth pixel position in a given row is a dropped pixel position, and the dropped pixel positions are offset from row to row by two pixel positions. The dropped pixel positions thus also follow a repeating pattern within the array.

- the six pixels which share a diffusion region in a given dropped pixel position are shown in FIG. 6 as being interconnected with one another. This shared diffusion region is assumed to be coupled to a corresponding region in an underlying circuit wafer via a corresponding inter-wafer interconnect, as in the embodiment of FIGS. 2 to 5 .

- the pixel array comprises a rectangular array of rows and columns.

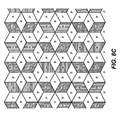

- FIG. 7 shows an alternative embodiment in which the pixel array of image sensor 20 is not a rectangular array, but is instead a hexagonal array.

- a pixel array 700 again comprises repeating groups of array positions with a given such group comprising multiple positions that include respective photodiodes and are arranged around a single central dropped pixel position that does not include a photodiode but is instead utilized for a diffusion region shared by the surrounding photodiodes.

- each group in this embodiment comprises six positions that include photodiodes and are arranged around a single central dropped pixel position 710 that does not include a photodiode.

- each of the photodiodes in the group is coupled via a corresponding transfer gate to a shared diffusion region arranged in the dropped pixel position. Again, this shared diffusion region is assumed to be coupled to a corresponding region in an underlying circuit wafer via a corresponding inter-wafer interconnect, as in the embodiment of FIGS. 2 to 5 .

- the photodiodes in two adjacent ones of the six positions that include photodiodes comprise same-color photodiodes in accordance with the CFA pattern associated with the image sensor, while the photodiodes in the remaining ones of the six positions comprise panchromatic photodiodes in accordance with the CFA pattern.

- the uppermost group at the left hand side of the pixel array 700 includes two adjacent red pixels and four panchromatic pixels arranged around the dropped pixel position 710.

- Other groups of positions in the pixel array are similarly configured to include two adjacent same-color pixels, which may be either red, green or blue, and four adjacent panchromatic pixels, surrounding a dropped pixel position. This particular arrangement facilitates color binning. Also, since each pair of same-color pixels is completely surrounded by panchromatic pixels, CFA interpolation operations can be performed more easily and accurately. Again, the particular CFA pattern and the pixel sharing arrangement may be varied in other embodiments.

- pixel arrays can be classified geometrically as plane tilings by regular polygons.

- the tiling may be viewed as being generated from a single polygon, namely a square, while in the example of FIG. 7 the tiling is also generated from a single polygon, but in this case a hexagon.

- the corresponding patterns are generally referred to as a square tiling pattern and a hexagonal tiling pattern, respectively.

- the dropped pixel positions of the pixel array correspond to selected ones of the tiles of the tiling pattern.

- FIG. 8 illustrates another embodiment of the invention.

- a pixel array 800 having a hexagonal tiling pattern is shown.

- the dropped pixel positions in this array are denoted by the letter D.

- Reference numeral 810 denotes a particular one of the dropped pixel positions.

- one in four of the hexagons of the hexagonal tiling pattern is identified as a dropped pixel position.

- FIG. 8B shows a plan view of the pixel array 800, with each dropped pixel position including a floating diffusion region that is shared by photodiodes in three neighboring pixel positions via respective transfer gates.

- the photodiodes may be viewed as having a quasiregular rhombic tiling.

- FIG. 8C shows an example of a CFA pattern that may be used for the quasiregular rhombic tiling of FIG. 8B .

- the red, green and blue color filter elements are grouped in pairs of two same-color elements so that they can be binned for better luminance matching.

- FIG. 9 illustrates yet another embodiment of the invention.

- the tiling pattern in this embodiment is a type of truncated square tiling pattern, shown generally in FIG. 9A .

- This truncated square tiling pattern is generated from two polygons, namely, a square and an octagon.

- the dropped pixel positions in the pixel array 900 are again denoted by the letter D, and generally correspond to half of the square polygons.

- Reference numeral 910 denotes a particular one of the dropped pixel positions.

- FIG. 9B shows a plan view of the pixel array 900, with each dropped pixel position including a floating diffusion region that is shared by photodiodes in two neighboring pixel positions via respective transfer gates.

- tiling arrangements may be used in implementing an image sensor in accordance with the invention.

- Other examples include rows with square unit cells, rows with rectangular unit cells, trihexagonal tiling, snub hexagonal tiling, prismatic pentagonal tiling, Cairo pentagonal tiling, truncated hexagonal tiling, snub square tiling, floret pentagonal tiling, etc.

- Those skilled in the art will recognize that the disclosed techniques can be adapted in a straightforward manner to these and other types of pixel arrays.

- the illustrative embodiments facilitate the interconnection of sensor and circuit wafers in a stacked image sensor, thereby reducing sensor cost and complexity.

- These embodiments leverage the advantages of sparse CFA patterns for increased low light sensitivity.

- configuring the dropped pixel positions in a regular repeating pattern subsequent image processing operations are simplified.

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Spectroscopy & Molecular Physics (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Color Television Image Signal Generators (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/049,579 US7781716B2 (en) | 2008-03-17 | 2008-03-17 | Stacked image sensor with shared diffusion regions in respective dropped pixel positions of a pixel array |

| PCT/US2009/000892 WO2009117046A1 (en) | 2008-03-17 | 2009-02-12 | Stacked image sensor with shared diffusion regions |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| EP2255389A1 EP2255389A1 (en) | 2010-12-01 |

| EP2255389B1 true EP2255389B1 (en) | 2014-01-22 |

Family

ID=40636724

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| EP09721716.0A Active EP2255389B1 (en) | 2008-03-17 | 2009-02-12 | Stacked image sensor with shared diffusion regions |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7781716B2 (enExample) |

| EP (1) | EP2255389B1 (enExample) |

| JP (1) | JP2011517506A (enExample) |

| KR (1) | KR101533134B1 (enExample) |

| CN (1) | CN101978499B (enExample) |

| TW (1) | TWI502731B (enExample) |

| WO (1) | WO2009117046A1 (enExample) |

Families Citing this family (55)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090302409A1 (en) * | 2008-06-04 | 2009-12-10 | Omnivision Technologies, Inc. | Image sensor with multiple thickness anti-relfective coating layers |

| JP4799594B2 (ja) * | 2008-08-19 | 2011-10-26 | 株式会社東芝 | 固体撮像装置およびその製造方法 |

| US20100149379A1 (en) * | 2008-12-16 | 2010-06-17 | Summa Joseph R | Image sensor with three-dimensional interconnect and ccd |

| JP5109962B2 (ja) * | 2008-12-22 | 2012-12-26 | ソニー株式会社 | 固体撮像装置および電子機器 |

| US8648932B2 (en) | 2009-08-13 | 2014-02-11 | Olive Medical Corporation | System, apparatus and methods for providing a single use imaging device for sterile environments |

| KR101648200B1 (ko) | 2009-10-22 | 2016-08-12 | 삼성전자주식회사 | 이미지 센서 및 그 제조 방법 |

| US20110115954A1 (en) * | 2009-11-19 | 2011-05-19 | Eastman Kodak Company | Sparse color pixel array with pixel substitutes |

| US8106427B2 (en) | 2009-12-21 | 2012-01-31 | Omnivision Technologies, Inc. | Image sensor with well bounce correction |

| US20110156197A1 (en) * | 2009-12-31 | 2011-06-30 | Tivarus Cristian A | Interwafer interconnects for stacked CMOS image sensors |

| US20110156195A1 (en) * | 2009-12-31 | 2011-06-30 | Tivarus Cristian A | Interwafer interconnects for stacked CMOS image sensors |

| JP6165624B2 (ja) | 2010-03-25 | 2017-07-19 | デピュー シンセス プロダクツ, インコーポレーテッドDePuy Synthes Products, Inc. | 医療用使い捨て画像装置を提供するためのシステムおよび方法 |

| FR2958079B1 (fr) * | 2010-03-26 | 2012-09-21 | Commissariat Energie Atomique | Dispositif imageur cmos a architecture en trois dimensions |

| US8644603B2 (en) * | 2010-06-03 | 2014-02-04 | Tripurari Singh | Methods and system for spectral image sampling |

| US8445828B2 (en) | 2010-07-01 | 2013-05-21 | Silicon Optronics, Inc. | High dynamic range image sensor with in pixel memory |

| US9739914B2 (en) | 2010-07-13 | 2017-08-22 | Nokia Technologies Oy | Color image sensing |

| JP5500007B2 (ja) * | 2010-09-03 | 2014-05-21 | ソニー株式会社 | 固体撮像素子およびカメラシステム |

| JP5785398B2 (ja) * | 2011-02-17 | 2015-09-30 | キヤノン株式会社 | 撮像装置及び画像信号処理装置 |

| JP2012199489A (ja) * | 2011-03-23 | 2012-10-18 | Sony Corp | 固体撮像装置、固体撮像装置の製造方法、及び電子機器 |

| WO2012148919A2 (en) | 2011-04-25 | 2012-11-01 | Skybox Imaging, Inc. | Systems and methods for overhead imaging and video |

| CN103648378B (zh) * | 2011-05-12 | 2016-10-12 | 橄榄医疗公司 | 用于使用竖直互连的混合堆叠图像传感器的子列并行数字转换器的系统和方法 |

| JP5547150B2 (ja) * | 2011-09-16 | 2014-07-09 | 株式会社東芝 | 固体撮像素子 |

| US8890047B2 (en) * | 2011-09-21 | 2014-11-18 | Aptina Imaging Corporation | Stacked-chip imaging systems |

| JP5963421B2 (ja) * | 2011-11-17 | 2016-08-03 | オリンパス株式会社 | 固体撮像装置および撮像装置 |

| JP6018376B2 (ja) * | 2011-12-05 | 2016-11-02 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| TW201334169A (zh) * | 2012-02-10 | 2013-08-16 | Sony Corp | 攝像元件、製造裝置及方法、及攝像裝置 |

| KR20130119193A (ko) * | 2012-04-23 | 2013-10-31 | 주식회사 동부하이텍 | 후면 수광 이미지 센서와 그 제조방법 |

| US9270906B2 (en) | 2012-05-02 | 2016-02-23 | Semiconductor Components Industries, Llc | Exposure time selection using stacked-chip image sensors |

| EP2677732B1 (en) * | 2012-06-22 | 2019-08-28 | Nokia Technologies Oy | Method, apparatus and computer program product for capturing video content |

| JP2014022561A (ja) | 2012-07-18 | 2014-02-03 | Sony Corp | 固体撮像装置、及び、電子機器 |

| IN2015MN00019A (enExample) | 2012-07-26 | 2015-10-16 | Olive Medical Corp | |

| US9153616B2 (en) * | 2012-12-26 | 2015-10-06 | Olympus Corporation | Solid-state imaging device and imaging device with circuit elements distributed on multiple substrates, method of controlling solid-state imaging device, and imaging device with circuit elements distributed on multiple substrates |

| EP2967286B1 (en) | 2013-03-15 | 2021-06-23 | DePuy Synthes Products, Inc. | Minimize image sensor i/o and conductor counts in endoscope applications |

| EP2967285B1 (en) | 2013-03-15 | 2023-08-16 | DePuy Synthes Products, Inc. | Image sensor synchronization without input clock and data transmission clock |

| US9692992B2 (en) * | 2013-07-01 | 2017-06-27 | Omnivision Technologies, Inc. | Color and infrared filter array patterns to reduce color aliasing |

| US9654714B2 (en) * | 2013-11-01 | 2017-05-16 | Silicon Optronics, Inc. | Shared pixel with fixed conversion gain |

| KR20150130186A (ko) | 2014-05-13 | 2015-11-23 | 삼성전자주식회사 | 이미지 센서 및 그 적층 구조 |

| US9508681B2 (en) | 2014-12-22 | 2016-11-29 | Google Inc. | Stacked semiconductor chip RGBZ sensor |

| KR102530162B1 (ko) * | 2015-02-27 | 2023-05-09 | 소니그룹주식회사 | 반도체 장치, 고체 촬상 소자, 촬상 장치, 및 전자 기기 |

| CA2980920C (en) | 2015-03-25 | 2023-09-26 | King Abdulaziz City Of Science And Technology | Apparatus and methods for synthetic aperture radar with digital beamforming |

| CN108432049B (zh) | 2015-06-16 | 2020-12-29 | 阿卜杜拉阿齐兹国王科技城 | 有效平面相控阵列天线组件 |

| EP3380864A4 (en) | 2015-11-25 | 2019-07-03 | Urthecast Corp. | APPARATUS AND METHODS FOR OPEN SYNTHESIS RADAR IMAGING |

| KR20170084519A (ko) | 2016-01-12 | 2017-07-20 | 삼성전자주식회사 | 이미지 센서 |

| US10893224B2 (en) * | 2016-02-29 | 2021-01-12 | Sony Corporation | Imaging element and electronic device |

| US10319071B2 (en) | 2016-03-23 | 2019-06-11 | Qualcomm Incorporated | Truncated square pyramid geometry and frame packing structure for representing virtual reality video content |

| US10103190B2 (en) * | 2016-05-13 | 2018-10-16 | Semiconductor Components Industries, Llc | Imaging sensor having floating region of imaging device on one substrate electrically coupled to another floating region formed on a second substrate |

| DE102016212771A1 (de) * | 2016-07-13 | 2018-01-18 | Robert Bosch Gmbh | Verfahren und Vorrichtung zum Abtasten eines Lichtsensors |

| US10051218B1 (en) | 2017-02-03 | 2018-08-14 | SmartSens Technology (U.S.), Inc. | Stacked image sensor pixel cell with in-pixel vertical channel transfer transistor and reflective structure |

| US9992437B1 (en) | 2017-02-03 | 2018-06-05 | SmartSense Technology(U.S.), Inc. | Stacked image sensor pixel cell with in-pixel vertical channel transfer transistor |

| US11506778B2 (en) | 2017-05-23 | 2022-11-22 | Spacealpha Insights Corp. | Synthetic aperture radar imaging apparatus and methods |

| CA3064586A1 (en) | 2017-05-23 | 2018-11-29 | King Abdullah City Of Science And Technology | Synthetic aperture radar imaging apparatus and methods for moving targets |

| WO2019226194A2 (en) | 2017-11-22 | 2019-11-28 | Urthecast Corp. | Synthetic aperture radar apparatus and methods |

| WO2019130702A1 (ja) * | 2017-12-27 | 2019-07-04 | ソニーセミコンダクタソリューションズ株式会社 | 撮像装置 |

| US11323643B2 (en) | 2018-09-12 | 2022-05-03 | Dolby Laboratories Licensing Corporation | CMOS sensor architecture for temporal dithered sampling |

| KR20220144702A (ko) | 2021-04-20 | 2022-10-27 | 삼성전자주식회사 | 픽셀 어레이 및 이를 포함하는 이미지 센서 |

| JP2023154356A (ja) * | 2022-04-06 | 2023-10-19 | ソニーセミコンダクタソリューションズ株式会社 | 光検出装置および測距装置ならびに撮像装置 |

Family Cites Families (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE2262848C2 (de) * | 1972-12-22 | 1974-12-19 | Gardisette Holding Ag, Luzern (Schweiz) | Vorrichtung zum Verpacken, Transportieren und Lagern von konfektionierten knitterfrei zu haltenden Textilien |

| US3971065A (en) | 1975-03-05 | 1976-07-20 | Eastman Kodak Company | Color imaging array |

| US5670817A (en) * | 1995-03-03 | 1997-09-23 | Santa Barbara Research Center | Monolithic-hybrid radiation detector/readout |

| US5652621A (en) * | 1996-02-23 | 1997-07-29 | Eastman Kodak Company | Adaptive color plane interpolation in single sensor color electronic camera |

| JP2001237405A (ja) * | 2000-02-24 | 2001-08-31 | Victor Co Of Japan Ltd | 固体撮像装置および固体撮像装置の製造方法 |

| JP3713418B2 (ja) | 2000-05-30 | 2005-11-09 | 光正 小柳 | 3次元画像処理装置の製造方法 |

| US6809769B1 (en) * | 2000-06-22 | 2004-10-26 | Pixim, Inc. | Designs of digital pixel sensors |

| EP1453097A4 (en) | 2001-11-05 | 2008-01-23 | Zycube Co Ltd | TUBE-FREE IMAGE SENSOR AND METHOD FOR THE PRODUCTION THEREOF |

| US6927432B2 (en) * | 2003-08-13 | 2005-08-09 | Motorola, Inc. | Vertically integrated photosensor for CMOS imagers |

| US6984816B2 (en) * | 2003-08-13 | 2006-01-10 | Motorola, Inc. | Vertically integrated photosensor for CMOS imagers |

| US6809008B1 (en) * | 2003-08-28 | 2004-10-26 | Motorola, Inc. | Integrated photosensor for CMOS imagers |

| US7304673B2 (en) * | 2003-10-22 | 2007-12-04 | Eastman Kodak Company | Image sensor array with substitutional circuit distribution |

| JP4665422B2 (ja) * | 2004-04-02 | 2011-04-06 | ソニー株式会社 | 撮像装置 |

| KR100674925B1 (ko) * | 2004-12-07 | 2007-01-26 | 삼성전자주식회사 | 허니콤 구조의 능동 픽셀 센서 |

| KR100610481B1 (ko) * | 2004-12-30 | 2006-08-08 | 매그나칩 반도체 유한회사 | 수광영역을 넓힌 이미지센서 및 그 제조 방법 |

| KR100598015B1 (ko) * | 2005-02-07 | 2006-07-06 | 삼성전자주식회사 | 공유 구조 상보성 금속 산화막 반도체 액티브 픽셀 센서어레이의 레이 아웃 |

| KR100782463B1 (ko) * | 2005-04-13 | 2007-12-05 | (주)실리콘화일 | 3차원 구조를 갖는 이미지 센서의 분리형 단위화소 및 그제조방법 |

| US7705900B2 (en) | 2005-06-01 | 2010-04-27 | Eastman Kodak Company | CMOS image sensor pixel with selectable binning and conversion gain |

| KR100703979B1 (ko) * | 2005-07-26 | 2007-04-06 | 삼성전자주식회사 | 수광 효율이 향상된 2 공유 픽셀 이미지 센서 및 그 제조방법 |

| US7671314B2 (en) * | 2005-07-09 | 2010-03-02 | Samsung Electronics Co., Ltd. | Image sensor including active pixel sensor array with photoelectric conversion region |

| US8306362B2 (en) * | 2005-07-20 | 2012-11-06 | Omnivision Technologies, Inc. | Selective pixel binning and averaging based on scene illuminant |

| FR2888989B1 (fr) * | 2005-07-21 | 2008-06-06 | St Microelectronics Sa | Capteur d'images |

| US20070018073A1 (en) | 2005-07-22 | 2007-01-25 | Taiwan Semiconductor Manufacturing Co., Ltd. | CMOS image sensor device with beehive pattern color sensor cell array |

| US8139130B2 (en) * | 2005-07-28 | 2012-03-20 | Omnivision Technologies, Inc. | Image sensor with improved light sensitivity |

| KR100775058B1 (ko) * | 2005-09-29 | 2007-11-08 | 삼성전자주식회사 | 픽셀 및 이를 이용한 이미지 센서, 그리고 상기 이미지센서를 포함하는 이미지 처리 시스템 |

| JP2007228460A (ja) * | 2006-02-27 | 2007-09-06 | Mitsumasa Koyanagi | 集積センサを搭載した積層型半導体装置 |

| US7667183B2 (en) | 2006-03-10 | 2010-02-23 | Samsung Electronics Co., Ltd. | Image sensor with high fill factor pixels and method for forming an image sensor |

| US7638804B2 (en) * | 2006-03-20 | 2009-12-29 | Sony Corporation | Solid-state imaging device and imaging apparatus |

| US7916362B2 (en) * | 2006-05-22 | 2011-03-29 | Eastman Kodak Company | Image sensor with improved light sensitivity |

| KR100818724B1 (ko) | 2006-07-19 | 2008-04-01 | 삼성전자주식회사 | Cmos 이미지 센서와 이를 이용한 이미지 센싱 방법 |

| US7773138B2 (en) | 2006-09-13 | 2010-08-10 | Tower Semiconductor Ltd. | Color pattern and pixel level binning for APS image sensor using 2×2 photodiode sharing scheme |

| US8049256B2 (en) | 2006-10-05 | 2011-11-01 | Omnivision Technologies, Inc. | Active pixel sensor having a sensor wafer connected to a support circuit wafer |

| KR100835892B1 (ko) * | 2007-03-26 | 2008-06-09 | (주)실리콘화일 | 칩 적층 이미지센서 |

| US7960768B2 (en) * | 2008-01-17 | 2011-06-14 | Aptina Imaging Corporation | 3D backside illuminated image sensor with multiplexed pixel structure |

-

2008

- 2008-03-17 US US12/049,579 patent/US7781716B2/en active Active

-

2009

- 2009-02-12 WO PCT/US2009/000892 patent/WO2009117046A1/en not_active Ceased

- 2009-02-12 EP EP09721716.0A patent/EP2255389B1/en active Active

- 2009-02-12 JP JP2011500767A patent/JP2011517506A/ja active Pending

- 2009-02-12 KR KR1020107020799A patent/KR101533134B1/ko active Active

- 2009-02-12 CN CN2009801094520A patent/CN101978499B/zh active Active

- 2009-03-16 TW TW098108472A patent/TWI502731B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| TW200947689A (en) | 2009-11-16 |

| JP2011517506A (ja) | 2011-06-09 |

| TWI502731B (zh) | 2015-10-01 |

| CN101978499A (zh) | 2011-02-16 |

| KR101533134B1 (ko) | 2015-07-01 |

| CN101978499B (zh) | 2013-11-06 |

| US20090230287A1 (en) | 2009-09-17 |

| KR20100126749A (ko) | 2010-12-02 |

| US7781716B2 (en) | 2010-08-24 |

| EP2255389A1 (en) | 2010-12-01 |

| WO2009117046A1 (en) | 2009-09-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP2255389B1 (en) | Stacked image sensor with shared diffusion regions | |

| EP2339828B1 (en) | Sampling and readout of an image sensor | |

| KR101417232B1 (ko) | 복수의 감지층들을 구비한 이미지 센서 | |

| KR101414662B1 (ko) | 다수의 센서층들을 갖는 이미지 센서와 이의 동작 및 제조 방법 | |

| KR102730554B1 (ko) | 고체 촬상 소자, 제조 방법 및 전자 기기 | |

| CN205792895U (zh) | 成像系统 | |

| US8314866B2 (en) | Imager with variable area color filter array and pixel elements | |

| US20090021629A1 (en) | Solid state imaging device | |

| CN113676682A (zh) | 用于快速像素合并的双行选择像素 | |

| US20070090274A1 (en) | Image sensors including active pixel sensor arrays | |

| TW201103340A (en) | Solid-state imaging device and electronic apparatus | |

| KR102891047B1 (ko) | 복수의 촬영 모드를 지원하는 이미지 센서 | |

| KR20220073033A (ko) | 이미지 센서 및 이미지 센싱 시스템 | |

| US8878255B2 (en) | Image sensors with multiple output structures | |

| US8878256B2 (en) | Image sensors with multiple output structures | |

| US20240047488A1 (en) | Image sensor | |

| KR20250152795A (ko) | 픽셀 및 그를 포함하는 이미지 센서 | |

| CN120129322A (zh) | 具有共享读出的混合成像传感器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PUAI | Public reference made under article 153(3) epc to a published international application that has entered the european phase |

Free format text: ORIGINAL CODE: 0009012 |

|

| 17P | Request for examination filed |

Effective date: 20100920 |

|

| AK | Designated contracting states |

Kind code of ref document: A1 Designated state(s): AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO SE SI SK TR |

|

| AX | Request for extension of the european patent |

Extension state: AL BA RS |

|

| 17Q | First examination report despatched |

Effective date: 20110302 |

|

| DAX | Request for extension of the european patent (deleted) | ||

| RAP1 | Party data changed (applicant data changed or rights of an application transferred) |

Owner name: OMNIVISION TECHNOLOGIES, INC. |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R079 Ref document number: 602009021570 Country of ref document: DE Free format text: PREVIOUS MAIN CLASS: H01L0027146000 Ipc: G02B0005200000 |

|

| RIC1 | Information provided on ipc code assigned before grant |

Ipc: H04N 5/3745 20110101ALI20130701BHEP Ipc: G02B 5/20 20060101AFI20130701BHEP Ipc: H01L 27/146 20060101ALI20130701BHEP Ipc: H04N 9/04 20060101ALI20130701BHEP Ipc: G02B 3/00 20060101ALI20130701BHEP |

|

| GRAP | Despatch of communication of intention to grant a patent |

Free format text: ORIGINAL CODE: EPIDOSNIGR1 |

|

| INTG | Intention to grant announced |

Effective date: 20130813 |

|

| GRAS | Grant fee paid |

Free format text: ORIGINAL CODE: EPIDOSNIGR3 |

|

| GRAA | (expected) grant |

Free format text: ORIGINAL CODE: 0009210 |

|

| AK | Designated contracting states |

Kind code of ref document: B1 Designated state(s): CH DE FR GB LI |

|

| RBV | Designated contracting states (corrected) |

Designated state(s): CH DE FR GB LI |

|

| REG | Reference to a national code |

Ref country code: GB Ref legal event code: FG4D |

|

| REG | Reference to a national code |

Ref country code: CH Ref legal event code: EP |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R096 Ref document number: 602009021570 Country of ref document: DE Effective date: 20140306 |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R097 Ref document number: 602009021570 Country of ref document: DE |

|

| PLBE | No opposition filed within time limit |

Free format text: ORIGINAL CODE: 0009261 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: NO OPPOSITION FILED WITHIN TIME LIMIT |

|

| 26N | No opposition filed |

Effective date: 20141023 |

|

| REG | Reference to a national code |

Ref country code: DE Ref legal event code: R097 Ref document number: 602009021570 Country of ref document: DE Effective date: 20141023 |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: PLFP Year of fee payment: 8 |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: PLFP Year of fee payment: 9 |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: PLFP Year of fee payment: 10 |

|

| P01 | Opt-out of the competence of the unified patent court (upc) registered |

Effective date: 20230419 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: DE Payment date: 20250109 Year of fee payment: 17 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: CH Payment date: 20250301 Year of fee payment: 17 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: FR Payment date: 20250110 Year of fee payment: 17 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: GB Payment date: 20250109 Year of fee payment: 17 |