CN1252834C - 用自对准硅化物工艺形成的mosfet及其制造方法 - Google Patents

用自对准硅化物工艺形成的mosfet及其制造方法 Download PDFInfo

- Publication number

- CN1252834C CN1252834C CNB031567274A CN03156727A CN1252834C CN 1252834 C CN1252834 C CN 1252834C CN B031567274 A CNB031567274 A CN B031567274A CN 03156727 A CN03156727 A CN 03156727A CN 1252834 C CN1252834 C CN 1252834C

- Authority

- CN

- China

- Prior art keywords

- mentioned

- film

- gate electrode

- semiconductor device

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

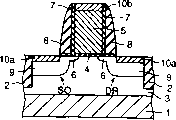

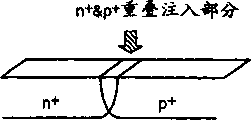

- H10D30/0223—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate

- H10D30/0227—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate having both lightly-doped source and drain extensions and source and drain regions self-aligned to the sides of the gate, e.g. lightly-doped drain [LDD] MOSFET or double-diffused drain [DDD] MOSFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/2807—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor the final conductor layer next to the insulator being Si or Ge or C and their alloys except Si

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0212—Manufacture or treatment of FETs having insulated gates [IGFET] using self-aligned silicidation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/01—Manufacture or treatment

- H10D64/021—Manufacture or treatment using multiple gate spacer layers, e.g. bilayered sidewall spacers

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP268970/2002 | 2002-09-13 | ||

| JP2002268970A JP2004111479A (ja) | 2002-09-13 | 2002-09-13 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1495911A CN1495911A (zh) | 2004-05-12 |

| CN1252834C true CN1252834C (zh) | 2006-04-19 |

Family

ID=32267040

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB031567274A Expired - Fee Related CN1252834C (zh) | 2002-09-13 | 2003-09-08 | 用自对准硅化物工艺形成的mosfet及其制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20040113209A1 (enExample) |

| JP (1) | JP2004111479A (enExample) |

| KR (1) | KR100508840B1 (enExample) |

| CN (1) | CN1252834C (enExample) |

| TW (1) | TW200406849A (enExample) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050253205A1 (en) * | 2004-05-17 | 2005-11-17 | Fujitsu Limited | Semiconductor device and method for fabricating the same |

| CN1700478A (zh) * | 2004-05-17 | 2005-11-23 | 富士通株式会社 | 半导体器件及其制造方法 |

| KR100678314B1 (ko) * | 2004-12-15 | 2007-02-02 | 동부일렉트로닉스 주식회사 | 저접촉저항을 갖는 반도체 소자의 제조방법 |

| KR100731096B1 (ko) | 2005-12-28 | 2007-06-22 | 동부일렉트로닉스 주식회사 | 반도체 소자 및 이의 제조방법 |

| US8258057B2 (en) * | 2006-03-30 | 2012-09-04 | Intel Corporation | Copper-filled trench contact for transistor performance improvement |

| US7566605B2 (en) * | 2006-03-31 | 2009-07-28 | Intel Corporation | Epitaxial silicon germanium for reduced contact resistance in field-effect transistors |

| JP4983087B2 (ja) * | 2006-04-27 | 2012-07-25 | 富士通セミコンダクター株式会社 | 成膜方法、半導体装置の製造方法、コンピュータ可読記録媒体、スパッタ処理装置 |

| JP2008071890A (ja) * | 2006-09-13 | 2008-03-27 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP5309454B2 (ja) * | 2006-10-11 | 2013-10-09 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| JP2008141003A (ja) * | 2006-12-01 | 2008-06-19 | Toshiba Corp | 半導体装置の製造方法 |

| JP5211503B2 (ja) * | 2007-02-16 | 2013-06-12 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| TW200910526A (en) | 2007-07-03 | 2009-03-01 | Renesas Tech Corp | Method of manufacturing semiconductor device |

| CN102446970B (zh) * | 2011-08-29 | 2014-05-28 | 上海华力微电子有限公司 | 一种防止酸槽清洗空洞形成的半导体器件及其制备方法 |

| CN110571190B (zh) * | 2018-06-05 | 2022-02-08 | 中芯国际集成电路制造(上海)有限公司 | 接触插塞的形成方法和刻蚀方法 |

| US11222820B2 (en) * | 2018-06-27 | 2022-01-11 | International Business Machines Corporation | Self-aligned gate cap including an etch-stop layer |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2740087B2 (ja) * | 1992-08-15 | 1998-04-15 | 株式会社東芝 | 半導体集積回路装置の製造方法 |

| US5427964A (en) * | 1994-04-04 | 1995-06-27 | Motorola, Inc. | Insulated gate field effect transistor and method for fabricating |

| JP3219996B2 (ja) * | 1995-03-27 | 2001-10-15 | 株式会社東芝 | 半導体装置及びその製造方法 |

| JP3199015B2 (ja) * | 1998-02-04 | 2001-08-13 | 日本電気株式会社 | 半導体装置及びその製造方法 |

| US6063680A (en) * | 1998-02-19 | 2000-05-16 | Texas Instruments - Acer Incorporated | MOSFETS with a recessed self-aligned silicide contact and an extended source/drain junction |

| JP3547419B2 (ja) * | 2001-03-13 | 2004-07-28 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US6506637B2 (en) * | 2001-03-23 | 2003-01-14 | Sharp Laboratories Of America, Inc. | Method to form thermally stable nickel germanosilicide on SiGe |

| TWI284348B (en) * | 2002-07-01 | 2007-07-21 | Macronix Int Co Ltd | Method for fabricating raised source/drain of semiconductor device |

-

2002

- 2002-09-13 JP JP2002268970A patent/JP2004111479A/ja active Pending

-

2003

- 2003-09-08 CN CNB031567274A patent/CN1252834C/zh not_active Expired - Fee Related

- 2003-09-09 KR KR10-2003-0062948A patent/KR100508840B1/ko not_active Expired - Fee Related

- 2003-09-10 TW TW092125040A patent/TW200406849A/zh unknown

- 2003-09-12 US US10/660,555 patent/US20040113209A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| KR100508840B1 (ko) | 2005-08-18 |

| US20040113209A1 (en) | 2004-06-17 |

| CN1495911A (zh) | 2004-05-12 |

| TW200406849A (en) | 2004-05-01 |

| JP2004111479A (ja) | 2004-04-08 |

| KR20040024501A (ko) | 2004-03-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6806534B2 (en) | Damascene method for improved MOS transistor | |

| KR100440840B1 (ko) | 반도체 장치의 제조 방법 및 반도체 장치 | |

| CN1252834C (zh) | 用自对准硅化物工艺形成的mosfet及其制造方法 | |

| US7453120B2 (en) | Semiconductor structure | |

| CN1655332A (zh) | 一种制造半导体器件的方法及其半导体器件 | |

| CN1175321A (zh) | 具有超浅端区的新型晶体管及其制造方法 | |

| KR100526366B1 (ko) | 반도체 장치와 그 제조 방법 | |

| US6747316B2 (en) | Surface-channel metal-oxide semiconductor transistors, their complementary field-effect transistors and method of producing the same | |

| US8816448B2 (en) | Semiconductor device and manufacturing method thereof | |

| US7545006B2 (en) | CMOS devices with graded silicide regions | |

| US20060046367A1 (en) | Method to selectively recess ETCH regions on a wafer surface using capoly as a mask | |

| US7141467B2 (en) | Semiconductor device having metal silicide films formed on source and drain regions and method for manufacturing the same | |

| CN1365146A (zh) | 半导体器件及其制造方法 | |

| JP3676276B2 (ja) | 半導体装置及びその製造方法 | |

| US20070257303A1 (en) | Transistor and method for forming the same | |

| US7416934B2 (en) | Semiconductor device | |

| JP2004253778A (ja) | 半導体装置及びその製造方法 | |

| CN1819267A (zh) | 半导体器件及其制造方法 | |

| US7427796B2 (en) | Semiconductor device and method of manufacturing a semiconductor device | |

| CN1127765C (zh) | 互补型金属氧化物晶体管半导体器件及其制造方法 | |

| US7544553B2 (en) | Integration scheme for fully silicided gate | |

| JP3918218B2 (ja) | 半導体装置の製造方法 | |

| JP2003179158A (ja) | 半導体装置及びその製造方法 | |

| JP2007305889A (ja) | 半導体装置およびその製造方法 | |

| JPH11214687A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C19 | Lapse of patent right due to non-payment of the annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |