CN106537683B - 多层基板上信号的耦合 - Google Patents

多层基板上信号的耦合 Download PDFInfo

- Publication number

- CN106537683B CN106537683B CN201580034311.2A CN201580034311A CN106537683B CN 106537683 B CN106537683 B CN 106537683B CN 201580034311 A CN201580034311 A CN 201580034311A CN 106537683 B CN106537683 B CN 106537683B

- Authority

- CN

- China

- Prior art keywords

- coupler

- dielectric material

- conductive layer

- signal line

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01P—WAVEGUIDES; RESONATORS, LINES, OR OTHER DEVICES OF THE WAVEGUIDE TYPE

- H01P3/00—Waveguides; Transmission lines of the waveguide type

- H01P3/02—Waveguides; Transmission lines of the waveguide type with two longitudinal conductors

- H01P3/08—Microstrips; Strip lines

- H01P3/081—Microstriplines

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01P—WAVEGUIDES; RESONATORS, LINES, OR OTHER DEVICES OF THE WAVEGUIDE TYPE

- H01P3/00—Waveguides; Transmission lines of the waveguide type

- H01P3/02—Waveguides; Transmission lines of the waveguide type with two longitudinal conductors

- H01P3/026—Coplanar striplines [CPS]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01P—WAVEGUIDES; RESONATORS, LINES, OR OTHER DEVICES OF THE WAVEGUIDE TYPE

- H01P3/00—Waveguides; Transmission lines of the waveguide type

- H01P3/02—Waveguides; Transmission lines of the waveguide type with two longitudinal conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01P—WAVEGUIDES; RESONATORS, LINES, OR OTHER DEVICES OF THE WAVEGUIDE TYPE

- H01P5/00—Coupling devices of the waveguide type

- H01P5/02—Coupling devices of the waveguide type with invariable factor of coupling

- H01P5/022—Transitions between lines of the same kind and shape, but with different dimensions

- H01P5/028—Transitions between lines of the same kind and shape, but with different dimensions between strip lines

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0216—Reduction of cross-talk, noise or electromagnetic interference

- H05K1/0228—Compensation of cross-talk by a mutually correlated lay-out of printed circuit traces, e.g. for compensation of cross-talk in mounted connectors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0237—High frequency adaptations

- H05K1/0242—Structural details of individual signal conductors, e.g. related to the skin effect

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Structure Of Printed Boards (AREA)

- Cable Transmission Systems, Equalization Of Radio And Reduction Of Echo (AREA)

Abstract

一种信号分配结构,包括:介电材料;在介电材料的第一层面上的上覆导电层;在介电材料的第二层面上的第一信号线,第一信号线通过介电材料与上覆导电层物理隔开;其中上覆导电层包括平行于第一信号线延伸的窗口,并且还在该窗口内包括在介电材料的第一层面上的第一耦合器电极,该第一耦合器电极在第一信号线上方、与其平行并且通过介电材料与其电隔离,其中第一耦合器电极沿着其外围的至少大部分与上覆导电层电隔离。

Description

本申请要求援引根据35U.S.C.§119(e)于2014年6月23日提交的标题为“MethodforTransmissionandCouplingofSignalson Multi-LayerBoardswithMinimumInterference”的临时申请序列No.62/015,604的权益,该申请的全部内容通过引用被结合于此。

技术领域

所描述的发明一般而言涉及印刷电路板(PCB)和其它多层基板上的高频信号分配并且涉及经由耦合器的线路分接。

背景技术

高频信号传输最常见地是点到点。功率在源(发送器)生成,并且经由传输线被输送到负载(接收器)。在这种情况下,接收器通常包括等于传输线的特征阻抗的端接电阻。所发送的信号功率在这个电阻中耗散,并且不从接收器发生信号反射。

在一些应用中,期望将信号从单个发送器发送到沿线路顺序布置的多个接收器。在这种情况下,每个接收器必须仅接收所发送功率的一部分,因为功率在所有接收器之间共享。此外,在每个接收器的信号相对于发送器以由接收器的位置确定的特有延迟到达。在这种情况下,信号传输路径中的阻抗不连续性是不期望的,因为它们引起干扰原始发送信号的反射。在这种布置中,仅仅简单的端接电阻不足以保证信号的完整性。此外,需要一种装置来将发送的信号功率的一部分耦合到沿线路布置的每个接收器。对这些耦合器的必要需求是它们不能产生会引起信号反射的局部阻抗不连续性。

相反的情况也会发生,其中多个发送器沿传输线串行布置,连接到位于线路末端的公共接收器。在这种情况下,期望在接收器聚合所有发送器的信号功率。类似于上面的情况,各种信号各自具有由发送器相对于接收器的位置确定的特有延迟。而且,就像在上面的情况下,信号反射是干扰源。对于在发送器和传输线之间耦合信号功率的结构的需求与上面的情况中相同。

更一般而言,可以利用有源电路系统来组合如上所述的分配网络,使得在一些操作模式下,位于线路端部的电路向沿线路串行布置的多个接收器发送,而在其它模式下,位于线路端部的电路从沿线路串行布置的多个发送器接收信号。

发明内容

本文描述的实施例采用用于在诸如PCB的平面技术中分配信号的方法。提供了一个或多个耦合器,以将来自传输线的信号电耦合到沿线路布置的发送器或接收器,而不引起明显的信号反射发生。

一般而言,在一方面,本发明的特征在于一种信号分配结构,包括:介电材料;在介电材料的第一层面上的上覆导电层;在介电材料的第二层面上的第一信号线,第一信号线通过介电材料与上覆导电层物理隔开;其中上覆导电层包括平行于第一信号线延伸的窗口,并且还在该窗口内包括在介电材料的第一层面上的第一耦合器电极,第一耦合器电极在第一信号线上方、与其平行并且通过介电材料与其电隔离,其中第一耦合器电极沿着其外围的至少大部分与上覆导电层电隔离。

一般而言,在另一方面,本发明的特征在于一种信号分配结构,包括:介电材料;在介电材料的第一层面上的上覆导电层;在介电材料的第二层面上的第一和第二并行信号线,第一和第二信号线通过介电材料与上覆导电层物理隔开;其中上覆导电层包括平行于第一和第二信号线延伸的窗口,并且还在该窗口内包括在介电材料的第一层面上的第一耦合器电极和第二耦合器电极,第一耦合器电极在第一信号线上方、与其平行并且通过介电材料与其电隔离并且第二耦合器电极在第二信号线上方、与其平行并且通过介电材料与其电隔离,其中第一和第二耦合器电极中的每一个沿着其外围的至少大部分与上覆导电层电隔离。

其它实施例具有以下特征中的一个或多个。信号分配结构还包括在介电材料的第三层面上的底层导电层,其中介电材料的第二层面在介电材料的第一和第三层面之间。第一和第二耦合器电极中的每一个是彼此物理隔开并且与上覆导电层物理隔开的金属孤岛(island)。信号分配结构还包括将第一耦合器电极的一端电连接到上覆导电层的第一电阻元件和将第二耦合器电极的一端电连接到上覆导电层的第二电阻元件。第一和第二耦合器电极中的每一个在其一端物理接触上覆导电层。第一耦合器电极包括用于电连接到第一耦合器电极的接触焊盘区域,第二耦合器电极包括用于电连接到第二耦合器电极的接触焊盘区域。第一和第二耦合器电极上的接触焊盘区域分别位于第一和第二耦合器电极的一端。第一和第二信号线与上覆导电层和底层导电层分别位于其上的第一和第三层面等距。信号分配结构还包括穿过介电材料并将上覆和底层导电层电连接在一起的多个导电通孔。第一信号线位于第一耦合器电极下方的部分与第一信号线位于上覆导电层下方的部分相比具有不同的宽度,并且第二信号线位于第二耦合器电极下方的部分与第二信号线位于上覆导电层下方的部分相比具有不同的宽度。介电材料以及上覆和底层导电层是利用印刷电路板技术制造的。第一和第二信号线与上覆导电层和底层导电层组合形成屏蔽的差分传输线。

一般而言,在还有另一方面,本发明的特征在于一种信号分配系统,该系统包括具有上述类型的耦合器结构序列的传输线,其中耦合器结构沿着传输线从第一端到第二端依次布置。

其它实施例可以包括以下特征中的一个或多个。传输线包括:介电材料;在介电材料的第一层面上的上覆导电层;在介电材料内的第二层面上的第一和第二并行信号线,第一和第二信号线通过介电材料与上覆导电层物理隔开。每个耦合器结构包括:在上覆导电层中平行于第一和第二信号线延伸的窗口;以及在该窗口内在介电材料的第一层面上的第一耦合器电极和第二耦合器电极,第一耦合器电极平行于第一耦合线路并通过介电材料与其电隔离并且第二耦合器电极平行于第二耦合线路并通过介电材料与其电隔离,其中第一和第二耦合器电极中的每一个沿其外围的至少大部分与上覆导电层电隔离。

还有其它实施例可以包括以下特征中的一个或多个。信号分配系统还包括在介电材料的第三层面上的底层导电层,其中介电材料的第二层面在介电材料的第一和第三层面之间。多个耦合器结构中每个相继的耦合器结构的耦合器电极比耦合器结构序列中的前一耦合器结构的耦合器电极长。在耦合器结构序列的每个耦合器结构中,第一和第二耦合器电极中的每一个是彼此物理隔开并且与上覆导电层物理隔开的金属孤岛,在这种情况下,耦合器结构序列的每个耦合器结构还可以包括将那个耦合器结构的第一耦合器电极的一端电连接到上覆导电层的第一电阻元件和将那个耦合器结构的第二耦合器电极的一端电连接到上覆导电层的第二电阻元件。在耦合器结构序列的每个耦合器结构中,那个耦合器结构的第一和第二耦合器电极中的每一个在一端物理接触上覆导电层。

在附图和下面的描述中阐述本发明的一个或多个实施例的细节。从说明书和附图以及从权利要求书中,本发明的其它特征、目的和优点将显而易见。

附图说明

图1示出了简单的点到点信号互连的示意图。

图2示出了从公共发送器到沿传输线串行布置的多个接收器的信号分配的示意图。

图3示出了从沿传输线串行布置的多个发送器到公共接收器的信号分配的示意图。

图4示出了一般的双模式串行信号分配网络的示意图。

图5示出了被用来在多层平面技术中实现均匀屏蔽差分传输线的典型结构的横截面。

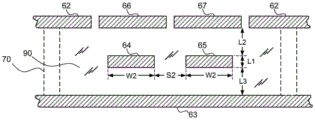

图6示出了与图8中所示的传输线相关联使用的耦合器结构。

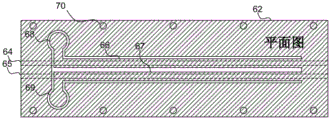

图7示出了电容型耦合器的平面图。

图8示出了感应型耦合器的平面图。

图9示出了具有到地平面的电阻连接的耦合器的平面图。

具体实施方式

图1示出了用于点到点信号传输的公共电路的示意图。这种简单的布置包括发送器11、接收器12和传输线1。物理传输线通常由促进电流从发送器的输出流到接收器的输入的导电通路(例如,电线)组成,以及允许相反的电流从接收器返回到发送器的第二导电通路。在包括多于一条这种通路的系统中,返回通路有时由多条传输线共享,在这种情况下,传输线常常被称为“单端”。在其它这样的系统中,每条传输线设有特有的返回通路,在这种情况下,传输线常常被称为“差分”。

所发送信号的各种频率成分作为波沿着传输线传播。尤其是对于高频成分,传输线的物理长度可以是那个成分的波长的很大的一部分。在这种情况下,接收到的信号的完整性会由于传输线上存在反射信号而降级。为了维持信号的完整性,通常的做法是在接收器提供端接电阻20。如果这个端接电阻的值与传输线的特征阻抗匹配,则信号功率在该电阻中耗散并且不发生信号反射。

在一些应用中,期望向沿着传输线布置的多个接收器发送信号,如图2中所示。在这种布置中,接收器共享总发送功率,因此每个接收器仅接收发送功率的一部分。为了促进这种布置,有利的是提供用于将来自传输线的信号耦合到每个接收器的耦合器30。除了控制传输线和接收器之间的信号耦合,耦合器30不应当引起传输线的特征阻抗的明显的局部变化,因为这会引起将降级所接收的信号的完整性的不期望的信号反射。而且,在一些信号功率没有分配到接收器的常见情况下,在传输线的终端处提供电阻20,以避免功率在那个点的反射。

图3示出了相反的情况,其中沿线路布置的多个发送器将信号功率输送到公共接收器。在这个布置中可以使用类似的耦合器结构。如在上述情况下,类似地期望耦合器在传输线的特征阻抗中引入可忽略的局部变化。

这些布置的一般化在图4中示出,其中使用双模式发送器-接收器电路13。利用这种类型的布置,多个接收器或发送器可以分别共享公共发送器或接收器,这取决于所选择的有源电路系统的操作模式。对于耦合结构的相同设计考虑适用于任一模式。

低反射、紧凑、宽带的差分耦合器

除了信号线本身之外,图4中所示的串行分布网络中的关键结构还有耦合器30。为了维持良好的信号完整性,耦合器的期望特性是它们在分布传输线中引入最小的信号反射。这要求主传输线的特征阻抗不受耦合器存在的干扰。满足这个标准由于大多数平面技术中通常存在的制造变化而变得复杂。这些变化导致传输线的特征阻抗的变化。因此,期望设计这样的耦合结构,其中影响传输线的制造变化也以类似的方式影响耦合器,使得不管变化如何,信号反射都被最小化。

定向耦合器通常在微波系统中被用来将信号能量的一部分从主信号传输线转移到另一辅助线路上,而不引起可感知的信号反射。在平面技术中,定向耦合器通常由一对传输线形成,传输线的长度等于在期望中心工作频率处的传输线中的信号波长的四分之一。两条线路放在邻近处,导致它们之间的电磁耦合。通过结构尺寸的适当选择,有可能实现具有期望的耦合强度特性和特征阻抗特性的耦合器。此外,这些结构表现出方向性的特性,其中从一条线路耦合到另一条线路的信号优先在一个方向流动。意在在宽频率范围上表现出耦合强度和方向性的复杂耦合器是通过级联耦合线路的多个四分之一波长区段来产生的。

当在与它们连接的线路相同的平面结构中实现时,这些常规的定向耦合器表现出对上述制造变化的不敏感性的期望特性。耦合器中耦合的传输线的结构通常类似于耦合器连接到的主传输线的结构。因此,影响传输线的特征阻抗的结构和材料变化通常对耦合器的特征阻抗具有类似的影响。在一些应用中,这些类型的耦合器的缺点是其大物理尺寸。

下面描述的实施例可以用在需要紧凑结构的应用中。在这种情况下,有可能在基本上短于信号波长四分之一的更紧凑的结构中,在宽频率范围上获得适当的耦合。

图5示出了用来在诸如PCB的多层平面技术中实现均匀屏蔽的差分传输线的典型结构的横截面。在该结构中,信号线60和61的差分对在具有形成环绕屏蔽结构的上覆层62和底层63的金属层中形成。这些屏蔽层通常通过沿垂直于横截面的线路的长度并按间隔放置的垂直导电通孔70电连接。环绕屏蔽结构的电位通常被作为参考(“地”),并且差分信号线上的电位相对于这个参考对称地变化,具有相等的振幅和相反的符号。金属平面之间的区域由电介质90填充。

在差分传输线中,两条信号线60和61的宽度W1完全相同。差分特征阻抗由线路宽度W1和间隔S1以及结构的垂直尺寸L1、L2和L3确定。

线路宽度和间隔通常与电介质厚度相当。例如,在所述实施例中,每个介电层的厚度为250微米(0.25mm),线路宽度为200微米,并且间距为250。

耦合器结构在图6中以横截面示出。耦合器内的信号线64和65分别直接连接到耦合器区域外的传输线中的信号线60和61,但它们的尺寸S2和W2可以不同。具有相同宽度的耦合器电极66和67在外屏蔽62中形成。这些电极沿线路延伸某个期望的长度。在操作中,沿差分传输线64和65传递的信号将分别在耦合器电极66和67中感应出差分电压和/或电流。耦合信号强度部分地由电极的长度确定。

从图5和图6的检查可以看出,两个图中的信号线的结构相似。基于电磁仿真和分析,可以选择耦合器中的线路的尺寸S2和W2,使得耦合器中的线路的特征阻抗与耦合器外部的线路紧密匹配,由此最小化在两者之间的连接处的信号反射。如果耦合器电极上的感应电压相对于信号线上的电压较小,则围绕传输线的场分布不会由于电极的存在而被大大扰动,因为它们的电位与屏蔽的电位没有很大不同。在那种情况下,耦合器内部和外部的信号线宽度W2和W1将类似,间隔S2和S1也是如此。

在耦合器内部和外部的线路的尺寸被调节为产生类似的特征阻抗并且线路的尺寸在两种情况下相似的情况下,制造中影响其中一个的特征阻抗的结构和材料变化对另一个具有类似的影响。在这种情况下,当耦合器在如上所述的串行分布网络中被使用时,它们将不会通过信号反射的引入而显著地降级信号完整性。而且,引起传输线的特征阻抗改变的制造变化将引起耦合器结构的类似变化,从而信号完整性得以维持。

这种类型的耦合器结构可以以三种不同的方式配置。图7示出了电容型耦合器的平面图。在这个图中,耦合器电极66和67与环绕屏蔽(地)62电隔离,如由环绕表示耦合器电极的金属膜孤岛的开放区域(无金属区域)所指示的。信号线64和65在耦合器电极下方通过。接触区域68和69偏离到侧面提供,以允许耦合器连接到外部电路。这种类型的耦合器主要是电容性的,因为在耦合器电极中感应出电压,但很小电流可以流过。当连接到高阻抗感应电路系统时,这些耦合器在宽频率范围内具有相对恒定的电压增益特点。通过改变耦合器电极的长度来调节电压增益。

类似的感应耦合器的平面图在图8中示出。它具有与其电容性对应物相同的结构特征。唯一的结构差异是在图的右手侧的电极(即,与具有接触焊盘的端部相对的端部)连接到地平面62。这种耦合器类型主要是感应性的,因为电流在耦合器电极中被感应出来,但是产生很小的电压。当连接到低阻抗有源电路时,这种类型的耦合器在宽频率范围内具有相对平坦的电流增益。

电阻连接的耦合器的平面图在图9中示出。在这种结构中,附加的电阻器100将电极连接到地平面。由于该电阻连接,在耦合器电极上感应出的信号是电流和电压的组合,因此这种耦合器类型是图7和8所示类型的混合。而且,通过适当选择在连接中使用的电阻100的结构尺寸和电阻值,这些耦合器表现出期望的方向性,即使它们大大短于在常规定向耦合器中使用的四分之一波长。常规的四分之一波长耦合器在对应的四分之一波长频率附近具有恒定的振幅频率响应。这些短耦合器一般在其响应的振幅中显示出更大的频率依赖性。

如上所述,这些类型的耦合器在需要将信号串行分布到许多接收器的应用中是有用的,如图2中所示。在这种情况下,常常期望在所有接收器12处维持几乎恒定的信号强度。但是,由于分配传输线1中固有的信号损耗,并且由于链路中的每个耦合器从线路提取少量功率,因此线路中的信号强度将随着距发送器11的距离的增加而衰减。这些损耗可以通过修改链路中每个耦合器的长度来补偿,使得信号最强的发送器附近的耦合器更短,从而给予它们更少的增益,而信号最弱的链路端部的耦合器更长,从而给予它们更多的增益。通过对耦合器的长度的适当调节,可以使每个接收器处的信号强度相同。

类似的情况在需要许多信号的串行聚合的应用中发生,如图3中所示。在这种情况下,源自离接收器20最远的信号在沿着分布线路1行进时将遭受最大的衰减。这种衰减可以通过调节耦合器的长度来补偿,使得从每个发送器11到公共接收器20的增益几乎相等(例如,通过使离接收器最远的耦合器的长度更长)。以这种方式,接收到的聚合信号表示所有单独发送信号的几乎相等的总和。

常规的定向耦合器是直接物理连接到配电线路的分立部件。为了将它们插入配电线路,必须断开线路。因此,配电线在一个端子端口进入耦合器并从另一个端子端口出来。耦合器中的内部连接提供进入和离开线路之间的电路径的连续性。因为主配电线路和耦合器是在两种不同的技术实现中制造的,所以制造变化将导致它们的传输线特点稍有不同,从而导致阻抗不连续和信号反射。这些反射会损害电路的功能,尤其是在其影响可能累积的串行分布网络中。上述类型的集成耦合器不会受到这种影响。与常规的分立实现相比,布置在以公共技术实现的串行配置中的两个或更多个此类耦合器的复合结构构成了具有优良质量的新颖结构。

在图7、8和9所示的实施例中,触点或焊盘区域68和69被示为偏离到侧面,使得它们不会在下层上的耦合器信号线64和65的上方。这样做是因为假设本公开内容中描述的三层金属具有在这些层之上的其它层,即,它们是更大的多层堆叠的一部分。换句话说,假设两个焊盘68和69将被埋在堆叠的中间。在那种情况下,为了与它们进行垂直连接,需要使用钻孔。如果焊盘位于线路的顶部,则钻机将穿过信号线并且它们也将短路到在钻孔中形成的通孔。因此,焊盘被偏移,以避免对线路的干扰。

对于一些类型的电路板构造,这将是不必要的。如果上覆金属层在堆叠的顶部,则关于短路到下部金属层的担心不是问题,在这种情况下,接触区域可以直接在耦合器信号线路上方。

而且,应当指出,对于电容性耦合器,焊盘68和69可以位于沿耦合器长度的任何地方。但是,对于感应型耦合器,它们需要在与它们并入地平面的点相对的端部。

通常期望耦合器与线路中的二分之一波长相比更短,但那不是严格的要求。为了保持阻抗几乎恒定,耦合器的关键需求是其具有远小于一(unity)的电压增益。这确保耦合器电极大致类似于环绕的地平面,并且不会扰动电势分布太多。越长的耦合器积累越大的增益。在足够长的长度,它们开始表现得奇怪,并且会表现出不期望的共振。

常规的定向耦合器由四分之一波长传输线区段组成。宽带耦合器要求若干这样的四分之一波区段的级联,因此它们会相当大。例如,在1GHz,简单的四分之一波定向耦合器将为1.5英寸长。在110MHz中心频率下工作的电路板中的中频耦合器需要13.6英寸长。为了比较,使用本文所述结构的这些相同的耦合器小于1英寸长(分别具有200和250微米的线路宽度和间隔)。

对于PCB,可以使用各种众所周知的制造方法。它们主要由在两侧覆盖有铜箔的电介质(通常为玻璃增强树脂)片构成。电介质通常是用有机电介质(环氧树脂、聚酰亚胺、漆、特氟隆等)浸渍的玻璃纤维基体。有许多专有的树脂和玻璃配方。导体图案被蚀刻到箔中。这些片的多个层被对齐并与具有在未固化状态下更介电的中间层堆叠。它们被压在一起并加热,以层压出多层结构。然后,钻孔并镀上金属,以形成垂直的层到层通孔。

本文描述的技术特别适用于多点信号生成网络和低成本天线阵列,诸如分别在US8,259,884和US 8,611,959中描述的那些,这二者的内容整体上被结合于此。例如,参考'884专利中的图5,示出了两个树形网络,其中一个携带第一载波信号,而第二个携带第二载波信号。在各个地方,一个树形网络的分支与另一个树形网络的对应分支并排(例如“并行”)延伸。对于那个分支对,一个分支在一个方向携带第一载波信号,而另一个分支在另一个方向携带第二载波信号。沿着双并行传输线的长度,存在多个到达时间平均电路(ATAC),每个ATAC具有连接到传输线之一的一个输入和连接到另一传输线的第二输入。到ATAC电路的连接可以利用本文描述的耦合器来实现,以减少那些电路对通过双传输线的信号的影响。

其它实施例在以下权利要求书以内。

Claims (25)

1.一种信号分配结构,包括:

介电材料;

在介电材料的第一层面上的上覆导电层,所述上覆导电层包括被上覆导电层四面包围的窗口区域;

在介电材料的第一层面下的第二层面上的第一信号线,所述第一信号线通过介电材料与上覆导电层物理隔开,所述窗口区域覆盖所述第一信号线的一部分并平行于所述第一信号线的所述一部分延伸,其中,在所述第一信号线的所述一部分的每侧的第一信号线在所述上覆导电层的下方穿过;

在介电材料的第一层面上并位于所述窗口区域内的第一耦合器电极,所述第一耦合器电极在第一信号线上方、与其平行并且通过介电材料与其电隔离,

其中第一耦合器电极比所述第一信号线短,并且第一耦合器电极沿着其外围的至少大部分与上覆导电层电隔离。

2.如权利要求1所述的信号分配结构,还包括:

在介电材料的第二层面上的第二信号线,所述第二信号线平行于第一信号线并且通过介电材料与上覆导电层物理隔开,所述窗口区域覆盖所述第二信号线的一部分并平行于所述第二信号线的所述一部分延伸,其中,在第二信号线的所述一部分的每侧的第二信号线在所述上覆导电层的下方穿过;

在介电材料的第一层面上并位于所述窗口区域内的第二耦合器电极,所述第二耦合器电极在第二信号线上方、与其平行并且通过介电材料与其电隔离,

其中第二耦合器电极比所述第二信号线短,并且第二耦合器电极沿着其外围的至少大部分与上覆导电层电隔离。

3.如权利要求2所述的信号分配结构,还包括在介电材料的第三层面上的底层导电层,其中介电材料的第二层面在介电材料的第一和第三层面之间。

4.如权利要求3所述的信号分配结构,其中第一和第二耦合器电极中的每一个是彼此物理隔开并且与上覆导电层物理隔开的金属孤岛。

5.如权利要求4所述的信号分配结构,还包括将第一耦合器电极的一端电连接到上覆导电层的第一电阻元件。

6.如权利要求5所述的信号分配结构,还包括将第二耦合器电极的一端电连接到上覆导电层的第二电阻元件。

7.如权利要求3所述的信号分配结构,其中第一和第二耦合器电极中的每一个在其一端物理接触并电接触上覆导电层。

8.如权利要求2所述的信号分配结构,其中第一耦合器电极包括用于电连接到第一耦合器电极的接触焊盘区域,并且其中第二耦合器电极包括用于电连接到第二耦合器电极的接触焊盘区域。

9.如权利要求8所述的信号分配结构,其中第一和第二耦合器电极上的接触焊盘区域分别位于第一和第二耦合器电极的一端。

10.如权利要求3所述的信号分配结构,其中第一和第二信号线与上覆导电层和底层导电层分别位于其上的第一和第三层面等距。

11.如权利要求3所述的信号分配结构,还包括穿过介电材料并将上覆和底层导电层电连接在一起的多个导电通孔。

12.如权利要求3所述的信号分配结构,其中第一信号线位于第一耦合器电极下方的部分与第一信号线位于上覆导电层下方的部分相比具有不同的宽度,并且第二信号线位于第二耦合器电极下方的部分与第二信号线位于上覆导电层下方的部分相比具有不同的宽度。

13.如权利要求3所述的信号分配结构,其中介电材料以及上覆和底层导电层是利用印刷电路板技术制造的。

14.如权利要求3所述的信号分配结构,其中第一和第二信号线与上覆导电层和底层导电层组合形成屏蔽的差分传输线。

15.如权利要求1所述的信号分配结构,其中,第一耦合器电极是与上覆导电层物理隔开和电隔离的金属孤岛。

16.如权利要求15所述的信号分配结构,还包括在介电材料的第三层面上的底层导电层,其中介电材料的第二层面在介电材料的第一和第三层面之间。

17.如权利要求16所述的信号分配结构,还包括穿过介电材料并将上覆和底层导电层电连接在一起的多个导电通孔。

18.一种信号分配系统,包括具有沿着传输线从第一端到第二端依次布置的耦合器结构序列的传输线,

其中传输线包括:

介电材料;

在介电材料的第一层面上的上覆导电层,所述上覆导电层包括多个窗口区域,所述多个窗口区域中的每个窗口区域被上覆导电层四面包围;

在介电材料中的第二层面上的第一信号线,所述第一信号线通过介电材料与上覆导电层物理隔开,所述多个窗口区域中的每个窗口区域覆盖第一信号线的对应不同部分并平行于所述第一信号线的所述对应不同部分延伸,其中在第一信号线的每个对应不同部分的每侧上的第一信号线在上覆导电层的下方穿过;

其中耦合器结构序列的每个耦合器结构包括:

在介电材料的第一层面上并位于对应的不同窗口区域内的第一耦合器电极,其中所述第一耦合器电极与第一信号线平行并且通过介电材料与其电隔离,其中第一耦合器电极比所述第一信号线短并且第一耦合器电极沿着其外围的至少大部分与上覆导电层电隔离。

19.如权利要求18所述的信号分配系统,其中传输线还包括在介电材料的第二层面上的第二信号线,所述第二信号线平行于第一信号线并且通过介电材料与上覆导电层物理隔开;并且其中耦合器结构序列的每个耦合器结构还包括在介电材料的第一层面上的第二耦合器电极,所述第二耦合器电极在第二信号线上方、与其平行并且通过介电材料与其电隔离,其中第二耦合器电极沿着其外围的至少大部分与上覆导电层电隔离。

20.如权利要求19所述的信号分配系统,还包括在介电材料的第三层面上的底层导电层,其中介电材料的第二层面在介电材料的第一和第三层面之间。

21.如权利要求19所述的信号分配系统,其中多个耦合器结构中每个相继的耦合器结构的第一耦合器电极和第二耦合器电极比耦合器结构序列中的前一耦合器结构的第一耦合器电极和第二耦合器电极长。

22.如权利要求21所述的信号分配系统,其中,在耦合器结构序列的每个耦合器结构中,第一和第二耦合器电极中每一个是彼此物理隔开并与上覆导电层物理隔开的金属孤岛。

23.如权利要求22所述的信号分配系统,其中耦合器结构序列的每个耦合器结构还包括将耦合器结构的第一耦合器电极的一端电连接到上覆导电层的第一电阻元件。

24.如权利要求23所述的信号分配系统,其中耦合器结构序列的每个耦合器结构还包括将耦合器结构的第二耦合器电极的一端电连接到上覆导电层的第二电阻元件。

25.如权利要求21所述的信号分配系统,其中,在耦合器结构序列的每个耦合器结构中,耦合器结构的第一和第二耦合器电极中每一个在一端物理接触上覆导电层。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201462015604P | 2014-06-23 | 2014-06-23 | |

| US62/015,604 | 2014-06-23 | ||

| PCT/US2015/036891 WO2015200171A1 (en) | 2014-06-23 | 2015-06-22 | Coupling of signals on multi-layer substrates |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN106537683A CN106537683A (zh) | 2017-03-22 |

| CN106537683B true CN106537683B (zh) | 2020-03-13 |

Family

ID=53541916

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201580034311.2A Active CN106537683B (zh) | 2014-06-23 | 2015-06-22 | 多层基板上信号的耦合 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US20150373837A1 (zh) |

| EP (1) | EP3158605A1 (zh) |

| JP (2) | JP6526069B2 (zh) |

| KR (1) | KR20170023095A (zh) |

| CN (1) | CN106537683B (zh) |

| WO (2) | WO2015200163A1 (zh) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20180029944A (ko) | 2014-06-12 | 2018-03-21 | 스카이워크스 솔루션즈, 인코포레이티드 | 지향성 커플러들에 관련된 디바이스들 및 방법들 |

| US9496902B2 (en) | 2014-07-24 | 2016-11-15 | Skyworks Solutions, Inc. | Apparatus and methods for reconfigurable directional couplers in an RF transceiver with selectable phase shifters |

| TWI720014B (zh) | 2015-09-10 | 2021-03-01 | 美商西凱渥資訊處理科技公司 | 用於多頻功率偵測之電磁耦合器及具有電磁耦合器之系統 |

| TWI716539B (zh) | 2016-02-05 | 2021-01-21 | 美商天工方案公司 | 具有多波段濾波的電磁耦合器 |

| US9960747B2 (en) | 2016-02-29 | 2018-05-01 | Skyworks Solutions, Inc. | Integrated filter and directional coupler assemblies |

| TW201801360A (zh) | 2016-03-30 | 2018-01-01 | 天工方案公司 | 用於耦合器線性改良及重組態的可調主動矽 |

| CN109314299B (zh) * | 2016-04-29 | 2021-09-21 | 天工方案公司 | 可调谐电磁耦合器和使用其的模块和装置 |

| TWI735568B (zh) | 2016-04-29 | 2021-08-11 | 美商天工方案公司 | 補償電磁耦合器 |

| US10284167B2 (en) | 2016-05-09 | 2019-05-07 | Skyworks Solutions, Inc. | Self-adjusting electromagnetic coupler with automatic frequency detection |

| US10164681B2 (en) | 2016-06-06 | 2018-12-25 | Skyworks Solutions, Inc. | Isolating noise sources and coupling fields in RF chips |

| CN109565292B (zh) | 2016-06-22 | 2021-02-05 | 天工方案公司 | 用于多频功率检测的电磁耦合器装置和包含其的设备 |

| CN107546486B (zh) * | 2016-06-23 | 2021-06-29 | 康普技术有限责任公司 | 具有恒定反转相位的天线馈送元件 |

| US10426023B2 (en) * | 2017-02-14 | 2019-09-24 | The Regents Of The University Of California | Systematic coupling balance scheme to enhance amplitude and phase matching for long-traveling multi-phase signals |

| US10742189B2 (en) | 2017-06-06 | 2020-08-11 | Skyworks Solutions, Inc. | Switched multi-coupler apparatus and modules and devices using same |

| JP7001158B2 (ja) * | 2018-06-07 | 2022-01-19 | 株式会社村田製作所 | 多層基板、電子機器および多層基板の製造方法 |

| US10813211B2 (en) * | 2018-12-14 | 2020-10-20 | Dell Products L.P. | Printed circuit board layout for mitigating near-end crosstalk |

| JP2021034536A (ja) * | 2019-08-23 | 2021-03-01 | 日本特殊陶業株式会社 | 配線基板 |

| CN111430863A (zh) * | 2019-12-16 | 2020-07-17 | 瑞声科技(新加坡)有限公司 | 传输线以及终端设备 |

| CN114552155B (zh) * | 2022-04-25 | 2022-07-05 | 电子科技大学成都学院 | 双模传输线 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5638402A (en) * | 1993-09-27 | 1997-06-10 | Hitachi, Ltd. | Fast data transfer bus |

| US6600790B1 (en) * | 1996-10-30 | 2003-07-29 | Hitachi, Ltd. | Gap-coupling bus system |

| CN1659499A (zh) * | 2002-07-01 | 2005-08-24 | 株式会社瑞萨科技 | 等振幅方向性耦合式总线系统 |

| US7271985B1 (en) * | 2004-09-24 | 2007-09-18 | Storage Technology Corporation | System and method for crosstalk reduction in a flexible trace interconnect array |

| CN102484505A (zh) * | 2009-09-01 | 2012-05-30 | 日本电气株式会社 | 通信系统和通信装置 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3942164A (en) * | 1975-01-30 | 1976-03-02 | Semi, Inc. | Sense line coupling reduction system |

| US5430247A (en) | 1993-08-31 | 1995-07-04 | Motorola, Inc. | Twisted-pair planar conductor line off-set structure |

| US5389735A (en) * | 1993-08-31 | 1995-02-14 | Motorola, Inc. | Vertically twisted-pair planar conductor line structure |

| EP1014471A1 (en) * | 1998-12-24 | 2000-06-28 | Kabushiki Kaisha Toyota Chuo Kenkyusho | Waveguide-transmission line transition |

| JP3880286B2 (ja) * | 1999-05-12 | 2007-02-14 | エルピーダメモリ株式会社 | 方向性結合式メモリシステム |

| JP2001044712A (ja) * | 1999-07-28 | 2001-02-16 | Ricoh Co Ltd | ストリップ線路 |

| US7170361B1 (en) * | 2000-04-13 | 2007-01-30 | Micron Technology, Inc. | Method and apparatus of interposing voltage reference traces between signal traces in semiconductor devices |

| US6573801B1 (en) * | 2000-11-15 | 2003-06-03 | Intel Corporation | Electromagnetic coupler |

| US6703907B1 (en) | 2002-08-26 | 2004-03-09 | Inphi Corporation | Circuit technique for increasing effective inductance of differential transmission lines |

| US7307492B2 (en) * | 2002-11-27 | 2007-12-11 | Intel Corporation | Design, layout and method of manufacture for a circuit that taps a differential signal |

| US7002430B2 (en) * | 2003-05-30 | 2006-02-21 | Intel Corporation | Compact non-linear geometry electromagnetic coupler for use with digital transmission systems |

| US7265647B2 (en) * | 2004-03-12 | 2007-09-04 | The Regents Of The University Of California | High isolation tunable MEMS capacitive switch |

| FI121516B (fi) | 2004-03-25 | 2010-12-15 | Filtronic Comtek Oy | Suuntakytkin |

| US7280808B2 (en) * | 2004-04-12 | 2007-10-09 | Sony Ericsson Mobile Communications, Ab | Wireless communications devices including circuit substrates with partially overlapping conductors thereon coupling power to/from power amplifier systems |

| EP1788765B1 (en) * | 2005-11-18 | 2012-08-01 | STMicroelectronics Srl | Transmission system of a digital signal |

| FI20065144A (fi) | 2006-02-28 | 2007-08-29 | Filtronic Comtek Oy | Suuntakytkin |

| DE102007021615A1 (de) * | 2006-05-12 | 2007-11-15 | Denso Corp., Kariya | Dielektrisches Substrat für einen Wellenhohlleiter und einen Übertragungsleitungsübergang, die dieses verwenden |

| JP5409621B2 (ja) | 2007-07-20 | 2014-02-05 | ブルー ダニューブ ラブズ インク | 位相同期ローカルキャリアを有するマルチポイント信号発生の方法及びシステム |

| EP2068391A3 (de) | 2007-12-04 | 2010-01-20 | Rohde & Schwarz GmbH & Co. KG | Einrichtung mit überkreutzter Streifenleitung |

| US7830221B2 (en) * | 2008-01-25 | 2010-11-09 | Micron Technology, Inc. | Coupling cancellation scheme |

| US9288893B2 (en) * | 2009-02-11 | 2016-03-15 | Broadcom Corporation | Implementations of twisted differential pairs on a circuit board |

| JP5225188B2 (ja) * | 2009-04-23 | 2013-07-03 | 三菱電機株式会社 | 方向性結合器 |

| PL2489095T3 (pl) * | 2009-10-14 | 2018-03-30 | Landis+Gyr Ag | Sprzęgacz antenowy |

| PL2589108T3 (pl) | 2010-07-01 | 2018-09-28 | Blue Danube Systems, Inc. | Tanie aktywne szyki antenowe |

| KR101375938B1 (ko) * | 2012-12-27 | 2014-03-21 | 한국과학기술원 | 저전력, 고속 멀티-채널 유전체 웨이브가이드를 이용한 칩-대-칩 인터페이스 |

-

2015

- 2015-06-22 WO PCT/US2015/036881 patent/WO2015200163A1/en active Application Filing

- 2015-06-22 JP JP2016574466A patent/JP6526069B2/ja active Active

- 2015-06-22 KR KR1020177001537A patent/KR20170023095A/ko not_active Application Discontinuation

- 2015-06-22 EP EP15736717.8A patent/EP3158605A1/en not_active Ceased

- 2015-06-22 US US14/745,624 patent/US20150373837A1/en not_active Abandoned

- 2015-06-22 CN CN201580034311.2A patent/CN106537683B/zh active Active

- 2015-06-22 US US14/745,710 patent/US9653768B2/en active Active

- 2015-06-22 WO PCT/US2015/036891 patent/WO2015200171A1/en active Application Filing

-

2019

- 2019-02-28 JP JP2019036460A patent/JP2019165213A/ja not_active Withdrawn

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5638402A (en) * | 1993-09-27 | 1997-06-10 | Hitachi, Ltd. | Fast data transfer bus |

| US6600790B1 (en) * | 1996-10-30 | 2003-07-29 | Hitachi, Ltd. | Gap-coupling bus system |

| CN1659499A (zh) * | 2002-07-01 | 2005-08-24 | 株式会社瑞萨科技 | 等振幅方向性耦合式总线系统 |

| US7271985B1 (en) * | 2004-09-24 | 2007-09-18 | Storage Technology Corporation | System and method for crosstalk reduction in a flexible trace interconnect array |

| CN102484505A (zh) * | 2009-09-01 | 2012-05-30 | 日本电气株式会社 | 通信系统和通信装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20170023095A (ko) | 2017-03-02 |

| CN106537683A (zh) | 2017-03-22 |

| JP2017520923A (ja) | 2017-07-27 |

| JP6526069B2 (ja) | 2019-06-05 |

| US9653768B2 (en) | 2017-05-16 |

| US20150373837A1 (en) | 2015-12-24 |

| WO2015200163A1 (en) | 2015-12-30 |

| JP2019165213A (ja) | 2019-09-26 |

| WO2015200171A1 (en) | 2015-12-30 |

| EP3158605A1 (en) | 2017-04-26 |

| US20150372366A1 (en) | 2015-12-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN106537683B (zh) | 多层基板上信号的耦合 | |

| US10673113B2 (en) | Transmission line and electronic device | |

| CN101662882B (zh) | 高频宽带阻抗匹配的传输孔 | |

| US6614325B1 (en) | RF/IF signal distribution network utilizing broadside coupled stripline | |

| CN100556243C (zh) | 高频宽带阻抗匹配的传输孔 | |

| US20040248468A1 (en) | High data rate interconnecting device | |

| US10056669B2 (en) | Transmission line | |

| US11011815B2 (en) | Circularly-polarized dielectric waveguide launch for millimeter-wave data communication | |

| JP2006024618A (ja) | 配線基板 | |

| US6602078B2 (en) | Electrical interconnect having a multi-layer circuit board structure and including a conductive spacer for impedance matching | |

| US10524351B2 (en) | Printed circuit board (PCB) with stubs coupled to electromagnetic absorbing material | |

| TW201019801A (en) | High frequency circuit module | |

| US9408306B2 (en) | Antenna array feeding structure having circuit boards connected by at least one solderable pin | |

| JPH09191205A (ja) | 信号分離マイクロ波スプリッタ/コンバイナ | |

| US9147925B2 (en) | Antenna coupler | |

| US20130293317A1 (en) | Directional coupler | |

| EP1568099B1 (en) | A circuit that taps a differential signal | |

| WO2019220530A1 (ja) | 信号伝送構造、信号伝送構造の製造方法、および、高周波信号送受信装置 | |

| CN113131165B (zh) | 电路结构 | |

| US10601185B2 (en) | Differential transmission cable module | |

| CN205921814U (zh) | 一种电路板装置及电子设备 | |

| US20210273307A1 (en) | Transmission line | |

| US10952313B1 (en) | Via impedance matching | |

| US10673119B2 (en) | Highly directive electromagnetic coupler with electrically large conductor | |

| JP2005347924A (ja) | 高周波信号伝送線路基板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |