CN100440464C - 层叠型半导体器件以及层叠型电子部件的制造方法 - Google Patents

层叠型半导体器件以及层叠型电子部件的制造方法 Download PDFInfo

- Publication number

- CN100440464C CN100440464C CNB2006100584978A CN200610058497A CN100440464C CN 100440464 C CN100440464 C CN 100440464C CN B2006100584978 A CNB2006100584978 A CN B2006100584978A CN 200610058497 A CN200610058497 A CN 200610058497A CN 100440464 C CN100440464 C CN 100440464C

- Authority

- CN

- China

- Prior art keywords

- mentioned

- semiconductor element

- equal

- film

- bonding

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/27—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0105—Tin [Sn]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/095—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00 with a principal constituent of the material being a combination of two or more materials provided in the groups H01L2924/013 - H01L2924/0715

- H01L2924/097—Glass-ceramics, e.g. devitrified glass

- H01L2924/09701—Low temperature co-fired ceramic [LTCC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Die Bonding (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP092596/2005 | 2005-03-28 | ||

| JP092595/2005 | 2005-03-28 | ||

| JP2005092595A JP4612450B2 (ja) | 2005-03-28 | 2005-03-28 | 積層型半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1841688A CN1841688A (zh) | 2006-10-04 |

| CN100440464C true CN100440464C (zh) | 2008-12-03 |

Family

ID=37030623

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2006100584978A Active CN100440464C (zh) | 2005-03-28 | 2006-03-28 | 层叠型半导体器件以及层叠型电子部件的制造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP4612450B2 (enExample) |

| CN (1) | CN100440464C (enExample) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5680330B2 (ja) * | 2010-04-23 | 2015-03-04 | 株式会社東芝 | 半導体装置の製造方法 |

| TWI393494B (zh) | 2010-06-11 | 2013-04-11 | 欣興電子股份有限公司 | 具有線路的基板條及其製造方法 |

| CN102315202B (zh) * | 2010-07-02 | 2016-03-09 | 欣兴电子股份有限公司 | 具有线路的基板条及其制造方法 |

| JP5384443B2 (ja) * | 2010-07-28 | 2014-01-08 | 日東電工株式会社 | フリップチップ型半導体裏面用フィルム、ダイシングテープ一体型半導体裏面用フィルム、半導体装置の製造方法、及び、フリップチップ型半導体装置 |

| JP2013098240A (ja) * | 2011-10-28 | 2013-05-20 | Toshiba Corp | 記憶装置、半導体装置及び半導体装置の製造方法 |

| JP6220706B2 (ja) * | 2014-03-14 | 2017-10-25 | リンテック株式会社 | シート貼付装置および貼付方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08288455A (ja) * | 1995-04-11 | 1996-11-01 | Oki Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| JP2002222913A (ja) * | 2001-01-24 | 2002-08-09 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2004072009A (ja) * | 2002-08-09 | 2004-03-04 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2004193363A (ja) * | 2002-12-11 | 2004-07-08 | Fujitsu Ltd | 半導体装置及びその製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003041209A (ja) * | 2001-07-30 | 2003-02-13 | Hitachi Chem Co Ltd | 接着シートならびに半導体装置およびその製造方法 |

| JP3966808B2 (ja) * | 2002-12-03 | 2007-08-29 | 古河電気工業株式会社 | 粘接着テープ |

| JP4316253B2 (ja) * | 2003-02-18 | 2009-08-19 | リンテック株式会社 | ウエハダイシング・接着用シートおよび半導体装置の製造方法 |

| JP2005327789A (ja) * | 2004-05-12 | 2005-11-24 | Sharp Corp | ダイシング・ダイボンド兼用粘接着シートおよびこれを用いた半導体装置の製造方法 |

-

2005

- 2005-03-28 JP JP2005092595A patent/JP4612450B2/ja not_active Expired - Fee Related

-

2006

- 2006-03-28 CN CNB2006100584978A patent/CN100440464C/zh active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08288455A (ja) * | 1995-04-11 | 1996-11-01 | Oki Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| JP2002222913A (ja) * | 2001-01-24 | 2002-08-09 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2004072009A (ja) * | 2002-08-09 | 2004-03-04 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2004193363A (ja) * | 2002-12-11 | 2004-07-08 | Fujitsu Ltd | 半導体装置及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1841688A (zh) | 2006-10-04 |

| JP4612450B2 (ja) | 2011-01-12 |

| JP2006278519A (ja) | 2006-10-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

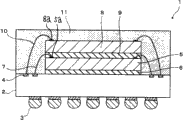

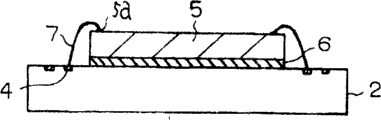

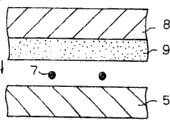

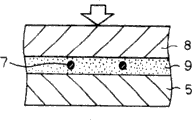

| US7785926B2 (en) | Method of manufacturing stack-type semiconductor device and method of manufacturing stack-type electronic component | |

| JP4188337B2 (ja) | 積層型電子部品の製造方法 | |

| JP5306385B2 (ja) | 積層型電子部品 | |

| CN101038891B (zh) | 半导体装置的制造方法 | |

| US20110057327A1 (en) | Semiconductor device and method of manufacturing the same | |

| JP2014053538A (ja) | 積層型半導体装置とその製造方法 | |

| JP2625654B2 (ja) | 半導体装置およびその製造方法 | |

| US10026679B2 (en) | Process for manufacturing a package for a surface-mount semiconductor device and semiconductor device | |

| US8169089B2 (en) | Semiconductor device including semiconductor chip and sealing material | |

| JP4881044B2 (ja) | 積層型半導体装置の製造方法 | |

| US20090246918A1 (en) | Method of manufacturing semiconductor device | |

| US9048331B2 (en) | Method of manufacturing semiconductor device | |

| US20070196952A1 (en) | Manufacturing method of semiconductor device | |

| CN100440464C (zh) | 层叠型半导体器件以及层叠型电子部件的制造方法 | |

| CN106505043A (zh) | 半导体装置的制造方法及制造装置 | |

| JP4203031B2 (ja) | 積層型電子部品の製造方法 | |

| JP4594777B2 (ja) | 積層型電子部品の製造方法 | |

| JP2007035865A (ja) | 半導体パッケージとその製造方法 | |

| CN108573933B (zh) | 半导体装置及其制造方法 | |

| JP4626445B2 (ja) | 半導体パッケージの製造方法 | |

| JP2007242684A (ja) | 積層型半導体装置及びデバイスの積層方法 | |

| JP4473668B2 (ja) | 半導体装置およびその製造方法 | |

| JP2010109153A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| TR01 | Transfer of patent right | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20170807 Address after: Tokyo, Japan Patentee after: TOSHIBA MEMORY Corp. Address before: Tokyo, Japan Patentee before: Toshiba Corp. |

|

| CP01 | Change in the name or title of a patent holder | ||

| CP01 | Change in the name or title of a patent holder |

Address after: Tokyo, Japan Patentee after: TOSHIBA MEMORY Corp. Address before: Tokyo, Japan Patentee before: Japanese businessman Panjaya Co.,Ltd. Address after: Tokyo, Japan Patentee after: Kaixia Co.,Ltd. Address before: Tokyo, Japan Patentee before: TOSHIBA MEMORY Corp. |

|

| TR01 | Transfer of patent right | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20220107 Address after: Tokyo, Japan Patentee after: Japanese businessman Panjaya Co.,Ltd. Address before: Tokyo, Japan Patentee before: TOSHIBA MEMORY Corp. |