JP4594777B2 - 積層型電子部品の製造方法 - Google Patents

積層型電子部品の製造方法 Download PDFInfo

- Publication number

- JP4594777B2 JP4594777B2 JP2005092596A JP2005092596A JP4594777B2 JP 4594777 B2 JP4594777 B2 JP 4594777B2 JP 2005092596 A JP2005092596 A JP 2005092596A JP 2005092596 A JP2005092596 A JP 2005092596A JP 4594777 B2 JP4594777 B2 JP 4594777B2

- Authority

- JP

- Japan

- Prior art keywords

- electronic component

- adhesive layer

- semiconductor element

- bonding wire

- bonding

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73215—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92247—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/095—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00 with a principal constituent of the material being a combination of two or more materials provided in the groups H01L2924/013 - H01L2924/0715

- H01L2924/097—Glass-ceramics, e.g. devitrified glass

- H01L2924/09701—Low temperature co-fired ceramic [LTCC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19106—Disposition of discrete passive components in a mirrored arrangement on two different side of a common die mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

Landscapes

- Die Bonding (AREA)

- Wire Bonding (AREA)

Description

Claims (5)

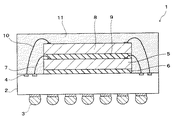

- 基板上に第1の電子部品を搭載して接着する工程と、

前記基板の電極部と前記第1の電子部品の電極パッドとを第1のボンディングワイヤを介して接続する工程と、

前記基板上に接着された前記第1の電子部品を、加熱機構を有するステージ上に載置して加熱する工程と、

裏面側に接着剤層が形成された第2の電子部品を、常温の吸着ツールで保持して前記第1の電子部品の上方に配置する工程と、

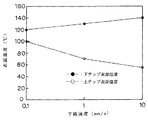

前記第2の電子部品を前記第1の電子部品から少なくとも0.5mm上方の位置から0.1mm/s以上20mm/s以下の範囲の速度で下降させ、加熱された前記第1の電子部品からの輻射熱および前記第1のボンディングワイヤとの伝熱により前記接着剤層を軟化または溶融させ、前記第1のボンディングワイヤを前記接着剤層に取り込みつつ、前記接着剤層を前記第1の電子部品と接触させる工程と、

前記加熱機構による加熱を継続しつつ前記第2の電子部品を加圧し、前記接着剤層を熱硬化させて前記第1の電子部品と前記第2の電子部品とを接着する工程と、

前記基板の電極部と前記第2の電子部品の電極パッドとを第2のボンディングワイヤを介して接続する工程と

を具備することを特徴とする積層型電子部品の製造方法。 - 請求項1記載の積層型電子部品の製造方法において、

前記接着剤層は30μm以上の厚さを有することを特徴とする積層型電子部品の製造方法。 - 請求項1または請求項2記載の積層型電子部品の製造方法において、

前記接着剤層は前記加熱時の粘度が1kPa・s以上100kPa・s未満の範囲の熱硬化型樹脂層を有することを特徴とする積層型電子部品の製造方法。 - 請求項1または請求項2記載の積層型電子部品の製造方法において、

前記接着剤層は、前記第1の電子部品側に配置され、前記加熱時の粘度が1kPa・s以上100kPa・s未満の範囲の第1の熱硬化型樹脂層と、前記第2の電子部品側に配置され、前記加熱時の粘度が100kPa・s以上の第2の熱硬化型樹脂層とを有することを特徴とする積層型電子部品の製造方法。 - 請求項1ないし請求項4のいずれか1項記載の積層型電子部品の製造方法において、

前記第1および第2の電子部品は半導体素子および半導体素子を含むパッケージ部品から選ばれる少なくとも1種からなることを特徴とする積層型電子部品の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005092596A JP4594777B2 (ja) | 2005-03-28 | 2005-03-28 | 積層型電子部品の製造方法 |

| TW095107613A TW200727446A (en) | 2005-03-28 | 2006-03-07 | Stack type semiconductor device manufacturing method and stack type electronic component manufacturing method |

| KR1020060027518A KR100796884B1 (ko) | 2005-03-28 | 2006-03-27 | 적층형 반도체 장치의 제조 방법 및 적층형 전자 부품의제조 방법 |

| US11/390,285 US7615413B2 (en) | 2005-03-28 | 2006-03-28 | Method of manufacturing stack-type semiconductor device and method of manufacturing stack-type electronic component |

| US12/585,547 US7785926B2 (en) | 2005-03-28 | 2009-09-17 | Method of manufacturing stack-type semiconductor device and method of manufacturing stack-type electronic component |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005092596A JP4594777B2 (ja) | 2005-03-28 | 2005-03-28 | 積層型電子部品の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006278520A JP2006278520A (ja) | 2006-10-12 |

| JP2006278520A5 JP2006278520A5 (ja) | 2007-06-14 |

| JP4594777B2 true JP4594777B2 (ja) | 2010-12-08 |

Family

ID=37212996

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005092596A Expired - Fee Related JP4594777B2 (ja) | 2005-03-28 | 2005-03-28 | 積層型電子部品の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4594777B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2650917A2 (en) | 2012-04-09 | 2013-10-16 | Canon Kabushiki Kaisha | Multilayered semiconductor device, printed circuit board, and method of manufacturing multilayered semiconductor device |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4879073B2 (ja) | 2007-04-16 | 2012-02-15 | 新日鐵化学株式会社 | 半導体装置の製造方法 |

| JP5044299B2 (ja) * | 2007-06-19 | 2012-10-10 | 積水化学工業株式会社 | 半導体チップ積層体の製造方法、接着テープ及びダイシングダイボンディングテープ |

| JP5532575B2 (ja) * | 2007-10-22 | 2014-06-25 | 日立化成株式会社 | 接着シート |

| JP4970388B2 (ja) * | 2008-09-03 | 2012-07-04 | 株式会社東芝 | 半導体装置及び半導体装置の製造方法 |

| JP5089560B2 (ja) | 2008-11-28 | 2012-12-05 | リンテック株式会社 | 半導体チップ積層体および半導体チップ積層用接着剤組成物 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002222913A (ja) * | 2001-01-24 | 2002-08-09 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2003086758A (ja) * | 2001-09-10 | 2003-03-20 | Mitsubishi Electric Corp | 半導体装置の製造方法、製造装置、及び、半導体装置 |

| JP2004072009A (ja) * | 2002-08-09 | 2004-03-04 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2004158716A (ja) * | 2002-11-07 | 2004-06-03 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2004282056A (ja) * | 2003-02-27 | 2004-10-07 | Sumitomo Bakelite Co Ltd | 半導体装置、半導体素子の製造方法、および半導体装置の製造方法 |

| JP2005327789A (ja) * | 2004-05-12 | 2005-11-24 | Sharp Corp | ダイシング・ダイボンド兼用粘接着シートおよびこれを用いた半導体装置の製造方法 |

| JP2006128169A (ja) * | 2004-10-26 | 2006-05-18 | Fujitsu Ltd | 半導体装置及び半導体装置の製造方法 |

-

2005

- 2005-03-28 JP JP2005092596A patent/JP4594777B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002222913A (ja) * | 2001-01-24 | 2002-08-09 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2003086758A (ja) * | 2001-09-10 | 2003-03-20 | Mitsubishi Electric Corp | 半導体装置の製造方法、製造装置、及び、半導体装置 |

| JP2004072009A (ja) * | 2002-08-09 | 2004-03-04 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2004158716A (ja) * | 2002-11-07 | 2004-06-03 | Sharp Corp | 半導体装置およびその製造方法 |

| JP2004282056A (ja) * | 2003-02-27 | 2004-10-07 | Sumitomo Bakelite Co Ltd | 半導体装置、半導体素子の製造方法、および半導体装置の製造方法 |

| JP2005327789A (ja) * | 2004-05-12 | 2005-11-24 | Sharp Corp | ダイシング・ダイボンド兼用粘接着シートおよびこれを用いた半導体装置の製造方法 |

| JP2006128169A (ja) * | 2004-10-26 | 2006-05-18 | Fujitsu Ltd | 半導体装置及び半導体装置の製造方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2650917A2 (en) | 2012-04-09 | 2013-10-16 | Canon Kabushiki Kaisha | Multilayered semiconductor device, printed circuit board, and method of manufacturing multilayered semiconductor device |

| US8836102B2 (en) | 2012-04-09 | 2014-09-16 | Canon Kabushiki Kaisha | Multilayered semiconductor device, printed circuit board, and method of manufacturing multilayered semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006278520A (ja) | 2006-10-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4188337B2 (ja) | 積層型電子部品の製造方法 | |

| JP4746646B2 (ja) | 積層型電子部品 | |

| KR100796884B1 (ko) | 적층형 반도체 장치의 제조 방법 및 적층형 전자 부품의제조 방법 | |

| JP4881044B2 (ja) | 積層型半導体装置の製造方法 | |

| JP2013008963A (ja) | 半導体装置とその製造方法 | |

| JP4203031B2 (ja) | 積層型電子部品の製造方法 | |

| JP2011222553A (ja) | 半導体チップ内蔵配線基板及びその製造方法 | |

| US7807510B2 (en) | Method of manufacturing chip integrated substrate | |

| US10026679B2 (en) | Process for manufacturing a package for a surface-mount semiconductor device and semiconductor device | |

| JP4594777B2 (ja) | 積層型電子部品の製造方法 | |

| JP5459108B2 (ja) | 部品内蔵配線基板 | |

| JP2012074497A (ja) | 回路基板 | |

| JP4621595B2 (ja) | 半導体装置の製造方法 | |

| JP2007035865A (ja) | 半導体パッケージとその製造方法 | |

| CN100440464C (zh) | 层叠型半导体器件以及层叠型电子部件的制造方法 | |

| JP2007035864A (ja) | 半導体パッケージ | |

| JP2007324443A (ja) | 積層型半導体装置とその製造方法 | |

| JP2002064162A (ja) | 半導体チップ | |

| JP5571045B2 (ja) | 積層型半導体装置 | |

| JP2007081127A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2010124005A (ja) | 半導体チップモジュール及び半導体チップモジュールの製造方法 | |

| JP2010004079A (ja) | 半導体チップ | |

| JP2001185672A (ja) | 電子回路装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070419 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070419 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100601 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100802 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100802 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100824 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100917 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4594777 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130924 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |