WO2023180859A1 - 半導体装置及び半導体装置の作製方法 - Google Patents

半導体装置及び半導体装置の作製方法 Download PDFInfo

- Publication number

- WO2023180859A1 WO2023180859A1 PCT/IB2023/052379 IB2023052379W WO2023180859A1 WO 2023180859 A1 WO2023180859 A1 WO 2023180859A1 IB 2023052379 W IB2023052379 W IB 2023052379W WO 2023180859 A1 WO2023180859 A1 WO 2023180859A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- insulator

- conductor

- oxide

- semiconductor device

- film

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims description 288

- 238000000034 method Methods 0.000 title claims description 257

- 238000005389 semiconductor device fabrication Methods 0.000 title 1

- 239000004020 conductor Substances 0.000 claims abstract description 959

- 239000012212 insulator Substances 0.000 claims abstract description 956

- 229910044991 metal oxide Inorganic materials 0.000 claims abstract description 104

- 150000004706 metal oxides Chemical class 0.000 claims abstract description 104

- 239000000463 material Substances 0.000 claims description 75

- 238000004519 manufacturing process Methods 0.000 claims description 68

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 62

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 61

- 238000012545 processing Methods 0.000 claims description 48

- 230000008569 process Effects 0.000 claims description 44

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 43

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 43

- 239000011248 coating agent Substances 0.000 claims description 42

- 238000000576 coating method Methods 0.000 claims description 42

- 229910052751 metal Inorganic materials 0.000 claims description 41

- 229910052721 tungsten Inorganic materials 0.000 claims description 38

- 239000010937 tungsten Substances 0.000 claims description 37

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 36

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 36

- 239000011701 zinc Substances 0.000 claims description 35

- 239000002184 metal Substances 0.000 claims description 33

- 150000004767 nitrides Chemical class 0.000 claims description 26

- 239000003990 capacitor Substances 0.000 claims description 24

- 229910000449 hafnium oxide Inorganic materials 0.000 claims description 23

- 229910052733 gallium Inorganic materials 0.000 claims description 21

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims description 21

- 229910052738 indium Inorganic materials 0.000 claims description 20

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims description 20

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 17

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 16

- 229910052725 zinc Inorganic materials 0.000 claims description 12

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 claims description 11

- 229910001928 zirconium oxide Inorganic materials 0.000 claims description 11

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 claims description 8

- 238000001020 plasma etching Methods 0.000 claims description 5

- 239000010408 film Substances 0.000 description 573

- 239000010410 layer Substances 0.000 description 244

- 229910052760 oxygen Inorganic materials 0.000 description 177

- 239000001301 oxygen Substances 0.000 description 176

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 170

- 230000006870 function Effects 0.000 description 170

- 229910052739 hydrogen Inorganic materials 0.000 description 128

- 239000001257 hydrogen Substances 0.000 description 128

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 116

- 210000004027 cell Anatomy 0.000 description 115

- 239000000758 substrate Substances 0.000 description 108

- 238000003860 storage Methods 0.000 description 99

- 238000004544 sputter deposition Methods 0.000 description 83

- 238000005530 etching Methods 0.000 description 78

- 239000007789 gas Substances 0.000 description 75

- 239000012535 impurity Substances 0.000 description 72

- 238000010438 heat treatment Methods 0.000 description 68

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 65

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 60

- 229910052710 silicon Inorganic materials 0.000 description 60

- 239000010703 silicon Substances 0.000 description 60

- 238000000231 atomic layer deposition Methods 0.000 description 53

- 229910052782 aluminium Inorganic materials 0.000 description 47

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical group [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 47

- 238000005229 chemical vapour deposition Methods 0.000 description 43

- 230000015572 biosynthetic process Effects 0.000 description 41

- 229910052735 hafnium Inorganic materials 0.000 description 40

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 40

- 229910001868 water Inorganic materials 0.000 description 40

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical group [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 39

- 238000009792 diffusion process Methods 0.000 description 36

- 239000012298 atmosphere Substances 0.000 description 34

- 230000004888 barrier function Effects 0.000 description 30

- 238000001312 dry etching Methods 0.000 description 30

- 229910004156 TaNx Inorganic materials 0.000 description 29

- 238000010586 diagram Methods 0.000 description 29

- 229910052757 nitrogen Inorganic materials 0.000 description 27

- 239000013078 crystal Substances 0.000 description 26

- 239000000203 mixture Substances 0.000 description 22

- 239000000523 sample Substances 0.000 description 21

- 238000004549 pulsed laser deposition Methods 0.000 description 19

- 238000004140 cleaning Methods 0.000 description 18

- 238000001451 molecular beam epitaxy Methods 0.000 description 18

- 239000002356 single layer Substances 0.000 description 18

- 229910052715 tantalum Inorganic materials 0.000 description 18

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical group [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 18

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 17

- -1 element M Chemical compound 0.000 description 17

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 16

- 230000007423 decrease Effects 0.000 description 16

- 150000002431 hydrogen Chemical class 0.000 description 16

- 239000002346 layers by function Substances 0.000 description 16

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 15

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical group [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 15

- 229910001882 dioxygen Inorganic materials 0.000 description 15

- 230000002093 peripheral effect Effects 0.000 description 15

- 229910052719 titanium Inorganic materials 0.000 description 15

- 239000010936 titanium Chemical group 0.000 description 15

- 238000003491 array Methods 0.000 description 14

- 238000004364 calculation method Methods 0.000 description 14

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical group [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 13

- 230000007547 defect Effects 0.000 description 12

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 11

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical group [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 11

- 229910001873 dinitrogen Inorganic materials 0.000 description 11

- 230000000694 effects Effects 0.000 description 11

- 230000003647 oxidation Effects 0.000 description 11

- 238000007254 oxidation reaction Methods 0.000 description 11

- 238000001039 wet etching Methods 0.000 description 11

- 229910052726 zirconium Inorganic materials 0.000 description 11

- 229910004205 SiNX Inorganic materials 0.000 description 10

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 10

- 229910052802 copper Inorganic materials 0.000 description 10

- 239000010949 copper Chemical group 0.000 description 10

- 238000001459 lithography Methods 0.000 description 10

- 229910052707 ruthenium Inorganic materials 0.000 description 10

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical group [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 9

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 9

- 229910052750 molybdenum Inorganic materials 0.000 description 9

- 239000011733 molybdenum Chemical group 0.000 description 9

- 230000005855 radiation Effects 0.000 description 9

- 238000001878 scanning electron micrograph Methods 0.000 description 9

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 8

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 8

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 8

- 239000000460 chlorine Substances 0.000 description 8

- 229910052746 lanthanum Inorganic materials 0.000 description 8

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical group [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 8

- 229910052759 nickel Inorganic materials 0.000 description 8

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 7

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical group [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 7

- 125000004429 atom Chemical group 0.000 description 7

- 229910052799 carbon Inorganic materials 0.000 description 7

- 230000005669 field effect Effects 0.000 description 7

- 239000002243 precursor Substances 0.000 description 7

- 239000011347 resin Substances 0.000 description 7

- 229920005989 resin Polymers 0.000 description 7

- 229910052718 tin Inorganic materials 0.000 description 7

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 6

- 235000011114 ammonium hydroxide Nutrition 0.000 description 6

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 6

- 229910001195 gallium oxide Inorganic materials 0.000 description 6

- 230000020169 heat generation Effects 0.000 description 6

- 239000011229 interlayer Substances 0.000 description 6

- 125000004430 oxygen atom Chemical group O* 0.000 description 6

- 230000003071 parasitic effect Effects 0.000 description 6

- 229910001925 ruthenium oxide Inorganic materials 0.000 description 6

- WOCIAKWEIIZHES-UHFFFAOYSA-N ruthenium(iv) oxide Chemical compound O=[Ru]=O WOCIAKWEIIZHES-UHFFFAOYSA-N 0.000 description 6

- 239000000126 substance Substances 0.000 description 6

- 229910052727 yttrium Inorganic materials 0.000 description 6

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical group [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 6

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 5

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical group [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 5

- 239000007864 aqueous solution Substances 0.000 description 5

- 229910052731 fluorine Inorganic materials 0.000 description 5

- 239000011737 fluorine Substances 0.000 description 5

- 229910052732 germanium Inorganic materials 0.000 description 5

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical group [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 5

- KQHQLIAOAVMAOW-UHFFFAOYSA-N hafnium(4+) oxygen(2-) zirconium(4+) Chemical compound [O--].[O--].[O--].[O--].[Zr+4].[Hf+4] KQHQLIAOAVMAOW-UHFFFAOYSA-N 0.000 description 5

- 238000003384 imaging method Methods 0.000 description 5

- 239000011810 insulating material Substances 0.000 description 5

- 230000010354 integration Effects 0.000 description 5

- 239000007788 liquid Substances 0.000 description 5

- 229910052749 magnesium Chemical group 0.000 description 5

- 239000011777 magnesium Chemical group 0.000 description 5

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 5

- 239000000395 magnesium oxide Substances 0.000 description 5

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 239000000376 reactant Substances 0.000 description 5

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 5

- 239000011787 zinc oxide Substances 0.000 description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical group [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 4

- 101001094647 Homo sapiens Serum paraoxonase/arylesterase 1 Proteins 0.000 description 4

- 101000621061 Homo sapiens Serum paraoxonase/arylesterase 2 Proteins 0.000 description 4

- 229910052779 Neodymium Inorganic materials 0.000 description 4

- 102100035476 Serum paraoxonase/arylesterase 1 Human genes 0.000 description 4

- 102100022824 Serum paraoxonase/arylesterase 2 Human genes 0.000 description 4

- 238000000137 annealing Methods 0.000 description 4

- 229910052786 argon Inorganic materials 0.000 description 4

- 229910052796 boron Inorganic materials 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 239000000470 constituent Substances 0.000 description 4

- 238000009826 distribution Methods 0.000 description 4

- 238000010894 electron beam technology Methods 0.000 description 4

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 4

- 239000011261 inert gas Substances 0.000 description 4

- 229910052742 iron Inorganic materials 0.000 description 4

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical group [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 4

- 230000001590 oxidative effect Effects 0.000 description 4

- 238000004528 spin coating Methods 0.000 description 4

- 229910052712 strontium Inorganic materials 0.000 description 4

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 4

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 4

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 3

- 229910052684 Cerium Inorganic materials 0.000 description 3

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 3

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 239000002585 base Substances 0.000 description 3

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical group [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 238000000605 extraction Methods 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 229930195733 hydrocarbon Natural products 0.000 description 3

- 150000002430 hydrocarbons Chemical class 0.000 description 3

- 229910003437 indium oxide Inorganic materials 0.000 description 3

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 238000009413 insulation Methods 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 125000004433 nitrogen atom Chemical group N* 0.000 description 3

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 3

- 239000007800 oxidant agent Substances 0.000 description 3

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 238000000682 scanning probe acoustic microscopy Methods 0.000 description 3

- 229910001936 tantalum oxide Inorganic materials 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 3

- 229910052723 transition metal Inorganic materials 0.000 description 3

- 229910001930 tungsten oxide Inorganic materials 0.000 description 3

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 239000004215 Carbon black (E152) Substances 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- 206010014357 Electric shock Diseases 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- 101000967087 Homo sapiens Metal-response element-binding transcription factor 2 Proteins 0.000 description 2

- 101001071233 Homo sapiens PHD finger protein 1 Proteins 0.000 description 2

- 101000612397 Homo sapiens Prenylcysteine oxidase 1 Proteins 0.000 description 2

- 102100040632 Metal-response element-binding transcription factor 2 Human genes 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- 102100036879 PHD finger protein 1 Human genes 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- ATUOYWHBWRKTHZ-UHFFFAOYSA-N Propane Chemical compound CCC ATUOYWHBWRKTHZ-UHFFFAOYSA-N 0.000 description 2

- 229910001080 W alloy Inorganic materials 0.000 description 2

- 238000004833 X-ray photoelectron spectroscopy Methods 0.000 description 2

- 230000002411 adverse Effects 0.000 description 2

- 238000013528 artificial neural network Methods 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- 229910052790 beryllium Inorganic materials 0.000 description 2

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical group [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 238000013527 convolutional neural network Methods 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 235000013305 food Nutrition 0.000 description 2

- 239000000446 fuel Substances 0.000 description 2

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 2

- 229910052736 halogen Inorganic materials 0.000 description 2

- 150000002367 halogens Chemical class 0.000 description 2

- 238000010348 incorporation Methods 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 2

- 229910052451 lead zirconate titanate Inorganic materials 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 2

- 239000013081 microcrystal Substances 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- MGRWKWACZDFZJT-UHFFFAOYSA-N molybdenum tungsten Chemical compound [Mo].[W] MGRWKWACZDFZJT-UHFFFAOYSA-N 0.000 description 2

- 239000002159 nanocrystal Substances 0.000 description 2

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 2

- 239000012466 permeate Substances 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 230000000704 physical effect Effects 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 238000001552 radio frequency sputter deposition Methods 0.000 description 2

- 239000002994 raw material Substances 0.000 description 2

- 210000005245 right atrium Anatomy 0.000 description 2

- 210000005241 right ventricle Anatomy 0.000 description 2

- 238000009751 slip forming Methods 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 238000005476 soldering Methods 0.000 description 2

- 210000001321 subclavian vein Anatomy 0.000 description 2

- 229910052714 tellurium Inorganic materials 0.000 description 2

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 2

- 238000004506 ultrasonic cleaning Methods 0.000 description 2

- 229910052720 vanadium Inorganic materials 0.000 description 2

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical group [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 2

- 210000002620 vena cava superior Anatomy 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 229910019311 (Ba,Sr)TiO Inorganic materials 0.000 description 1

- SDDGNMXIOGQCCH-UHFFFAOYSA-N 3-fluoro-n,n-dimethylaniline Chemical compound CN(C)C1=CC=CC(F)=C1 SDDGNMXIOGQCCH-UHFFFAOYSA-N 0.000 description 1

- 210000002925 A-like Anatomy 0.000 description 1

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- OTMSDBZUPAUEDD-UHFFFAOYSA-N Ethane Chemical compound CC OTMSDBZUPAUEDD-UHFFFAOYSA-N 0.000 description 1

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 1

- VGGSQFUCUMXWEO-UHFFFAOYSA-N Ethene Chemical compound C=C VGGSQFUCUMXWEO-UHFFFAOYSA-N 0.000 description 1

- 239000005977 Ethylene Substances 0.000 description 1

- 235000015842 Hesperis Nutrition 0.000 description 1

- 235000012633 Iberis amara Nutrition 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- 229910016001 MoSe Inorganic materials 0.000 description 1

- 241000699670 Mus sp. Species 0.000 description 1

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 1

- 240000007594 Oryza sativa Species 0.000 description 1

- 235000007164 Oryza sativa Nutrition 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910007610 Zn—Sn Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 1

- 150000001342 alkaline earth metals Chemical class 0.000 description 1

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 1

- AZDRQVAHHNSJOQ-UHFFFAOYSA-N alumane Chemical group [AlH3] AZDRQVAHHNSJOQ-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000013473 artificial intelligence Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- LNMGXZOOXVAITI-UHFFFAOYSA-N bis(selanylidene)hafnium Chemical compound [Se]=[Hf]=[Se] LNMGXZOOXVAITI-UHFFFAOYSA-N 0.000 description 1

- WVMYSOZCZHQCSG-UHFFFAOYSA-N bis(sulfanylidene)zirconium Chemical compound S=[Zr]=S WVMYSOZCZHQCSG-UHFFFAOYSA-N 0.000 description 1

- 229910000416 bismuth oxide Inorganic materials 0.000 description 1

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 description 1

- 229910052794 bromium Inorganic materials 0.000 description 1

- 239000001273 butane Substances 0.000 description 1

- 239000002775 capsule Substances 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 230000000747 cardiac effect Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- TYIXMATWDRGMPF-UHFFFAOYSA-N dibismuth;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Bi+3].[Bi+3] TYIXMATWDRGMPF-UHFFFAOYSA-N 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000002635 electroconvulsive therapy Methods 0.000 description 1

- 230000005670 electromagnetic radiation Effects 0.000 description 1

- 125000002534 ethynyl group Chemical group [H]C#C* 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 239000000284 extract Substances 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- NRJVMVHUISHHQB-UHFFFAOYSA-N hafnium(4+);disulfide Chemical compound [S-2].[S-2].[Hf+4] NRJVMVHUISHHQB-UHFFFAOYSA-N 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 229910000040 hydrogen fluoride Inorganic materials 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 238000009616 inductively coupled plasma Methods 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- HFGPZNIAWCZYJU-UHFFFAOYSA-N lead zirconate titanate Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ti+4].[Zr+4].[Pb+2] HFGPZNIAWCZYJU-UHFFFAOYSA-N 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000005435 mesosphere Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- MHWZQNGIEIYAQJ-UHFFFAOYSA-N molybdenum diselenide Chemical compound [Se]=[Mo]=[Se] MHWZQNGIEIYAQJ-UHFFFAOYSA-N 0.000 description 1

- CWQXQMHSOZUFJS-UHFFFAOYSA-N molybdenum disulfide Chemical compound S=[Mo]=S CWQXQMHSOZUFJS-UHFFFAOYSA-N 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- IJDNQMDRQITEOD-UHFFFAOYSA-N n-butane Chemical compound CCCC IJDNQMDRQITEOD-UHFFFAOYSA-N 0.000 description 1

- OFBQJSOFQDEBGM-UHFFFAOYSA-N n-pentane Natural products CCCCC OFBQJSOFQDEBGM-UHFFFAOYSA-N 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 229910000484 niobium oxide Inorganic materials 0.000 description 1

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 1

- 229910052756 noble gas Inorganic materials 0.000 description 1

- 239000003758 nuclear fuel Substances 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 235000006408 oxalic acid Nutrition 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 235000011007 phosphoric acid Nutrition 0.000 description 1

- 239000011295 pitch Substances 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 239000001294 propane Substances 0.000 description 1

- QQONPFPTGQHPMA-UHFFFAOYSA-N propylene Natural products CC=C QQONPFPTGQHPMA-UHFFFAOYSA-N 0.000 description 1

- 125000004805 propylene group Chemical group [H]C([H])([H])C([H])([*:1])C([H])([H])[*:2] 0.000 description 1

- MWWATHDPGQKSAR-UHFFFAOYSA-N propyne Chemical compound CC#C MWWATHDPGQKSAR-UHFFFAOYSA-N 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 239000012857 radioactive material Substances 0.000 description 1

- 239000002901 radioactive waste Substances 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 230000000306 recurrent effect Effects 0.000 description 1

- 235000009566 rice Nutrition 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 1

- HVEIXSLGUCQTMP-UHFFFAOYSA-N selenium(2-);zirconium(4+) Chemical compound [Se-2].[Se-2].[Zr+4] HVEIXSLGUCQTMP-UHFFFAOYSA-N 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000005477 sputtering target Methods 0.000 description 1

- 229910002076 stabilized zirconia Inorganic materials 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000005437 stratosphere Substances 0.000 description 1

- VEALVRVVWBQVSL-UHFFFAOYSA-N strontium titanate Chemical compound [Sr+2].[O-][Ti]([O-])=O VEALVRVVWBQVSL-UHFFFAOYSA-N 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 239000005439 thermosphere Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- ITRNXVSDJBHYNJ-UHFFFAOYSA-N tungsten disulfide Chemical compound S=[W]=S ITRNXVSDJBHYNJ-UHFFFAOYSA-N 0.000 description 1

- 208000003663 ventricular fibrillation Diseases 0.000 description 1

- 206010047302 ventricular tachycardia Diseases 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/70—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the floating gate being an electrode shared by two or more components

Definitions

- the sixth conductor of the memory cell has the same material as the eighth conductor of the first memory cell, and in a cross-sectional view of the transistor, one of the side ends of the third conductor is , substantially coincides with one of the side edges of the metal oxide, and one of the side edges of the fourth conductor substantially coincides with the other side edge of the metal oxide.

- a seventh insulator that covers the third conductor, the fourth conductor, the metal oxide, and the third insulator, and the seventh insulator is the third conductor.

- a first opening overlapping a region sandwiched between the body and the fourth conductor; a second opening overlapping the opening of the first insulator; and a second opening overlapping the opening of the first insulator;

- At least a portion of a second insulator and a fifth conductor are disposed within the first opening

- a seventh conductor and a fourth insulator are disposed within the second opening of the seventh insulator.

- at least a portion of the eighth conductor are preferably arranged.

- ordinal numbers such as “first” and “second” are used for convenience, and do not limit the number of components or the order of the components (for example, the order of steps or the order of lamination). It's not something you do. Further, the ordinal number attached to a constituent element in a certain part of this specification may not match the ordinal number attached to the constituent element in another part of this specification or in the claims.

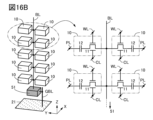

- each layer from the second layer onwards has a similar configuration, so in this embodiment, the second layer 11_2 will mainly be described as an example. Further, regarding the first layer 11_1, descriptions of parts similar to those of the second layer 11_2 will be omitted, and parts different from the second layer 11_2 will be mainly described.

- the first layer 11_1 includes transistors 202a and 202b and capacitive elements 101a and 101b.

- the second layer 11_2 includes transistors 201a and 201b and capacitive elements 101a and 101b.

- Each layer from the third layer 11_3 to the m-th layer 11_m also includes transistors 201a and 201b and capacitive elements 101a and 101b.

- the first layer 11_1 and the second layer 11_2 have a configuration on the right side and a configuration on the left side, respectively, which are symmetrical with respect to the conductor 240. That is, in FIG. 1, the transistor 201a and the transistor 201b are symmetrical, the transistor 202a and the transistor 202b are symmetrical, and the capacitor 101a and the capacitor 101b are symmetrical.

- the structure on the left side of the first layer 11_1 and the second layer 11_2 (transistors 201a, 202a, and capacitor 101a) will be mainly described as an example.

- the transistor 201a includes a conductor 261 (conductor 261a and conductor 261b) embedded in an insulator 284, an insulator 222 on the conductor 261, an insulator 224 on the insulator 222, and The oxide 230 (oxide 230a and oxide 230b) on the body 224, the conductor 242a (conductor 242a1 and conductor 242a2) and the conductor 242b (conductor 242b1 and conductor 242b2) on the oxide 230, , an insulator 271a on the conductor 242a, an insulator 271b on the conductor 242b, an insulator 250 on the oxide 230, and a conductor 260 on the insulator 250 (conductor 260a and conductor 260b), has.

- An insulator 275 is provided on the insulators 271a and 271b, and an insulator 280 is provided on the insulator 275. Insulator 250 and conductor 260 are embedded in openings provided in insulator 280 and insulator 275.

- An insulator 282 is provided on the insulator 280 and on the conductor 260. Further, an insulator 283 is provided on the insulator 282, and an insulator 285 is provided on the insulator 283. Further, an insulator 284 is provided on the insulator 285.

- one of the side ends of the conductor 242a approximately coincides with one of the side ends of the oxide 230, and one of the side ends of the conductor 242b is Preferably, it approximately coincides with the other side edge of the oxide 230. Furthermore, it is preferable that the side edges of the insulator 224 substantially coincide with the side edges of the oxide 230. In one embodiment of the present invention, the insulator 224, the oxide 230, and the conductor that will become the conductor 242a and the conductor 242b in a later step can be processed into an island shape all at once. Accordingly, a semiconductor device according to one embodiment of the present invention can be manufactured with good productivity.

- the insulator 271a and the insulator 271b are films that protect the conductor 242a and the conductor 242b during the island-shaped processing.

- the insulator 271a and the insulator 271b function as etching stoppers when removing the hard mask in processing the conductor 242a and the conductor 242b. Therefore, as shown in FIG. 2A, in a cross-sectional view of the transistor 201a, the side end of the insulator 271a on the insulator 250 side approximately coincides with the side end of the conductor 242a on the insulator 250 side, and the insulator 271b It is preferable that both side ends of the conductor 242b substantially coincide with the side ends of the conductor 242b.

- the stacked layers will be different from each other in the top view. It can be said that at least part of the outlines overlap. For example, this includes a case where the lower part of the side edge of the upper layer contacts the upper part of the side edge of the lower layer.

- the upper layer and the lower layer include a case where the upper layer and the lower layer are processed using the same mask pattern or partially the same mask pattern.

- the outlines do not overlap, and part of the upper layer may be located inside the lower layer, or part of the upper layer may be located outside the lower layer, and in this case, the side edges are approximately the same. It is said that they match, or that their top surface shapes roughly match.

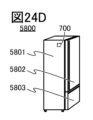

- the capacitive element 101a includes a conductor 153 on a conductor 242b, an insulator 154 on the conductor 153, and a conductor 160 (conductor 160a and conductor 160b) on the insulator 154.

- the conductor 153, the insulator 154, and the conductor 160 each have at least a portion formed in an opening provided in the insulator 271b, the insulator 275, the insulator 280, the insulator 282, the insulator 283, and the insulator 285. is located inside.

- the ends of each of the conductor 153, the insulator 154, and the conductor 160 are located at least on the insulator 282, and preferably on the insulator 285.

- the insulator 154 is provided to cover the end of the conductor 153. Thereby, the conductor 153 and the conductor 160 can be electrically insulated.

- the conductor 242b provided in an overlapping manner on the oxide 230 functions as a wiring electrically connected to the conductor 153 of the capacitive element 101a.

- the conductor 242a provided overlappingly on the oxide 230 functions as a wiring electrically connected to the conductor 240.

- the upper surface and side end portions of the conductor 242a are electrically connected to the conductor 240_2 extending in the Z direction.

- the conductor 240_2 directly contacts at least one of the top surface and side end portion of the conductor 242a, there is no need to provide a separate connection electrode, so the area occupied by the memory array can be reduced. Furthermore, the degree of integration of memory cells is improved, and storage capacity can be increased. Note that it is preferable that the conductor 240_2 be in contact with a part of the upper surface and the side end portion of the conductor 242a. The contact resistance between the conductor 240_2 and the conductor 242a can be reduced by the conductor 240_2 being in contact with multiple surfaces of the conductor 242a.

- the width W2 is preferably larger than the width W1.

- the conductor 240_2 contacts at least a portion of the upper surface and a portion of the side end portion of the conductor 242a. Therefore, the area of the region where the conductor 240_2 and the conductor 242a are in contact can be increased. Note that in this specification and the like, the contact between the conductor 240_2 and the conductor 242a shown in FIG. 4A and the like may be referred to as a top side contact.

- an insulator 241 is provided in contact with the side surface of the conductor 240 (for example, the conductor 240_2 corresponds to this in FIGS. 4A and 4B).

- the insulator 241 includes a conductor 240_2, an insulator 284, an insulator 222, an insulator 224, an oxide 230, an insulator 271a, an insulator 275, an insulator 280, an insulator 282, the insulator 283, and the insulator 285.

- the conductor 242a is exposed from the insulator 241 and is in contact with the conductor 240_2.

- the insulator 241 can prevent impurities such as hydrogen and oxygen contained in the conductor 240_2 from diffusing into the oxide 230. Thereby, the electrical characteristics and reliability of the transistor 201a can be improved.

- the components of the transistor 201a will be mainly described below as an example, the description can also be applied to the components of the transistor 202a.

- the oxide 230 preferably includes an oxide 230a on the insulator 224 and an oxide 230b on the oxide 230a. By having the oxide 230a below the oxide 230b, diffusion of impurities from a structure formed below the oxide 230a to the oxide 230b can be suppressed.

- the oxide 230 has a two-layer structure of the oxide 230a and the oxide 230b

- the structure is not limited thereto.

- the oxide 230 may have a single layer structure of the oxide 230b, or may have a stacked structure of three or more layers.

- the region 230bc has fewer oxygen vacancies or has a lower impurity concentration than the regions 230ba and 230bb, so it is a high resistance region with a lower carrier concentration. Therefore, the region 230bc can be said to be i-type (intrinsic) or substantially i-type.

- the carrier concentration of the region 230bc is 1 ⁇ 10 18 cm ⁇ 3 or less, less than 1 ⁇ 10 17 cm ⁇ 3 , less than 1 ⁇ 10 16 cm ⁇ 3 , less than 1 ⁇ 10 15 cm ⁇ 3 , or 1 ⁇ 10 14 cm -3, less than 1 ⁇ 10 13 cm ⁇ 3 , less than 1 ⁇ 10 12 cm ⁇ 3 , less than 1 ⁇ 10 11 cm ⁇ 3 , or preferably less than 1 ⁇ 10 10 cm ⁇ 3 .

- the lower limit value of the carrier concentration in the region 230bc is not particularly limited, but may be set to, for example, 1 ⁇ 10 ⁇ 9 cm ⁇ 3 .

- the impurity concentration in the oxide 230b is lowered to lower the defect level density.

- the term "high purity intrinsic” or “substantially high purity intrinsic” means that the impurity concentration is low and the defect level density is low.

- an oxide semiconductor (or metal oxide) with a low carrier concentration is sometimes referred to as a high-purity intrinsic or substantially high-purity intrinsic oxide semiconductor (or metal oxide).

- the impurity concentration in the oxide 230b In order to stabilize the electrical characteristics of the transistor 201a, it is effective to reduce the impurity concentration in the oxide 230b. Further, in order to reduce the impurity concentration of the oxide 230b, it is preferable to also reduce the impurity concentration in the adjacent film.

- impurities include hydrogen, nitrogen, alkali metals, alkaline earth metals, iron, nickel, and silicon. Note that the impurities in the oxide 230b refer to, for example, substances other than the main components that constitute the oxide 230b. For example, an element having a concentration of less than 0.1 atomic % can be considered an impurity.

- region 230bc, the region 230ba, and the region 230bb may each include not only the oxide 230b but also the oxide 230a.

- the concentration of metal elements and impurity elements such as hydrogen and nitrogen detected in each region is not limited to a stepwise change from region to region, and may be continuously changed within each region. In other words, the closer the region is to the region 230bc, the lower the concentration of metal elements and impurity elements such as hydrogen and nitrogen may be.

- the oxide 230 has a stacked structure of a plurality of oxide layers having different chemical compositions.

- the atomic ratio of the element M to the metal element that is the main component is the same as the atomic ratio of the element M to the metal element that is the main component in the metal oxide used for the oxide 230b. It is preferable that it be larger.

- the atomic ratio of the element M to In is preferably larger than the atomic ratio of the element M to In in the metal oxide used for the oxide 230b.

- the nearby composition includes a range of ⁇ 30% of the desired atomic ratio.

- the element M it is preferable to use gallium.

- the transistor using an oxide semiconductor if impurities and oxygen vacancies are present in a region of the oxide semiconductor where a channel is formed, electrical characteristics are likely to fluctuate and reliability may deteriorate. Furthermore, hydrogen near the oxygen vacancy may form a defect in which hydrogen is present in the oxygen vacancy (hereinafter sometimes referred to as V OH ), and generate electrons that serve as carriers. Therefore, if oxygen vacancies are included in the region 230bc where a channel is formed in the oxide semiconductor, the transistor exhibits normally-on characteristics (a channel exists even when no voltage is applied to the gate electrode, and current flows through the transistor). flow characteristics). Therefore, in the region 230bc in the oxide semiconductor, impurities, oxygen vacancies, and V OH are preferably reduced as much as possible. In other words, the region 230bc in the oxide semiconductor preferably has a reduced carrier concentration and is i-type (intrinsic) or substantially i-type.

- the insulator 250 may have a laminated structure of an insulator 250a in contact with the oxide 230, an insulator 250b on the insulator 250a, and an insulator 250c on the insulator 250b.

- the insulator 250a has the function of capturing and fixing hydrogen.

- the insulator 250b it is preferable to use an insulator having a stable structure against heat, such as silicon oxide or silicon oxynitride.

- the insulator 250b may have a laminated structure.

- the insulator 250b can have a stacked structure in which an insulator that can be used for the insulator 250a is provided on silicon oxide or silicon oxynitride.

- a stacked structure including silicon oxide or silicon oxynitride and hafnium oxide on silicon oxide or silicon oxynitride may be used as the insulator 250.

- barrier insulator refers to an insulator that has barrier properties.

- barrier property is defined as a function of suppressing the diffusion of a corresponding substance (also referred to as low permeability).

- the function is to capture and fix (also referred to as gettering) the corresponding substance.

- the insulator 250a is provided in contact with the top and side surfaces of the oxide 230b, the side surfaces of the oxide 230a, the side surfaces of the insulator 224, and the top surface of the insulator 222. Since the insulator 250a has barrier properties against oxygen, desorption of oxygen from the region 230bc of the oxide 230b can be suppressed when heat treatment or the like is performed. Therefore, formation of oxygen vacancies in the oxide 230a and the oxide 230b can be reduced.

- barrier insulators against hydrogen examples include oxides such as aluminum oxide, hafnium oxide, and tantalum oxide, and nitrides such as silicon nitride.

- oxides such as aluminum oxide, hafnium oxide, and tantalum oxide

- nitrides such as silicon nitride.

- the insulator 275 has a single layer structure or a multilayer structure of the hydrogen barrier insulator.

- the insulator 275 has barrier properties against hydrogen. Since the insulator 275 has barrier properties against hydrogen, it is possible to suppress the insulator 250 from capturing and fixing hydrogen in the regions 230ba and 230bb. Therefore, the region 230ba and the region 230bb can be n-type.

- the films In order to reduce the film thickness of the insulators 250a to 250c as described above, it is preferable to form the films using an atomic layer deposition (ALD) method.

- ALD atomic layer deposition

- the ALD method include a thermal ALD method in which a reaction between a precursor and a reactant is performed using only thermal energy, and a PEALD method in which a plasma-excited reactant is used.

- PEALD method by using plasma, it is possible to form a film at a lower temperature, which may be preferable.

- the ALD method can deposit atoms one layer at a time, it is possible to form extremely thin films, to form structures with high aspect ratios, to form films with few defects such as pinholes, and to improve coverage. It has the advantage of being able to form excellent films and being able to form films at low temperatures. Therefore, the insulator 250 can be formed with good coverage on the side surfaces of the opening formed in the insulator 280 and the side edges of the conductors 242a, 242b, etc., with a thin film thickness as described above. .

- One or more of the insulator 212, the insulator 214, the insulator 282, the insulator 283, the insulator 286, and the insulator 287 are exposed to impurities such as water and hydrogen from the substrate side or from the transistors 201a, 202a, etc. It is preferable to function as a barrier insulator that suppresses diffusion from above into the transistors 201a, 202a, etc.

- the insulator 212, the insulator 214, the insulator 282, the insulator 283, the insulator 286, and the insulator 287 may each have an insulator having a function of suppressing the diffusion of impurities such as water and hydrogen, and oxygen.

- impurities such as water and hydrogen, and oxygen.

- aluminum oxide, magnesium oxide, hafnium oxide, gallium oxide, indium gallium zinc oxide, silicon nitride, silicon nitride oxide, or the like can be used.

- the insulators 212, 283, and 287 it is preferable to use silicon nitride, which has higher hydrogen barrier properties.

- the conductor 261 may have a single layer structure or a laminated structure.

- the conductor 261 includes a conductor 261a and a conductor 261b.

- the conductor 261a is provided in contact with the bottom and side walls of the opening.

- the conductor 261b is provided in contact with the upper surface of the conductor 261a and in contact with the side wall of the opening.

- the height of the top surface of the conductor 261b approximately matches the height of the top surface of the insulator 284.

- the conductor 261b is made of a conductive material containing tungsten, copper, or aluminum as a main component.

- the conductor 261b preferably includes tungsten.

- the conductor 261 can function as a second gate electrode.

- the threshold voltage (Vth) of the transistor 201a can be controlled by changing the potential applied to the conductor 261 independently of the potential applied to the conductor 260 without interlocking with the potential applied to the conductor 260.

- Vth threshold voltage

- the electrical resistivity of the conductor 261 is designed in consideration of the potential applied to the conductor 261, and the film thickness of the conductor 261 is set in accordance with the electrical resistivity. Furthermore, the thickness of the insulator 284 is approximately the same as that of the conductor 261. Here, it is preferable that the film thicknesses of the conductor 261 and the insulator 284 be made as thin as the design of the conductor 261 allows. By reducing the film thickness of the insulator 284, the absolute amount of impurities such as hydrogen contained in the insulator 284 can be reduced, so that diffusion of the impurities into the oxide 230 can be reduced. .

- the conductor 261 is formed in the same layer as the conductor 160, the conductor 261a can have the same configuration as the conductor 160a, and the conductor 261b can have the same configuration as the conductor 160b.

- an insulator 263 having the same configuration as the insulator 154 is provided in contact with the lower surface of the conductor 261 .

- the insulator 222 preferably includes an oxide of one or both of aluminum and hafnium, which are insulating materials.

- the insulator it is preferable to use aluminum oxide, hafnium oxide, an oxide containing aluminum and hafnium (hafnium aluminate), or the like.

- an oxide containing hafnium and zirconium, such as hafnium zirconium oxide is preferable to use.

- the insulator 222 prevents the release of oxygen from the oxide 230 to the substrate side and the release of hydrogen, etc. from the peripheral areas of the transistors 201a and 202a to the oxide 230.

- the insulator 222 It functions as a layer that suppresses the diffusion of impurities. Therefore, by providing the insulator 222, impurities such as hydrogen can be suppressed from diffusing inside the transistors 201a and 202a, and generation of oxygen vacancies in the oxide 230 can be suppressed. Further, it is possible to suppress the conductor 205 or the conductor 160 from reacting with oxygen contained in the insulator 224 and the oxide 230.

- aluminum oxide, bismuth oxide, germanium oxide, niobium oxide, silicon oxide, titanium oxide, tungsten oxide, yttrium oxide, or zirconium oxide may be added to the above insulator.

- these insulators may be nitrided.

- the insulator 222 may be used by stacking silicon oxide, silicon oxynitride, or silicon nitride on the above insulator.

- the insulator 222 may have a single layer structure or a multilayer structure of an insulator containing a so-called high-k material such as aluminum oxide, hafnium oxide, tantalum oxide, zirconium oxide, and hafnium zirconium oxide.

- a so-called high-k material such as aluminum oxide, hafnium oxide, tantalum oxide, zirconium oxide, and hafnium zirconium oxide.

- the thickness of the insulator 285 may be set in a range from 50 nm to 250 nm, and the depth of the opening may be set to about 150 nm to 350 nm.

- the capacitive element 101a has sufficient capacitance, and in a semiconductor device in which a plurality of memory cell layers are stacked, the height of one layer becomes excessive. You can keep it from getting too expensive.

- a structure may be adopted in which the capacitances of the capacitive elements provided in each memory cell are made different in each of the layers of the plurality of memory cells. In the case of this configuration, for example, the thickness of the insulator 285 provided in each memory cell layer may be made different.

- examples of insulators that have the function of suppressing the permeation of impurities such as hydrogen and oxygen include aluminum oxide, magnesium oxide, gallium oxide, germanium oxide, yttrium oxide, zirconium oxide, lanthanum oxide, neodymium oxide, and Examples include metal oxides such as hafnium and tantalum oxide, and metal nitrides such as aluminum nitride, silicon nitride oxide, and silicon nitride.

- Examples of conductors include tantalum nitride, titanium nitride, tungsten, nitrides containing titanium and aluminum, nitrides containing tantalum and aluminum, ruthenium oxide, ruthenium nitride, oxides containing strontium and ruthenium, and lanthanum and nickel. Examples include oxides containing.

- oxide semiconductors may be classified into a different classification from the above.

- oxide semiconductors are classified into single-crystal oxide semiconductors and other non-single-crystal oxide semiconductors.

- non-single crystal oxide semiconductors include the above-mentioned CAAC-OS and nc-OS.

- non-single crystal oxide semiconductors include polycrystalline oxide semiconductors, pseudo-amorphous oxide semiconductors (a-like OS), amorphous oxide semiconductors, and the like.

- CAC-OS has a structure in which the material is separated into a first region and a second region, resulting in a mosaic shape, and the first region is distributed throughout the film (hereinafter also referred to as cloud shape). ). That is, CAC-OS is a composite metal oxide having a configuration in which the first region and the second region are mixed.

- the first region is a region with higher conductivity than the second region.

- carriers flow through the first region, thereby exhibiting conductivity as a metal oxide. Therefore, by distributing the first region in a cloud shape in the metal oxide, high field effect mobility ( ⁇ ) can be achieved.

- Oxide semiconductors have a variety of structures, each with different properties.

- the oxide semiconductor of one embodiment of the present invention includes two or more of an amorphous oxide semiconductor, a polycrystalline oxide semiconductor, an a-like OS, a CAC-OS, an nc-OS, and a CAAC-OS. It's okay.

- an insulating material for forming an insulator, a conductive material for forming a conductor, or a semiconductor material for forming a semiconductor is used by sputtering method, chemical vapor deposition (CVD).

- the film can be formed by appropriately using a method such as a molecular beam epitaxy (MBE) method, a pulsed laser deposition (PLD) method, or an ALD method.

- MBE molecular beam epitaxy

- PLD pulsed laser deposition

- sputtering methods include an RF sputtering method that uses a high frequency power source as a sputtering power source, a DC sputtering method that uses a DC power source, and a pulsed DC sputtering method that changes the voltage applied to the electrode in a pulsed manner.

- the RF sputtering method is mainly used when forming an insulating film

- the DC sputtering method is mainly used when forming a metal conductive film.

- the pulsed DC sputtering method is mainly used when forming a film of a compound such as an oxide, nitride, or carbide by a reactive sputtering method.

- the ALD method a thermal ALD method in which a reaction between a precursor and a reactant is performed using only thermal energy, a PEALD method in which a plasma-excited reactant is used, etc. can be used.

- the insulator 212 and the insulator 214 are each formed using a sputtering method.

- a sputtering method that does not require the use of molecules containing hydrogen in the film formation gas, the hydrogen concentration in the insulator 212 or the insulator 214 can be reduced.

- the method for forming the insulator 212 and the insulator 214 is not limited to the sputtering method, and for example, a CVD method, an MBE method, a PLD method, or an ALD method may be used.

- the insulator 212 and the insulator 214 be formed continuously without being exposed to the atmosphere.

- the insulator 212 and the insulator 214 can be formed while reducing hydrogen in the film, and furthermore, it is possible to reduce the amount of hydrogen mixed into the film between each film forming process.

- the frequency of RF is preferably 10 MHz or more. Typically, it is 13.56 MHz. The higher the RF frequency, the smaller the damage to the substrate can be.

- each insulating film serving as the insulator 216 is preferably formed using a sputtering method.

- a sputtering method that does not require the use of molecules containing hydrogen in the film formation gas, the hydrogen concentration in the insulator 216 can be reduced.

- the method for forming the insulator 216 is not limited to the sputtering method, and for example, a CVD method, an MBE method, a PLD method, or an ALD method may be used.

- silicon oxide is formed as the insulator 216 by pulsed DC sputtering using a silicon target in an atmosphere containing oxygen gas.

- pulsed DC sputtering method the film thickness distribution can be made more uniform, and the sputtering rate and film quality can be improved.

- the present invention is not limited to this.

- the insulator 216 in which an opening is formed may be first produced, and the conductor 205 may be formed so as to be embedded in the opening.

- the insulator 222 can be a laminated film of an insulator containing an oxide of one or both of aluminum and hafnium, and silicon oxide, silicon oxynitride, silicon nitride, or silicon nitride oxide.

- the temperature of the heat treatment is preferably 250°C or more and 650°C or less, more preferably 300°C or more and 500°C or less, and even more preferably 320°C or more and 450°C or less.

- the heat treatment is performed in an atmosphere of nitrogen gas or inert gas, or an atmosphere containing 10 ppm or more, 1% or more, or 10% or more of oxidizing gas.

- the oxygen gas content be about 20%.

- the heat treatment may be performed under reduced pressure.

- heat treatment may be performed in an atmosphere containing 10 ppm or more, 1% or more, or 10% or more of an oxidizing gas to compensate for the desorbed oxygen.

- heat treatment is performed at a temperature of 400° C. for one hour at a flow rate ratio of nitrogen gas and oxygen gas of 4:1. Through the heat treatment, impurities such as water and hydrogen contained in the insulator 222 can be removed. Further, when an oxide containing hafnium is used as the insulator 222, a part of the insulator 222 may be crystallized by the heat treatment. Further, the heat treatment can also be performed at a timing such as after the insulator 224 is formed.

- an insulating film 224f is formed on the insulator 222 (FIG. 7B).

- the oxide film 230af and the oxide film 230bf can be formed using, for example, a sputtering method, a CVD method, an MBE method, a PLD method, or an ALD method, respectively.

- a sputtering method is used to form the oxide film 230af and the oxide film 230bf.

- oxygen or a mixed gas of oxygen and a noble gas is used as the sputtering gas.

- a noble gas By increasing the proportion of oxygen contained in the sputtering gas, excess oxygen in the oxide film to be formed can be increased.

- an In-M-Zn oxide target or the like can be used.