WO2023033126A1 - リードフレーム及びその製造方法 - Google Patents

リードフレーム及びその製造方法 Download PDFInfo

- Publication number

- WO2023033126A1 WO2023033126A1 PCT/JP2022/033037 JP2022033037W WO2023033126A1 WO 2023033126 A1 WO2023033126 A1 WO 2023033126A1 JP 2022033037 W JP2022033037 W JP 2022033037W WO 2023033126 A1 WO2023033126 A1 WO 2023033126A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- lead

- die pad

- rough

- metal substrate

- lead frame

- Prior art date

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 135

- 239000010410 layer Substances 0.000 claims description 376

- 239000004065 semiconductor Substances 0.000 claims description 369

- 229910052751 metal Inorganic materials 0.000 claims description 343

- 239000002184 metal Substances 0.000 claims description 343

- 238000007747 plating Methods 0.000 claims description 216

- 239000000758 substrate Substances 0.000 claims description 206

- 238000007789 sealing Methods 0.000 claims description 100

- 238000005530 etching Methods 0.000 claims description 62

- 239000011247 coating layer Substances 0.000 claims description 22

- 238000007788 roughening Methods 0.000 claims description 19

- 238000012545 processing Methods 0.000 claims description 14

- 229920005989 resin Polymers 0.000 description 100

- 239000011347 resin Substances 0.000 description 100

- 238000000034 method Methods 0.000 description 40

- 239000010949 copper Substances 0.000 description 32

- 230000002093 peripheral effect Effects 0.000 description 31

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 30

- 229910052802 copper Inorganic materials 0.000 description 30

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 26

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 26

- 239000000853 adhesive Substances 0.000 description 26

- 230000001070 adhesive effect Effects 0.000 description 26

- 229910052709 silver Inorganic materials 0.000 description 26

- 239000004332 silver Substances 0.000 description 26

- 239000007788 liquid Substances 0.000 description 25

- 235000019592 roughness Nutrition 0.000 description 24

- 238000010586 diagram Methods 0.000 description 21

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 18

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 17

- 239000003822 epoxy resin Substances 0.000 description 17

- 229920000647 polyepoxide Polymers 0.000 description 17

- 229910000881 Cu alloy Inorganic materials 0.000 description 15

- 238000009713 electroplating Methods 0.000 description 15

- 230000007774 longterm Effects 0.000 description 15

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 14

- 239000000243 solution Substances 0.000 description 14

- 239000000463 material Substances 0.000 description 13

- KDLHZDBZIXYQEI-UHFFFAOYSA-N palladium Substances [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 12

- 239000011241 protective layer Substances 0.000 description 11

- 239000010931 gold Substances 0.000 description 10

- 230000000052 comparative effect Effects 0.000 description 9

- 229920001971 elastomer Polymers 0.000 description 9

- 238000012856 packing Methods 0.000 description 9

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 8

- 230000008595 infiltration Effects 0.000 description 8

- 238000001764 infiltration Methods 0.000 description 8

- 230000035515 penetration Effects 0.000 description 8

- 238000012986 modification Methods 0.000 description 7

- 230000004048 modification Effects 0.000 description 7

- 239000012756 surface treatment agent Substances 0.000 description 7

- 239000002585 base Substances 0.000 description 6

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 6

- 229910052737 gold Inorganic materials 0.000 description 6

- 238000000691 measurement method Methods 0.000 description 6

- 229920005992 thermoplastic resin Polymers 0.000 description 6

- 229920001187 thermosetting polymer Polymers 0.000 description 6

- 229910001316 Ag alloy Inorganic materials 0.000 description 5

- 229910001020 Au alloy Inorganic materials 0.000 description 5

- 239000003513 alkali Substances 0.000 description 5

- NNFCIKHAZHQZJG-UHFFFAOYSA-N potassium cyanide Chemical compound [K+].N#[C-] NNFCIKHAZHQZJG-UHFFFAOYSA-N 0.000 description 5

- 238000000926 separation method Methods 0.000 description 5

- LFAGQMCIGQNPJG-UHFFFAOYSA-N silver cyanide Chemical compound [Ag+].N#[C-] LFAGQMCIGQNPJG-UHFFFAOYSA-N 0.000 description 5

- 229940098221 silver cyanide Drugs 0.000 description 5

- 230000003746 surface roughness Effects 0.000 description 5

- 239000003353 gold alloy Substances 0.000 description 4

- 239000007769 metal material Substances 0.000 description 4

- 238000000465 moulding Methods 0.000 description 4

- 229910052763 palladium Inorganic materials 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- 229910000640 Fe alloy Inorganic materials 0.000 description 3

- KWYUFKZDYYNOTN-UHFFFAOYSA-M Potassium hydroxide Chemical compound [OH-].[K+] KWYUFKZDYYNOTN-UHFFFAOYSA-M 0.000 description 3

- HEMHJVSKTPXQMS-UHFFFAOYSA-M Sodium hydroxide Chemical compound [OH-].[Na+] HEMHJVSKTPXQMS-UHFFFAOYSA-M 0.000 description 3

- 229910045601 alloy Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 3

- 239000007864 aqueous solution Substances 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000005260 corrosion Methods 0.000 description 3

- 238000001746 injection moulding Methods 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- -1 platinum group metals Chemical class 0.000 description 3

- 238000002360 preparation method Methods 0.000 description 3

- 229920002050 silicone resin Polymers 0.000 description 3

- 239000007787 solid Substances 0.000 description 3

- 238000001721 transfer moulding Methods 0.000 description 3

- 229910021578 Iron(III) chloride Inorganic materials 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- RBTARNINKXHZNM-UHFFFAOYSA-K iron trichloride Chemical compound Cl[Fe](Cl)Cl RBTARNINKXHZNM-UHFFFAOYSA-K 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Substances [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 238000005096 rolling process Methods 0.000 description 2

- 230000003595 spectral effect Effects 0.000 description 2

- 239000000725 suspension Substances 0.000 description 2

- DJQYKWDYUQPOOE-OGRLCSSISA-N (2s,3s)-2-[4-[(1s)-1-amino-3-methylbutyl]triazol-1-yl]-1-[4-[4-[4-[(2s,3s)-2-[4-[(1s)-1-amino-3-methylbutyl]triazol-1-yl]-3-methylpentanoyl]piperazin-1-yl]-6-[2-[2-(2-prop-2-ynoxyethoxy)ethoxy]ethylamino]-1,3,5-triazin-2-yl]piperazin-1-yl]-3-methylpentan- Chemical compound Cl.N1([C@@H]([C@@H](C)CC)C(=O)N2CCN(CC2)C=2N=C(NCCOCCOCCOCC#C)N=C(N=2)N2CCN(CC2)C(=O)[C@H]([C@@H](C)CC)N2N=NC(=C2)[C@@H](N)CC(C)C)C=C([C@@H](N)CC(C)C)N=N1 DJQYKWDYUQPOOE-OGRLCSSISA-N 0.000 description 1

- 229920001342 Bakelite® Polymers 0.000 description 1

- QPLDLSVMHZLSFG-UHFFFAOYSA-N Copper oxide Chemical compound [Cu]=O QPLDLSVMHZLSFG-UHFFFAOYSA-N 0.000 description 1

- 239000005751 Copper oxide Substances 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- 229910000990 Ni alloy Inorganic materials 0.000 description 1

- 240000007594 Oryza sativa Species 0.000 description 1

- 235000007164 Oryza sativa Nutrition 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 229910000431 copper oxide Inorganic materials 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000005238 degreasing Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 230000007935 neutral effect Effects 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 235000011962 puddings Nutrition 0.000 description 1

- 235000009566 rice Nutrition 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 241000894007 species Species 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

- H01L23/49548—Cross section geometry

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49579—Lead-frames or other flat leads characterised by the materials of the lead frames or layers thereon

- H01L23/49582—Metallic layers on lead frames

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4821—Flat leads, e.g. lead frames with or without insulating supports

- H01L21/4828—Etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4821—Flat leads, e.g. lead frames with or without insulating supports

- H01L21/4842—Mechanical treatment, e.g. punching, cutting, deforming, cold welding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/561—Batch processing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/60—Attaching or detaching leads or other conductive members, to be used for carrying current to or from the device in operation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3142—Sealing arrangements between parts, e.g. adhesion promotors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49503—Lead-frames or other flat leads characterised by the die pad

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49503—Lead-frames or other flat leads characterised by the die pad

- H01L23/49513—Lead-frames or other flat leads characterised by the die pad having bonding material between chip and die pad

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49517—Additional leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49579—Lead-frames or other flat leads characterised by the materials of the lead frames or layers thereon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/50—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor for integrated circuit devices, e.g. power bus, number of leads

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C18/00—Chemical coating by decomposition of either liquid compounds or solutions of the coating forming compounds, without leaving reaction products of surface material in the coating; Contact plating

- C23C18/16—Chemical coating by decomposition of either liquid compounds or solutions of the coating forming compounds, without leaving reaction products of surface material in the coating; Contact plating by reduction or substitution, e.g. electroless plating

- C23C18/18—Pretreatment of the material to be coated

- C23C18/20—Pretreatment of the material to be coated of organic surfaces, e.g. resins

- C23C18/22—Roughening, e.g. by etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16245—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49572—Lead-frames or other flat leads consisting of thin flexible metallic tape with or without a film carrier

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0307—Providing micro- or nanometer scale roughness on a metal surface, e.g. by plating of nodules or dendrites

Definitions

- the present disclosure relates to lead frames and manufacturing methods thereof.

- a QFN type semiconductor device is constructed by sealing a semiconductor element mounted on a mounting surface of a lead frame with a sealing resin and exposing a portion of leads on the back side.

- the distance from the outer periphery of the semiconductor device to the electrodes of the semiconductor element which is the distance through which moisture contained in the outside air (air) can enter, tends to be short. Therefore, there is a possibility that moisture in the air may enter from the periphery of the semiconductor device to the electrodes of the semiconductor element.

- This embodiment provides a lead frame capable of manufacturing a semiconductor device capable of suppressing penetration of moisture in the air up to the electrodes of the semiconductor element, and a manufacturing method thereof.

- the present embodiment provides a lead frame and a method of manufacturing the same, which can make good connection between the bumps and the lead frame and can suppress the intrusion of moisture from the outer periphery of the semiconductor device toward the electrodes of the semiconductor element.

- the present embodiment provides a lead frame and a method of manufacturing the same, which can manufacture a lead frame having a rough surface at low cost.

- the present embodiment provides a lead frame and a method of manufacturing the same that can prevent moisture from penetrating from the periphery of the semiconductor device toward the electrodes of the semiconductor element.

- the present embodiment provides a lead frame and a method of manufacturing the same that can suppress bleed-out and prevent moisture from entering from the outer periphery of the semiconductor device toward the electrodes of the semiconductor element.

- a plurality of lead portions are provided, and at least a portion of the upper surface of the lead portion and the side wall surface of the lead portion are roughened rough surfaces, and the a * value of the rough surface in the CIELab color space is in the range of 12-19 and the b * value is in the range of 12-17.

- a plurality of lead portions are provided, and at least a portion of the upper surface of the lead portion and the side wall surface of the lead portion are roughened rough surfaces, and the arithmetic mean curvature Spc of the peak points of the rough surfaces is 700 mm.

- a lead frame that is greater than or equal to -1.

- a part of the upper surface of the lead portion and a side wall surface of the lead portion are the rough surface, and a metal plating layer is provided on a surface of the upper surface of the lead portion that is not the rough surface.

- the lead frame according to any one of [1] to [3].

- the metal plating layer includes at least one of an Ag plating layer, a Ni plating layer, a Pd plating layer, and an Au plating layer.

- the plurality of lead sections are arranged around the die pad section, and the upper surface of the die pad section and the side wall surface of the die pad section are the rough surfaces.

- the lead frame according to any one of [5].

- the lead frame is used for manufacturing a semiconductor device including a sealing portion that seals at least the plurality of leads, wherein the upper surface of the lead portion that contacts the sealing portion and The lead frame according to any one of [1] to [7], wherein sidewall surfaces of the lead portions are rough surfaces.

- a metal plating layer is provided on a part of the upper surface of the lead portion, and in the rough surface forming step, the upper surface and the sidewall surface of the lead portion on which the metal plating layer is not provided are roughened.

- the metal plating layer includes at least one of an Ag plating layer, a Ni plating layer, a Pd plating layer, and an Au plating layer.

- the lead portion including a thinned inner lead portion is formed from the lower surface side of the lead portion, and in the rough surface forming step, the rough surface is formed on the lower surface of the inner lead portion.

- a die pad portion on which a semiconductor element is mounted is formed so that the plurality of lead portions are arranged around the die pad portion; roughening the upper surface and side wall surfaces of the die pad portion, and at least a portion of the upper surface of the lead portion and the side wall surface of the lead portion to form the rough surface.

- the lead portion has an inner lead thinned from the back surface side, the inner lead surface is formed on the surface side of the inner lead, the inner lead back surface is formed on the back surface of the inner lead, and the inner lead surface is formed on the back surface side of the inner lead.

- An inner lead tip surface is formed on a surface of the inner lead facing the die pad, and an external terminal is formed on a non-thinned portion of the back surface of the lead portion.

- the shortest distance between the smooth surface region and the periphery of the die pad or the lead portion is 0.025 mm or more and 1.0 mm or less. Lead frame.

- a method for manufacturing a lead frame the steps of: preparing a metal substrate; etching the metal substrate to form a die pad and lead portions positioned around the die pad; forming a plating layer on a portion of the die pad; forming a rough surface on a portion of the metal substrate not covered with the plating layer; and removing the plating layer.

- a method of manufacturing a lead frame wherein a smooth surface region is formed on the surface or the surface of the lead portion, and the rough surface region exists so as to surround the entire periphery of the smooth surface region.

- a method of manufacturing a lead frame comprising: a step of forming; and a step of removing the plating layer.

- the plating layer is formed on a portion of the surface of the lead portion, and in the step of removing the other plating layer, the plating layer is present on a portion of the surface of the lead portion.

- An external terminal is formed in the non-coated portion, and at least a part of the surface of the inner lead, the back surface of the inner lead, and the tip surface of the inner lead are rough surfaces, and the external terminal is smooth.

- a metal layer is located on the surface of the lead portion, and a first surface portion of the surface of the lead portion adjacent to the outside of the metal layer is a smooth surface, and is outside the first surface portion.

- a metal layer is positioned on the surface of the lead portion, a recess is formed outside the metal layer in the surface of the lead portion, and a third surface portion adjacent to the outside of the recess is a rough surface.

- a metal layer is positioned on the surface of the lead portion, a recess is formed outside the metal layer in the surface of the lead portion, and a third surface portion adjacent to the outside of the recess is a rough surface. and the inner surface of the recess is roughened.

- the lead portion has an inner lead that is thinned from the back side, and an inner lead tip surface is formed on a surface of the inner lead facing the die pad, and the inner lead tip surface is a rough surface.

- the lead frame according to any one of [35] to [39], wherein

- a step of preparing a metal substrate, and etching the metal substrate to obtain a die pad and leads positioned around the die pad and partially thinned from the back surface side a step of forming a plated layer around the metal substrate; a step of removing a part of the plated layer existing in a region where a rough surface is to be formed; forming a roughened surface on a portion not covered with a layer; and removing the plating layer, wherein the thinned portion of the back surface of the lead portion becomes a roughened surface and is thinned.

- a method of manufacturing a lead frame, wherein the non-smooth portion has a smooth surface.

- a lead frame at least partially formed with a second rough surface, wherein the second rough surface of the lead portion is rougher than the first rough surface of the die pad.

- a third rough surface is formed on the side surface of the die pad, and the roughness of the third rough surface of the die pad is rougher than the roughness of the first rough surface of the die pad, to [43] Leadframe as described.

- the lead portion has an inner lead that is thinned from the back surface side, the inner lead back surface is formed on the back surface side of the inner lead, and a fourth rough surface is formed on the inner lead back surface.

- the lead portion has an inner lead that is thinned from the back surface side, and an inner lead tip surface is formed on a surface of the inner lead facing the die pad, and the inner lead tip surface has a second 5 rough surfaces are formed, and the roughness of the fifth rough surface of the lead portion is rougher than the roughness of the first rough surface of the die pad, any one of [43] to [45]. lead frame described in .

- the S-ratio of the first rough surface is 1.10 or more and less than 1.30, and the S-ratio of the second rough surface is 1.30 or more and 2.30 or less, [43] The lead frame according to any one of [49].

- a method for manufacturing a lead frame the steps of preparing a metal substrate, etching the metal substrate to form a die pad and lead portions positioned around the die pad, forming a coating layer on the lead portion; removing the coating layer existing on at least a part of the surface of the die pad; forming a surface; removing the coating layer present on at least a portion of the surface of the lead; and forming a second rough surface on a portion of the lead not covered by the coating layer.

- the second rough surface of the lead portion is rougher than the first rough surface of the die pad.

- the bumps and the lead frames can be well connected, and moisture can be prevented from entering from the periphery of the semiconductor device toward the electrodes of the semiconductor element.

- a lead frame having a rough surface can be manufactured at low cost.

- the present embodiment it is possible to suppress bleed-out and prevent moisture from entering from the periphery of the semiconductor device toward the electrodes of the semiconductor element.

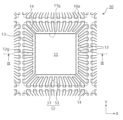

- FIG. 1 is a plan view showing the lead frame according to the first embodiment.

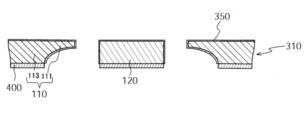

- FIG. FIG. 2 is a partially cut end view of the lead frame according to the first embodiment.

- FIG. 3 is a plan view showing the semiconductor device according to the first embodiment.

- FIG. 4 is a partially cut end view of the semiconductor device according to the first embodiment.

- FIG. 5 is a partially cut end view of a semiconductor device according to a modification of the first embodiment.

- FIG. 6A is a process diagram for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 6B is a process diagram following FIG. 6A for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 6C is a process drawing following FIG. 6B for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 6A is a process diagram for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 6B is a process diagram following FIG. 6A for explaining the method of manufacturing the lead frame according to the first

- FIG. 6D is a process drawing following FIG. 6C for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 6E is a process drawing following FIG. 6D for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 6F is a process drawing following FIG. 6E for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 6G is a process drawing following FIG. 6F for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 6H is a process drawing following FIG. 6G for explaining the method of manufacturing the lead frame according to the first embodiment.

- FIG. 7A is a process diagram for explaining the method of manufacturing the semiconductor device according to the first embodiment.

- FIG. 7B is a process drawing following FIG.

- FIG. 7A for explaining the method of manufacturing the semiconductor device according to the first embodiment.

- FIG. 7C is a process drawing following FIG. 7B for explaining the method of manufacturing the semiconductor device according to the first embodiment.

- FIG. 7D is a process drawing following FIG. 7C for explaining the method of manufacturing the semiconductor device according to the first embodiment.

- FIG. 8 is a plan view showing the lead frame according to the second embodiment.

- FIG. 9 is a cross-sectional view (cross-sectional view taken along line IX-IX in FIG. 8) showing the lead frame according to the second embodiment.

- 10A and 10B are enlarged plan views showing the surface of the die pad and the surface of the lead, respectively.

- FIG. 11 is a plan view showing the semiconductor device according to the second embodiment.

- FIG. 12 is a cross-sectional view (cross-sectional view taken along line XII-XII in FIG. 11) showing the semiconductor device according to the second embodiment.

- 13(a) and 13(b) are enlarged cross-sectional views showing bumps as connection portions, respectively.

- 14(a)-(i) are cross-sectional views showing the method of manufacturing the lead frame according to the second embodiment.

- 15A to 15D are cross-sectional views showing the method of manufacturing the semiconductor device according to the second embodiment.

- FIG. 16 is a partially enlarged cross-sectional view showing the semiconductor device according to the second embodiment.

- FIGS. 17(a) to 17(d) are enlarged plan views respectively showing the surface of the die pad and the surface of the lead portion according to the modified example of the second embodiment.

- FIG. 18 is a plan view showing the lead frame according to the third embodiment.

- FIG. 19 is a cross-sectional view (cross-sectional view taken along line XIX-XIX in FIG. 18) showing the lead frame according to the third embodiment.

- FIG. 20 is a plan view showing the semiconductor device according to the third embodiment.

- FIG. 21 is a cross-sectional view (cross-sectional view taken along the line XXI-XXI of FIG. 20) showing the semiconductor device according to the third embodiment.

- FIG. 22 is an enlarged cross-sectional view showing a bump as a connecting portion.

- 23(a)-(i) are cross-sectional views showing the method of manufacturing the lead frame according to the third embodiment.

- FIG. 24A to 24D are cross-sectional views showing the method of manufacturing the semiconductor device according to the third embodiment.

- FIG. 25 is a partially enlarged cross-sectional view showing the semiconductor device according to the third embodiment.

- FIG. 26 is a cross-sectional view showing the lead frame according to the fourth embodiment.

- FIG. 27 is a cross-sectional view showing the semiconductor device according to the fourth embodiment.

- 28(a)-(j) are cross-sectional views showing the method of manufacturing the lead frame according to the fourth embodiment.

- FIG. 29 is a partially enlarged cross-sectional view showing the semiconductor device according to the fourth embodiment.

- FIG. 30 is a plan view showing a lead frame according to a fifth embodiment

- 31 is a cross-sectional view showing the lead frame according to the fifth embodiment (cross-sectional view taken along line XXXI-XXXI in FIG. 30)

- FIG. 32 is a plan view showing a semiconductor device according to a fifth embodiment

- FIG. 33 is a cross-sectional view showing the semiconductor device according to the fifth embodiment (cross-sectional view taken along line XXXIII-XXXIII in FIG. 32);

- FIG. 34 is an enlarged cross-sectional view showing a bump as a connecting portion;

- 35(a) to 35(j) are sectional views showing a method of manufacturing a lead frame according to the fifth embodiment;

- FIG. 36(a) to 36(d) are cross-sectional views showing the method of manufacturing the semiconductor device according to the fifth embodiment

- FIG. 37 is a partially enlarged cross-sectional view showing a semiconductor device according to a fifth embodiment

- FIG. 38 is a cross-sectional view showing a lead frame according to a sixth embodiment

- FIG. 39 is a cross-sectional view showing a semiconductor device according to a sixth embodiment

- 40(a) to 40(j) are cross-sectional views showing a method of manufacturing a lead frame according to the sixth embodiment

- 41 is a partially enlarged cross-sectional view showing a semiconductor device according to a sixth embodiment

- FIG. FIG. 42 is a cross-sectional view showing a lead frame according to a seventh embodiment

- FIG. 43 is a cross-sectional view showing a semiconductor device according to a seventh embodiment; 44(a) to 44(j) are cross-sectional views showing a method of manufacturing a lead frame according to the seventh embodiment;

- FIG. 45 is a partially enlarged cross-sectional view showing a semiconductor device according to a seventh embodiment;

- FIG. 46 is a cross-sectional view showing a lead frame according to an eighth embodiment;

- FIG. 47 is a cross-sectional view showing a semiconductor device according to an eighth embodiment;

- 48(a)-(j) are cross-sectional views showing a method of manufacturing a lead frame according to the eighth embodiment;

- FIG. 49 is a partially enlarged cross-sectional view showing a semiconductor device according to an eighth embodiment;

- FIG. 50 is a plan view showing a lead frame according to a ninth embodiment

- FIG. 51 is a cross-sectional view showing the lead frame according to the ninth embodiment (cross-sectional view taken along line LI-LI in FIG. 50)

- FIG. 52 is a plan view showing a semiconductor device according to a ninth embodiment

- FIG. 53 is a cross-sectional view (cross-sectional view taken along line LIII-LIII of FIG. 52) showing the semiconductor device according to the ninth embodiment

- 54(a) to 54(e) are sectional views showing a method of manufacturing a lead frame according to the ninth embodiment

- FIG. 55(a) to 55(h) are sectional views showing a method of manufacturing a lead frame according to the ninth embodiment

- FIG. 56(a) to 56(e) are cross-sectional views showing the method of manufacturing the semiconductor device according to the ninth embodiment

- FIG. 57 is a partially enlarged cross-sectional view showing a semiconductor device according to a ninth embodiment

- FIG. 58 is a cross-sectional view showing a lead frame according to a modification of the ninth embodiment

- a numerical range represented using “ ⁇ ” means a range that includes the numerical values described before and after “ ⁇ ” as lower and upper limits, respectively.

- terms such as “film”, “sheet”, and “plate” are not distinguished from each other based on the difference in designation.

- “plate” is a concept that includes members that can be generally called “sheets” and “films.”

- the lead frame 100 is used to manufacture a semiconductor device 200 (see FIGS. 3 and 4).

- the leadframe 100 has a plurality of package regions 100A.

- the plurality of package regions 100A are arranged in multiple rows and multiple stages (matrix). Note that FIG. 1 shows only a portion of the lead frame 100 centering on one package region 100A.

- the package area 100A is an area corresponding to a semiconductor device 200, which will be described later, and is an area surrounded by rectangular imaginary lines (broken lines shown in FIG. 1) (see FIG. 1).

- the lead frame 100 includes a plurality of package regions 100A, but the lead frame 100 is not limited to this embodiment, and the lead frame 100 is composed of only one package region 100A. may have been

- the terms “inner” and “inner” refer to the side toward the center of each package region 100A, and the terms “outer” and “outer” refer to the sides away from the center of each package region 100A. (Connecting bar 130 side).

- the “upper surface” refers to the surface on which the semiconductor element 210 is mounted

- the “lower surface” refers to the surface opposite to the “upper surface”, which is mounted on an external mounting substrate (not shown).

- the term “side wall surface” refers to the surface to be connected, and the “side wall surface” is a surface located between the “upper surface” and the “lower surface”, which constitutes the thickness of the lead frame 100 (metal substrate 310).

- half-etching means etching the material to be etched halfway in its thickness direction.

- the thickness of the material to be etched after half-etching is 30% to 70%, preferably 40% to 60%, of the thickness of the material to be etched before half-etching.

- each package region 100A of the lead frame 100 includes a plurality of lead portions 110, a die pad portion 120, and a connecting bar 130 connecting the lead portions 110.

- Lead portion 110 may include inner lead portion 111 and terminal portion 113 .

- the inner lead portion 111 is a portion thinned from the lower surface side, and is positioned inside (on the die pad portion 120 side) in each package region 100A.

- the terminal portion 113 is positioned on the outside (connecting bar 130 side) in each package region 100A.

- the inner lead portion 111 extends from the terminal portion 113 toward the die pad portion 120 .

- An internal terminal is formed on the upper surface side of the inner lead portion 111 .

- the internal terminals are regions electrically connected to the semiconductor element 210 through the connecting members 220 as described later.

- a metal plating layer 112 is provided on the internal terminals to improve adhesion with the connection member 220 .

- Each lead portion 110 is connected to the semiconductor element 210 via a connection member 220 as will be described later, and is arranged with a space between it and the die pad portion 120 (see FIGS. 4 and 5). .

- the plurality of lead portions 110 are spaced apart from each other along the longitudinal direction of the connecting bar 130 .

- Each lead portion 110 extends from the connecting bar 130 respectively.

- the lead portion 110 is arranged along the periphery of the die pad portion 120 .

- the lead portion 110 is partially thinned from the lower surface side.

- the inner lead portion 111 is the portion that is thinned from the lower surface side.

- a portion of the lead portion 110 that is not thinned from the lower surface side is the terminal portion 113 , and the external terminal 150 is formed on the lower surface of the terminal portion 113 .

- the external terminal 150 is a portion electrically connected to an external mounting board (not shown).

- the external terminal 150 is a portion exposed to the outside of the semiconductor device 200, which will be described later.

- the inner lead portion 111 is thinned by, for example, half-etching from the lower surface side.

- the inner lead portion 111 has an inner lead portion upper surface 111A, an inner lead portion lower surface 111B facing the inner lead portion upper surface 111A, and an inner lead portion side wall surface.

- the inner lead portion upper surface 111A is a part of the upper surface of the lead portion 110 .

- the inner lead side wall surface includes a die pad portion facing surface 111C facing the die pad portion 120 side and a surface facing the adjacent lead portion 110 .

- the inner lead portion lower surface 111B is positioned below the lead portion 110 .

- the terminal portion 113 is located on the connecting bar 130 side. Terminal portion 113 is connected to connecting bar 130 .

- the lower surface of the terminal portion 113 constitutes the external terminal 150 described above.

- the terminal portion 113 has the same thickness as the die pad portion 120 without being half-etched. A portion of the lower surface of the terminal portion 113 located on the connecting bar 130 side may be thinned to form a connection portion with the connecting bar 130 .

- At least a part of the upper surface and side wall surfaces of the lead portions 110 are roughened surfaces, and the lower surfaces of the lead portions 110 (terminal portions 113) are non-roughened surfaces.

- the inner lead portion lower surface 111B is a roughened rough surface.

- the roughened rough surface is shown by the thick broken line.

- the rough surface when simply referred to as a "rough surface”, the rough surface means a rough surface that has been roughened, preferably a rough surface that has been roughened by microetching or the like.

- a thinned portion of the lower surface of the lead portion 110 is a roughened rough surface.

- the entire inner lead portion lower surface 111B is a rough surface.

- the portion of the lower surface of the lead portion 110 that is not thinned is a non-roughened surface.

- the terminal portion 113 is not thinned from the lower surface side, and the entire external terminal 150 located on the lower surface side of the terminal portion 113 has a non-roughened surface.

- the inner lead portion side wall surface including the die pad portion facing surface 111C is a rough surface in which the entire area is roughened.

- a part of the upper surface of the lead portion 110 (inner lead portion 111) located on the die pad portion 120 side may be a non-roughened surface, and the metal plating layer 112 is provided on the non-roughened surface.

- the metal plating layer 112 may be formed by electroplating, for example.

- the thickness of the metal plating layer 112 may be in the range of 1 ⁇ m to 10 ⁇ m.

- the metal plating layer 112 is, for example, Ag plating layer, Ag alloy plating layer, Au plating layer, Au alloy plating layer, Pt plating layer, Cu plating layer, Cu alloy plating layer, Pd plating layer, Ni plating layer, etc. It may well contain one or more of these.

- the metal plating layer 112 preferably includes at least one of an Ag plating layer, a Ni plating layer, a Pd plating layer, and an Au plating layer.

- a well-known base plating may be applied.

- a Ni plating layer, a Cu plating layer, or the like can be used as the base plating.

- a semiconductor element 210 is mounted on the upper surface of the die pad section 120 as described later. Moreover, it is sufficient that a plurality of lead portions 110 are arranged around the die pad portion 120 .

- the upper surface and side wall surfaces of the die pad section 120 may be roughened surfaces, and the lower surface of the die pad section 120 may be a non-roughened surface (see FIG. 2).

- the upper surface of the die pad portion 120 is a region (internal terminal) that is bonded to the semiconductor element 210 via an adhesive 240 such as die attach paste, as will be described later.

- the lower surface of the die pad portion 120 is not thinned by, for example, half-etching, and is a non-roughened surface that is not roughened like the metal substrate 310 before processing, which will be described later.

- a lower surface of the die pad portion 120 is exposed to the outside in a semiconductor device 200 which will be described later.

- the package regions 100A are connected to each other via connecting bars 130, and the connecting bars 130 extend along the X and Y directions.

- the X direction and the Y direction are two directions parallel to each side of the package region 100A in the plane of the lead frame 100, and the X direction and the Y direction are orthogonal to each other.

- Each connecting bar 130 is arranged around the package area 100A and outside the package area 100A.

- Each connecting bar 130 has an elongated rod shape in plan view.

- the width W of each connecting bar 130 (the distance in the direction perpendicular to the longitudinal direction of the connecting bar 130) is not particularly limited, but can be set appropriately within the range of 95 ⁇ m to 250 ⁇ m, for example.

- a plurality of lead portions 110 are connected to each connecting bar 130 at predetermined intervals along the longitudinal direction of the connecting bar 130 , and the die pad portion 120 is supported by the connecting bar 130 via suspension leads 140 . ing.

- the connecting bar 130 in this embodiment is not thinned, it is not limited to this aspect.

- the connecting bar 130 may be thinned by half-etching from its lower surface side.

- the thickness of the connecting bar 130 in this case can be set in consideration of the configuration of the semiconductor device 200 and the like.

- the thickness of the connecting bar 130 can be appropriately set within a range of, for example, 80 ⁇ m to 200

- the lead frame 100 is used to manufacture a semiconductor device 200 having a sealing portion 230 which will be described later.

- the sidewall surface may be a rough surface that is roughened.

- the upper surface of the lead portion 110, the side wall surface of the lead portion 110, and the connecting bar 130 located outside the package region 100A may be roughened surfaces, or may be non-roughened surfaces. It can be a face.

- the lead frame 100 is diced along the connecting bar 130 when the semiconductor device 200 is manufactured using the lead frame 100 . At this time, if each package region 100A is individually molded and diced, if the upper surface of the connecting bar 130 is roughened, there is a risk that foreign matter will be generated when the lead frame 100 is diced. Therefore, by forming the upper surface of the connecting bar 130 as a non-roughened surface, it is possible to suppress the generation of foreign matter when manufacturing the semiconductor device 200 .

- the a * value in the CIELab color space is in the range of 12 to 19

- the b * value is in the range of 12 to 17

- the a * value is preferably 13. ⁇ 18 with b * values in the range of 12-16.

- the surface area ratio increases. Become. Therefore, in a semiconductor device that can be manufactured using the lead frame 100, the adhesion strength with the mold resin increases. As a result, it is possible to prevent moisture in the air from entering the electrodes of the semiconductor element.

- the a * value and the b * value in the CIELab color space of the rough surface in the lead frame 100 according to the present embodiment are within the above range, thereby suppressing the infiltration of moisture in the air to the electrodes of the semiconductor element. possible semiconductor devices can be manufactured.

- the a * value and b * value in the CIELab color space are measured using a spectral density/colorimeter eXact (manufactured by X-rite).

- the CIELab color space (L * a * b * color space) will be described.

- the L * a * b * color space is the CIELab chromaticity diagram recommended by the CIE.

- L * represents lightness

- a * represents the degree of red/magenta or green

- b * represents the degree of yellow or blue.

- the more the value of b * goes to the minus side, the closer to blue, and the more to the plus side, the closer to yellow.

- An L * value of 100 indicates white (total reflection), and an L * value of 0 indicates black (total absorption).

- the center of these three values is the neutral color (gray). That is, movement along the L * axis indicates a change in lightness, and movement on the a * b * plane indicates a change in hue.

- the distance in the L * a * b * space corresponds to the closeness of colors, and it can be said that the closer the distance, the closer the color.

- the a * value in the CIELab color space is between red/magenta and green

- the b * value is between yellow and blue. can be said to be equivalent.

- the arithmetic mean curvature Spc of the peak point of the rough surface is 700 mm ⁇ 1 or more, preferably 1000 mm ⁇ 1 to 5000 mm ⁇ 1 , more preferably 2000 mm ⁇ 1 to 4000 mm -1 .

- the contact point with the contacted body is sharp. It is shown that.

- the adhesion strength with the mold resin is increased, and it is possible to suppress the infiltration of moisture in the air to the electrodes of the semiconductor element. That is, the arithmetic mean curvature Spc of the peak point of the rough surface in the lead frame 100 according to the present embodiment is within the above range, thereby manufacturing a semiconductor device capable of suppressing penetration of moisture in the air to the electrodes of the semiconductor element. can. Furthermore, the arithmetic mean height Sa of the rough surface is preferably 0.12 ⁇ m or more, more preferably in the range of 0.12 ⁇ m to 0.34 ⁇ m.

- the arithmetic mean curvature Spc of the peak points of the rough surface is 700 mm ⁇ 1 or more, and the arithmetic mean height Sa of the rough surface is within a predetermined range, so that moisture in the air can be effectively prevented from reaching the electrodes of the semiconductor element. It is possible to manufacture a semiconductor device that can be effectively suppressed.

- the arithmetic mean curvature Spc of the peak points represents the average of the principal curvatures of the peak points present in the object.

- the arithmetic mean height Sa is a parameter obtained by extending the arithmetic mean height Ra of lines to three dimensions, that is, a plane, and represents the average of the absolute values of the height differences of each point with respect to the average plane of the surface.

- the arithmetic mean curvature Spc and the arithmetic mean height Sa of the summit point are measured using a laser microscope VK-X260 (manufactured by Keyence Corporation, measurement section) and a laser microscope VK-X250 (manufactured by Keyence Corporation, controller section). measured using

- the inventors have found that the state of the roughened surface of the lead frame is important for the lead frame used in the semiconductor device.

- the inventors noticed that attention should be paid to the CIELab color space or the arithmetic mean curvature Spc and the arithmetic mean height Sa of the peak point as indices indicating the state of the rough surface.

- the rough surface according to the present embodiment may be formed, for example, by roughening the metal substrate 310 described later with a micro-etching liquid.

- the microetching liquid that can be used in the present embodiment includes those containing sulfuric acid or hydrochloric acid as main components, those containing hydrogen peroxide and sulfuric acid as main components, and the like.

- the rough surface in this embodiment has an a * value in the range of 12-19 and a b * value in the range of 12-17 in the CIELab color space. Further, the arithmetic mean curvature Spc of the peak points of the rough surface is 700 mm ⁇ 1 or more, and the arithmetic mean height Sa of the rough surface is 0.12 ⁇ m or more.

- the lead frame 100 described above is made of metal such as copper, copper alloy, or Ni alloy.

- the thickness of the lead frame 100 can be set in consideration of the configuration of the semiconductor device 200 and the like.

- the lead portions 110 in this embodiment are arranged along all four sides of the package region 100A, but are not limited to this. may be

- the portion 110 may be connected to the semiconductor element 210 via a bump as a connection member 220 as described later (see FIG. 5).

- the semiconductor device 200 includes a plurality of lead portions 110, a die pad portion 120, a semiconductor element 210, a connection member 220, and a sealing portion 230.

- FIG. 1 An embodiment of a semiconductor device of the present disclosure will be described.

- the semiconductor device 200 includes a plurality of lead portions 110, a die pad portion 120, a semiconductor element 210, a connection member 220, and a sealing portion 230.

- the semiconductor device 200 in this embodiment is manufactured using the lead frame 100 described above. Therefore, the lead portion 110 and the die pad portion 120 in the semiconductor device 200 are provided in the lead frame 100 described above. Therefore, the upper surface of the lead portion 110 outside the metal plating layer 112 (the side farther from the die pad portion 120) and the sidewall surface of the lead portion 110 are rough surfaces. In addition, the upper surface of the die pad portion 120 and the side wall surfaces of the die pad portion 120 are also rough surfaces.

- the lead portion 110 includes an inner lead portion 111 thinned from the lower surface side of the lead portion 110, and the inner lead portion lower surface 111B is a rough surface.

- a sealing portion 230 is in close contact with the lower surface 111B of the inner lead portion.

- the terminal portion 113 of the lead portion 110 is not thinned from the lower surface side.

- the external terminal 150 located on the lower surface of the terminal portion 113 has a non-roughened surface. The external terminals 150 are exposed from the sealing portion 230 .

- the rough surface has an a * value in the range of 12-19 and a b * value in the range of 12-17 in the CIELab color space.

- a * value and b * value in the CIELab color space of the rough surface are within the above range, it is possible to suppress the infiltration of moisture in the air to the electrodes of the semiconductor element 210 .

- the arithmetic mean curvature Spc of the peak point of the rough surface is 700 mm ⁇ 1 or more.

- the arithmetic mean height Sa of the rough surface is preferably 0.12 ⁇ m or more, more preferably in the range of 0.12 ⁇ m to 0.34 ⁇ m.

- the arithmetic mean curvature Spc of the peak points of the rough surface is 700 mm ⁇ 1 or more, and the arithmetic mean height Sa of the rough surface is within a predetermined range. can be suppressed more effectively.

- the semiconductor element 210 can use various semiconductor elements commonly used in the past, and is not particularly limited. For example, integrated circuits, large-scale integrated circuits, transistors, thyristors, diodes, etc. can be used. can be done.

- This semiconductor element 210 has a plurality of electrodes 210A to which connecting members 220 are attached.

- connection member 220 is made of, for example, a highly conductive metal material such as copper or gold. They are electrically connected to the metal plating layers 112 respectively. It should be noted that conductors such as bonding wires and bumps may be used as the connection member 220 .

- the sealing portion 230 seals at least the lead portion 110 , the die pad portion 120 , the semiconductor element 210 and the connection member 220 .

- the sealing portion 230 may be made of, for example, thermosetting resin such as silicone resin or epoxy resin; thermoplastic resin such as PPS resin.

- the thickness of the entire sealing portion 230 is not particularly limited, but can be appropriately set within a range of, for example, approximately 300 ⁇ m to 1500 ⁇ m.

- the length of one side of the sealing portion 230 is not particularly limited, but is appropriately set within a range of about 0.2 mm to 20 mm, for example. can be

- the portion 110 may be connected to the electrode 210A of the semiconductor element 210 via a bump as the connecting member 220 (see FIG. 5).

- FIGS. 1 and 2 A method for manufacturing the lead frame 100 shown in FIGS. 1 and 2 will be described as an example.

- 6A to 6H are process diagrams for explaining the method of manufacturing the lead frame according to this embodiment.