実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

図面において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面に開示された位置、大きさ、範囲などに限定されない。

なお、「膜」という言葉と、「層」という言葉とは、場合によっては、又は、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能である。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能である。

(実施の形態1)

本実施の形態では、本発明の一態様の表示装置について説明する。本実施の形態では、特に表示装置の画素が有する回路構成について説明する。

本発明の一態様の表示装置は表示部を有し、表示部はマトリクス状に配置された複数の画素を有する。画素は、発光デバイス(発光素子ともいう)と、受光デバイス(受光素子ともいう)と、を有する。

発光デバイスは、表示デバイス(表示素子ともいう)として機能する。本発明の一態様の表示装置は、表示部に発光デバイスがマトリクス状に配置されており、当該表示部で画像を表示することができる。また、本発明の一態様の表示装置は、受光デバイスを用いて、光を検出する機能を有する。

発光デバイスは、OLED(Organic Light Emitting Diode)、QLED(Quantum−dot Light Emitting Diode)などのELデバイスを用いることが好ましい。ELデバイスが有する発光物質として、蛍光を発する物質(蛍光材料)、燐光を発する物質(燐光材料)、無機化合物(量子ドット材料など)、熱活性化遅延蛍光を示す物質(熱活性化遅延蛍光(Thermally Activated Delayed Fluorescence:TADF)材料)などが挙げられる。また、発光デバイスとして、マイクロLED(Light Emitting Diode)などのLEDを用いることもできる。なお、TADF材料として、一重項励起状態と三重項励起状態が熱平衡状態にある材料を用いてもよい。このようなTADF材料は発光寿命(励起寿命)が短くなるため、発光デバイスにおける高輝度領域での効率低下を抑制することができる。

本発明の一態様の表示装置の表示部には、受光デバイスがマトリクス状に配置されており、表示部は、画像表示機能に加えて、撮像機能及びセンシング機能の一方または双方を有する。表示部は、イメージセンサまたはタッチセンサに用いることができる。つまり、表示部で光を検出することで、画像を撮像すること、または、対象物(指、手、またはペンなど)の近接もしくは接触を検出することができる。さらに、本発明の一態様の表示装置は、発光デバイスをセンサの光源として利用することができる。したがって、表示装置と別に受光部及び光源を設けなくてもよく、電子機器の部品点数を削減することができる。

受光デバイスをイメージセンサに用いる場合、表示装置は、受光デバイスを用いて、画像を撮像することができる。例えば、本実施の形態の表示装置は、スキャナとして用いることができる。

例えば、イメージセンサを用いて、指紋、掌紋などの生体情報に係るデータを取得することができる。つまり、表示装置に、生体認証用センサを内蔵させることができる。表示装置が生体認証用センサを内蔵することで、表示装置とは別に生体認証用センサを設ける場合に比べて、電子機器の部品点数を少なくでき、電子機器の小型化及び軽量化が可能である。

受光デバイスをタッチセンサに用いる場合、表示装置は、受光デバイスを用いて、対象物の近接または接触を検出することができる。

以下ではより具体的な例について、図面を用いて説明する。

<表示装置のブロック図>

表示装置10のブロック図を、図1Aに示す。表示装置10は、表示部71、駆動回路部72、駆動回路部73、駆動回路部74、及び回路部75等を有する。

表示部71は、マトリクス状に配置された複数の画素80を有する。画素80は、副画素81R、副画素81G、副画素81B、及び副画素82PSを有する。副画素81R、副画素81G、及び副画素81Bは、それぞれ表示デバイスとして機能する発光デバイスを有する。副画素82PSは、光電変換素子として機能する受光デバイスを有する。

なお、本明細書等では、一つの「画素」の中で独立した動作が行われる最小単位を便宜的に「副画素」と定義して説明を行うが、「画素」を「領域」と置き換え、「副画素」を「画素」と置き換えてもよい。

画素80は、配線GL、配線SLR、配線SLG、配線SLB、配線SE、配線RS、及び配線WX等と電気的に接続されている。配線SLR、配線SLG、配線SLBは、駆動回路部72と電気的に接続されている。配線GLは、駆動回路部73と電気的に接続されている。駆動回路部72は、ソース線駆動回路(ソースドライバともいう)として機能する。駆動回路部73は、ゲート線駆動回路(ゲートドライバともいう)として機能する。

画素80は、発光デバイスを有する副画素として、副画素81R、副画素81G、及び副画素81Bを有する。例えば、副画素81Rは赤色を呈する副画素であり、副画素81Gは緑色を呈する副画素であり、副画素81Bは青色を呈する副画素である。これにより、表示装置100はフルカラーの表示を行うことができる。なお、ここでは画素80が3色の副画素を有する例を示したが、4色以上の副画素を有していてもよい。

副画素81Rは、赤色の光を呈する発光デバイスを有する。副画素81Gは、緑色の光を呈する発光デバイスを有する。副画素81Bは、青色の光を呈する発光デバイスを有する。なお、画素80は、他の色の光を呈する発光デバイスを有する副画素を有していてもよい。例えば画素80は、上記3つの副画素に加えて、白色の光を呈する発光デバイスを有する副画素、または黄色の光を呈する発光デバイスを有する副画素などを有していてもよい。

配線GLは、行方向(配線GLの延伸方向)に配列する副画素81R、副画素81G、及び副画素81Bと電気的に接続されている。配線SLR、配線SLG、及び配線SLBは、それぞれ、列方向(配線SLR等の延伸方向)に配列する副画素81R、副画素81G、または副画素81Bと電気的に接続されている。

画素80が有する副画素82PSは、配線SE、配線RS、及び配線WXが電気的に接続されている。配線SE、配線RSは、それぞれ駆動回路部74に電気的に接続され、配線WXは、回路部75に電気的に接続される。

駆動回路部74は、副画素82PSを駆動させるための信号を生成し、配線SE、及び配線RSを介して副画素82PSに出力する機能を有する。回路部75は、副画素82PSから配線WXを介して出力される信号を受信し、画像データとして外部に出力する機能を有する。回路部75は、読み出し回路として機能する。

<画素回路の構成例>

副画素81R、副画素81G、及び副画素81Bに適用することができる画素81の回路図の一例を、図1Bに示す。画素81は、トランジスタM11、トランジスタM12、容量C11、及び発光デバイス11を有する。画素81には、配線GL及び配線SLが電気的に接続される。配線SLは、図1Aに示した配線SLR、配線SLG、及び配線SLBのうちのいずれかに対応する。

トランジスタM11は、ゲートが配線GLと電気的に接続され、ソース及びドレインの一方が配線SLと電気的に接続され、他方が容量C11の一方の電極、及びトランジスタM12のゲートと電気的に接続される。トランジスタM12は、ソース及びドレインの一方が配線EALと電気的に接続され、ソース及びドレインの他方が発光デバイス11の一方の電極、及び容量C11の他方の電極と電気的に接続される。発光デバイス11は、他方の電極が配線ACLと電気的に接続される。

トランジスタM11は、スイッチとして機能する。トランジスタM12は、発光デバイス11に流れる電流を制御するためのトランジスタとして機能する。

ここで、トランジスタM11及びトランジスタM12に、チャネル形成領域にシリコンを有するトランジスタ(以下、Siトランジスタと記す)を適用することが好ましい。または、トランジスタM11に、チャネル形成領域に金属酸化物(酸化物半導体ともいう)を有するトランジスタ(以下、OSトランジスタと記す)を適用し、トランジスタM12にSiトランジスタを適用することが好ましい。

シリコンとしては、単結晶シリコン、多結晶シリコン、非晶質シリコンなどが挙げられる。Siトランジスタは、電界効果移動度が高く、周波数特性が良好である。例えば、チャネル形成領域に低温ポリシリコン(LTPS:Low Temperature Poly Silicon)を有するトランジスタ(以下、LTPSトランジスタと記す)を用いることができる。

Siトランジスタを適用することで、高周波数で駆動する必要のある回路(例えばソースドライバ回路)を表示部と同一基板上に作り込むことができる。これにより、表示装置に実装される外部回路を簡略化でき、部品コスト及び実装コストを削減することができる。

酸化物半導体は、例えば、インジウムと、金属M(Mは、ガリウム、アルミニウム、シリコン、ホウ素、イットリウム、スズ、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、及びマグネシウムから選ばれた一種または複数種)と、亜鉛と、を有することが好ましい。特に、Mは、アルミニウム、ガリウム、イットリウム、及びスズから選ばれた一種または複数種であることが好ましい。特に、OSトランジスタの半導体層として、インジウム、ガリウム、及び亜鉛を含む酸化物(IGZOとも記す)を用いることが好ましい。または、インジウム、スズ、及び亜鉛を含む酸化物を用いることが好ましい。または、インジウム、ガリウム、スズ、及び亜鉛を含む酸化物を用いることが好ましい。

シリコンよりもバンドギャップが広く、かつキャリア密度の小さい酸化物半導体を用いたOSトランジスタは、極めて小さいオフ電流を実現することができる。そのため、その小さいオフ電流により、OSトランジスタと直列に接続された容量に蓄積した電荷を長期間に亘って保持することが可能である。そのため、特に容量C11に直列に接続されるトランジスタM11には、OSトランジスタを用いることが好ましい。トランジスタM11としてOSトランジスタを適用することで、容量C11に保持される電荷が、トランジスタM11を介してリークされることを防ぐことができる。また、容量C11に保持される電荷を長時間に亘って保持できるため、画素81のデータを書き換えることなく、静止画を長期間に亘って表示することが可能となる。

また、室温下における、チャネル幅1μmあたりのOSトランジスタのオフ電流値は、1aA(1×10−18A)以下、1zA(1×10−21A)以下、または1yA(1×10−24A)以下とすることができる。なお、室温下における、チャネル幅1μmあたりのSiトランジスタのオフ電流値は、1fA(1×10−15A)以上1pA(1×10−12A)以下である。したがって、OSトランジスタのオフ電流は、Siトランジスタのオフ電流よりも10桁程度低いともいえる。

配線SLには、データ電位が与えられる。配線GLには、選択信号が与えられる。当該選択信号には、トランジスタを導通状態とする電位と、非導通状態とする電位が含まれる。

配線EALには、第1の電位が与えられる。配線ACLには、第2の電位が与えられる。配線EALは、発光デバイス11の陽極と電気的に接続され、発光デバイス11の陽極に第1の電位を供給する機能をする。配線ACLは、発光デバイス11の陰極と電気的に接続され、発光デバイス11の陰極に第2の電位を供給する機能を有する。第2の電位は、第1の電位より低い電位とする。画素81において、第1の電位をアノード電位、第2の電位をカソード電位ということができる。配線EALは、電源線という場合がある。

副画素82PSに適用することができる回路図の一例を、図1Cに示す。画素82は、トランジスタM16、トランジスタM17、トランジスタM18、容量C21、及び受光デバイス12を有する。

受光デバイス12は、陰極がトランジスタM16のソース及びドレインの一方、容量C21の第1の電極、及びトランジスタM17のゲートと電気的に接続されている。トランジスタM16は、ゲートが配線RSと電気的に接続され、ソース及びドレインの他方が、配線V11と電気的に接続されている。トランジスタM17は、ソース及びドレインの一方が、配線V13と電気的に接続され、ソース及びドレインの他方が、トランジスタM18のソース及びドレインの一方と電気的に接続されている。トランジスタM18は、ゲートが配線SEと電気的に接続され、ソース及びドレインの他方が配線WXに電気的に接続されている。受光デバイス12は、陽極が配線ACLと電気的に接続されている。容量C21は、第2の電極が配線V12と電気的に接続されている。

トランジスタM16、及びトランジスタM18は、スイッチとして機能する。トランジスタM17は、増幅素子(アンプ)として機能する。

トランジスタM16乃至トランジスタM18の全てに、Siトランジスタを適用することが好ましい。または、トランジスタM16に、OSトランジスタを適用し、トランジスタM17に、Siトランジスタを適用することが好ましい。このとき、トランジスタM18は、OSトランジスタ及びSiトランジスタのどちらを適用してもよい。

トランジスタM17には、Siトランジスタを適用することが好ましい。Siトランジスタは、OSトランジスタよりも、高い電界効果移動度を実現することができ、駆動能力及び電流能力に優れる。そのため、トランジスタM17は、トランジスタM16と比較して、より高速な動作が可能となる。トランジスタM17にSiトランジスタを用いることで、受光デバイス12の受光量に基づく微小の電位に応じた出力動作を、トランジスタM18に対して素早く行うことができる。

なお、図1B及び図1Cにおいて、トランジスタをnチャネル型のトランジスタとして表記しているが、pチャネル型のトランジスタを用いることもできる。

画素81及び画素82が有する各トランジスタは、同一基板上に並べて形成されることが好ましい。

画素82において受光デバイス12の陽極と電気的に接続される配線ACLは、画素81の配線ACLと共通にすることができ、第2の電位が与えられる。画素82において、配線ACLは、受光デバイス12の陽極に第2の電位を与える機能を有する。また画素82において、受光デバイス12の陰極と電気的に接続される配線V11は、画素81の配線EALと共通にすることができ、第1の電位が与えられる。第1の電位は、第2の電位より高い電位とする。これにより、受光デバイス12には逆バイアス電圧を印加することができる。

つまり画素81及び画素82は、図2Aに図示するように、配線EALを共通にすることができる。なお図2Aでは、配線V11と、配線V13と、配線V12と、配線EALと、を共通にする例を図示している。つまり、図2Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82が有する複数の配線を共通にすることができる。そのため、画素80に電気的に接続される配線数の削減、及び画素80に与える電位の数を削減することができる。その結果、画素80のレイアウト面積の縮小を図ることができるため、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

<発光デバイス及び受光デバイスの構成例>

本発明の一態様の表示装置に適用できる発光デバイス、及び受光デバイスについて、説明する。本発明の一態様の表示装置10が有する発光デバイス11、及び受光デバイス12の断面概略図を、図2Bに示す。

発光デバイス11は、光を発する機能(以下、発光機能とも記す)を有する。発光デバイス11は、電極13A、EL層17、及び電極15を有する。発光デバイス11は、有機ELデバイス(有機電界発光デバイス)であることが好ましい。電極13Aと電極15との間に挟持されるEL層17は、少なくとも発光層を有する。発光層は、光を発する発光物質を有する。電極13Aと電極15との間に電圧を印加することにより、EL層17から光が射出される。EL層17は、さらに、正孔注入層、正孔輸送層、電子輸送層、電子注入層、キャリアブロック層、励起子ブロック層、電荷発生層など、様々な層を有することができる。

受光デバイス12は、光を検出する機能(以下、受光機能とも記す)を有する。受光デバイス12は、例えば、pn型またはpin型のフォトダイオードを用いることができる。受光デバイス12は、電極13B、受光層19、及び電極15を有する。電極13Bと電極15との間に挟持される受光層19は、少なくとも活性層を有する。受光デバイス12は、光電変換デバイスとして機能し、受光層19に入射する光によって電荷を発生させ、電流として取り出すことができる。この時、電極13Bと電極15との間に電圧を印加してもよい。受光層19に入射する光量に基づき、発生する電荷量が決まる。

受光デバイス12は、可視光を検出する機能を有する。受光デバイス12は、可視光に感度を有する。受光デバイス12は、可視光及び赤外光を検出する機能を有するとさらに好ましい。受光デバイス12は、可視光、または赤外光の少なくともいずれかに感度を有することが好ましい。

なお、本明細書等において、青色(B)の波長領域は、400nm以上490nm未満であり、青色(B)の光は、該波長領域に少なくとも一つの発光スペクトルのピークを有する。緑色(G)の波長領域は、490nm以上580nm未満であり、緑色(G)の光は、該波長領域に少なくとも一つの発光スペクトルのピークを有する。赤色(R)の波長領域は、580nm以上700nm未満であり、赤色(R)の光は、該波長領域に少なくとも一つの発光スペクトルのピークを有する。また、本明細書等において、可視光の波長領域は、400nm以上700nm未満であり、可視光は、該波長領域に少なくとも一つの発光スペクトルのピークを有する。赤外(IR)の波長領域は、700nm以上900nm未満であり、赤外(IR)光は、該波長領域に少なくとも一つの発光スペクトルのピークを有する。

活性層は、半導体を含む。当該半導体として、シリコンなどの無機半導体、及び、有機化合物を含む有機半導体が挙げられる。特に、受光デバイス12として、有機半導体を含む層を有する有機フォトダイオードを用いることが好ましい。有機フォトダイオードは、薄型化、軽量化、及び大面積化が容易であり、また、形状及びデザインの自由度が高いため、様々な表示装置に適用できる。また、有機半導体を用いることで、発光デバイス11が有するEL層と、受光デバイス12が有する受光層と、を同じ方法(例えば、真空蒸着法)で形成することができ、共通の製造装置を使用できるため好ましい。

本発明の一態様の表示装置は、発光デバイス11として有機ELデバイスを用い、受光デバイス12として有機フォトダイオードを好適に用いることができる。有機ELデバイス及び有機フォトダイオードは、同一基板上に形成することができる。したがって、有機ELデバイスを用いた表示装置に有機フォトダイオードを内蔵することができる。本発明の一態様である表示装置は、画像を表示する機能に加えて、撮像機能及びセンシング機能の一方または双方も有する。

電極13A及び電極13Bは、同一面上に設けられる。図2Bは、電極13A及び電極13Bが基板23上に設けられる構成を示している。電極13A及び電極13Bは、例えば、基板23上に形成された導電膜を島状に加工することにより形成できる。つまり、電極13A及び電極13Bは、同じ工程を経て形成することができる。

基板23は、発光デバイス11及び受光デバイス12の形成に耐えうる耐熱性を有する基板を用いることができる。基板23として、絶縁性基板を用いる場合には、ガラス基板、石英基板、サファイア基板、セラミック基板、有機樹脂基板などを用いることができる。また、シリコンまたは炭化シリコンなどを材料とした単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI基板などの半導体基板を用いることができる。

特に、基板23として、前述の絶縁性基板または半導体基板上に、トランジスタなどの半導体素子を含む半導体回路が形成された基板を用いることが好ましい。当該半導体回路は、例えば、画素回路、ゲート線駆動回路(ゲートドライバ)、ソース線駆動回路(ソースドライバ)などを構成していることが好ましい。また、上記に加えて演算回路、記憶回路などが構成されていてもよい。

電極13A、及び電極13Bはそれぞれ、画素電極ということができる。電極15は、発光デバイス11及び受光デバイス12で共通する層であり、共通電極ということができる。画素電極と共通電極のうち、光を射出させる、または光を入射させる側の電極には、可視光及び赤外光を透過する導電膜を用いる。光を射出させない、または光を入射させない側の電極には、可視光及び赤外光を反射する導電膜を用いることが好ましい。

本発明の一態様である表示装置は、共通電極として機能する電極15が、発光デバイス11において陽極または陰極の一方として機能し、受光デバイス12において陽極または陰極の他方として機能する構成とする。

次いで図2Cでは、発光デバイス11において、電極13Aが陽極として機能し、電極15が陰極として機能し、受光デバイス12において、電極13Bが陰極として機能し、電極15が陽極として機能する構成を明示的に示すため、図2Bに回路記号等を追加した模式図を示す。図2Cでは、陽極と陰極の向きを分かりやすくするため、発光デバイス11の左側に発光ダイオードの回路記号を示し、受光デバイス12の右側にフォトダイオードの回路記号を示している。また、電子及びホールの流れる向きを模式的に矢印で示している。また図2Cでは、図2Bの電極15を配線ACLとして図示している。また図2Cでは、基板23上に設けられる配線EAL、及び配線EALに接続されるトランジスタM12及びトランジスタM16がそれぞれ、電極13A及び電極13Bに接続される様子を図示している。

発光デバイス11において、電極13Aは陽極として機能し、トランジスタM12を介して第1の電位を供給する配線EALに接続される。発光デバイス11において、配線ACLは、第2の電位を供給する陰極として機能する。第2の電位は、第1の電位より低い電位とする。

受光デバイス12において、電極13Bは陰極として機能し、トランジスタM16を介して第1の電位を供給する配線EALに接続される。受光デバイス12において、配線ACLは、第2の電位を供給する陽極として機能する。ここで、受光デバイス12では、第2の電位が第1の電位より低い電位であるため、逆バイアス電圧が印加される。

発光デバイス11において、電極13Aが陽極として機能し、電極15が陰極として機能し、受光デバイス12において、電極13Bが陰極として機能し、電極15が陽極として機能する構成とすることにより、電極13Aと電極13Bの電位差を小さくすることができ、電極13Aと電極13Bの間のリーク(以下、サイドリークともいう)を抑制することができる。したがって、SN比(Signal to Noise Ratio)が高い受光デバイスとすることができる。

本発明の一態様の表示装置は、発光デバイス11と受光デバイス12との間のサイドリークが抑制されることから、発光デバイス11と受光デバイス12の間隔を狭くすることができる。つまり、画素に占める発光デバイス11、及び受光デバイス12の割合(以下、開口率ともいう)を高めることができる。また、画素のサイズを小さくすることができ、表示装置の精細度を高めることができる。したがって、光検出機能を有し、高開口率の表示装置を実現することができる。また、光検出機能を有し、高精細の表示装置を実現することができる。

なお、受光デバイス12の精細度としては、100ppi以上、好ましくは200ppi以上、より好ましくは300ppi以上、より好ましくは400ppi以上、さらに好ましくは500ppi以上であって、2000ppi以下、1000ppi以下、または600ppi以下などとすることができる。特に、200ppi以上600ppi以下、好ましくは300ppi以上600ppi以下の精細度で受光デバイス12を配置することで、指紋の撮像に好適に用いることができる。また、精細度が、500ppi以上であると、米国国立標準技術研究所(NIST)などの規格に準拠できるため好適である。なお、受光デバイスの精細度を500ppiと仮定した場合、1画素あたり50.8μmのサイズとなり、指紋の幅(代表的には、300μm以上500μm以下)を撮像するには、十分な精細度であることがわかる。

または、本発明の一態様である表示装置10は、発光デバイス11において、電極13Aが陰極として機能し、電極15が陽極として機能し、受光デバイス12において、電極13Bが陽極として機能し、電極15が陰極として機能する構成としてもよい。

<画素回路の変形例>

以下では、画素81及び画素82について、上記とは異なる構成例について説明する。

画素81及び画素82が有するトランジスタとして、半導体層を介して重なる一対のゲートを有するトランジスタを適用することができる。一対のゲートを有するLTPSトランジスタ及びOSトランジスタの具体的な例については、以降に詳細に説明する。

一対のゲートを有するトランジスタにおいて、一対のゲートが互いに電気的に接続され、同じ電位が与えられる構成とすることで、トランジスタのオン電流が高まること、及び飽和特性が向上するといった利点がある。また、一対のゲートの一方に、トランジスタのしきい値電圧を制御する電位を与えてもよい。また、一対のゲートの一方に、定電位を与えることで、トランジスタの電気特性の安定性を向上させることができる。例えば、トランジスタの一方のゲートを、定電位が与えられる配線と電気的に接続する構成としてもよいし、自身のソースまたはドレインと電気的に接続する構成としてもよい。

図3Aに示す画素81_1は、画素81のトランジスタM12に、一対のゲートを有するトランジスタを適用した場合の例である。トランジスタM12は、一対のゲートの他方が自身のソースまたはドレインと電気的に接続されている。トランジスタM12に、このようなトランジスタを適用することで、飽和特性が向上するため、発光デバイス11の発光輝度の制御が容易となり、表示品位を高めることができる。

図3Bに示す画素82_1は、画素82のトランジスタM17に、一対のゲートを有するトランジスタを適用した場合の例である。トランジスタM17は、一対のゲートの他方が自身のソースまたはドレインと電気的に接続されている。トランジスタM17に、このようなトランジスタを適用することで、飽和特性が向上するため、受光デバイス12が生成する信号の読み出し精度を向上することができる。

図3Cに示す画素81_2は、画素81_1のトランジスタM11に、一対のゲートを有するトランジスタを適用した場合の例である。トランジスタM12は、一対のゲートの他方が自身のソースまたはドレインと電気的に接続されている。トランジスタM11に、このようなトランジスタを適用することで、良好なスイッチング動作を行うことが可能となるため、表示動作に要する時間を短縮することができる。

図3Dに示す画素82_2は、画素82_1のトランジスタM16及びM18に、一対のゲートを有するトランジスタを適用した場合の例である。トランジスタM17は、一対のゲートの他方が自身のソースまたはドレインと電気的に接続されている。トランジスタM16及びM18に、このようなトランジスタを適用することで、良好なスイッチング動作を行うことが可能となるため、リセット動作に要する時間を短縮することができる。

図4Aに示す画素81_3は、画素81にトランジスタM13を追加し、トランジスタM11及びM13を別々に制御するための配線GL1および配線GL2を有する場合の例である。トランジスタM11のゲートは、配線GL1に電気的に接続される。トランジスタM13のゲートは、配線GL2に電気的に接続される。トランジスタM13は、トランジスタM11と同様、スイッチとして機能する。トランジスタM13は、ソース及びドレインの一方が発光デバイス11の一方の電極と電気的に接続され、ソース及びドレインの他方がソース及びドレインの他方が配線RLと電気的に接続される。

配線RLには、リセット電位が与えられる。配線RLに与えられるリセット電位は、リセット電位と発光デバイス11のカソード電位との電位差が、発光デバイス11のしきい値電圧よりも小さくなるような電位とすることができる。リセット電位は、カソード電位よりも高い電位、カソード電位と同じ電位、または、カソード電位よりも低い電位とすることができる。

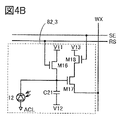

図4Bに示す画素82_3は、画素82におけるトランジスタM18の位置をトランジスタM17と配線V13との間に変更した場合の例である。

図5Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_3を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図5Aでは、配線V11、配線V13、配線V12及び配線EAL、を共通にする例を図示している。つまり、図5Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図5Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_3を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図5Bでは、配線V11、配線V13、及び配線EALを共通にし、ならびに、配線RL及び配線V12を共通にする例を図示している。つまり、図5Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図6Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図6Aでは、配線V11、配線V12及び配線EALを共通にし、配線V13を別の配線とする例を図示している。つまり、図6Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図6Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図6Bでは、配線V11、配線V12、及び配線EALを共通にし、ならびに、配線RL及び配線V13を共通にする例を図示している。つまり、図6Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図7Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図7Aでは、配線V13及び配線EALを共通にし、ならびに、配線V11及び配線V12を共通にする例を図示している。つまり、図7Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図7Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図7Bでは、配線V13及び配線EALを共通にし、ならびに、配線RL、配線V11及び配線V12を共通にする例を図示している。つまり、図7Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図8Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図8Aでは、配線V13及び配線V12を共通にし、ならびに、配線V11及び配線EALを共通にする例を図示している。つまり、図8Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図8Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図8Bでは、配線V11及び配線EALを共通にし、ならびに、配線RL、配線V12及び配線V13を共通にする例を図示している。つまり、図8Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

なお図5A乃至図8Bでは、画素82(または画素82_3)を副画素82PSに適用する例を図示したが、画素82_1乃至82_3を適用する構成としてもよい。また図5A乃至図8Bでは、画素81または81_3を副画素81R、副画素81G、または副画素81Bに適用する図を図示したが、画素81_1または82_2を適用する構成としてもよい。

また図5A乃至図8Bでは、画素80が有するトランジスタに接続される配線を共通にする構成について説明したが、他の構成としてもよい。

図9Aには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82を副画素82PSに適用した場合の画素80が有する回路図において、配線WXに電気的に接続されたトランジスタM21のゲートと、配線RLとを共通にする例を図示している。配線RLに与えられるリセット電位をトランジスタM21のゲートに与えることで、トランジスタM21を定電流源として機能させることができる。また図9Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_3を副画素82PSに適用した場合の画素80が有する回路図において、配線WXに電気的に接続されたトランジスタM21のゲートと、配線RLとを共通にする例を図示している。配線RLに与えられるリセット電位をトランジスタM21のゲートにあたえることで、トランジスタM21を定電流源として機能させることができる。つまり、図9A及び図9Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82(または画素82_3)が有する複数の配線と、そのほかの配線(電位を与える配線)を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図1Aで示した表示装置10のブロック図とは異なる構成について図10Aにて説明する。なお図10Aにおける説明は、図1Aと異なる点についてのみ説明し、共通の符号を付した構成については図1Aと同様である。

図10Aにおいて、画素80は、配線GL、配線SLR、配線SLG、配線SLB、配線TX、配線SE、配線RS、及び配線WX等と電気的に接続されている。

図10Aにおいて、画素80が有する副画素82PSは、配線TX、配線SE、配線RS、及び配線WXが電気的に接続されている。配線TX、配線SE、配線RSは、それぞれ駆動回路部74に電気的に接続され、配線WXは、回路部75に電気的に接続される。

駆動回路部74は、副画素82PSを駆動させるための信号を生成し、配線SE、配線TX、及び配線RSを介して副画素82PSに出力する機能を有する。

図10Aにおいて、副画素82PSに適用することができる回路図の一例を、図10Bに示す。画素82_4は、トランジスタM15、トランジスタM16、トランジスタM17、トランジスタM18、容量C21、及び受光デバイス12を有する。受光デバイス12は、前述の受光デバイスを用いることができる。

トランジスタM15は、ゲートが配線TXと電気的に接続され、ソース及びドレインの一方が、受光デバイス12の陰極と電気的に接続され、ソース及びドレインの他方が、トランジスタM16のソース及びドレインの一方、容量C21の第1の電極、及びトランジスタM17のゲートと電気的に接続されている。

トランジスタM15は、スイッチとして機能する。トランジスタM15は、SiトランジスタまたはOSトランジスタを適用することが好ましい。トランジスタM15及びトランジスタM16にOSトランジスタを適用することで、受光デバイス12に発生する電荷に基づき、トランジスタM17のゲートに保持される電位が、トランジスタM15またはトランジスタM16を介してリークすることを防ぐことができる。

例えば、グローバルシャッタ方式を用いた撮像を行う場合、画素によって電荷の転送動作が終了してから読み出し動作が開始されるまでの期間(電荷保持期間)が異なる。ここで、全ての画素で階調値が等しくなる画像を撮像すると、理想的には全ての画素において同じ値の電位を有する出力信号が得られる。しかし、電荷保持期間の長さが行毎に異なる場合、各行の画素のノードに蓄積されている電荷が時間の経過と共にリークしてしまうと、画素の出力信号の電位が行毎に異なってしまい、行毎にその階調数が変化した画像データが得られてしまう。そこで、トランジスタM15及びトランジスタM16としてOSトランジスタを適用することで、画素のノードの電位変化を極めて小さくすることができる。すなわち、グローバルシャッタ方式を用いて撮像を行っても、電荷保持期間が異なることに起因する画像データの階調の変化を小さく抑え、撮像された画像の品質を向上させることができる。

一方で、トランジスタM17には、Siトランジスタを適用することが好ましい。Siトランジスタは、OSトランジスタよりも、高い電界効果移動度を実現することができ、駆動能力及び電流能力に優れる。そのため、トランジスタM17は、トランジスタM15及びトランジスタM16と比較して、より高速な動作が可能となる。トランジスタM17にSiトランジスタを用いることで、受光デバイス12の受光量に基づく微小の電位に応じた出力動作を、トランジスタM18に対して素早く行うことができる。

つまり、画素82において、トランジスタM15及びトランジスタM16はリーク電流が少なく、かつ、トランジスタM17は駆動能力が高いことで、受光デバイス12で受光し、トランジスタM15を介して転送された電荷がリークすることなく保持でき、かつ、高速で読み出しを行うことができる。

なお、図10Bにおいて、トランジスタをnチャネル型のトランジスタとして表記しているが、pチャネル型のトランジスタを用いることもできる。

図11Aに示す画素82_5は、画素82_4におけるトランジスタM16を、トランジスタM15のソース及びドレインの一方と受光デバイス12の陰極とに接続される位置に変更した場合の例である。

図11Bに示す画素82_6は、画素82_5におけるトランジスタM18の位置をトランジスタM17と配線V13との間に変更した場合の例である。

図12に示す画素82_7は、画素82_6におけるトランジスタM16を、トランジスタM15のソース及びドレインの一方と受光デバイス12の陰極とに接続される位置に変更した場合の例である。

図13Aに示す画素82_8は、画素82_4において、トランジスタM15及び受光デバイスPDを一組として、複数備えた構成の例である。トランジスタM15_1は、ゲートが配線TX_1と電気的に接続され、ソース及びドレインの一方が、受光デバイスPD1の陰極と電気的に接続され、ソース及びドレインの他方が、トランジスタM16のソース及びドレインの一方、容量C21の第1の電極、及びトランジスタM17のゲートと電気的に接続されている。トランジスタM15_2は、ゲートが配線TX_2と電気的に接続され、ソース及びドレインの一方が、受光デバイスPD2の陰極と電気的に接続され、ソース及びドレインの他方が、トランジスタM16のソース及びドレインの一方、容量C21の第1の電極、及びトランジスタM17のゲートと電気的に接続されている。受光デバイスPD1の陽極及び受光デバイスPD2の陽極は、配線ACLに電気的に接続される。

図13Bに示す画素82_9は、画素82_8におけるトランジスタM18の位置をトランジスタM17と配線V13との間に変更した場合の例である。

図14Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図14Aでは、配線V11、配線V13、配線V12及び配線EAL、を共通にする例を図示している。つまり、図14Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図14Bには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_5を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図14Bでは、配線V11、配線V13、配線V12及び配線EAL、を共通にする例を図示している。つまり、図14Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_5が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図15Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図15Aでは、配線V11、配線V13及び配線EALを共通にし、配線V12を別の配線とする例を図示している。つまり、図15Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

なお図15Aにおいて、画素82_4が有する容量C21は、トランジスタM17のゲートの寄生容量を大きくすることで、図15Bに図示するように省略することができる。

図16Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_6を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図16Aでは、配線V11、配線V13、配線V12及び配線EAL、を共通にする例を図示している。つまり、図16Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_6が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図16Bには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_7を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図16Bでは、配線V11、配線V13、配線V12及び配線EAL、を共通にする例を図示している。つまり、図16Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_7が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図17Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_8を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図17Aでは、配線V11、配線V13、配線V12及び配線EAL、を共通にする例を図示している。つまり、図17Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_8が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図17Bには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_9を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図17Bでは、配線V11、配線V13、配線V12及び配線EAL、を共通にする例を図示している。つまり、図17Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_9が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

なお図17A及び図17Bに図示するように、複数の受光デバイスを画素82_8または82_9内に設ける場合、異なる分光感度特性を有する受光デバイスとすることもできる。例えば赤外光の波長領域に分光感度特性を有する受光デバイス12IRと、可視光の波長領域に分光感度特性を有する受光デバイス12を配置する構成とすることができる。図18Aは、図17Aに示す回路図の構成において、赤外光の波長領域に分光感度特性を有する受光デバイス12IRと、可視光の波長領域に分光感度特性を有する受光デバイス12と、を備えた画素80が有する回路図の例である。また、図18Bは、図17Bに示す回路図の構成において、赤外光の波長領域に分光感度特性を有する受光デバイス12IRと、可視光の波長領域に分光感度特性を有する受光デバイス12と、を備えた画素80が有する回路図の例である。

図19Aには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図19Aでは、配線V11、配線V12、配線V13及び配線EALを共通とする例を図示している。つまり、図19Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図19Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_5を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図19Bでは、配線V11、配線V12、配線V13及び配線EALを共通とする例を図示している。つまり、図19Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_5が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図20Aには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図20Aでは、配線V11、配線V13及び配線EALを共通とし、ならびに、配線RL及び配線V12を共通とする例を図示している。つまり、図20Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図20Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図20Bでは、配線V11、配線V13及び配線EALを共通とし、配線V12を省略する例を図示している。つまり、図20Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図21Aには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_6を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図21Aでは、配線V11、配線V12、配線V13及び配線EALを共通とする例を図示している。つまり、図21Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_6が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図21Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_7を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図21Bでは、配線V11、配線V12、配線V13及び配線EALを共通とする例を図示している。つまり、図21Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_7が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

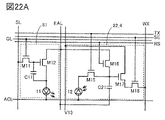

図22Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図22Aでは、配線V11、配線V12及び配線EALを共通にし、配線V13を別の配線とする例を図示している。つまり、図22Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図22Bには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図22Bでは、配線V12、配線V13及び配線EALを共通にし、配線V11を別の配線とする例を図示している。つまり、図22Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図23Aには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図23Aでは、配線V11、配線V12及び配線EALを共通にし、配線RL及び配線V13を共通とする、例を図示している。つまり、図23Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図23Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図23Bでは、配線V12、配線V13及び配線EALを共通にし、配線RL及び配線V11を共通とする例を図示している。つまり、図23Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_4が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図24Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_6を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図24Aでは、配線V11、配線V12及び配線EALを共通にし、配線V13を別の配線とする例を図示している。つまり、図24Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_6が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図24Bには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_7を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図24Bでは、配線V12、配線V13及び配線EALを共通にし、配線V11を別の配線とする例を図示している。つまり、図24Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_7が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図25Aには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_6を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図25Aでは、配線V11、配線V12及び配線EALを共通にし、配線RL及び配線V13を共通とする例を図示している。つまり、図25Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_6が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図25Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_7を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図25Bでは、配線V12、配線V13及び配線EALを共通にし、配線RL及び配線V11を共通とする例を図示している。つまり、図25Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_7が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図26Aには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_6を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図26Aでは、配線V11及び配線EALを共通にし、配線V12及び配線V13を共通にする例を図示している。つまり、図26Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_6が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図26Bには、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_7を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図26Bでは、配線V11及び配線EALを共通にし、配線V12及び配線V13を共通にする例を図示している。つまり、図26Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81及び画素82_7が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図27Aには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_6を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図27Aでは、配線V11及び配線EALを共通にし、配線RL、配線V12、及び配線V13を共通とする例を図示している。つまり、図27Aに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_6が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

図27Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_7を副画素82PSに適用した場合の画素80が有する回路図の例を示す。図27Bでは、配線V11及び配線EALを共通にし、配線RL、配線V12及び配線V13を共通とする例を図示している。つまり、図27Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3及び画素82_7が有する複数の配線を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

また図19A乃至図27Bでは、画素80が有するトランジスタに接続される配線を共通にする構成について説明したが、他の構成としてもよい。

図28Aには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の画素80が有する回路図において、配線WXに電気的に接続されたトランジスタM21のゲートと、配線RLとを共通にする例を図示している。トランジスタM21は、配線RLに与えられるリセット電位に応じて電流を流す電流源として機能させることができる。また図28Bには、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_5を副画素82PSに適用した場合の画素80が有する回路図において、配線WXに電気的に接続されたトランジスタM21のゲートと、配線RLとを共通にする例を図示している。トランジスタM21は、配線RLに与えられるリセット電位に応じて電流を流す電流源として機能させることができる。つまり、図28A及び図28Bに示す回路図では、発光デバイス11に順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、画素81_3および画素82_4(または画素82_5)が有する複数の配線と、そのほかの配線(電位を与える配線)を共通にすることができる。そのため、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。

副画素81R、副画素81G、副画素81B、及び副画素82PSを有する画素80の回路図の一例を、図29に示す。図29では、画素81を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の回路図である。

副画素82PSにおいて、配線V11乃至配線V13は、副画素81Bの配線EALと共通にすることができる。図29に示す回路図では、発光デバイス11R,11G,11Bに順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、副画素81B及び画素82PSが有する複数の配線を共通にすることができる。なお副画素81Bの代わりに、副画素81Rまたは副画素81Gでもよい。図29に示すように、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。その結果、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

なお、副画素81R、副画素81G、副画素81B、及び副画素82PSの構成は、図29に示す構成に限定されない。図29とは異なる画素80の回路図の一例を、図30に示す。図30では、画素81_3を副画素81R、副画素81G、または副画素81Bに適用し、画素82_4を副画素82PSに適用した場合の回路図である。

副画素82PSにおいて、配線V11乃至配線V13は、副画素81Bの配線EALと共通にすることができる。図29に示す回路図では、発光デバイス11R,11G,11Bに順バイアス電圧を印加し、受光デバイス12には逆バイアス電圧を印加する構成において、副画素81B及び副画素82PSが有する複数の配線を共通にすることができる。なお副画素81Bの代わりに、副画素81Rまたは副画素81Gでもよい。図30に示すように、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。その結果、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

なお図30において図示する副画素81R、副画素81G、副画素81B、及び副画素82PSの構成は、図31に示すように別の配線を共通にしてもよい。例えば、配線GL1と配線GL2とを共通にする構成としてもよい。図31に示すように、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。その結果、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

なお図29において図示する副画素81G、副画素81B、及び副画素82PSの構成は、図32に示すように別の配線を共通にしてもよい。例えば副画素82PSに接続される配線は、副画素81Gに接続される配線EALと、副画素81Bに接続される配線EALと、に接続される配線を振り分けてもよい。図32に示すように、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。その結果、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

また上記図17Aおよび図17Bで図示したように画素82PS内に複数の受光デバイスを有する構成では、例えば図33Aに図示する構成のように副画素81Gに接続される配線EALと、副画素81Bに接続される配線EALと、の間に受光デバイスを設ける構成とすることができる。図33Aでは、トランジスタM15_1に接続された受光デバイス12_1と、トランジスタM15_2に接続された受光デバイス12_2と、が副画素81Gに接続される配線EALと、副画素81Bに接続される配線EALとの間に設けられる様子を図示している。図33Aに示すように、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。その結果、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

また上記図33Aとは異なる構成として図33Bでは、トランジスタM15_1に接続された受光デバイス12_1と、トランジスタM15_2に接続された受光デバイス12_2と、が副画素81Gに接続される配線EALと、副画素81Rに接続される配線EALとを横断して設けられる様子を図示している。図33Bに示すように、副画素81R、副画素81G、副画素81B及び副画素82PSを有する画素において、配線数の削減、及び与える電位の数を削減することができる。その結果、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

また上記図33A、図33Bとは異なる構成として図34では、トランジスタM15_1に接続された受光デバイス12_1と、トランジスタM15_2に接続された受光デバイス12_2と、が別の画素の領域に渡って設けられる様子を図示している。図34に示すように、N行目の副画素81R_N、副画素81G_N、副画素81B_N及び副画素82PS_Nを有する画素において、副画素82PS_Nが有するトランジスタM15_2に接続された受光デバイス12_2が、N+1行目の副画素81R_N+1、副画素81G_N+1、副画素81B_N+1を有する画素に設けられる様子を図示している。図34に示すように、複数の行に渡って設けられる副画素82PSにおいても、配線数の削減、及び与える電位の数を削減することができる。その結果、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

また図35Aでは、図29に図示する回路図に対応する画素のレイアウト図の一例を示す。図35A中に図示する符号は、図29で示した構成に対応するものである。なお図35Aでは、理解を容易にするため、発光デバイスおよび受光デバイスに接続される電極までのレイアウト図を示しており、絶縁層、および配線ACLなどの各構成は図示を省略している。また、図35Aでは、トランジスタの形状および大きさ等について、理解を容易にするため、同じ大きさとして図示しているが、チャネル幅およびチャネル長を異ならせる構成としてもよい。

また図35Bでは、図35A中に図示する破線X1−X2における断面模式図である。図35Aに図示するレイアウト図では、図35Bに図示する半導体層SEML、導電層SDM、および導電層GEを有するトランジスタMT、並びにトランジスタMTに接続される導電層PEを図示している。トランジスタMTの断面模式図は、トランジスタM11、M12、およびトランジスタM15乃至M18に適用可能である。図35A及び図35Bに示すように、トランジスタM15乃至M18に接続される配線として、発光素子11Bが設けられる副画素81Bに接続される配線EALを適用することができるため、配線数の削減、及び与える電位の数を削減することができる。その結果、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

<駆動方法例>

次いで上述した画素の駆動方法例について説明する。一例として、図36Aに示す画素81_3の駆動方法の一例について説明する。

図36Bは、図36Aの動作を説明するためのタイミングチャートである。図36Aに示す画素81_3は、配線GL1と配線GL2とに与える信号を図36Bに示すように異ならせることで、画素ごとのトランジスタ特性のばらつきに伴う輝度のばらつきを補正することができる。図36B中に示す期間P1乃至P3での画素81_3の動作について図37A乃至図37Cを参照して説明する。

図37Aは、配線GL1と配線GL2とに与える信号を共にHレベルとする期間P1の動作を説明する図である。図37Aでは、配線GL1と配線GL2とに与える信号のHレベルについて、理解を容易にするために5Vとしている。同様に、配線SLに与える画素81_3に与えるデータ電位を3V、配線EALに与える電位を5V、配線ACLに与える電位を0V、配線RLに与える電位を0Vとしている。このとき、トランジスタM11及びトランジスタM13は共に導通状態となる。図37Aでは、画素81_3への各配線の電位の作用について点線矢印で図示している。容量C11の両端には、3Vの電圧が印加される。当該電圧は、トランジスタM12のゲートとソースの間の電圧(ゲートソース間電圧:Vgs)であり、図37AではVgs=3Vと記している。なお図36Bでは、配線GL1と配線GL2とに与える信号が同時にHレベルとなるよう図示しているが、同時でなくてもよい。

図37Bは、配線GL1に与える信号をHレベル、配線GL2に与える信号をLレベル、とする期間P2の動作を説明する図である。図37Bでは、配線GL2に与える信号のLレベルについて、理解を容易にするために0Vとしている。このとき、トランジスタM11は導通状態、トランジスタM13は非導通状態、となる。図37B中、非導通状態のトランジスタには、バツ印を付している。図37Bでは、画素81_3への各配線の電位の作用について点線矢印で図示している。トランジスタM12には、Vgsに応じて電流が流れる。そのため、トランジスタM12のソース側の電位が上昇し、容量C11の両端に保持される電圧が3VからΔだけ変動する。当該電圧の変動Δの大きさは、トランジスタM12の電界効果移動度などによって画素ごとに異なる。つまり図37Bの動作によって、トランジスタM12の特性のばらつきに応じたVgsが保持されることとなる。なお期間P2の長さは、長すぎると電圧の変動Δが大きくなり、容量C11の両端の電圧が小さくなるため、期間P1と比べて短いことが好ましい。

図37Cは、配線GL1と配線GL2とに与える信号を共にLレベルとする期間P3の動作を説明する図である。図37Cでは、配線GL1と配線GL2に与える信号のLレベルについて、理解を容易にするために0Vとしている。このとき、トランジスタM11及びトランジスタM13は非導通状態、となる。図37C中、非導通状態のトランジスタには、バツ印を付している。図37Cでは、画素81_3への各配線の電位の作用について点線矢印で図示している。トランジスタM13は、容量C11の両端に保持される電圧が3VからΔだけ変動した電圧(3V−Δ)に応じた電流を発光デバイス11に流すことができる。Vgsとなる電圧(3V−Δ)によって、トランジスタM12の特性のばらつきが補正された電流を発光デバイス11に流すことができる。

また図38A及び図38Bでは、異なる行に設けられた、図36Aに示す画素81_3を駆動する際の駆動方法の一例について説明する。

図38Aでは、表示装置10における副画素81R、81G、81Bに画素81_3が適用された際のブロック図を示す。表示装置10は、表示部71、駆動回路部72、駆動回路部73等を有する。表示部71は、マトリクス状に配置された複数の画素80_N及び画素80_N+1を有する。図38Aでは、異なる行にある画素として、画素80_N及び画素80_N+1を図示している。図38Aでは、画素80_Nのある行の配線GL1、GL2として、配線GL1_N、GL2_Nを図示している。また図38Aでは、画素80_N+1のある行の配線GL1、GL2として、配線GL1_N+1、GL2_N+1を図示している。

図38Bは、図38Aに示す配線GL1_N、GL2_N、配線GL1_N+1、GL2_N+1に与える信号を説明するためのタイミングチャートである。図38Bにおいて、期間P_Fは、1フレーム期間、期間P_Eは発光デバイス11の発光期間である。また期間P_GS1、P_GS2が各配線に与えられる画素を選択するための信号が与えられる期間である。なお図38Bでは、配線GL1_NとGL2_N、及び配線GL1_N+1とGL2_N+1は、同じタイミングで信号が変化する様子を図示しているが、上記図36Bで図示したように異なるタイミングで信号が変化してもよい。

期間P_GS1における画素の選択期間では、発光デバイス11を発光させて画像を表示するための信号を配線SLに与える。期間P_GS2における画素の選択期間では、発光デバイス11を消灯させて黒表示するための信号を配線SLに与える。当該構成とすることで、1フレーム期間中ずっと点灯しているのではなく、1フレーム期間中に消灯期間を設ける駆動方法(デューティ駆動)とすることができる。デューティ駆動を用いることで、動画を表示する際の残像現象を低減することができるため、動画表示性能の高い表示装置を実現できる。特にVR機器などでは、残像を低減することで、いわゆるVR酔いを軽減することができる。

デューティ駆動において、一水平期間に対する点灯期間の割合を、デューティ比と呼ぶことができる。なお、デューティ比は自由に設定することが可能であり、例えば0%より高く、100%以下の範囲で適宜調整することができる。

次いで図10Bに示す画素82_4の駆動方法の一例について、図39に示すタイミングチャートを用いて説明する。図39には、配線TX、配線SE、配線RS、及び配線WXに入力される信号を示している。

時刻T21以前において、配線TX、配線SE、及び配線RSにはローレベル電位が与えられる。また、配線WXはデータが出力されていない状態であり、ここではローレベル電位として示している。なお、配線WXに所定の電位が与えられていてもよい。

時刻T21において、配線TXと配線RSに、トランジスタを導通状態とする電位(ここではハイレベル電位)が与えられる。また配線SEには、トランジスタを非導通状態とする電位(ここではローレベル電位)が与えられる。

このとき、トランジスタM15とトランジスタM16が導通状態になることで、配線V11からトランジスタM16及びトランジスタM15を介して、受光デバイス12の陽極に、陰極の電位よりも低い電位が与えられる。すなわち、受光デバイス12に逆バイアス電圧が印加された状態となる。

容量C21の第1の電極にも、配線V11の電位が供給され、容量C21が充電された状態となる。

期間T21−T22は、リセット(初期化)期間とも呼ぶことができる。

時刻T22において、配線TX及び配線RSに、ローレベル電位が与えられる。これにより、トランジスタM15とトランジスタM16とが互いに非導通状態となる。

トランジスタM15が非導通状態となるため、受光デバイス12には逆バイアス電圧が印加された状態で保持される。ここで、受光デバイス12に入射される光によって光電変換が起こり、受光デバイス12に電荷が蓄積される。

期間T22−T23は、露光期間とも呼ぶことができる。露光期間は、受光デバイス12の感度、入射光の光量などに応じて設定すればよいが、少なくともリセット期間と比較して十分に長い期間を設定することが好ましい。

期間T22−T23において、トランジスタM15及びトランジスタM16が非導通状態となるため、容量C21の第1の電極の電位は、配線V11から供給される電位に保持された状態となる。

時刻T23において、配線TXにハイレベル電位が与えられる。これにより、トランジスタM15が導通状態となり、受光デバイス12に蓄積された電荷が、トランジスタM15を介して容量C21の第1の電極に転送される。これにより、容量C21の第1の電極が接続されるノードの電位は、受光デバイス12に蓄積された電荷量に応じて上昇する。その結果、トランジスタM17のゲートには、受光デバイス12の露光量に応じた電位が与えられた状態となる。

時刻T24において、配線TXにローレベル電位が与えられる。これにより、トランジスタM15が非導通状態となり、トランジスタM17のゲートが接続されるノードがフローティング状態となる。受光デバイス12の露光は常に生じているため、期間T23−T24における転送動作が完了した後に、トランジスタM15を非導通状態とすることで、トランジスタM17のゲートが接続されるノードの電位が変化することを防ぐことができる。

時刻T25において、配線SEにハイレベル電位が与えられる。これにより、トランジスタM18が導通状態となる。期間T25−T26は、読み出し期間ともいうことができる。

例えば、トランジスタM17と回路部75が有するトランジスタとでソースフォロワ回路を構成し、データを読み出すことができる。この場合、配線WXに出力されるデータ電位DSは、トランジスタM17のゲート電位に応じて決定される。具体的には、トランジスタM17のゲート電位から、トランジスタM17のしきい値電圧を差し引いた電位が、データ電位DSとして配線WXに出力され、当該電位を回路部75が有する読み出し回路により読み出される。

なお、トランジスタM17と回路部75が有するトランジスタとでソース接地回路を構成し、回路部75が有する読み出し回路により、データを読み出すこともできる。

時刻T26において、配線SEにローレベル電位が与えられる。これにより、トランジスタM18が非導通状態となる。これにより、画素82のデータの読み出しが完了する。時刻T26以降は、次の行以降のデータの読み出し動作が順次行われる。

図39で例示した駆動方法を用いることで、露光期間と読み出し期間を別々に設定することができるため、表示部71に設けられた全ての画素82で同時に露光し、その後、データを順次読み出すことができる。これにより、いわゆるグローバルシャッタ駆動を実現できる。グローバルシャッタ駆動を実行する場合には、画素82内のスイッチとして機能するトランジスタ(特にトランジスタM15及びトランジスタM16)に、非導通状態におけるリーク電流が極めて低い、酸化物半導体が適用されたトランジスタを用いることが好ましい。

以上が、画素82_4の駆動方法の例についての説明である。

上述したように、本発明の一態様の表示装置では、発光デバイスに順バイアス電圧を印加し、受光デバイスに逆バイアス電圧を印加する副画素を備えた画素において、配線EALと別の配線の機能を共通にすることができる。そのため、画素に電気的に接続される配線数の削減、及び画素に与える電位の数を削減することができる。その結果、画素のレイアウト面積の縮小を図ることができるため、光検出機能を有しつつ、高精細な表示部を有する表示装置とすることができる。また光検出機能を有しつつ、高解像度の表示部を有する表示装置とすることができる。

(実施の形態2)

本実施の形態では、本発明の一態様の表示装置について説明する。特に本実施の形態では、表示装置が有する受光デバイス及び発光デバイスの構成例について説明する。

実施の形態1で説明した表示装置10と異なる例を、図40Aに示す。図40Aに示す表示装置10Aは、発光デバイス11aと、受光デバイス12aと、を有する。表示装置10Aは、発光デバイス11aが、EL層17と電極15との間に層21を有し、受光デバイス12aが、受光層19と電極15との間に層21を有する点で、前述の表示装置10と主に異なる。層21は、発光デバイス11aと受光デバイス12aで共通する層であり、共通層ということができる。例えば、正孔注入層、正孔輸送層、電子輸送層、及び電子注入層の少なくとも1つを、受光デバイス及び発光デバイスで共通の層とすることが好ましい。

図40Aに示すように、発光デバイス11aにおいて、電極13Aが陽極として機能し、電極15が陰極として機能し、受光デバイス12aにおいて、電極13Bが陰極として機能し、電極15が陽極として機能する構成とする場合、層21は、例えば、電子注入性の高い物質を含む層(電子注入層)などを有する。層21は、発光デバイス11aにおいて、陰極として機能する電極15からEL層17に電子を注入する電子注入層として機能することができる。

なお、電子注入性の高い物質を含む層(電子注入層)などを有する層21は、受光デバイス12aにおいて、特定の機能を有さない。前述したように、層21は、発光デバイス11aにおいて、電子注入層として機能するように構成すればよい。

受光デバイスと発光デバイスが共通で有する層は、発光デバイスにおける機能と受光デバイスにおける機能とが異なる場合がある。本明細書中では、発光デバイスにおける機能に基づいて構成要素を呼称することがある。例えば、正孔注入層は、発光デバイスにおいて正孔注入層として機能し、受光デバイスにおいて正孔輸送層として機能する。同様に、電子注入層は、発光デバイスにおいて電子注入層として機能し、受光デバイスにおいて電子輸送層として機能する。また、受光デバイスと発光デバイスが共通で有する層は、発光デバイスにおける機能と受光デバイスにおける機能とが同一である場合もある。正孔輸送層は、発光デバイス及び受光デバイスのいずれにおいても、正孔輸送層として機能し、電子輸送層は、発光デバイス及び受光デバイスのいずれにおいても、電子輸送層として機能する。

図40Bに示すように、発光デバイス11aにおいて、電極13Aが陰極として機能し、電極15が陽極として機能し、受光デバイス12aにおいて、電極13Bが陽極として機能し、電極15が陰極として機能する構成とする場合、層21は、例えば、正孔注入性の高い物質を含む層(正孔注入層)などを有する。層21は、発光デバイス11aにおいて、陽極として機能する電極15からEL層17にホールを注入する正孔注入層として機能することができる。

なお、正孔注入性の高い物質を含む層(正孔注入層)などを有する層21は、受光デバイス12aにおいて、特定の機能を有さない。前述したように、層21は、発光デバイス11aにおいて、正孔注入層として機能するように構成すればよい。

本発明の一態様の表示装置を、図40Cに示す。図40Cに示す表示装置10Bは、発光デバイス11bと、受光デバイス12bと、を有する。発光デバイス11bが有するEL層17は、層31A、発光層41、及び層37Aがこの順で積層された積層構造を有する。受光デバイス12bが有する受光層19は、層37B、活性層43、及び層31Bがこの順で積層された積層構造を有する。

発光デバイス11bにおいて、電極13Aは陽極として機能し、電極15は陰極として機能する。受光デバイス12bにおいて、電極13Bは陰極として機能し、電極15は陽極として機能する。層21は、例えば、電子注入性の高い物質を含む層(電子注入層)などを有する。

層31A及び層31Bは、例えば、正孔輸送性の高い物質を含む層(正孔輸送層)を有する。さらに、層31A及び層31Bは、正孔注入性の高い物質を含む層(正孔注入層)を有してもよい。なお、層31A及び層31Bがそれぞれ正孔輸送性の高い物質を含む場合、層31Aが有する正孔輸送性の高い物質と、層31Bが有する正孔輸送性の高い物質は同じであってもよく、異なってもよい。同様に、層31A及び層31Bがそれぞれ正孔注入性の高い物質を含む場合、層31Aが有する正孔注入性の高い物質と、層31Bが有する正孔注入性の高い物質は同じであってもよく、異なってもよい。また、層31A及び層31Bがそれぞれ積層構造を有してもよい。

層37A及び層37Bは、例えば、電子輸送性の高い物質を含む層(電子輸送層)を有する。さらに、層37A及び層37Bは、電子注入性の高い物質を含む層(電子注入層)を有してもよい。なお、層37A及び層37Bがそれぞれ電子輸送性の高い物質を含む場合、層37Aが有する電子輸送性の高い物質と、層37Bが有する電子輸送性の高い物質は同じであってもよく、異なってもよい。同様に、層37A及び層37Bがそれぞれ電子注入性の高い物質を含む場合、層37Aが有する電子注入性の高い物質と、層37Bが有する電子注入性の高い物質は同じであってもよく、異なってもよい。また、層37A及び層37Bがそれぞれ積層構造を有してもよい。

活性層43は、半導体を含む。活性層43は、特に有機半導体を含むことが好ましい。

発光層41は、光を発する発光物質を有する。発光デバイス11において、一対の電極(電極13A及び電極15)の間に設けられた層31A、発光層41、及び層37Aを有する構成は単一の発光ユニットとして機能することができ、本明細書等において発光デバイス11bの構成をシングル構造と呼ぶ場合がある。

発光デバイス11bは、電極13A側から順に、正孔輸送性の高い物質を含む層(正孔輸送層)を有する層31A、発光層41、電子輸送性の高い物質を含む層(電子輸送層)を有する層37Aを有する。受光デバイス12bは、電極13B側から順に、電子輸送性の高い物質を含む層(電子輸送層)を有する層37B、活性層43、正孔輸送性の高い物質を含む層(正孔輸送層)を有する層31Bを有する。本発明の一態様である表示装置において、発光層及び活性層を挟む電子輸送性の高い物質を含む層(電子輸送層)と正孔輸送性の高い物質を含む層(正孔輸送層)の積層順が、発光デバイスと受光デバイスで逆とする。このような構成とすることにより、発光デバイスと受光デバイスとの間のサイドリークを抑制することができる。

前述の表示装置10Bと異なる表示装置の構成を、図40Dに示す。図40Dに示す表示装置10Cは、発光デバイス11cと、受光デバイス12cと、を有する。発光デバイス11cは、EL層17を構成する層の積層順が逆である点で、前述の発光デバイス11bと主に異なる。受光デバイス12cは、受光層19を構成する層の積層順が逆である点で、前述の受光デバイス12bと主に異なる。

発光デバイス11cが有するEL層17は、層37A、発光層41、及び層31Aがこの順で積層された積層構造を有する。受光デバイス12cが有する受光層19は、層31B、活性層43、及び層37Bがこの順で積層された積層構造を有する。

発光デバイス11bにおいて、電極13Aは陰極として機能し、電極15は陽極として機能する。受光デバイス12において、電極13Bは陽極として機能し、電極15は陰極として機能する。層21は、例えば、正孔注入性の高い物質を含む層(正孔注入層)などを有する。

前述の表示装置と異なる構成について、説明する。以降では、発光デバイスにおいて電極13Aが陽極として機能し、電極15が陰極として機能し、受光デバイスにおいて電極13Bが陰極として機能し、電極15が陽極として機能する構成を例に挙げて、説明する。

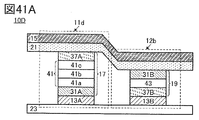

本発明の一態様の表示装置を、図41Aに示す。図41Aに示す表示装置10Dは、発光デバイス11dと、受光デバイス12bと、を有する。発光デバイス11dが有する発光層41は、発光層41a、発光層41b、及び発光層41cがこの順で積層された積層構造を有する。層31Aと層37Aの間に複数の発光層(例えば、発光層41a、発光層41b及び発光層41c)が設けられる構成も、シングル構造と呼ぶことができる。

本発明の一態様の表示装置を、図41Bに示す。図41Bに示す表示装置10Eは、発光デバイス11eと、受光デバイス12eと、を有する。

発光デバイス11eは、層31Aが、層33Aと、層33A上の層35Aとの積層構造を有する点で、前述の発光デバイス11bと主に異なる。受光デバイス12eは、層31Bが、層35Bと、層35B上の層33Bとの積層構造を有する点で、前述の受光デバイス12bと主に異なる。

層33A及び層33Bは、例えば、正孔注入性の高い物質を含む層(正孔注入層)を有する。層33Aが有する正孔注入性の高い物質と、層33Bが有する正孔注入性の高い物質は同じであってもよく、異なってもよい。

層35A及び層35Bは、例えば、正孔輸送性の高い物質を含む層(正孔輸送層)を有する。層35Aが有する正孔輸送性の高い物質と、層35Bが有する正孔輸送性の高い物質は同じであってもよく、異なってもよい。

このような層構造とすることで、発光デバイス11eは、発光層41に効率よくキャリアを注入し、発光層41内におけるキャリアの再結合の効率を高めることが可能となる。なお、前述したように受光デバイス12eにおいて、層33Bは正孔輸送層として機能する。

本発明の一態様の表示装置を、図41Cに示す。図41Cに示す表示装置10Fは、発光デバイス11fと、受光デバイス12fと、を有する。

発光デバイス11fは、電極13AとEL層17との間に光学調整層39Aを有する点で、前述の発光デバイス11eと主に異なる。受光デバイス12fは、電極13Bと受光層19との間に光学調整層39Bを有する点で、前述の受光デバイス12eと主に異なる。

光学調整層39A、及び光学調整層39Bは、可視光に対する透過性が高い導電性材料を用いることが好ましい。光学調整層39A、及び光学調整層39Bは、可視光及び赤外光に対する透過性が高い導電性材料を用いることがさらに好ましい。光学調整層39A、及び光学調整層39Bは、例えば、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを含む酸化亜鉛、シリコンを含むインジウム錫酸化物、シリコンを含むインジウム亜鉛酸化物などの導電性酸化物を用いることができる。

ここで、電極13A、及び電極13Bに、可視光に対して反射性を有する導電膜を用い、電極15に、可視光に対して反射性及び透過性を有する導電膜を用いる。これにより、発光デバイス11f及び受光デバイス12fは、いわゆるマイクロキャビティ構造(微小共振器構造)が実現される。発光デバイス11fは、特定の波長の光が強められ、色純度の高い発光デバイスとすることができる。受光デバイス12fは、検出したい特定の波長の光が強められ、感度の高い受光デバイスとすることができる。

なお、発光デバイス11fが有する光学調整層39Aと、受光デバイス12fが有する光学調整層39Bで膜厚を異ならせることで、それぞれの光路長を異ならせることができる。各光学調整層は、それぞれ厚さの異なる導電膜を用いてもよいし、単層構造と複数構造で構造を異ならせてもよい。

本発明の一態様の表示装置を、図42に示す。図42に示す表示装置10Gは、発光デバイス11gと、受光デバイス12bと、を有する。

発光デバイス11gは、電極13Aと電極15の間に、EL層47、中間層50及びEL層17がこの順で積層された積層構造を有する。EL層47は、層51A、発光層61及び層57Aがこの順で積層された積層構造を有する。

なお、層51A、発光層61、及び層57Aはそれぞれ、積層構造を有してもよい。層51Aは、層31Aの記載を参照できるため、詳細な説明は省略する。発光層61は、発光層41の記載を参照できるため、詳細な説明は省略する。層57Aは、層37Aの記載を参照できるため、詳細な説明は省略する。

発光デバイス11gのように、複数の発光ユニット(EL層17、及びEL層47)が、中間層50(電荷発生層ともいう)を介して直列に接続された構成を、本明細書等ではタンデム構造と呼ぶ場合がある。なお、タンデム構造をスタック構造と呼んでもよい。タンデム構造とすることで、高輝度発光が可能な発光デバイスとすることができる。

発光デバイスの発光色は、EL層17を構成する材料によって、赤、緑、青、シアン、マゼンタ、黄または白などとすることができる。また、発光デバイスにマイクロキャビティ構造を付与することにより色純度をさらに高めることができる。

白色の光を発する発光デバイスは、発光層41に2種類以上の発光物質を含む構成とすることが好ましい。2つの発光物質を含む構成とする場合は、各発光が補色の関係となるような発光物質を選択すればよい。例えば、第1の発光層の発光色と第2の発光層の発光色を補色の関係になるようにすることで、発光デバイス全体として白色発光する発光デバイスを得ることができる。3つ以上の発光物質を含む構成とする場合は、各々の発光色の混合により、白色発光する構成とすることができる。また、発光層を2つ以上有する発光デバイスの場合も同様である。例えば、図41Aに示す発光デバイス11dは、発光層41a、発光層41b、及び発光層41cの発光色の混合により、シングル構造の白色発光デバイスを実現することができる。

発光層には、R(赤)、G(緑)、B(青)、Y(黄)、O(橙)等の発光を示す発光物質を2以上含むことが好ましい。または、発光物質を2以上有し、それぞれの発光物質の発光は、R、G、Bのうち2以上の色のスペクトル成分を含むことが好ましい。

なお、発光デバイスと受光デバイスの組み合わせは、特に限定されない。前述の発光デバイスのいずれか一または複数と、前述の受光デバイスのいずれか一または複数と、を有する表示装置とすることができる。例えば、発光デバイス11eと、受光デバイス12cとを有する表示装置としてもよい。

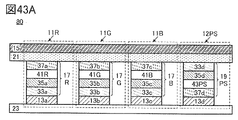

表示装置の一画素に設けられる発光デバイス及び受光デバイスの構成例を、図43Aに示す。図43Aは、画素80においてRGBの三色の副画素を有する画素の断面概略図である。画素80の断面概略図では、発光デバイス11R、発光デバイス11G、発光デバイス11B、及び受光デバイス12PSを示している。

なお、図43Aは、発光デバイス11R、発光デバイス11G、及び発光デバイス11Bに、図41Bに示す発光デバイス11eの構成を適用し、受光デバイス12PSに、図41Bに示す受光デバイス12eの構成を適用した例を示している。

発光デバイス11Rは、副画素81Rが有する発光デバイスに適用することができ、赤色の光を射出する機能を有する。発光デバイス11Rは、基板23上に電極13a、EL層17R、層21、及び電極15をこの順で積層された積層構造を有する。EL層17Rは、層33a、層35a、発光層41R、及び層37aをこの順で積層された積層構造を有する。

層33aは、正孔注入性の高い物質を含む層(正孔注入層)を有する。層35aは、正孔輸送性の高い物質を含む層(正孔輸送層)を有する。発光層41Rは、赤色の発光を示す発光物質を有する。層37aは、電子輸送性の高い物質を含む層(電子輸送層)を有する。層21は、電子注入性の高い物質を含む層(電子注入層)を有する。

発光デバイス11Rにおいて、電極13aは陽極として機能し、電極15は陰極として機能する。つまり、電極13aに供給される電位は、電極15に供給される電位よりも高い構成とする。

発光デバイス11Gは、副画素81Gが有する発光デバイスELGに適用することができ、緑色の光を射出する機能を有する。発光デバイス11Gは、基板23上に電極13b、EL層17G、層21、及び電極15をこの順で積層された積層構造を有する。EL層17Gは、層33b、層35b、発光層41G、及び層37bをこの順で積層された積層構造を有する。

層33bは、正孔注入性の高い物質を含む層(正孔注入層)を有する。層35bは、正孔輸送性の高い物質を含む層(正孔輸送層)を有する。発光層41Gは、緑色の発光を示す発光物質を有する。層37bは、電子輸送性の高い物質を含む層(電子輸送層)を有する。

発光デバイス11Gにおいて、電極13bは陽極として機能し、電極15は陰極として機能する。つまり、電極13bに供給される電位は、電極15に供給される電位よりも高い構成とする。

発光デバイス11Bは、副画素81Bが有する発光デバイスELBに適用することができ、青色の光を射出する機能を有する。発光デバイス11Bは、基板23上に電極13c、EL層17B、層21、及び電極15をこの順で積層された積層構造を有する。EL層17Bは、層33c、層35c、発光層41B、及び層37cをこの順で積層された積層構造を有する。

層33cは、正孔注入性の高い物質を含む層(正孔注入層)を有する。層35cは、正孔輸送性の高い物質を含む層(正孔輸送層)を有する。発光層41Bは、青色の発光を示す発光物質を有する。層37cは、電子輸送性の高い物質を含む層(電子輸送層)を有する。

発光デバイス11Bにおいて、電極13cは陽極として機能し、電極15は陰極として機能する。つまり、電極13cに供給される電位は、電極15に供給される電位よりも高い構成とする。

受光デバイス12PSは、副画素82PSが有する受光デバイス12に適用することができ、可視光及び赤外光を検出する機能を有する。受光デバイス12PSは、基板23上に電極13d、受光層19PS、層21、及び電極15をこの順で積層された積層構造を有する。受光層19PSは、層37d、活性層43、層35d、及び層33dをこの順で積層された積層構造を有する。

層37dは、電子輸送性の高い物質を含む層(電子輸送層)を有する。活性層43PSは、半導体を含む。活性層43PSは、特に有機半導体を含むことが好ましい。層35dは、正孔輸送性の高い物質を含む層(正孔輸送層)を有する。層33dは、正孔注入性の高い物質を含む層(正孔注入層)を有する。なお、受光デバイス12PSにおいて、層33dは、正孔輸送層として機能する。

受光デバイス12PSにおいて、電極13dは陰極として機能し、電極15は陽極として機能する。つまり、電極13dに供給される電位は、電極15に供給される電位よりも高い構成とする。受光デバイス12PSは、電極13dと電極15との間に逆バイアスが印加される。

電極13a、電極13b、電極13c、及び電極13dは、基板23上に設けられる。電極13a、電極13b、電極13c、及び電極13dは、例えば、基板23上に形成された導電膜を島状に加工することにより形成できる。電極13a、電極13b、電極13c、及び電極13dはそれぞれ、画素電極として機能する。電極13a、電極13b、電極13c、及び電極13dについては、前述の電極13A及び電極13Bの記載を参照できるため、詳細な説明は省略する。電極15は、共通電極として機能する。電極15については、前述の記載を参照できるため、詳細な説明は省略する。

層33a、層33b、層33c、及び層33dについては、前述の層33A及び層33Bの記載を参照できるため、詳細な説明は省略する。層35a、層35b、層35c、及び層35dについては、前述の層35A及び層35Bの記載を参照できるため、詳細な説明は省略する。層37a、層37b、層37c、及び層37dについては、前述の層37A及び層37Bの記載を参照できるため、詳細な説明は省略する。共通層である層21については、前述の記載を参照できるため、詳細な説明は省略する。

図43Bは、発光デバイス11Rから射出される赤色(R)の光、発光デバイス11Gから射出される緑色(G)の光、発光デバイス11Bから射出される青色(B)の光、及び受光デバイス12PSに入射する光をそれぞれ、矢印で模式的に示している。

前述の画素80と異なる構成例を、図44Aに示す。図44Aに示す画素80Aは、発光デバイス11R、発光デバイス11G、発光デバイス11B、発光デバイス11IR、及び受光デバイス12PSを有する。図44Aは、発光デバイス11R、発光デバイス11G、発光デバイス11B、発光デバイス11IR、及び受光デバイス12PSの構成を示す断面概略図である。画素80Aは、発光デバイス11IRを有する点で、図43A等に示した画素80と主に異なる。

発光デバイス11IRは、赤外光を射出する機能を有する。発光デバイス11IRは、基板23上に電極13e、EL層17IR、層21、及び電極15をこの順で積層された積層構造を有する。EL層17IRは、層33e、層35e、発光層41IR、及び層37eをこの順で積層された積層構造を有する。

層33eは、正孔注入性の高い物質を含む層(正孔注入層)を有する。層35eは、正孔輸送性の高い物質を含む層(正孔輸送層)を有する。発光層41IRは、赤外の波長領域の発光を示す発光物質を有する。層37eは、電子輸送性の高い物質を含む層(電子輸送層)を有する。

発光デバイス11IRにおいて、電極13eは陽極として機能し、電極15は陰極として機能する。つまり、電極13eに供給される電位は、電極15に供給される電位よりも高い構成とする。

電極13eは、基板23上に設けられる。電極13eは、電極13a、電極13b、電極13c、及び電極13dと同じ工程で形成することができる。電極13eは、画素電極として機能する。電極13eについては、前述の電極13A及び電極13Bの記載を参照できるため、詳細な説明は省略する。

層33eについては、前述の層33A及び層33Bの記載を参照できるため、詳細な説明は省略する。層35eについては、前述の層35A及び層35Bの記載を参照できるため、詳細な説明は省略する。層37eについては、前述の層37A及び層37Bの記載を参照できるため、詳細な説明は省略する。

図44Bは、発光デバイス11Rから射出される赤色(R)の光、発光デバイス11Gから射出される緑色(G)の光、発光デバイス11Bから射出される青色(B)の光、発光デバイス11IRから射出される赤外(IR)光、及び受光デバイス12PSに入射する光をそれぞれ、矢印で模式的に示している。

前述の画素80と異なる構成例を、図45Aに示す。図45Aに示す画素80Bは、発光デバイス11R、発光デバイス11G、発光デバイス11B、受光デバイス12PS、及び受光デバイス12IRSを有する。図45Aは、発光デバイス11R、発光デバイス11G、発光デバイス11B、受光デバイス12PS、及び受光デバイス12IRSの構成を示す断面概略図である。画素80Bは、受光デバイスの構成が異なる点で、図43A等に示した画素80と主に異なる。

画素80が有する受光デバイス12PSは、可視光を受光する機能を有し、受光デバイス12IRSは、赤外光を受光する機能を有する。

受光デバイス12IRSは、基板23上に電極13f、受光層19IRS、層21、及び電極15をこの順で積層された積層構造を有する。受光層19IRSは、層37f、活性層43IRS、層35f、及び層33fをこの順で積層された積層構造を有する。

層37fは、電子輸送性の高い物質を含む層(電子輸送層)を有する。活性層43IRSは、半導体を含む。活性層43IRSは、特に有機半導体を含むことが好ましい。層35fは、正孔輸送性の高い物質を含む層(正孔輸送層)を有する。層33fは、正孔注入性の高い物質を含む層(正孔注入層)を有する。なお、受光デバイス12IRSにおいて、層33fは、正孔輸送層として機能する。

受光デバイス12IRSにおいて、電極13fは陰極として機能し、電極15は陽極として機能する。つまり、電極13fに供給される電位は、電極15に供給される電位よりも高い構成とする。

電極13fは、基板23上に設けられる。電極13fは、電極13a、電極13b、電極13c、電極13d、及び電極13eと同じ工程で形成することができる。電極13eは、画素電極として機能する。電極13fについては、前述の電極13A及び電極13Bの記載を参照できるため、詳細な説明は省略する。

層33fについては、前述の層33A及び層33Bの記載を参照できるため、詳細な説明は省略する。層35fについては、前述の層35A及び層35Bの記載を参照できるため、詳細な説明は省略する。層37fについては、前述の層37A及び層37Bの記載を参照できるため、詳細な説明は省略する。

図45Bは、発光デバイス11Rから射出される赤色(R)の光、発光デバイス11Gから射出される緑色(G)の光、発光デバイス11Bから射出される青色(B)の光、受光デバイス12PSに入射する光、及び受光デバイス12IRSに入射する光をそれぞれ、矢印で模式的に示している。

前述の画素80Bと異なる構成例を、図46Aに示す。図46Aに示す画素80Cは、発光デバイス11R、発光デバイス11G、発光デバイス11B、発光デバイス11IR、受光デバイス12PS、及び受光デバイス12IRSを有する。図46Aは、発光デバイス11R、発光デバイス11G、発光デバイス11B、発光デバイス11IR、受光デバイス12PS、及び受光デバイス12IRSの構成を示す断面概略図である。画素80Cは、発光デバイス11IRを有する点で、図45A等に示した画素80Bと主に異なる。

図46Bは、発光デバイス11Rから射出される赤色(R)の光、発光デバイス11Gから射出される緑色(G)の光、発光デバイス11Bから射出される青色(B)の光、発光デバイス11IRから射出される赤外(IR)光、受光デバイス12PSに入射する光、及び受光デバイス12IRSに入射する光をそれぞれ、矢印で模式的に示している。

本実施の形態は、他の実施の形態と適宜組み合わせることができる。また、本明細書において、1つの実施の形態の中に、複数の構成例が示される場合は、構成例を適宜組み合わせることが可能である。

(実施の形態3)

本実施の形態では、上記実施の形態で説明した発光デバイス及び受光デバイスを有する表示装置の利用形態等について説明する。

本発明の一態様の表示装置の模式図を、図47Aに示す。図47Aに示す表示装置200は、基板201、基板202、発光デバイス211R、発光デバイス211G、発光デバイス211B、受光デバイス212PS、及び機能層203等を有する。

発光デバイス211R、発光デバイス211G、発光デバイス211B、及び受光デバイス212PSは、基板201と基板202の間に設けられている。発光デバイス211R、発光デバイス211G、発光デバイス211Bはそれぞれ赤色(R)、緑色(G)、または青色(B)の光を発する。発光デバイス211R、発光デバイス211G、及び発光デバイス211Bは、前述の発光デバイスを用いることができる。受光デバイス212PSは、前述の受光デバイスを用いることができる。なお、以下では、発光デバイス211R、発光デバイス211G及び発光デバイス211Bを特に区別しない場合に、発光デバイス211と表記する場合がある。

図47Aは、基板202の表面に指220が触れる様子を示している。発光デバイス(例えば、発光デバイス211G)が発する光の一部は、基板202と指220との接触部で反射される。そして、反射光の一部が、受光デバイス212PSに入射されることにより、指220が基板202に接触したことを検出することができる。すなわち、表示装置200はタッチパネルとして機能することができる。

機能層203は、発光デバイス211R、発光デバイス211G、発光デバイス211Bを駆動する回路、及び、受光デバイス212PSを駆動する回路を有する。機能層203には、スイッチ、トランジスタ、容量、配線などが設けられる。なお、発光デバイス211R、発光デバイス211G、発光デバイス211B、及び受光デバイス212PSをパッシブマトリクス方式で駆動させる場合には、スイッチ、及びトランジスタを設けない構成としてもよい。

表示装置200は、例えば、指220の指紋を検出することができる。図47Bは、基板202と指220の接触部の拡大図を模式的に示している。また、図47Bには、交互に配列した発光デバイス211と受光デバイス212を示している。

指220は凹部及び凸部により指紋が形成されている。そのため、図47Bに示すように指紋の凸部が基板202に触れている。

ある表面、または界面から反射される光には、正反射と拡散反射とがある。正反射光は入射角と反射角が一致する、指向性の高い光であり、拡散反射光は、強度の角度依存性が低い、指向性の低い光である。指220の表面から反射される光は、正反射と拡散反射のうち拡散反射の成分が支配的となる。一方、基板202と大気との界面から反射される光は、正反射の成分が支配的となる。

指220と基板202との接触面または非接触面で反射され、これらの直下に位置する受光デバイス212に入射される光の強度は、正反射光と拡散反射光とを足し合わせたものとなる。上述のように指220の凹部では基板202と指220が接触しないため、正反射光(実線矢印で示す)が支配的となり、凸部ではこれらが接触するため、指220からの拡散反射光(破線矢印で示す)が支配的となる。したがって、凹部の直下に位置する受光デバイス212で受光する光の強度は、凸部の直下に位置する受光デバイス212よりも高くなる。これにより、指220の指紋を撮像することができる。

受光デバイス212の配列間隔は、指紋の2つの凸部間の距離、好ましくは隣接する凹部と凸部間の距離よりも小さい間隔とすることで、鮮明な指紋の画像を取得することができる。人の指紋の凹部と凸部の間隔は概ね200μmであることから、例えば受光デバイス212の配列間隔は、400μm以下、好ましくは200μm以下、より好ましくは150μm以下、さらに好ましくは100μm以下、さらに好ましくは50μm以下であって、1μm以上、好ましくは10μm以上、より好ましくは20μm以上とする。

表示装置200で撮像した指紋の画像の例を、図47Cに示す。図47Cは、撮像範囲227内に、指220の輪郭を破線で、接触部224の輪郭を一点鎖線で示している。接触部224内において、受光デバイス212に入射する光量の違いによって、コントラストの高い指紋222を撮像することができる。

表示装置200は、タッチパネル、またはペンタブレットとしても機能させることができる。図47Dは、スタイラス229の先端を基板202に接触させた状態で、破線矢印の方向に滑らせている様子を示している。

図47Dに示すように、スタイラス229の先端と、基板202の接触面で拡散される拡散反射光が、当該接触面と重なる部分に位置する受光デバイス212に入射することで、スタイラス229の先端の位置を高精度に検出することができる。

図47Eには、表示装置200で検出したスタイラス229の軌跡226の例を示している。表示装置200は、高い位置精度でスタイラス229等の被検出体の位置検出が可能であるため、描画アプリケーション等において、高精細な描画を行うことも可能である。また、静電容量式のタッチセンサ、電磁誘導型のタッチペン等を用いた場合とは異なり、絶縁性の高い被検出体であっても位置検出が可能であるため、スタイラス229の先端部の材料は問われず、様々な筆記用具(例えば筆、ガラスペン、羽ペン)を用いることもできる。

受光デバイス212PSは、タッチセンサ(ダイレクトタッチセンサともいう)、またはニアタッチセンサ(ホバーセンサ、ホバータッチセンサ、非接触センサ、タッチレスセンサともいう)に用いることができる。図48は、発光デバイス(例えば、発光デバイス211G)から射出された光31が、対象物(例えば、指220)で反射し、その反射した光32が受光デバイス212PSに入射する様子を示している。対象物は、表示装置200に接触していないが、受光デバイス212PSを用いて、対象物を検出することができる。なお、受光デバイス212PSは、用途に応じて、検出する光の波長を適宜決定してもよい。

タッチセンサまたはニアタッチセンサは、対象物(指、手、またはペンなど)の近接もしくは接触を検出することができる。タッチセンサは、表示装置と、対象物とが、直接接することで、対象物を検出できる。また、ニアタッチセンサは、対象物が表示装置に接触しなくても、当該対象物を検出することができる。例えば、表示装置と、対象物との間の距離が0.1mm以上300mm以下、好ましくは3mm以上50mm以下の範囲で表示装置が当該対象物を検出できる構成であると好ましい。当該構成とすることで、表示装置に対象物が直接触れずに操作することが可能となる、別言すると非接触(タッチレス)で表示装置を操作することが可能となる。上記構成とすることで、表示装置に汚れ、または傷がつくリスクを低減することができる、または対象物が表示装置に付着した汚れ(例えば、ゴミ、またはウィルス)に直接触れずに、表示装置を操作することが可能となる。

本発明の一態様の表示装置は、リフレッシュレートを可変にすることができる。例えば、表示装置に表示されるコンテンツに応じてリフレッシュレートを調整(例えば、1Hz以上240Hz以下の範囲で調整)し、消費電力を低減させることができる。また、当該リフレッシュレートに応じて、タッチセンサ、またはニアタッチセンサの駆動周波数を変化させてもよい。例えば、表示装置のリフレッシュレートが120Hzの場合、タッチセンサ、またはニアタッチセンサの駆動周波数を120Hzよりも高い周波数(代表的には240Hz)とする構成とすることができる。当該構成とすることで、低消費電力が実現でき、且つタッチセンサ、またはニアタッチセンサの応答速度を高めることが可能となる。

受光デバイス212PSは、表示装置が有する全ての画素に設けられていることが好ましい。全ての画素に受光デバイス212PSを設けることにより、高い精度でタッチを検出することができる。なお、一部の画素に受光デバイス212PSを設ける構成としてもよい。例えば、発光デバイス及び受光デバイスを設けた画素と、受光デバイスを設けた(発光デバイスのみを設けない)画素と、有する表示装置としてもよい。

前述の表示装置200と異なる構成例を、図49Aに示す。図49Aに示す表示装置200Aは、基板201、基板202、発光デバイス211R、発光デバイス211G、発光デバイス211B、発光デバイス211IR、受光デバイス212PS、及び機能層203等を有する。表示装置200Aは、発光デバイス211IRを有する点で、前述の表示装置200と主に異なる。

発光デバイス211R、発光デバイス211G、発光デバイス211B、及び受光デバイス212PSは、基板201と基板202の間に設けられている。発光デバイス211IRは、赤外光を発する。発光デバイス211IRは、前述の発光デバイスを用いることができる。

図49Aは、基板202の表面に指220が触れる様子を示している。発光デバイス(例えば、発光デバイス211IR)が発する光の一部は、基板202と指220との接触部で反射される。そして、反射光の一部が、受光デバイス212PSに入射されることにより、指220が基板202に接触したことを検出することができる。例えば、発光デバイス211IRから赤外線を射出し、受光デバイス212PSで赤外光を検出することにより、暗い場所でも、タッチ検出が可能となる。

表示装置200Aは、発光デバイス211R、発光デバイス211G及び発光デバイス211Bを用いて表示部に画像を表示するとともに、発光デバイス211IR及び受光デバイス212PSを用いて表示部でタッチ検出を行うことができる。また、表示装置200Aは、表示部に画像を表示するとともに、表示部で撮像を行うことができる。

図49Bは、発光デバイス211Gから射出された光31が、対象物(例えば、指220)で反射し、その反射した光32が受光デバイス212PSに入射する様子を示している。図49Cは、発光デバイス211IRから射出された光31が、対象物(例えば、指220)で反射し、その反射した光32が受光デバイス212PSに入射する様子を示している。対象物は、表示装置200Aに接触していないが、受光デバイス212PSを用いて、対象物を検出することができる。

前述の表示装置200Aと異なる構成例を、図50Aに示す。図50Aに示す表示装置200Bは、基板201、基板202、発光デバイス211R、発光デバイス211G、発光デバイス211B、発光デバイス211IR、受光デバイス212PS、受光デバイス212IRS、及び機能層203等を有する。表示装置200Bは、受光デバイスの構成が異なる点で、前述の表示装置200Aと主に異なる。

発光デバイス211R、発光デバイス211G、発光デバイス211B、受光デバイス212PS、及び受光デバイス212IRSは、基板201と基板202の間に設けられている。受光デバイス212PSは、可視光を受光する。受光デバイス212IRSは、赤外光を受光する。受光デバイス212PS、及び受光デバイス212IRSは、前述の受光デバイスを用いることができる。

図50Aは、基板202の表面に指220が触れる様子を示している。発光デバイス(例えば、発光デバイス211IR)が発する光の一部は、基板202と指220との接触部で反射される。そして、反射光の一部が、受光デバイス212IRSに入射されることにより、指220が基板202に接触したことを検出することができる。

図50Bは、発光デバイス211IRから射出された光31が、対象物(例えば、指220)で反射し、その反射した光32が受光デバイス212IRSに入射する様子を示している。図50Cは、発光デバイス211Gから射出された光31が、対象物(例えば、指220)で反射し、その反射した光32が受光デバイス212PSに入射する様子を示している。対象物は、表示装置200Bに接触していないが、受光デバイス212PS、または受光デバイス212IRSを用いて、対象物を検出することができる。

受光デバイス212PSの受光領域の面積(以下、受光面積とも記す)は、受光デバイス212IRSの受光面積よりが小さいことが好ましい。受光デバイス212PSの受光面積を小さく、つまり撮像範囲を狭くすることで、受光デバイス212PSは受光デバイス212IRSに比べて高精細な撮像を行うことができる。このとき、受光デバイス212PSは、指紋、掌紋、虹彩、脈形状(静脈形状、動脈形状を含む)、または顔などを用いた個人認証のための撮像などに用いることができる。なお、受光デバイス212PSは、用途に応じて、検出する光の波長を適宜決定してもよい。

受光デバイス212PSと、受光デバイス212IRSとの検出精度の差から、機能に応じて、対象物の検出方法を選択してもよい。例えば、表示画面のスクロール機能は、受光デバイス212IRSを用いたニアタッチセンサ機能によって実現し、画面に表示されたキーボードでの入力機能は、受光デバイス212PSを用いた高精細なタッチセンサ機能によって実現してもよい。

1つの画素に、2種類の受光デバイスを搭載することで、表示機能に加えて、2つの機能を追加することができ、多機能の表示装置とすることができる。

なお、高精細な撮像を行うため、受光デバイス212PSは、表示装置が有する全ての画素に設けられていることが好ましい。一方で、タッチセンサまたはニアタッチセンサなどに用いる受光デバイス212IRSは、受光デバイス212PSを用いた検出に比べて高い精度が求められないため、表示装置が有する一部の画素に設けてもよい。表示装置が有する受光デバイス212IRSの数を、受光デバイス212PSの数よりも少なくすることで、検出速度を高めることができる。

以上のように、本実施の形態の表示装置は、1つの画素に発光デバイス及び受光デバイスを搭載することで、多機能の表示装置とすることができる。例えば、高精細な撮像機能、及びタッチセンサまたはニアタッチセンサなどのセンシング機能を有する表示装置を実現することができる。

本発明の一態様の表示装置は、特定の色の光を射出し、対象物で反射した反射光を受光してもよい。図51Aは、表示装置から射出される赤色の光と、対象物(ここでは指220)で反射することにより表示装置に入射した赤色の光をそれぞれ矢印で模式的に示している。図51Bは、表示装置から射出される赤外光と、対象物(ここでは指220)で反射することにより表示装置に入射した赤外光をそれぞれ矢印で模式的に示している。

対象物が表示装置に接触または近接した状態で、赤色の光を射出し、対象物からの反射光が表示装置に入射することにより、対象物の赤色の光に対する透過率を測定できる。同様に、対象物が表示装置に接触または近接した状態で、赤外光を射出し、対象物からの反射光が表示装置に入射することにより、対象物の赤外光に対する透過率を測定できる。

図51Aの一点鎖線で示す領域Pの拡大図を、図51Cに示す。発光デバイス211Rから射出された光31は、指220の表面及び内部の生体組織により散乱し、一部の散乱光が生体内部から受光デバイス212PSの方向に進む。この散乱光が血管91を透過し、その透過した光32が受光デバイス212PSに入射する。

同様に、発光デバイス211IRから射出された赤外光は、指220の表面及び内部の生体組織により散乱し、一部の散乱した赤外光が生体内部から受光デバイス212IRSの方向に進む。この散乱した赤外光が血管91を透過し、その透過した赤外光が受光デバイス212IRSに入射する。

ここで、光32は、生体組織93、及び血管91(動脈、及び静脈)を経た光である。動脈血は心拍によって脈動するため、動脈による光の吸収は、心拍に応じて変動する。一方、生体組織93、及び静脈は心拍の影響を受けないため、生体組織93よる光の吸収、及び静脈による光の吸収は一定となる。したがって、表示装置に入射した光32から経時的に一定な成分を除外することにより、動脈の光の透過率を算出することができる。また、赤色の光の透過率は、酸素と結合しているヘモグロビン(酸素化ヘモグロビンともいう)より酸素と結合していないヘモグロビン(還元ヘモグロビンともいう)で低くなる。赤外光の透過率は、酸素化ヘモグロビンと還元ヘモグロビンで同程度となる。赤色の光に対する動脈の透過率と、赤外光に対する動脈の透過率を測定することにより、酸素化ヘモグロビンと還元ヘモグロビンの総和に対する酸素化ヘモグロビンの比率、つまり酸素飽和度(以下、経皮的酸素飽和度(SpO2:Peripheral Oxygen Saturation)ともいう)を算出することができる。このように、本発明の一態様である表示装置は、反射型のパルスオキシメータとしての機能を有することができる。

例えば、表示装置の表示部に指が接触した際に、指が接触している領域の位置情報を取得する。その後、指が接触している領域及びその近傍の画素から赤色の光を射出して赤色の光に対する動脈の透過率を測定する。続いて、赤外光を射出して赤外光に対する動脈の透過率を測定することにより、酸素飽和度を算出することができる。なお、赤色の光に対する透過率と、赤外光に対する透過率を測定する順は特に限定されない。赤外光に対する透過率を測定した後に、赤色の光に対する透過率を測定してもよい。また、ここでは指を用いて酸素飽和度を算出する例を示したが、本発明の一態様はこれに限られない。指以外の部位で酸素飽和度を算出することもできる。例えば、表示装置の表示部に掌を接触させた状態で赤色の光に対する動脈の透過率と、赤外光に対する動脈の透過率を測定することにより、酸素飽和度を算出することができる。

本発明の一態様の表示装置を適用した電子機器の一例を、図52Aに示す。図52Aに示す携帯情報端末400は、例えば、スマートフォンとして用いることができる。携帯情報端末400は、筐体402と、表示部404を有する。表示部404は、前述の表示装置を適用することができる。表示部404は、例えば、前述の表示装置200Bを好適に用いることができる。

図52Aは、携帯情報端末400の表示部404に指406が接触している様子を示している。図52Aは、タッチを検出した領域及びその近傍である領域408を一点鎖線で示している。

携帯情報端末400は、領域408の画素から赤色の光を射出し、表示部404に入射した赤色の光を検出する。同様に、領域408の画素から赤外光を射出し、表示部404に入射した赤外光を検出することにより、指406の酸素飽和度を測定することができる。図52Bは、領域408の画素を点灯する様子を示している。図52Bは、指406を透過させ、輪郭のみを破線で示し、領域408にハッチングを施している。図52Bに示すように、点灯している領域408は、指406によって隠れ、ユーザーから視認されにくい。そのため、ユーザーにストレスを感じさせることなく、酸素飽和度を測定することができる。また、携帯情報端末400は、表示部404内のどの位置でも酸素飽和度の測定することができる。

得られた酸素飽和度を、表示部404に示してもよい。図52Cは、領域407に酸素飽和度を示す画像409を表示する様子を示している。図52Cでは、画像409の例として、“SpO297%”の文字を示している。なお、画像409は画像であってもよく、画像及び文字を含んでもよい。また、領域407は表示部404の任意に位置に設ければよい。

本実施の形態は、他の実施の形態と適宜組み合わせることができる。また、本明細書において、1つの実施の形態の中に、複数の構成例が示される場合は、構成例を適宜組み合わせることが可能である。

(実施の形態4)

本実施の形態では、本発明の一態様の表示装置とその作製方法について、図53乃至図71を用いて説明する。

発光色がそれぞれ異なる発光デバイス、及び受光デバイスを有する表示装置を作製する場合、複数の発光層及び活性層をそれぞれ島状に形成する必要がある。

例えば、メタルマスク(シャドーマスクともいう)を用いた真空蒸着法により、島状の発光層及び活性層を成膜することができる。しかし、この方法では、メタルマスクの精度、メタルマスクと基板との位置ずれ、メタルマスクのたわみ、及び蒸気の散乱などによる成膜される膜の輪郭の広がりなど、様々な影響により、島状の発光層及び活性層の形状及び位置に設計からのずれが生じるため、表示装置の高精細化、及び高開口率化が困難である。

本発明の一態様の表示装置の作製方法では、島状の画素電極(下部電極ともいえる)を形成し、EL層となる第1の層を一面に形成した後、第1の層上に第1の犠牲層を形成する。そして、第1の犠牲層上に第1のレジストマスクを形成し、第1のレジストマスクを用いて、第1の層と第1の犠牲層を加工することで、島状のEL層を形成する。同様に、受光層となる第2の層を、第2の犠牲層及び第2のレジストマスクを用いて、島状の受光層を形成する。

このように、本発明の一態様の表示装置の作製方法では、島状のEL層は、メタルマスクのパターンによって形成されるのではなく、EL層となる層を一面に成膜した後に加工することで形成される。同様に、島状の受光層は、メタルマスクのパターンによって形成されるのではなく、受光層となる層を一面に成膜した後に加工することで形成される。したがって、これまで実現が困難であった高精細な表示装置または高開口率の表示装置を実現することができる。さらに、EL層を各色で作り分けることができるため、極めて鮮やかでコントラストが高く、表示品位の高い表示装置を実現できる。さらに、画素内に受光デバイスを設けることができ、高精細な撮像機能、及びタッチセンサまたはニアタッチセンサなどのセンシング機能を有する表示装置を実現できる。また、EL層上、及び受光層上に犠牲層を設けることで、表示装置の作製工程中にEL層及び受光層が受けるダメージを低減し、発光デバイス及び受光デバイスの信頼性を高めることができる。

隣り合う発光デバイス及び受光デバイスの間隔は、例えば、メタルマスクを用いた形成方法では10μm未満にすることは困難であるが、上記方法によれば、3μm以下、2μm以下、または、1μm以下にまで狭めることができる。また、例えば、LSI向けの露光装置を用いることで、500nm以下、200nm以下、100nm以下、さらには50nm以下にまで間隔を狭めることもできる。これにより、画素に占める発光領域の面積(以下、発光面積とも記す)、及び受光面積を大きくすることができ、開口率を100%に近づけることが可能となる。例えば、開口率は、50%以上、60%以上、70%以上、80%以上、さらには90%以上であって、100%未満を実現することもできる。

EL層及び受光層自体のパターンについても、メタルマスクを用いた場合に比べて極めて小さくすることができる。例えば、EL層及び受光層の作り分けにメタルマスクを用いた場合では、パターンの中央と端で厚さのばらつきが生じるため、パターン全体の面積に対して、発光領域または受光領域として使用できる有効な面積は小さくなる。一方、上記作製方法では、均一な厚さに成膜した膜を加工することでパターンを形成するため、パターン内で厚さを均一にでき、微細なパターンであっても、そのほぼ全域を発光領域または受光領域として用いることができる。そのため、高い精細度と高い開口率を兼ね備えた表示装置を作製することができる。

<表示装置の構成例1>

本発明の一態様の表示装置を、図53A及び図53Bに示す。

図53Aは、表示装置100の上面図である。表示装置100は、複数の画素110がマトリクス状に配置された表示部と、表示部の外側の接続部140と、を有する。

図53Aに示す画素110には、ストライプ配列が適用されている。図53Aに示す画素110は、副画素110a、副画素110b、副画素110c、及び副画素110dの、4つの副画素から構成される。副画素110a、副画素110b、及び副画素110cは、それぞれ異なる波長領域の光を発する発光デバイスを有する。当該発光デバイスとして、前述の発光デバイスを用いることができる。副画素110a、副画素110b、及び副画素110cとしては、赤色(R)、緑色(G)、青色(B)の3色の副画素、黄色(Y)、シアン(C)、及びマゼンタ(M)の3色の副画素などが挙げられる。副画素110dは、受光デバイスを有する。当該受光デバイスとして、前述の受光デバイスを用いることができる。

図53Aでは、各副画素がX方向に並べて配置されており、同じ種類の副画素が、Y方向に並べて配置されている例を示す。なお、異なる種類の副画素がY方向に並べて配置され、同じ種類の副画素が、X方向に並べて配置されていてもよい。

図53Aでは、上面視において、接続部140が表示部の下側に位置する例を示すが、特に限定されない。接続部140は、上面視において、表示部の上側、右側、左側、下側の少なくとも一箇所に設けられていればよく、表示部の四辺を囲むように設けられていてもよい。また、接続部140は、単数であっても複数であってもよい。

図53Aにおける一点鎖線X1−X2間の断面図を、図53Bに示す。

図53Bに示すように、表示装置100は、トランジスタを含む層101上に、発光デバイス130a、発光デバイス130b、発光デバイス130c、及び受光デバイス130dが設けられる。さらに、これらの発光デバイス及び受光デバイスを覆うように保護層131、及び保護層132が設けられている。保護層132上には、樹脂層122によって基板120が貼り合わされている。また、隣り合う発光デバイス及び受光デバイスの間の領域には、絶縁層125と、絶縁層125上の絶縁層127と、が設けられている。

本発明の一態様の表示装置は、発光デバイスが形成されている基板とは反対方向に光を射出する上面射出型(トップエミッション型)、発光デバイスが形成されている基板側に光を射出する下面射出型(ボトムエミッション型)、両面に光を射出する両面射出型(デュアルエミッション型)のいずれであってもよい。

トランジスタを含む層101には、例えば、基板に複数のトランジスタが設けられ、これらのトランジスタを覆うように絶縁層が設けられた積層構造を適用することができる。トランジスタを含む層101は、隣り合う発光デバイスの間に凹部を有していてもよい。例えば、トランジスタを含む層101の最表面に位置する絶縁層に凹部が設けられていてもよい。

発光デバイス130a、発光デバイス130b、及び発光デバイス130cはそれぞれ、異なる波長領域の光を発する。発光デバイス130a、発光デバイス130b、及び発光デバイス130cは、例えば、赤色(R)、緑色(G)、青色(B)の3色の光を発する組み合わせであることが好ましい。

発光デバイス130aは、トランジスタを含む層101上の画素電極111aと、画素電極111a上の島状のEL層113aと、島状のEL層113a上の層114と、層114上の共通電極115と、を有する。

発光デバイス130bは、トランジスタを含む層101上の画素電極111bと、画素電極111b上の島状のEL層113bと、島状のEL層113b上の層114と、層114上の共通電極115と、を有する。

発光デバイス130cは、トランジスタを含む層101上の画素電極111cと、画素電極111c上の島状のEL層113cと、島状のEL層113c上の層114と、層114上の共通電極115と、を有する。

受光デバイス130dは、トランジスタを含む層101上の画素電極111dと、画素電極111d上の島状の受光層113dと、島状の受光層113d上の層114と、層114上の共通電極115と、を有する。

各色の発光デバイス及び受光デバイスは、共通電極として同一の膜を共有している。共通電極は、接続部140に設けられた導電層と電気的に接続される。これにより、各色の発光デバイス及び受光デバイスが有する共通電極には、同電位が供給される。

発光デバイス及び受光デバイスの一対の電極(画素電極と共通電極)として、金属、合金、電気伝導性化合物、及びこれらの混合物などを適宜用いることができる。具体的には、インジウムスズ酸化物(In−Sn酸化物、ITOともいう)、In−Si−Sn酸化物(ITSOともいう)、インジウム亜鉛酸化物(In−Zn酸化物)、In−W−Zn酸化物、アルミニウム、ニッケル、及びランタンの合金(Al−Ni−La)等のアルミニウムを含む合金(アルミニウム合金)、及び、銀とパラジウムと銅の合金(Ag−Pd−Cu、APCとも記す)が挙げられる。その他、アルミニウム(Al)、チタン(Ti)、クロム(Cr)、マンガン(Mn)、鉄(Fe)、コバルト(Co)、ニッケル(Ni)、銅(Cu)、ガリウム(Ga)、亜鉛(Zn)、インジウム(In)、スズ(Sn)、モリブデン(Mo)、タンタル(Ta)、タングステン(W)、パラジウム(Pd)、金(Au)、白金(Pt)、銀(Ag)、イットリウム(Y)、ネオジム(Nd)などの金属、及びこれらを適宜組み合わせて含む合金を用いることもできる。その他、上記例示のない元素周期表の第1族または第2族に属する元素(例えば、リチウム(Li)、セシウム(Cs)、カルシウム(Ca)、ストロンチウム(Sr))、ユウロピウム(Eu)、イッテルビウム(Yb)などの希土類金属及びこれらを適宜組み合わせて含む合金、グラフェン等を用いることができる。

発光デバイスには、微小光共振器(マイクロキャビティ)構造が適用されていることが好ましい。したがって、発光デバイスが有する一対の電極の一方は、可視光に対する透過性及び反射性を有する電極(半透過・半反射電極)を有することが好ましく、他方は、可視光に対する反射性を有する電極(反射電極)を有することが好ましい。発光デバイスがマイクロキャビティ構造を有することで、発光層から得られる発光を両電極間で共振させ、発光デバイスから射出される光を強めることができる。

なお、半透過・半反射電極は、可視光に対する反射性を有する電極と、可視光に対する透過性を有する電極(透明電極ともいう)との積層構造とすることができる。

透明電極の光の透過率は、40%以上とする。例えば、発光素子には、可視光の透過率が40%以上である電極を用いることが好ましい。半透過・半反射電極の可視光の反射率は、10%以上95%以下、好ましくは30%以上80%以下とする。反射電極の可視光の反射率は、40%以上100%以下、好ましくは70%以上100%以下とする。また、これらの電極の抵抗率は、1×10−2Ωcm以下が好ましい。なお、発光素子が赤外光を発する場合、これらの電極の赤外光の透過率または反射率は、可視光の透過率または反射率と同様に、上記の数値範囲を満たすことが好ましい。

EL層113a、EL層113b、EL層113c、及び受光層113dはそれぞれ、島状に設けられる。EL層113a、EL層113b、及びEL層113cはそれぞれ、発光層を有する。EL層113a、EL層113b、及びEL層113cはそれぞれ、異なる波長領域の光を発する発光層を有することが好ましい。受光層113dは、活性層を有する。

発光層は、発光物質を含む層である。発光層は、1種または複数種の発光物質を有することができる。発光物質としては、青色、紫色、青紫色、緑色、黄緑色、黄色、橙色、赤色などの発光色を呈する物質を適宜用いる。また、発光物質として、赤外光を発する物質を用いることもできる。

発光物質としては、蛍光材料、燐光材料、TADF材料、量子ドット材料などが挙げられる。

蛍光材料としては、例えば、ピレン誘導体、アントラセン誘導体、トリフェニレン誘導体、フルオレン誘導体、カルバゾール誘導体、ジベンゾチオフェン誘導体、ジベンゾフラン誘導体、ジベンゾキノキサリン誘導体、キノキサリン誘導体、ピリジン誘導体、ピリミジン誘導体、フェナントレン誘導体、ナフタレン誘導体などが挙げられる。

燐光材料としては、例えば、4H−トリアゾール骨格、1H−トリアゾール骨格、イミダゾール骨格、ピリミジン骨格、ピラジン骨格、またはピリジン骨格を有する有機金属錯体(特にイリジウム錯体)、電子吸引基を有するフェニルピリジン誘導体を配位子とする有機金属錯体(特にイリジウム錯体)、白金錯体、希土類金属錯体等が挙げられる。

発光層は、発光物質(ゲスト材料)に加えて、1種または複数種の有機化合物(ホスト材料、アシスト材料等)を有していてもよい。1種または複数種の有機化合物としては、正孔輸送性材料及び電子輸送性材料の一方または双方を用いることができる。また、1種または複数種の有機化合物として、バイポーラ性材料、またはTADF材料を用いてもよい。

発光層は、例えば、燐光材料と、励起錯体を形成しやすい組み合わせである正孔輸送性材料及び電子輸送性材料と、を有することが好ましい。このような構成とすることにより、励起錯体から発光物質(燐光材料)へのエネルギー移動であるExTET(Exciplex−Triplet Energy Transfer)を用いた発光を効率よく得ることができる。発光物質の最も低エネルギー側の吸収帯の波長と重なるような発光を呈する励起錯体を形成するような組み合わせを選択することで、エネルギー移動がスムーズとなり、効率よく発光を得ることができる。この構成により、発光デバイスの高効率、低電圧駆動、長寿命を同時に実現できる。

励起錯体を形成する材料の組み合わせとしては、正孔輸送性材料のHOMO準位(最高被占有軌道準位)が電子輸送性材料のHOMO準位以上の値であると好ましい。正孔輸送性材料のLUMO準位(最低空軌道準位)が電子輸送性材料のLUMO準位以上の値であると好ましい。材料のLUMO準位及びHOMO準位は、サイクリックボルタンメトリ(CV)測定によって測定される材料の電気化学特性(還元電位及び酸化電位)から導出することができる。

励起錯体の形成は、例えば正孔輸送性材料の発光スペクトル、電子輸送性材料の発光スペクトル、及びこれら材料を混合した混合膜の発光スペクトルを比較し、混合膜の発光スペクトルが、各材料の発光スペクトルよりも長波長シフトする(または長波長側に新たなピークを持つ)現象を観測することにより確認することができる。または、正孔輸送性材料の過渡フォトルミネッセンス(PL)、電子輸送性材料の過渡PL、及びこれら材料を混合した混合膜の過渡PLを比較し、混合膜の過渡PL寿命が、各材料の過渡PL寿命よりも長寿命成分を有する、または遅延成分の割合が大きくなるなどの過渡応答の違いを観測することにより、確認することができる。また、上述の過渡PLは過渡エレクトロルミネッセンス(EL)と読み替えても構わない。すなわち、正孔輸送性材料の過渡EL、電子輸送性を有する材料の過渡EL、及びこれらの混合膜の過渡ELを比較し、過渡応答の違いを観測することによっても、励起錯体の形成を確認することができる。

EL層113a、EL層113b、及び、EL層113cは、発光層以外の層として、正孔注入性の高い物質、正孔輸送性の高い物質(正孔輸送性材料とも記す)、正孔ブロック材料、電子輸送性の高い物質(電子輸送性材料とも記す)、電子注入性の高い物質、電子ブロック材料、またはバイポーラ性の物質(電子輸送性及び正孔輸送性が高い物質、バイポーラ性材料とも記す)等を含む層をさらに有していてもよい。

発光デバイスには低分子系化合物及び高分子系化合物のいずれを用いることもでき、無機化合物を含んでいてもよい。発光デバイスを構成する層は、それぞれ、蒸着法(真空蒸着法を含む)、転写法、印刷法、インクジェット法、塗布法等の方法で形成することができる。

例えば、EL層113a、EL層113b、及び、EL層113cは、それぞれ、正孔注入層、正孔輸送層、正孔ブロック層、電子ブロック層、電子輸送層、及び電子注入層のうち一つ以上を有していてもよい。

EL層のうち、各色に共通して形成される層としては、正孔注入層、正孔輸送層、正孔ブロック層、電子ブロック層、電子輸送層、及び電子注入層のうち一つ以上を適用することができる。例えば、層114として、キャリア注入層(正孔注入層または電子注入層)を形成してもよい。なお、EL層の全ての層を色ごとに作り分けてもよい。つまり、EL層は、各色に共通して形成される層を有していなくてもよい。

EL層113a、EL層113b、及び、EL層113cは、それぞれ、発光層と、発光層上のキャリア輸送層を有することが好ましい。これにより、表示装置100の作製工程中に、発光層が最表面に露出することを抑制し、発光層が受けるダメージを低減することができる。これにより、発光デバイスの信頼性を高めることができる。

正孔注入層は、陽極から正孔輸送層に正孔を注入する層であり、正孔注入性の高い物質を含む層である。正孔注入性の高い物質としては、芳香族アミン化合物、及び、正孔輸送性材料とアクセプター性材料(電子受容性材料)とを含む複合材料などが挙げられる。

正孔輸送層は、正孔注入層によって、陽極から注入された正孔を発光層に輸送する層である。正孔輸送層は、正孔輸送性材料を含む層である。正孔輸送性材料としては、10−6cm2/Vs以上の正孔移動度を有する物質が好ましい。なお、電子よりも正孔の輸送性の高い物質であれば、これら以外のものも用いることができる。正孔輸送性材料としては、π電子過剰型複素芳香族化合物(例えばカルバゾール誘導体、チオフェン誘導体、フラン誘導体など)、芳香族アミン(芳香族アミン骨格を有する化合物)等の正孔輸送性の高い物質が好ましい。

電子輸送層は、電子注入層によって、陰極から注入された電子を発光層に輸送する層である。電子輸送層は、電子輸送性材料を含む層である。電子輸送性材料としては、1×10−6cm2/Vs以上の電子移動度を有する物質が好ましい。なお、正孔よりも電子の輸送性の高い物質であれば、これら以外のものも用いることができる。電子輸送性材料としては、キノリン骨格を有する金属錯体、ベンゾキノリン骨格を有する金属錯体、オキサゾール骨格を有する金属錯体、チアゾール骨格を有する金属錯体等の他、オキサジアゾール誘導体、トリアゾール誘導体、イミダゾール誘導体、オキサゾール誘導体、チアゾール誘導体、フェナントロリン誘導体、キノリン配位子を有するキノリン誘導体、ベンゾキノリン誘導体、キノキサリン誘導体、ジベンゾキノキサリン誘導体、ピリジン誘導体、ビピリジン誘導体、ピリミジン誘導体、その他含窒素複素芳香族化合物を含むπ電子不足型複素芳香族化合物等の電子輸送性の高い物質を用いることができる。

電子注入層は、陰極から電子輸送層に電子を注入する層であり、電子注入性の高い物質を含む層である。電子注入性の高い物質としては、アルカリ金属、アルカリ土類金属、またはそれらの化合物を用いることができる。電子注入性の高い物質としては、電子輸送性材料とドナー性材料(電子供与性材料)とを含む複合材料を用いることもできる。

電子注入層としては、例えば、リチウム、セシウム、イッテルビウム、フッ化リチウム(LiF)、フッ化セシウム(CsF)、フッ化カルシウム(CaFx、Xは任意数)、8−(キノリノラト)リチウム(略称:Liq)、2−(2−ピリジル)フェノラトリチウム(略称:LiPP)、2−(2−ピリジル)−3−ピリジノラトリチウム(略称:LiPPy)、4−フェニル−2−(2−ピリジル)フェノラトリチウム(略称:LiPPP)、リチウム酸化物(LiOx)、炭酸セシウム等のようなアルカリ金属、アルカリ土類金属、またはこれらの化合物を用いることができる。また、電子注入層としては、2以上の積層構造としてもよい。当該積層構造としては、例えば、1層目にフッ化リチウムを用い、2層目にイッテルビウムを設ける構成とすることができる。

または、電子注入層としては、電子輸送性材料を用いてもよい。例えば、非共有電子対を備え、電子不足型複素芳香環を有する化合物を、電子輸送性材料に用いることができる。具体的には、ピリジン環、ジアジン環(ピリミジン環、ピラジン環、ピリダジン環)、トリアジン環の少なくとも一つを有する化合物を用いることができる。

なお、非共有電子対を備える有機化合物の最低空軌道(LUMO:Lowest Unoccupied Molecular Orbital)が、−3.6eV以上−2.3eV以下であると好ましい。また、一般にCV(サイクリックボルタンメトリ)、光電子分光法、光吸収分光法、逆光電子分光法等により、有機化合物の最高被占有軌道(HOMO:Highest Occupied Molecular Orbital)準位及びLUMO準位を見積もることができる。

例えば、4,7−ジフェニル−1,10−フェナントロリン(略称:BPhen)、2,9−ビス(ナフタレン−2−イル)−4,7−ジフェニル−1,10−フェナントロリン(略称:NBPhen)、ジキノキサリノ<2,3−a:2’,3’−c>フェナジン(略称:HATNA)、2,4,6−トリス<3’−(ピリジン−3−イル)ビフェニル−3−イル>−1,3,5−トリアジン(略称:TmPPPyTz)等を、非共有電子対を備える有機化合物に用いることができる。なお、NBPhenはBPhenと比較して、高いガラス転移温度(Tg)を備え、耐熱性に優れる。

タンデム構造の発光デバイスを作製する場合、2つの発光ユニットとの間に、中間層を設ける。中間層は、一対の電極間に電圧を印加したときに、2つの発光ユニットの一方に電子を注入し、他方に正孔を注入する機能を有する。

中間層としては、例えば、リチウムなどの電子注入層に適用可能な材料を好適に用いることができる。また、中間層としては、例えば、正孔注入層に適用可能な材料を好適に用いることができる。また、中間層には、正孔輸送性材料とアクセプター性材料(電子受容性材料)とを含む層を用いることができる。また、中間層には、電子輸送性材料とドナー性材料とを含む層を用いることができる。このような層を有する中間層を形成することにより、発光ユニットが積層された場合における駆動電圧の上昇を抑制することができる。

活性層は、半導体を含む。当該半導体としては、シリコンなどの無機半導体、及び、有機化合物を含む有機半導体が挙げられる。本実施の形態では、活性層が有する半導体として、有機半導体を用いる例を示す。有機半導体を用いることで、発光層と、活性層と、を同じ方法(例えば、真空蒸着法)で形成することができ、製造装置を共通化できるため好ましい。

活性層が有するn型半導体の材料としては、フラーレン(例えばC60、C70等)、フラーレン誘導体等の電子受容性の有機半導体材料が挙げられる。フラーレンは、サッカーボールのような形状を有し、当該形状はエネルギー的に安定である。フラーレンは、HOMO準位及びLUMO準位の双方が深い(低い)。フラーレンは、LUMO準位が深いため、電子受容性(アクセプター性)が極めて高い。通常、ベンゼンのように、平面にπ電子共役(共鳴)が広がると、電子供与性(ドナー性)が高くなるが、フラーレンは球体形状であるため、π電子共役が大きく広がっているにも関わらず、電子受容性が高くなる。電子受容性が高いと、電荷分離を高速に効率よく起こすため、受光素子として有益である。C60、C70ともに可視光領域に広い吸収帯を有しており、特にC70はC60に比べてπ電子共役系が大きく、長波長領域にも広い吸収帯を有するため好ましい。そのほか、フラーレン誘導体としては、[6,6]−Phenyl−C71−butyric acid methyl ester(略称:PC70BM)、[6,6]−Phenyl−C61−butyric acid methyl ester(略称:PC60BM)、1’,1’’,4’,4’’−Tetrahydro−di[1,4]methanonaphthaleno[1,2:2’,3’,56,60:2’’,3’’][5,6]fullerene−C60(略称:ICBA)などが挙げられる。

n型半導体の材料として、キノリン骨格を有する金属錯体、ベンゾキノリン骨格を有する金属錯体、オキサゾール骨格を有する金属錯体、チアゾール骨格を有する金属錯体、オキサジアゾール誘導体、トリアゾール誘導体、イミダゾール誘導体、オキサゾール誘導体、チアゾール誘導体、フェナントロリン誘導体、キノリン誘導体、ベンゾキノリン誘導体、キノキサリン誘導体、ジベンゾキノキサリン誘導体、ピリジン誘導体、ビピリジン誘導体、ピリミジン誘導体、ナフタレン誘導体、アントラセン誘導体、クマリン誘導体、ローダミン誘導体、トリアジン誘導体、キノン誘導体等が挙げられる。

活性層が有するp型半導体の材料としては、銅(II)フタロシアニン(Copper(II)phthalocyanine;CuPc)、テトラフェニルジベンゾペリフランテン(Tetraphenyldibenzoperiflanthene;DBP)、亜鉛フタロシアニン(Zinc Phthalocyanine;ZnPc)、スズフタロシアニン(SnPc)、キナクリドン等の電子供与性の有機半導体材料が挙げられる。

p型半導体の材料として、カルバゾール誘導体、チオフェン誘導体、フラン誘導体、芳香族アミン骨格を有する化合物等が挙げられる。さらに、p型半導体の材料としては、ナフタレン誘導体、アントラセン誘導体、ピレン誘導体、トリフェニレン誘導体、フルオレン誘導体、ピロール誘導体、ベンゾフラン誘導体、ベンゾチオフェン誘導体、インドール誘導体、ジベンゾフラン誘導体、ジベンゾチオフェン誘導体、インドロカルバゾール誘導体、ポルフィリン誘導体、フタロシアニン誘導体、ナフタロシアニン誘導体、キナクリドン誘導体、ポリフェニレンビニレン誘導体、ポリパラフェニレン誘導体、ポリフルオレン誘導体、ポリビニルカルバゾール誘導体、ポリチオフェン誘導体等が挙げられる。

電子供与性の有機半導体材料のHOMO準位は、電子受容性の有機半導体材料のHOMO準位よりも浅い(高い)ことが好ましい。電子供与性の有機半導体材料のLUMO準位は、電子受容性の有機半導体材料のLUMO準位よりも浅い(高い)ことが好ましい。

電子受容性の有機半導体材料として、球状のフラーレンを用い、電子供与性の有機半導体材料として、平面に近い形状の有機半導体材料を用いることが好ましい。似た形状の分子同士は集まりやすい傾向にあり、同種の分子が凝集すると、分子軌道のエネルギー準位が近いため、キャリア輸送性を高めることができる。

例えば、活性層は、n型半導体とp型半導体と共蒸着して形成することが好ましい。または、活性層は、n型半導体とp型半導体とを積層して形成してもよい。

発光素子及び受光素子には低分子化合物及び高分子化合物のいずれを用いることもでき、無機化合物を含んでいてもよい。発光素子及び受光素子を構成する層は、それぞれ、蒸着法(真空蒸着法を含む)、転写法、印刷法、インクジェット法、塗布法等の方法で形成することができる。

例えば、正孔輸送性材料として、ポリ(3,4−エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)(PEDOT/PSS)などの高分子化合物、及び、モリブデン酸化物、ヨウ化銅(CuI)などの無機化合物を用いることができる。また、電子輸送性材料として、酸化亜鉛(ZnO)などの無機化合物を用いることができる。

活性層に、ドナーとして機能するPoly[[4,8−bis[5−(2−ethylhexyl)−2−thienyl]benzo[1,2−b:4,5−b’]dithiophene−2,6−diyl]−2,5−thiophenediyl[5,7−bis(2−ethylhexyl)−4,8−dioxo−4H,8H−benzo[1,2−c:4,5−c’]dithiophene−1,3−diyl]]polymer(略称:PBDB−T)、または、PBDB−T誘導体などの高分子化合物を用いることができる。例えば、PBDB−TまたはPBDB−T誘導体にアクセプター材料を分散させる方法などが使用できる。

活性層に、3種類以上の材料を混合させてもよい。例えば、波長領域を拡大する目的で、n型半導体の材料と、p型半導体の材料と、に加えて、第3の材料を混合してもよい。このとき、第3の材料は、低分子化合物でも高分子化合物でもよい。

画素電極111a、画素電極111b、画素電極111c、画素電極111d、EL層113a、EL層113b、EL層113c、及び受光層113dのそれぞれの側面は、絶縁層125及び絶縁層127によって覆われている。これにより、層114(または共通電極115)が、画素電極111a、画素電極111b、画素電極111c、画素電極111d、EL層113a、EL層113b、EL層113c、及び受光層113dのいずれかの側面と接することを抑制し、発光デバイス及び受光デバイスのショートを抑制することができる。

絶縁層125は、少なくとも画素電極111a、画素電極111b、画素電極111c、及び画素電極111dの側面を覆うことが好ましい。さらに、絶縁層125は、EL層113a、EL層113b、EL層113c、及び受光層113dの側面を覆うことが好ましい。絶縁層125は、画素電極111a、画素電極111b、画素電極111c、画素電極111d、EL層113a、EL層113b、EL層113c、及び受光層113dのそれぞれの側面と接する構成とすることができる。

絶縁層127は、絶縁層125に形成された凹部を充填するように、絶縁層125上に設けられる。絶縁層127は、絶縁層125を介して、画素電極111a、画素電極111b、画素電極111c、画素電極111d、EL層113a、EL層113b、EL層113c、及び受光層113dのそれぞれの側面と重なる構成とすることができる。

なお、絶縁層125及び絶縁層127のいずれか一方を設けなくてもよい。例えば、絶縁層125を設けない場合、絶縁層127は、EL層113a、EL層113b、EL層113c、及び受光層113dのそれぞれの側面と接する構成とすることができる。絶縁層127は、発光デバイスが有するEL層、及び受光デバイスが有する受光層の間を充填するように、層101上に設けることができる。

層114及び共通電極115は、EL層113a、EL層113b、EL層113c、受光層113d、絶縁層125、及び絶縁層127上に設けられる。絶縁層125及び絶縁層127を設ける前の段階では、画素電極が設けられる領域と、画素電極が設けられない領域(発光デバイス及び受光デバイス間の領域)で段差が生じている。本発明の一態様の表示装置は、絶縁層125及び絶縁層127を有することで当該段差を平坦にすることができ、層114及び共通電極115の被覆性を向上させることができる。したがって、共通電極115の段切れによる接続不良を抑制することができる。または、段差によって共通電極115が局所的に薄くなり、電気抵抗が上昇することを抑制することができる。

層114及び共通電極115の形成面の平坦性を向上させるために、絶縁層125の上面及び絶縁層127の上面の高さは、それぞれ、EL層113a、EL層113b、EL層113c及び受光層113dの少なくとも一つの上面の高さと一致または概略一致することが好ましい。また、絶縁層127の上面は平坦な形状を有することが好ましく、凸部または凹部を有していてもよい。

絶縁層125は、EL層113a、EL層113b、EL層113c及び受光層113dの側面と接する領域を有し、EL層113a、EL層113b、EL層113c及び受光層113dの保護絶縁層として機能する。絶縁層125を設けることで、EL層113a、EL層113b、EL層113c及び受光層113dの側面から内部へ不純物(酸素、水分等)が侵入することを抑制でき、信頼性の高い表示装置とすることができる。

断面視においてEL層113a、EL層113b、EL層113c及び受光層113dの側面と接する領域における絶縁層125の幅(厚さ)が大きいと、EL層113a、EL層113b、EL層113c及び受光層113dの間隔が大きくなり、開口率が低くなってしまう場合がある。また、絶縁層125の幅(厚さ)が小さいと、EL層113a、EL層113b、EL層113c及び受光層113dの側面から内部へ不純物が侵入することを抑制する効果が小さくなってしまう場合がある。

EL層113a、EL層113b、EL層113c及び受光層113dの側面と接する領域における絶縁層125の幅(厚さ)は、3nm以上200nm以下が好ましく、さらには3nm以上150nm以下が好ましく、さらには5nm以上150nm以下が好ましく、さらには5nm以上100nm以下が好ましく、さらには10nm以上100nm以下が好ましく、さらには10nm以上50nm以下が好ましい。絶縁層125の幅(厚さ)を前述の範囲とすることで、高い開口率を有し、かつ信頼性の高い表示装置とすることができる。

絶縁層125は、無機材料を有することができる。絶縁層125は、例えば、酸化絶縁膜、窒化絶縁膜、酸化窒化絶縁膜、及び窒化酸化絶縁膜などの無機絶縁膜を用いることができる。絶縁層125は単層構造であってもよく積層構造であってもよい。

絶縁層125の形成は、スパッタリング法、化学気相堆積(CVD:Chemical Vapor Deposition)法、パルスレーザー堆積(PLD:Pulsed Laser Deposition)法、原子層堆積(ALD:Atomic Layer Deposition)法などを用いることができる。絶縁層125は、被覆性が良好なALD法を用いて形成することが好ましい。ALD法は、被形成面への成膜ダメージが小さいため、好適に用いることができる。

酸化絶縁膜として、酸化シリコン膜、酸化アルミニウム膜、酸化マグネシウム膜、インジウムガリウム亜鉛酸化物膜、酸化ガリウム膜、酸化ゲルマニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ランタン膜、酸化ネオジム膜、酸化ハフニウム膜、及び酸化タンタル膜などが挙げられる。窒化絶縁膜としては、窒化シリコン膜及び窒化アルミニウム膜などが挙げられる。酸化窒化絶縁膜としては、酸化窒化シリコン膜、酸化窒化アルミニウム膜などが挙げられる。窒化酸化絶縁膜としては、窒化酸化シリコン膜、窒化酸化アルミニウム膜などが挙げられる。特に、酸化アルミニウムは、エッチングにおいて、EL層との選択比が高く、後述する絶縁層127の形成において、EL層を保護する機能を有するため、好ましい。特にALD法により形成した酸化アルミニウム膜、酸化ハフニウム膜、酸化シリコン膜などの無機絶縁膜を絶縁層125に適用することで、ピンホールが少なく、EL層を保護する機能に優れた絶縁層125を形成することができる。

なお、本明細書などにおいて、酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い材料を指し、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い材料を指す。例えば、酸化窒化シリコンと記載した場合は、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化シリコンと記載した場合は、その組成として、酸素よりも窒素の含有量が多い材料を示す。

絶縁層125上に設けられる絶縁層127は、隣接する発光デバイス間に形成された絶縁層125の凹部を平坦化する機能を有する。換言すると、絶縁層127を有することで共通電極115の形成面の平坦性を向上させる効果を奏する。絶縁層127としては、有機材料を有する絶縁層を好適に用いることができる。例えば、絶縁層127として、アクリル樹脂、ポリイミド樹脂、エポキシ樹脂、イミド樹脂、ポリアミド樹脂、ポリイミドアミド樹脂、シリコーン樹脂、シロキサン樹脂、ベンゾシクロブテン系樹脂、フェノール樹脂、及びこれら樹脂の前駆体等を適用することができる。また、絶縁層127として、ポリビニルアルコール(PVA)、ポリビニルブチラル、ポリビニルピロリドン、ポリエチレングリコール、ポリグリセリン、プルラン、水溶性のセルロース、またはアルコール可溶性のポリアミド樹脂などの有機材料を用いてもよい。また、絶縁層127として、感光性の樹脂を用いることができる。感光性の樹脂としてはフォトレジストを用いてもよい。感光性の樹脂は、ポジ型の材料、またはネガ型の材料を用いることができる。

絶縁層127の上面の高さと、EL層113a、EL層113b、EL層113c及び受光層113dのいずれかの上面の高さとの差が、例えば、絶縁層127の厚さの0.5倍以下が好ましく、0.3倍以下がより好ましい。また、例えば、EL層113a、EL層113b、EL層113c及び受光層113dのいずれかの上面が絶縁層127の上面よりも高くなるように、絶縁層127を設けてもよい。また、例えば、絶縁層127の上面が、EL層113a、EL層113b、及びEL層113cが有する発光層の上面よりも高く、かつ受光層113dが有する活性層の上面よりも高くなるように、絶縁層127を設けてもよい。

発光デバイス130a、発光デバイス130b、発光デバイス130c、及び受光デバイス130d上に保護層131、及び保護層132を有することが好ましい。保護層131、及び保護層132を設けることで、発光デバイス及び受光デバイスの信頼性を高めることができる。

保護層131、及び保護層132の導電性は問わない。保護層131、及び保護層132として、絶縁膜、半導体膜、及び、導電膜の少なくとも一種を用いることができる。

保護層131、及び保護層132が無機膜を有することで、共通電極115の酸化を防止する、発光デバイス130a、発光デバイス130b、発光デバイス130c、及び受光デバイス130dに不純物(水分、酸素など)が入り込むことを抑制する、など、発光デバイス及び受光デバイスの劣化を抑制し、表示装置の信頼性を高めることができる。

保護層131、及び保護層132には、例えば、酸化絶縁膜、窒化絶縁膜、酸化窒化絶縁膜、及び窒化酸化絶縁膜などの無機絶縁膜を用いることができる。酸化絶縁膜としては、酸化シリコン膜、酸化アルミニウム膜、酸化ガリウム膜、酸化ゲルマニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ランタン膜、酸化ネオジム膜、酸化ハフニウム膜、及び酸化タンタル膜などが挙げられる。窒化絶縁膜としては、窒化シリコン膜及び窒化アルミニウム膜などが挙げられる。酸化窒化絶縁膜としては、酸化窒化シリコン膜、酸化窒化アルミニウム膜などが挙げられる。窒化酸化絶縁膜としては、窒化酸化シリコン膜、窒化酸化アルミニウム膜などが挙げられる。

保護層131、及び132はそれぞれ、窒化絶縁膜または窒化酸化絶縁膜を有することが好ましく、窒化絶縁膜を有することがより好ましい。

保護層131、及び保護層132には、In−Sn酸化物(ITOともいう)、In−Zn酸化物、Ga−Zn酸化物、Al−Zn酸化物、またはインジウムガリウム亜鉛酸化物(In−Ga−Zn酸化物、IGZOともいう)などを含む無機膜を用いることもできる。当該無機膜は、高抵抗であることが好ましく、具体的には、共通電極115よりも高抵抗であることが好ましい。当該無機膜は、さらに窒素を含んでいてもよい。

発光デバイスからの光の射出、及び受光デバイスへの光の入射を、保護層131、及び保護層132を介して取り出す場合、保護層131、保護層132は、可視光に対する透過性が高いことが好ましい。例えば、ITO、IGZO、及び、酸化アルミニウムは、それぞれ、可視光に対する透過性が高い無機材料であるため、好ましい。

保護層131、及び保護層132としては、例えば、酸化アルミニウム膜と、酸化アルミニウム膜上の窒化シリコン膜と、の積層構造、または、酸化アルミニウム膜と、酸化アルミニウム膜上のIGZO膜と、の積層構造などを用いることができる。当該積層構造を用いることで、EL層側に入り込む不純物(水、酸素など)を抑制することができる。

さらに、保護層131、及び保護層132は、有機膜を有していてもよい。例えば、保護層132は、有機膜と無機膜の双方を有していてもよい。

保護層131と保護層132とで異なる成膜方法を用いてもよい。具体的には、ALD法を用いて保護層131を形成し、スパッタリング法を用いて保護層132を形成してもよい。

画素電極111a、画素電極111b、画素電極111c、及び画素電極111dのそれぞれの上面端部は、絶縁層によって覆われていない。そのため、隣り合う発光デバイス及び受光デバイスの間隔を極めて狭くすることができる。したがって、高精細、または、高解像度の表示装置とすることができる。

本明細書等において、メタルマスク、またはFMM(ファインメタルマスク、高精細なメタルマスク)を用いて作製されるデバイスをMM(メタルマスク)構造のデバイスと呼称する場合がある。また、本明細書等において、メタルマスク、またはFMMを用いることなく作製されるデバイスをMML(メタルマスクレス)構造のデバイスと呼称する場合がある。

なお、本明細書等において、各色の発光デバイス(ここでは青(B)、緑(G)、及び赤(R))で、発光層を作り分ける、または発光層を塗り分ける構造をSBS(Side By Side)構造と呼ぶ場合がある。SBS構造は、発光デバイスごとに材料及び構成を最適化することができるため、材料及び構成の選択の自由度が高まり、輝度の向上、信頼性の向上を図ることが容易となる。

本明細書等において、白色光を発することのできる発光デバイスを白色発光デバイスと呼ぶ場合がある。なお、白色発光デバイスは、着色層(たとえば、カラーフィルタ)と組み合わせることで、フルカラー表示の表示装置を実現することができる。

ここで、発光デバイスは、シングル構造と、タンデム構造とに大別することができる。シングル構造のデバイスは、一対の電極間に1つの発光ユニットを有し、当該発光ユニットは、1以上の発光層を含む構成とすることが好ましい。白色発光を得るには、2以上の発光層の各々の発光が補色の関係となるような発光層を選択すればよい。例えば、第1の発光層の発光色と第2の発光層の発光色を補色の関係になるようにすることで、発光デバイス全体として白色発光する構成を得ることができる。また、発光層を3つ以上有する発光デバイスの場合は、各発光層の発光色の混合により白色発光する構成とすることができる。

タンデム構造のデバイスは、一対の電極間に2以上の複数の発光ユニットを有し、各発光ユニットは、1以上の発光層を含む構成とすることが好ましい。白色発光を得るには、複数の発光ユニットの発光層からの光を合わせて白色発光が得られる構成とすればよい。なお、白色発光が得られる構成については、シングル構造の構成と同様である。なお、タンデム構造のデバイスにおいて、複数の発光ユニットの間には、電荷発生層などの中間層を設けると好適である。

上述の白色発光デバイス(シングル構造またはタンデム構造)と、SBS構造の発光デバイスと、を比較した場合、SBS構造の発光デバイスは、白色発光デバイスよりも消費電力を低くすることができる。消費電力を低く抑えたい場合は、SBS構造の発光デバイスを用いると好適である。一方で、白色発光デバイスは、製造プロセスがSBS構造の発光デバイスよりも簡単であるため、製造コストを低くすることができる、又は製造歩留まりを高くすることができるため、好適である。

本実施の形態の表示装置は、発光デバイス間の距離を狭くすることができる。具体的には、発光デバイス間の距離、EL層間の距離、または画素電極間の距離を、10μm未満、5μm以下、3μm以下、2μm以下、1μm以下、500nm以下、200nm以下、100nm以下、90nm以下、70nm以下、50nm以下、30nm以下、20nm以下、15nm以下、または10nm以下とすることができる。別言すると、EL層113aの側面とEL層113bの側面との間隔、またはEL層113bの側面とEL層113cの側面との間隔が1μm以下の領域を有し、好ましくは0.5μm(500nm)以下の領域を有し、さらに好ましくは100nm以下の領域を有する。

同様に、本実施の形態の表示装置は、受光デバイス間の距離を狭くすることができる。具体的には、受光デバイス間の距離、受光層間の距離、または画素電極間の距離を、10μm未満、5μm以下、3μm以下、2μm以下、1μm以下、500nm以下、200nm以下、100nm以下、90nm以下、70nm以下、50nm以下、30nm以下、20nm以下、15nm以下、または10nm以下とすることができる。別言すると、受光層の側面と隣接する受光層の側面との間隔が1μm以下の領域を有し、好ましくは0.5μm(500nm)以下の領域を有し、さらに好ましくは100nm以下の領域を有する。

本実施の形態の表示装置は、発光デバイスと受光デバイスの間の距離を狭くすることができる。具体的には、発光デバイスと受光デバイスの間の距離、EL層と受光層の間の距離、または画素電極間の距離を、20μm未満、10μm以下、5μm以下、3μm以下、2μm以下、1μm以下、500nm以下、200nm以下、100nm以下、90nm以下、70nm以下、50nm以下、30nm以下、20nm以下、15nm以下、または10nm以下とすることができる。別言すると、EL層113aの側面と受光層113dの側面との間隔、EL層113bの側面と受光層113dの側面との間隔、またはEL層113cの側面と受光層113dの側面との間隔が1μm以下の領域を有し、好ましくは0.5μm(500nm)以下の領域を有し、さらに好ましくは100nm以下の領域を有する。

基板120の樹脂層122側の面には、遮光層を設けてもよい。また、基板120の外側には各種光学部材を配置することができる。光学部材としては、偏光板、位相差板、光拡散層(拡散フィルムなど)、反射防止層、及び集光フィルム等が挙げられる。また、基板120の外側には、ゴミの付着を抑制する帯電防止膜、汚れを付着しにくくする撥水性の膜、使用に伴う傷の発生を抑制するハードコート膜、衝撃吸収層等を配置してもよい。

基板120には、ガラス、石英、セラミック、サファイア、樹脂、金属、合金、半導体などを用いることができる。発光デバイスからの光を取り出す側の基板には、該光を透過する材料を用いる。基板120に可撓性を有する材料を用いると、表示装置の可撓性を高めることができる。また、基板120として偏光板を用いてもよい。

基板120としては、それぞれ、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)等のポリエステル樹脂、ポリアクリロニトリル樹脂、アクリル樹脂、ポリイミド樹脂、ポリメチルメタクリレート樹脂、ポリカーボネート(PC)樹脂、ポリエーテルスルホン(PES)樹脂、ポリアミド樹脂(ナイロン、アラミド等)、ポリシロキサン樹脂、シクロオレフィン樹脂、ポリスチレン樹脂、ポリアミドイミド樹脂、ポリウレタン樹脂、ポリ塩化ビニル樹脂、ポリ塩化ビニリデン樹脂、ポリプロピレン樹脂、ポリテトラフルオロエチレン(PTFE)樹脂、ABS樹脂、セルロースナノファイバー等を用いることができる。基板120に、可撓性を有する程度の厚さのガラスを用いてもよい。

なお、表示装置に円偏光板を重ねる場合、表示装置が有する基板には、光学等方性の高い基板を用いることが好ましい。光学等方性が高い基板は、複屈折が小さい(複屈折量が小さい、ともいえる)。

光学等方性が高い基板のリタデーション(位相差)値の絶対値は、30nm以下が好ましく、20nm以下がより好ましく、10nm以下がさらに好ましい。

光学等方性が高いフィルムとしては、トリアセチルセルロース(TAC、セルローストリアセテートともいう)フィルム、シクロオレフィンポリマー(COP)フィルム、シクロオレフィンコポリマー(COC)フィルム、及びアクリルフィルム等が挙げられる。

基板としてフィルムを用いる場合、フィルムが吸水することで、表示パネルにしわが発生するなどの形状変化が生じる恐れがある。そのため、基板には、吸水率の低いフィルムを用いることが好ましい。例えば、吸水率が1%以下のフィルムを用いることが好ましく、0.1%以下のフィルムを用いることがより好ましく、0.01%以下のフィルムを用いることがさらに好ましい。

樹脂層122は、紫外線硬化型等の光硬化型接着剤、反応硬化型接着剤、熱硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。これら接着剤として、エポキシ樹脂、アクリル樹脂、シリコーン樹脂、フェノール樹脂、ポリイミド樹脂、イミド樹脂、PVC(ポリビニルクロライド)樹脂、PVB(ポリビニルブチラル)樹脂、EVA(エチレンビニルアセテート)樹脂等が挙げられる。特に、エポキシ樹脂等の透湿性が低い材料が好ましい。また、二液混合型の樹脂を用いてもよい。また、接着シート等を用いてもよい。

トランジスタのゲート、ソース及びドレインのほか、表示装置を構成する各種配線及び電極などの導電層に用いることのできる材料としては、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、及びタングステンなどの金属、並びに、当該金属を主成分とする合金などが挙げられる。これらの材料を含む膜を単層で、または積層構造として用いることができる。

透光性を有する導電材料として、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを含む酸化亜鉛などの導電性酸化物またはグラフェンを用いることができる。または、金、銀、白金、マグネシウム、ニッケル、タングステン、クロム、モリブデン、鉄、コバルト、銅、パラジウム、及びチタンなどの金属材料、または、該金属材料を含む合金材料を用いることができる。または、該金属材料の窒化物(例えば、窒化チタン)などを用いてもよい。なお、金属材料、または、合金材料(またはそれらの窒化物)を用いる場合には、透光性を有する程度に薄くすることが好ましい。また、上記材料の積層膜を導電層として用いることができる。例えば、銀とマグネシウムの合金とインジウムスズ酸化物の積層膜などを用いると、導電性を高めることができるため好ましい。これらは、表示装置を構成する各種配線及び電極などの導電層、及び、発光デバイスが有する導電層(画素電極または共通電極として機能する導電層)にも用いることができる。

各絶縁層に用いることのできる絶縁材料として、例えば、アクリル樹脂、エポキシ樹脂などの樹脂、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウムなどの無機絶縁材料が挙げられる。

なお、本発明の一態様の表示装置は、OSトランジスタを有し、且つMML(メタルマスクレス)構造の発光素子を有する構成とすることができる。当該構成とすることで、トランジスタに流れうるリーク電流、及び隣接する発光素子間に流れうるリーク電流(横リーク電流、サイドリーク電流などともいう)を、極めて低くすることができる。また、上記構成とすることで、表示装置に画像を表示した場合に、観察者が画像のきれ、画像のするどさ、及び高いコントラスト比のいずれか一または複数を観測できる。なお、トランジスタに流れうるリーク電流、及び発光素子間の横リーク電流が極めて低い構成とすることで、黒表示時に生じうる光漏れなどが限りなく少ない表示(真黒表示ともいう)とすることができる。

<画素のレイアウト>

画素のレイアウトについて、説明する。副画素の配列に特に限定はなく、様々な方法を適用することができる。副画素の配列としては、例えば、ストライプ配列、Sストライプ配列、マトリクス配列、デルタ配列、ベイヤー配列、ペンタイル配列などが挙げられる。

副画素の上面形状は、例えば、三角形、四角形(長方形、正方形を含む)、五角形などの多角形、これら多角形の角が丸い形状、楕円形、または円形などが挙げられる。ここで、副画素の上面形状は、発光デバイスの発光領域、または受光デバイスの受光領域の上面形状に相当する。

図54A乃至図54Cに示す画素110は、ストライプ配列が適用されている。

本発明の一態様の表示装置の表示部は、複数の画素を有し、画素は行方向及び列方向にマトリクス状に配置される。図54A乃至図54Cに示す画素のレイアウトを適用した表示部は、行方向に副画素110a、副画素110b、副画素110c、及び副画素110dがこの順に繰り返し配置される第1の配列を有する。さらに、列方向に、第1の配列が繰り返し配置される。

当該表示部は、列方向に副画素110aが繰り返し配置される第2の配列と、列方向に副画素110bが繰り返し配置される第3の配列と、列方向に副画素110cが繰り返し配置される第4の配列と、列方向に副画素110dが繰り返し配置される第5の配列と、を有する。さらに、行方向に、第2の配列、第3の配列、第4の配列、及び第5の配列がこの順に繰り返し配置される。