WO2021220641A1 - 半導体装置および電力変換装置 - Google Patents

半導体装置および電力変換装置 Download PDFInfo

- Publication number

- WO2021220641A1 WO2021220641A1 PCT/JP2021/010172 JP2021010172W WO2021220641A1 WO 2021220641 A1 WO2021220641 A1 WO 2021220641A1 JP 2021010172 W JP2021010172 W JP 2021010172W WO 2021220641 A1 WO2021220641 A1 WO 2021220641A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- terminal

- semiconductor device

- groove

- solder

- end surface

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 302

- 238000006243 chemical reaction Methods 0.000 title claims description 42

- 229910000679 solder Inorganic materials 0.000 claims abstract description 114

- 229910052751 metal Inorganic materials 0.000 claims description 47

- 239000002184 metal Substances 0.000 claims description 47

- 239000000463 material Substances 0.000 claims description 19

- 229920005989 resin Polymers 0.000 description 76

- 239000011347 resin Substances 0.000 description 76

- 238000007789 sealing Methods 0.000 description 63

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 33

- 239000003990 capacitor Substances 0.000 description 27

- 230000001681 protective effect Effects 0.000 description 22

- 238000009499 grossing Methods 0.000 description 15

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 13

- 238000000034 method Methods 0.000 description 11

- 238000000465 moulding Methods 0.000 description 10

- 239000010949 copper Substances 0.000 description 8

- 230000004048 modification Effects 0.000 description 8

- 238000012986 modification Methods 0.000 description 8

- 230000002093 peripheral effect Effects 0.000 description 8

- 239000003507 refrigerant Substances 0.000 description 8

- 230000006870 function Effects 0.000 description 7

- 238000007747 plating Methods 0.000 description 7

- 239000010931 gold Substances 0.000 description 6

- 239000010410 layer Substances 0.000 description 6

- 238000005520 cutting process Methods 0.000 description 5

- 238000007665 sagging Methods 0.000 description 5

- 239000000758 substrate Substances 0.000 description 5

- 238000004804 winding Methods 0.000 description 5

- 238000004380 ashing Methods 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- 238000005352 clarification Methods 0.000 description 4

- 230000017525 heat dissipation Effects 0.000 description 4

- 230000001678 irradiating effect Effects 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 238000003892 spreading Methods 0.000 description 4

- 230000007480 spreading Effects 0.000 description 4

- 229910000881 Cu alloy Inorganic materials 0.000 description 3

- LYCAIKOWRPUZTN-UHFFFAOYSA-N Ethylene glycol Chemical compound OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 238000007788 roughening Methods 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 230000002457 bidirectional effect Effects 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- NJPPVKZQTLUDBO-UHFFFAOYSA-N novaluron Chemical compound C1=C(Cl)C(OC(F)(F)C(OC(F)(F)F)F)=CC=C1NC(=O)NC(=O)C1=C(F)C=CC=C1F NJPPVKZQTLUDBO-UHFFFAOYSA-N 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 239000005360 phosphosilicate glass Substances 0.000 description 2

- 238000003825 pressing Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 239000000725 suspension Substances 0.000 description 2

- 230000008961 swelling Effects 0.000 description 2

- 238000001721 transfer moulding Methods 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- HBBGRARXTFLTSG-UHFFFAOYSA-N Lithium ion Chemical compound [Li+] HBBGRARXTFLTSG-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- -1 argon and nitrogen Chemical compound 0.000 description 1

- 238000005219 brazing Methods 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 239000000835 fiber Substances 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 239000000446 fuel Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 239000004519 grease Substances 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 229910001416 lithium ion Inorganic materials 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000001172 regenerating effect Effects 0.000 description 1

- 230000008929 regeneration Effects 0.000 description 1

- 238000011069 regeneration method Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000008016 vaporization Effects 0.000 description 1

- 238000011179 visual inspection Methods 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

- H01L23/49562—Geometry of the lead-frame for devices being provided for in H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/367—Cooling facilitated by shape of device

- H01L23/3675—Cooling facilitated by shape of device characterised by the shape of the housing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/565—Moulds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3142—Sealing arrangements between parts, e.g. adhesion promotors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/367—Cooling facilitated by shape of device

- H01L23/3672—Foil-like cooling fins or heat sinks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/42—Fillings or auxiliary members in containers or encapsulations selected or arranged to facilitate heating or cooling

- H01L23/433—Auxiliary members in containers characterised by their shape, e.g. pistons

- H01L23/4334—Auxiliary members in encapsulations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49568—Lead-frames or other flat leads specifically adapted to facilitate heat dissipation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49575—Assemblies of semiconductor devices on lead frames

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49861—Lead-frames fixed on or encapsulated in insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49866—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers characterised by the materials

- H01L23/49894—Materials of the insulating layers or coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0655—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0067—Converter structures employing plural converter units, other than for parallel operation of the units on a single load

- H02M1/007—Plural converter units in cascade

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/003—Constructional details, e.g. physical layout, assembly, wiring or busbar connections

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/003—Constructional details, e.g. physical layout, assembly, wiring or busbar connections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/0601—Structure

- H01L2224/0603—Bonding areas having different sizes, e.g. different heights or widths

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/33—Structure, shape, material or disposition of the layer connectors after the connecting process of a plurality of layer connectors

- H01L2224/331—Disposition

- H01L2224/3318—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/33181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/02—Containers; Seals

- H01L23/04—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls

- H01L23/043—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls the container being a hollow construction and having a conductive base as a mounting as well as a lead for the semiconductor body

- H01L23/051—Containers; Seals characterised by the shape of the container or parts, e.g. caps, walls the container being a hollow construction and having a conductive base as a mounting as well as a lead for the semiconductor body another lead being formed by a cover plate parallel to the base plate, e.g. sandwich type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/373—Cooling facilitated by selection of materials for the device or materials for thermal expansion adaptation, e.g. carbon

- H01L23/3735—Laminates or multilayers, e.g. direct bond copper ceramic substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/40—Mountings or securing means for detachable cooling or heating arrangements ; fixed by friction, plugs or springs

- H01L23/4006—Mountings or securing means for detachable cooling or heating arrangements ; fixed by friction, plugs or springs with bolts or screws

- H01L23/4012—Mountings or securing means for detachable cooling or heating arrangements ; fixed by friction, plugs or springs with bolts or screws for stacked arrangements of a plurality of semiconductor devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/46—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements involving the transfer of heat by flowing fluids

- H01L23/473—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements involving the transfer of heat by flowing fluids by flowing liquids

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49503—Lead-frames or other flat leads characterised by the die pad

- H01L23/49513—Lead-frames or other flat leads characterised by the die pad having bonding material between chip and die pad

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1203—Rectifying Diode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

- H01L2924/3512—Cracking

- H01L2924/35121—Peeling or delaminating

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/42—Conversion of dc power input into ac power output without possibility of reversal

- H02M7/44—Conversion of dc power input into ac power output without possibility of reversal by static converters

- H02M7/48—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/493—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode the static converters being arranged for operation in parallel

Definitions

- the disclosure in this specification relates to semiconductor devices and power conversion devices.

- Patent Document 1 discloses a semiconductor device having a double-sided heat dissipation structure. The contents of the prior art document are incorporated by reference as an explanation of the technical elements in this specification.

- the power converter disclosed herein is The first semiconductor device that constitutes the first power conversion unit and The second semiconductor device that constitutes the second power conversion unit and With Each semiconductor device A semiconductor device having a first main electrode and a second main electrode formed on a surface opposite to the first main electrode in the plate thickness direction.

- the first wiring member connected to the first main electrode and It has a first end face connected to the second main electrode and a second end face opposite to the first end face in the plate thickness direction, and the second end surface is parallel to the first direction orthogonal to the plate thickness direction.

- a terminal having a rectangular shape having two sides and two sides parallel to the second direction orthogonal to the plate thickness direction and the first direction.

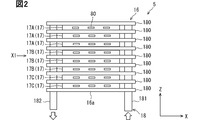

- FIG. 2 is a side view of FIG. 2 as viewed from the X1 direction. It is a top view which shows the semiconductor device which concerns on 1st Embodiment. It is a plan view seen from the side opposite to FIG. It is sectional drawing which follows the VI-VI line shown in FIG. It is sectional drawing which follows the line VII-VII shown in FIG. It is sectional drawing which follows the line VIII-VIII shown in FIG. It is a top view which shows the lead frame. It is a top view which shows the state which arranged the semiconductor element and the terminal.

- the power conversion device can be applied to a moving body whose drive source is a rotary electric machine.

- the moving body is, for example, an electric vehicle such as an electric vehicle (EV), a hybrid vehicle (HV), a fuel cell vehicle (FCV), a vehicle such as a drone, a ship, a construction machine, or an agricultural machine.

- a vehicle hybrid vehicle

- FCV fuel cell vehicle

- the vehicle drive system 1 includes a DC power supply 2, motor generators 3 and 4, and a power conversion device 5 that performs power conversion between the DC power supply 2 and the motor generators 3 and 4. There is.

- the motor generator 3 functions as a generator (alternator) that is driven by an engine (not shown) to generate electricity, and an electric motor (starter) that starts the engine.

- the motor generator 4 functions as a traveling drive source of the vehicle, that is, an electric motor.

- the motor generator 4 functions as a generator during regeneration.

- the vehicle includes an engine and a motor generator 4 as a traveling drive source.

- the power conversion device 5 performs power conversion between the DC power supply 2 and the motor generators 3 and 4.

- the power conversion device 5 includes a filter capacitor C1, a smoothing capacitor C2, a converter 6, inverters 7 and 8, a control circuit unit 9, a drive circuit unit 10, and the like.

- the P line 11 which is a power line on the high potential side has a VL line 11L and a VH line 11H.

- the VL line 11L is connected to the positive electrode terminal of the DC power supply 2.

- a converter 6 is provided between the VL line 11L and the VH line 11H.

- the potential of the VH line 11H is equal to or higher than the potential of the VL line 11L.

- the N line 12 is a power line on the low potential side connected to the negative electrode terminal of the DC power supply 2.

- the N line 12 is sometimes referred to as a ground line.

- the converter 6 is a DC-DC converter.

- the converter 6 converts the DC voltage into a DC voltage having a different value according to the switching control by the control circuit unit 9.

- the converter 6 has a function of boosting the DC voltage supplied from the DC power supply 2.

- the converter 6 also has a step-down function of charging the DC power supply 2 by using the electric charge of the smoothing capacitor C2.

- the converter 6 has an upper and lower arm circuit 6HL and a reactor R1.

- the collector of the switching element Q1 on the upper arm 6H side is connected to the VH line 11H, and the emitter of the switching element Q1 on the lower arm 6L side is connected to the N line 12.

- the emitter of the switching element Q1 on the upper arm 6H side and the collector of the switching element Q1 on the lower arm 6L side are connected to each other.

- One end of the reactor R1 is connected to the VL line 11L, and the other end is connected to the connection points of the upper arm 6H and the lower arm 6L via the booster wiring 13.

- the converter 6 of the present embodiment is configured as a multi-phase converter, specifically, a two-phase converter.

- the converter 6 has a two-phase upper / lower arm circuit 6HL and a reactor R1 provided for each upper / lower arm circuit 6HL.

- Inverters 7 and 8 are DC-AC converters.

- the inverter 7 is connected to the converter 6 via a smoothing capacitor C2.

- the inverter 7 converts the DC voltage into a three-phase AC voltage according to the switching control by the control circuit unit 9, and outputs the DC voltage to the motor generator 3.

- the motor generator 3 is driven so as to generate a predetermined torque.

- the inverter 7 can also convert the three-phase AC voltage generated by the motor generator 3 in response to the output of the engine into a DC voltage according to switching control by the control circuit unit 9 and output it to the VH line 11H. In this way, the inverter 7 performs bidirectional power conversion between the converter 6 and the motor generator 3.

- the inverter 7 has a three-phase (U-phase, V-phase, W-phase) upper and lower arm circuit 7HL.

- the inverter 8 is also connected to the converter 6 via the smoothing capacitor C2.

- the inverter 8 converts the DC voltage into a three-phase AC voltage and outputs it to the motor generator 4 according to the switching control by the control circuit unit 9.

- the motor generator 4 is driven so as to generate a predetermined torque.

- the inverter 8 converts the three-phase AC voltage generated by the motor generator 4 by receiving the rotational force from the drive wheels into a DC voltage according to the switching control by the control circuit unit 9 during the regenerative braking of the vehicle, and shifts to the VH line 11H. It can also be output. In this way, the inverter 8 performs bidirectional power conversion between the converter 6 and the motor generator 4.

- the inverter 8 has a three-phase (U-phase, V-phase, W-phase) upper and lower arm circuit 8HL.

- the control circuit unit 9 generates a drive command for operating the switching elements Q1, Q2, and Q3, and outputs the drive command to the drive circuit unit 10.

- the control circuit unit 9 generates a drive command based on a torque request input from a higher-level ECU (not shown), signals detected by various sensors, and the like.

- the control circuit unit 9 outputs, for example, a PWM signal as a drive command.

- the control circuit unit 9 is configured to include, for example, a microcomputer (microcomputer).

- ECU is an abbreviation for Electronic Control Unit.

- PWM is an abbreviation for Pulse Width Modulation.

- Various sensors include current sensors, rotation angle sensors, voltage sensors, temperature sensors, and the like.

- One of the current sensors detects the phase current flowing through the windings of each phase of the motor generators 3 and 4.

- the other one of the current sensors detects the current flowing through the reactor R1.

- the rotation angle sensor detects the rotation angle of the rotors of the motor generators 3 and 4.

- One of the voltage sensors detects the voltage across the smoothing capacitor C2, that is, the voltage of the VH line 11H.

- the other one of the voltage sensors detects the voltage across the filter capacitor C1, that is, the voltage of the VL line 11L.

- the temperature sensor detects the temperature of the reactor R1.

- the power conversion device 5 has these sensors (not shown).

- the drive circuit unit 10 supplies a drive voltage to the gates of the switching elements Q1, Q2, and Q3 of the corresponding arms 6H, 6L, 7H, 7L, 8H, and 8L based on the drive command of the control circuit unit 9.

- the drive circuit unit 10 drives the corresponding switching elements Q1, Q2, and Q3 by applying a drive voltage, that is, on-drive and off-drive.

- the drive circuit unit 10 may be referred to as a driver.

- one drive circuit unit 10 is provided for one arm.

- the arrangement of the drive circuit unit 10 is not limited to this.

- the drive circuit unit 10 may be provided for each of the upper and lower arm circuits 6HL, 7HL, and 8HL.

- the semiconductor device 17 includes a semiconductor device 17A that constitutes the inverter 7, a semiconductor device 17B that constitutes the inverter 8, and a semiconductor device 17C that constitutes the upper and lower arm circuits 6HL of the converter 6.

- one of the semiconductor devices 17 constitutes one of the upper and lower arm circuits.

- the semiconductor module 16 includes three semiconductor devices 17A constituting a three-phase upper / lower arm circuit 7HL, three semiconductor devices 17B forming a three-phase upper / lower arm circuit 8HL, and a two-phase upper / lower arm circuit 6HL. It includes two semiconductor devices 17C that constitute it.

- the outer contours of the semiconductor devices 17A, 17B, and 17C are substantially equal to each other.

- the cooler 18 is formed by using a metal material having excellent thermal conductivity, for example, an aluminum-based material.

- the cooler 18 includes a heat exchange unit 180, an introduction pipe 181 and a discharge pipe 182.

- the heat exchange unit 180 is housed in a housing.

- the heat exchange unit 180 is a tubular body having a flat shape as a whole.

- the heat exchange unit 180 processes, for example, at least one of a pair of plates (thin metal plates) into a shape bulging in the Z direction by press working. After that, the outer peripheral edges of the pair of plates are fixed to each other by caulking or the like, and are joined to each other by brazing or the like on the entire circumference. As a result, a flow path through which the refrigerant can flow is formed between the pair of plates, and it can be used as the heat exchange unit 180.

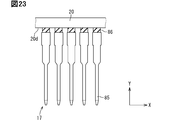

- the semiconductor device 17 has a main terminal 80 and a signal terminal 85 as terminals for external connection.

- the main terminal 80 and the signal terminal 85 extend in opposite directions in the Y direction.

- the signal terminal 85 is connected to a circuit board 19 arranged on one side in the Y direction with respect to the laminated body 16a.

- the circuit board 19 is provided so as to overlap all the semiconductor devices 17 constituting the laminated body 16a in a plan view in the Y direction.

- the signal terminal 85 of each semiconductor device 17 is inserted and mounted on the circuit board 19.

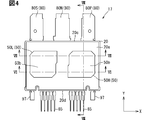

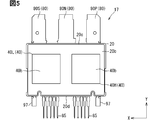

- FIGS. 4, 5, 9, and 11 show structures common to each other in the semiconductor devices 17A, 17B, and 17C.

- the semiconductor element 30 is formed by forming a vertical element on a semiconductor substrate made of silicon (Si), a wide bandgap semiconductor having a wider bandgap than silicon, or the like.

- Examples of wide bandgap semiconductors include silicon carbide (SiC), gallium nitride (GaN), gallium oxide (Ga 2 O 3 ), and diamond.

- the vertical element is configured such that the main current flows in the plate thickness direction of the semiconductor element 30 (semiconductor substrate), that is, in the Z direction.

- the semiconductor element 30 has a gate electrode (not shown).

- the gate electrode has, for example, a trench structure.

- the semiconductor element 30 has main electrodes of the element on both sides in its own plate thickness direction, that is, in the Z direction.

- the collector electrode 31C is provided on one surface side

- the emitter electrode 31E is provided on the back surface side, which is the opposite surface to the one surface.

- the collector electrode 31C also serves as a cathode electrode of the diode.

- the emitter electrode 31E also serves as an anode electrode of the diode.

- the collector electrode 31C corresponds to the first main electrode

- the emitter electrode 31E corresponds to the second main electrode.

- the semiconductor element 30 has a substantially rectangular shape in a plane.

- the semiconductor element 30 has a pad 31P formed at a position different from that of the emitter electrode 31E on the back surface.

- the emitter electrode 31E and the pad 31P are each exposed from a protective film (not shown).

- the collector electrode 31C is formed on almost the entire surface of one surface of the semiconductor element 30.

- the emitter electrode 31E is formed on a part of the back surface of the semiconductor element 30. In plan view, the collector electrode 31C has a larger area than the emitter electrode 31E.

- the emitter electrode 31E has a substantially rectangular shape in a plane.

- the pad 31P is a signal electrode.

- the pad 31P is electrically separated from the emitter electrode 31E.

- the pad 31P is formed at an end portion of the emitter electrode 31E opposite to the forming region in the Y direction.

- the pad 31P is provided alongside the emitter electrode 31E in the Y direction.

- the pad 31P includes at least a pad for a gate electrode.

- the semiconductor element 30 of this embodiment has five pads 31P. Specifically, for the gate electrode, for the Kelvin emitter that detects the potential of the emitter electrode 31E, for the current sense, for the anode potential of the temperature sensor (temperature sensitive diode) that detects the temperature of the semiconductor element 30, and also for the cathode potential. Have.

- the five pads 31P are collectively formed on one end side in the Y direction and are formed side by side in the X direction in the semiconductor element 30 having a substantially rectangular plane.

- the semiconductor device 17B includes a semiconductor element 30H that constitutes the upper arm 7H and a semiconductor element 30L that constitutes the lower arm 7L.

- the two semiconductor elements 30H and 30L have the same configuration as each other.

- the semiconductor elements 30H and 30L are arranged in the X direction.

- the semiconductor elements 30H and 30L are arranged at substantially the same positions as each other in the Z direction.

- the semiconductor device 17C includes a semiconductor element 30H that constitutes the upper arm 8H and a semiconductor element 30L that constitutes the lower arm 8L.

- the two semiconductor elements 30H and 30L have the same configuration as each other.

- the semiconductor elements 30H and 30L are arranged in the X direction.

- the semiconductor elements 30H and 30L are arranged at substantially the same positions as each other in the Z direction.

- the sizes of the semiconductor elements 30 are different from each other.

- the size is the size (area) of the planar shape.

- the semiconductor elements 30H and 30L of the semiconductor devices 17C constituting the converter 6 are larger than the semiconductor elements 30H and 30L of the semiconductor devices 17A and 17B constituting the inverters 7 and 8.

- the semiconductor elements 30H and 30L of the semiconductor device 17A constituting the inverter 7 are smaller than the semiconductor elements 30H and 30L of the semiconductor devices 17B and 17C constituting the inverter 7 and the converter 6.

- the size of the semiconductor element 30 satisfies the relationship of semiconductor device 17A ⁇ semiconductor device 17B ⁇ semiconductor device 17C.

- the size of the emitter electrode 31E satisfies the relationship of semiconductor device 17A ⁇ semiconductor device 17B ⁇ semiconductor device 17C.

- the heat sink 40 is arranged on the collector electrode 31C side of the semiconductor element 30 in the Z direction.

- the heat sink 40 is a wiring member electrically connected to the collector electrode 31C via the solder 90.

- the heat sink 40 corresponds to the first wiring member.

- the heat sink 40 has a facing surface 40a, which is a surface on the semiconductor element 30 side, and a back surface 40b, which is a surface opposite to the facing surface 40a.

- the solder 90 is interposed between the facing surface 40a of the heat sink 40 and the collector electrode 31C of the semiconductor element 30, and a solder joint is formed.

- the heat sink 40 dissipates the heat of the semiconductor element 30 to the outside.

- the heat sink 40 first wiring member

- a metal plate made of Cu, a Cu alloy, or the like, a DBC (Direct Bonded Copper) substrate, or the like can be adopted.

- the heat sink 40 may be provided with a plating film such as Ni or Au on its surface.

- the heat sink 40 of this embodiment is a metal plate made of Cu as a material.

- the heat sink 40 is configured as a part of the lead frame 95.

- the heat sink 40 is a thick portion in the lead frame 95 of the deformed strip.

- the semiconductor device 17 includes two heat sinks 40, respectively.

- the semiconductor device 17 includes a heat sink 40H forming an upper arm and a heat sink 40L forming a lower arm, respectively.

- the heat sinks 40H and 40L have a substantially rectangular shape in a plane.

- the heat sinks 40H and 40L are arranged in the X direction.

- the heat sinks 40H and 40L have substantially the same thickness and are arranged at substantially the same position in the Z direction.

- a joint made of solder 90 is formed between the facing surface 40a of the heat sink 40H and the collector electrode 31C of the semiconductor element 30H, and between the facing surface 40a of the heat sink 40L and the collector electrode 31C of the semiconductor element 30L.

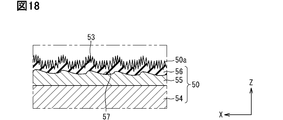

- the heat sink 50 dissipates the heat of the semiconductor element 30 to the outside.

- the heat sink 50 (second wiring member), for example, a metal plate made of Cu, a Cu alloy, or the like, a DBC (Direct Bonded Copper) substrate, or the like can be adopted.

- the heat sink 50 may be provided with a plating film such as Ni or Au on its surface.

- the heat sink 50 of this embodiment is a metal plate made of Cu as a material.

- the heat sink 50 has a facing surface 50a, which is a surface on the semiconductor element 30 side, and a back surface 50b, which is a surface opposite to the facing surface 50a.

- the semiconductor device 17 includes two heat sinks 50, respectively.

- the semiconductor device 17 includes a heat sink 50H forming an upper arm and a heat sink 50L forming a lower arm, respectively.

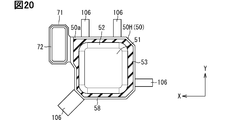

- connection area 51 is an area of the facing surface 50a surrounded by the groove 52.

- the connection area 51 is an area of a predetermined size (area) defined for electrical connection with the terminal 60.

- the groove 52 defines a connection area 51 inside the groove 52.

- the groove 52 accommodates the excess solder 91.

- the groove 52 is formed in an annular shape, for example.

- the back surface 50b of the heat sinks 50H and 50L is exposed from the sealing resin body 20.

- the back surface 50b may be referred to as a heat radiating surface or an exposed surface.

- the back surface 50b is substantially flush with one surface 20a of the sealing resin body 20.

- the back surfaces 50b of the heat sinks 50H and 50L are arranged in the X direction.

- the terminals 60H and 60L of the present embodiment are substantially rectangular columnar bodies having substantially the same size as the emitter electrode 31E in a plan view. As shown in FIGS. 6, 8 and 10, the size of the terminal 60 satisfies the relationship of semiconductor device 17A ⁇ semiconductor device 17B ⁇ semiconductor device 17C. The positional relationship between the terminal 60 and the groove 52 of the heat sink 50 will be described later.

- the thickness (length in the Z direction) of the terminal 60 is substantially equal to each other in the semiconductor devices 17A, 17B, and 17C.

- the joint portions 70 and 71 connect the elements constituting the upper and lower arm circuits.

- the joint portion connects the elements constituting the semiconductor device 17.

- the joint portion 70 is connected to the heat sink 40L.

- the thickness of the joint portion 70 is thinner than that of the heat sink 40L.

- the joint portion 70 is connected to the facing surface (side surface) of the heat sink 40H in a state of being substantially flush with the facing surface 40a of the heat sink 40L.

- the joint portion 70 has a substantially crank shape in the ZX plane by having two bent portions.

- the joint portion 70 is covered with the sealing resin body 20.

- the joint portion 70 may be provided integrally with the heat sink 40L to be connected, or may be provided as a separate member and may be connected by connection.

- the joint portion 70 of the present embodiment is provided integrally with the heat sink 40L as a part of the lead frame 95.

- the joint portion 71 is connected to the corresponding heat sink 50.

- a joint portion 71 is connected to each of the heat sinks 50H and 50L.

- the thickness of the joint portion 71 is thinner than that of the corresponding heat sink 50.

- the joint portion 71 is covered with the sealing resin body 20.

- the joint portion 71 may be provided integrally with the heat sink 50 to be connected, or may be provided as a separate member and may be connected by connection.

- the joint portion 71 of the present embodiment is provided integrally with the corresponding heat sinks 50H and 50L.

- the joint portion 71 extends in the X direction from the side surfaces facing each other in the two heat sinks 50H and 50L.

- the positive electrode terminal 80P is connected to one end of the heat sink 40H in the Y direction.

- the thickness of the positive electrode terminal 80P is thinner than that of the heat sink 40H.

- the positive electrode terminal 80P is substantially flush with the facing surface 40a and is connected to the heat sink 40H.

- the positive electrode terminals 80P may be provided integrally with the heat sink 40H to be connected, or may be provided as a separate member and connected by connection.

- the positive electrode terminal 80P of this embodiment is provided integrally with the heat sink 40H as a part of the lead frame 95.

- the positive electrode terminal 80P extends in the Y direction from the heat sink 40H and projects outward from the side surface 20c of the sealing resin body 20.

- the positive electrode terminal 80P has a bent portion in the middle of the portion covered by the sealing resin body 20, and projects from the vicinity of the center in the Z direction on the side surface 20c.

- the negative electrode terminal 80N is connected to the joint portion 71 connected to the heat sink 50L.

- a solder 94 is interposed between the facing surfaces of the negative electrode terminal 80N and the joint portion 71 to form a solder joint portion.

- the negative electrode terminal 80N extends in the Y direction and projects from the same side surface 20c as the positive electrode terminal 80P to the outside of the sealing resin body 20.

- the negative electrode terminal 80N has a connecting portion 81 with a joint portion 71 near one end in the Y direction. A part of the negative electrode terminal 80N including the connecting portion 81 is covered with the sealing resin body 20, and the remaining part protrudes from the sealing resin body 20.

- the connecting portion 81 is thicker than the portion protruding from the sealing resin body 20.

- the plate thickness of the connecting portion 81 is substantially the same as that of the heat sink 40, for example.

- the negative electrode terminal 80N also has a bent portion like the main terminal, and projects from the vicinity of the center in the Z direction on the side surface 20c.

- the negative electrode terminal 80N of this embodiment is configured as a part of the lead frame 95.

- the output terminal 80S is connected to one end of the heat sink 40L in the Y direction.

- the thickness of the output terminal 80S is thinner than that of the heat sink 40L.

- the output terminal 80S is substantially flush with the facing surface 40a and is connected to the heat sink 40L.

- the output terminals 80S may be provided integrally with the heat sink 40L to be connected, or may be provided as a separate member and connected by connection.

- the output terminal 80S of this embodiment is provided integrally with the heat sink 40L as a part of the lead frame 95.

- the output terminal 80S extends from the heat sink 40L in the Y direction, and projects from the same side surface 20c as the positive electrode terminal 80P to the outside of the sealing resin body 20.

- the output terminal 80S also has a bent portion like the positive electrode terminal 80P, and projects from the vicinity of the center in the Z direction on the side surface 20c.

- the three main terminals 80 are arranged in the order of the positive electrode terminal 80P, the negative electrode terminal 80N, and the output terminal 80S in the X direction.

- the signal terminal 85 is electrically connected to the pad 31P of the corresponding semiconductor element 30. In this embodiment, they are electrically connected via the bonding wire 96.

- the signal terminal 85 extends in the Y direction and projects outward from the side surface 20d of the sealing resin body 20.

- the side surface 20d is a surface opposite to the side surface 20c in the Y direction. In this embodiment, five signal terminals 85 are provided for one semiconductor element 30.

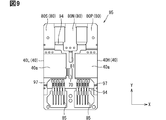

- the inner lead portion arranged inside the sealing resin body 20 has a crank shape as shown in FIGS. 9 and 10.

- the positions of the connecting portion of the bonding wire 96 and the sealing end portion on the side surface 20d are deviated in the X direction.

- the connecting portion of the bonding wire 96 is closer to the corresponding semiconductor element 30 (pad 31P) in the X direction than the sealing end portion on the side surface 20d.

- Reference numeral 97 shown in FIG. 5 and the like is a hanging lead.

- the heat sink 40 (40H, 40L), the joint portion 70, the main terminal 80, and the signal terminal 85 are configured in a lead frame 95 which is a common member.

- the lead frame 95 is a deformed strip having a partially different thickness.

- the signal terminal 85 is connected to the suspension lead 97 via the tie bar 98 in the state before cutting. Unnecessary parts of the lead frame 95, such as the tie bar 98, are cut (removed) after molding the sealing resin body 20.

- a plurality of semiconductor elements 30 constituting the upper and lower arm circuits for one phase are sealed by the sealing resin body 20.

- the sealing resin body 20 integrates a plurality of semiconductor elements 30, a part of each of the heat sinks 40, a part of each of the heat sinks 50, a terminal 60, joints 70 and 71, a part of each of the main terminals 80 and the signal terminal 85. Is sealed.

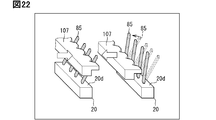

- the lead frame 95 shown in FIG. 9 is prepared.

- a laminate in which the semiconductor element 30 and the terminal 60 are arranged is formed on the heat sink 40.

- the molten solder 90 is applied on the facing surface 40a of the heat sink 40, and the semiconductor element 30 is arranged on the molten solder 90 so that the collector electrode 31C is on the facing surface 40a side.

- the molten solder 92 is applied onto the emitter electrode 31E of the semiconductor element 30, and the terminal 60 is arranged on the molten solder 92.

- the molten solder 91 is applied onto the end face 60b of the terminal 60.

- the molten solders 93 and 94 are also applied on the joint portion 70 and the connection portion 81.

- the molten solders 90 to 94 can be applied, for example, by using a transfer method.

- a laminated body is obtained by solidifying (solidifying) the applied molten solders 90 and 92.

- the molten solders 90 to 94 may be solidified (solidified) in the order of lamination, or all of them may be solidified (solidified) at once.

- the bonding wire 96 may be connected after the laminated body is formed, or may be performed after the molten solder 90 is solidified and before the molten solder 92 is applied on the emitter electrode 31E.

- the semiconductor device 17 having a double-sided heat dissipation structure is sandwiched from both sides in the Z direction by the heat exchange portion 180 of the cooler 18 as described above. Therefore, high parallelism of the surfaces and high dimensional accuracy between the surfaces are required in the Z direction. Therefore, for the solder 91, an amount capable of absorbing the height variation of the semiconductor device 17 is arranged. That is, more solder 91 is arranged than the solder 90 and 92. The same applies to the solders 93 and 94.

- the laminate and the heat sink 50 are connected.

- the heat sink 50 is arranged on a pedestal (not shown) so that the facing surface 50a faces up.

- the laminate is arranged on the heat sink 50 so that the end surface 60b of the terminal 60, that is, the solder 91 faces the facing surface 50a, and reflow is performed.

- a load is applied from the heat sink 40 side in the Z direction so that the height of the semiconductor device 17 becomes a predetermined height.

- a spacer (not shown) is brought into contact with both the facing surface 40a of the heat sink 40 and the mounting surface of the pedestal. In this way, the height of the semiconductor device 17 is set to a predetermined height.

- the sealing resin body 20 is molded by the transfer molding method.

- the sealing resin body 20 is molded so that the heat sinks 40 and 50 are completely covered.

- the resin 21 is injected from the gate 102 into the cavity 101 of the molding die 100.

- the gate 102 is connected to the side surface forming the cavity 101 on the semiconductor element 30H side.

- the gate 102 is connected to the cavity 101 in the vicinity of the connecting portion between the heat sink 40H and the suspension lead 97.

- Mold 100 has a flow cavity 103.

- the flow cavity 103 is connected to the cavity 101 that forms the sealing resin body 20.

- the flow cavity 103 is connected to the side surface of the wall surface forming the cavity 101 opposite to the gate 102.

- the flow cavity 103 is provided on the signal terminal 85 side in the Y direction.

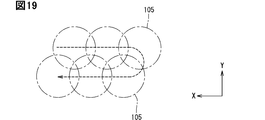

- FIG. 15 shows the positional relationship between the terminal 60 and the groove 52 in each of the semiconductor devices 17A, 17B, and 17C.

- an end surface 60b which is a surface facing the heat sink 50, is shown in order to show the positional relationship.

- the end face 60b has a substantially rectangular shape in a plane. As shown in FIG. 15, the end face 60b has two sides 61a and 61b substantially parallel to the X direction and two sides 61c and 61d substantially parallel to the Y direction as outer peripheral end portions. The end face 60b may have R portions at the four corners, or may have no R portions.

- the side 61a is provided on the signal terminal 85 side, that is, the pad 31P side

- the side 61b is provided on the main terminal 80 side.

- the side 61c is provided on the joint portion side

- the side 61d is provided outside the side 61c in the X direction.

- the groove 52 of the heat sink 50 has a common configuration in the semiconductor devices 17A, 17B, and 17C. That is, they are configured to match each other in a plan view. Due to the common use of the grooves 52, the heat sink 50 is a common component in the semiconductor devices 17A, 17B, and 17C.

- the size of the groove 52 is set according to the largest terminal 60 in the semiconductor devices 17A, 17B, and 17C constituting the power conversion unit. In this embodiment, the terminal 60 of the semiconductor device 17C constituting the converter 6 is the largest.

- the size of the groove 52 is set so that the terminal 60 of the semiconductor device 17C fits in the plan view.

- the groove 52 is provided so as to overlap only one or only two of the four sides 61a, 61b, 61c, and 61d of the end face 60b in a plan view.

- the groove 52 of the present embodiment has a substantially rectangular annular shape in a plane.

- the groove 52 has two extending portions 52a and 52b extending substantially parallel to the X direction and two extending portions 52a and 52b extending substantially parallel to the Y direction.

- the extension portion 52a is provided on the signal terminal 85 side, that is, the pad 31P side

- the extension portion 52b is provided on the main terminal 80 side.

- the extension portion 52c is provided on the joint portion side

- the extension portion 52d is provided outside the extension portion 52c.

- the groove 52 may have R portions at the four corners of the rectangle, or may have no R portion.

- the groove 52 is provided unevenly with respect to the terminal 60 in the Y direction. Specifically, in the Y direction, the distance between the side 61a on the pad 31P side and the extension portion 52a is shorter than the distance between the side 61b on the opposite side and the extension portion 52b. As described above, the groove 52 is provided so that the side 61a on the pad 31P side is closer to the groove 52 than the side 61b on the opposite side. In other words, the center of the groove 52 does not coincide with the center of the terminal 60 and is deviated in the direction away from the pad 31P. Therefore, the terminals 60 are arranged unevenly toward the side 61a in the Y direction.

- the semiconductor devices 17A, 17B, and 17C form a non-overlapping region 51a in which the terminal 60 does not overlap between the side 61b of the end surface 60b and the extension portion 52b of the groove 52 as a part of the connection region 51.

- the distance L1 between the side 61a on the pad 31P side and the extension portion 52a is shorter than the distance L2 between the side 61b on the opposite side and the extension portion 52b. The same applies to the other semiconductor devices 17A and 17B.

- the extending portion 52a of the groove 52 overlaps with the side 61a of the end face 60b.

- the groove 52 does not overlap the sides 61b, 61c, 61d.

- the sides 61b, 61c, and 61d overlap with the connection area 51.

- the groove 52 of the heat sink 50 overlaps the side 61a on the pad 31P side of the end surface 60b and does not overlap the side 61b on the opposite side.

- the groove 52 overlaps only the side 61a.

- the groove 52 is designed so that a plurality of types of terminals 60 having different sizes can be accommodated.

- the groove 52 is not provided so as to overlap all of the four sides 61a, 61b, 61c, 61d of the end face 60b of the terminal 60, but only one of the four sides 61a, 61b, 61c, 61d.

- it is provided in a size that overlaps only two.

- excess solder 91 can be accommodated in the grooves 52 having a common configuration for the plurality of terminals 60 having different sizes.

- the heat sink 50 can be used as a common component.

- the semiconductor device 17 of the present embodiment it is possible to reduce the types of parts (product numbers) while accommodating the surplus solder 91. Thereby, the cost can be reduced. Further, by standardizing the heat sink 50, the mold forming the groove 52 can also be standardized. As a result, the manufacturing cost can be reduced.

- the power conversion device 5 of the present embodiment includes a plurality of types of semiconductor devices 17A, 17B, and 17C that form different power conversion units.

- the semiconductor devices 17A, 17B, and 17C the sizes of the semiconductor element 30 and the terminal 60 are different from each other.

- the structure of the groove 52 is common.

- the heat sink 50 can be used as a common component.

- the groove 52 having the common configuration has a size that overlaps with only one or only two of the four sides 61a, 61b, 61c, 61d of the end face 60b of the terminal 60. There is.

- the surplus solder 91 can be accommodated in the groove 52. From the above, it is possible to reduce the types of parts in the power conversion device 5.

- the power conversion device 5 includes a semiconductor device 17A that constitutes the inverter 7, a semiconductor device 17B that constitutes the inverter 8, and a semiconductor device 17C that constitutes the converter 6. That is, three types of semiconductor devices 17 (17A, 17B, 17C) having different sizes of the semiconductor element 30 and the terminal 60 are provided. Of the three types of semiconductor devices 17, one of any two types corresponds to the first semiconductor device, and the other corresponds to the second semiconductor device.

- the power conversion unit composed of the first semiconductor device corresponds to the first power conversion unit, and the power conversion unit composed of the second semiconductor device corresponds to the second power conversion unit.

- the semiconductor device 17A corresponds to the first semiconductor device

- the semiconductor device 17C corresponds to the second semiconductor device.

- the inverter 7 corresponds to the first power conversion unit

- the converter 6 corresponds to the second conversion unit.

- FIG. 16 is a cross-sectional view showing the effect of the arrangement of the grooves 52 of the present embodiment, and also shows a reference example.

- the elements that are the same as or related to the elements of the present embodiment are shown by adding r to the end of the reference numerals of the present embodiment.

- the groove 52r does not overlap with the sides 61ar and 61r of the end face 60br of the terminal 60r.

- the sides 61ar and 61r overlap with the connection area 51r.

- the molten solder 91r is pushed from the laminate side and flows around the end surface 60br.

- the groove 52r is recessed with respect to the substantially flat connection region 51r, and when the solder 91 wets and spreads from the connection region 51r to the groove 52r, it stays at the interface not a little due to surface tension. Therefore, the solder 91 rises around the end face 60br.

- the solder 91r is closer to the semiconductor element 30r than the end face 60br in the Z direction. Therefore, the raised portion of the solder 91r may come into contact with the bonding wire 96r. Further, the solder 91r may come into contact with the side surface of the terminal 60r.