WO2021210600A1 - 電力用半導体装置、電力用半導体装置の製造方法および電力変換装置 - Google Patents

電力用半導体装置、電力用半導体装置の製造方法および電力変換装置 Download PDFInfo

- Publication number

- WO2021210600A1 WO2021210600A1 PCT/JP2021/015421 JP2021015421W WO2021210600A1 WO 2021210600 A1 WO2021210600 A1 WO 2021210600A1 JP 2021015421 W JP2021015421 W JP 2021015421W WO 2021210600 A1 WO2021210600 A1 WO 2021210600A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- impurity region

- semiconductor device

- gate electrode

- sic

- region

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 76

- 238000006243 chemical reaction Methods 0.000 title claims description 41

- 238000004519 manufacturing process Methods 0.000 title claims description 36

- 238000000034 method Methods 0.000 title claims description 34

- 239000000758 substrate Substances 0.000 claims abstract description 31

- 239000012535 impurity Substances 0.000 claims description 61

- 239000010410 layer Substances 0.000 claims description 48

- 239000002344 surface layer Substances 0.000 claims description 20

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 4

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 3

- 229920005591 polysilicon Polymers 0.000 claims description 3

- 230000000149 penetrating effect Effects 0.000 abstract 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 37

- 229910010271 silicon carbide Inorganic materials 0.000 description 36

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 32

- 238000007747 plating Methods 0.000 description 31

- 230000008569 process Effects 0.000 description 22

- 239000011229 interlayer Substances 0.000 description 18

- 229910000838 Al alloy Inorganic materials 0.000 description 12

- 229910052759 nickel Inorganic materials 0.000 description 11

- 239000010931 gold Substances 0.000 description 10

- 238000005530 etching Methods 0.000 description 9

- 230000000694 effects Effects 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 230000004048 modification Effects 0.000 description 6

- 238000012986 modification Methods 0.000 description 6

- 230000003647 oxidation Effects 0.000 description 6

- 238000007254 oxidation reaction Methods 0.000 description 6

- 229910000679 solder Inorganic materials 0.000 description 6

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 5

- 229910052725 zinc Inorganic materials 0.000 description 5

- 239000011701 zinc Substances 0.000 description 5

- 239000002253 acid Substances 0.000 description 4

- 230000009471 action Effects 0.000 description 4

- 239000003638 chemical reducing agent Substances 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000004140 cleaning Methods 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 230000001681 protective effect Effects 0.000 description 4

- NWONKYPBYAMBJT-UHFFFAOYSA-L zinc sulfate Chemical compound [Zn+2].[O-]S([O-])(=O)=O NWONKYPBYAMBJT-UHFFFAOYSA-L 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 230000008602 contraction Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 238000005238 degreasing Methods 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 229910018503 SF6 Inorganic materials 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 230000033116 oxidation-reduction process Effects 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 2

- 229960000909 sulfur hexafluoride Drugs 0.000 description 2

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 229910020776 SixNy Inorganic materials 0.000 description 1

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- PTFCDOFLOPIGGS-UHFFFAOYSA-N Zinc dication Chemical compound [Zn+2] PTFCDOFLOPIGGS-UHFFFAOYSA-N 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 230000003197 catalytic effect Effects 0.000 description 1

- 239000008139 complexing agent Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- -1 first Substances 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 230000006698 induction Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 238000001000 micrograph Methods 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- ACVYVLVWPXVTIT-UHFFFAOYSA-N phosphinic acid Chemical compound O[PH2]=O ACVYVLVWPXVTIT-UHFFFAOYSA-N 0.000 description 1

- 238000005554 pickling Methods 0.000 description 1

- 238000010248 power generation Methods 0.000 description 1

- 238000007781 pre-processing Methods 0.000 description 1

- 238000001556 precipitation Methods 0.000 description 1

- 238000002203 pretreatment Methods 0.000 description 1

- 230000009257 reactivity Effects 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 150000003609 titanium compounds Chemical class 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/07—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L29/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/18—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof the devices being of types provided for in two or more different subgroups of the same main group of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/063—Reduced surface field [RESURF] pn-junction structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

- H01L29/0653—Dielectric regions, e.g. SiO2 regions, air gaps adjoining the input or output region of a field-effect device, e.g. the source or drain region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table

- H01L29/1608—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42372—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out

- H01L29/42376—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the conducting layer, e.g. the length, the sectional shape or the lay-out characterised by the length or the sectional shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/66068—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/08—Circuits specially adapted for the generation of control voltages for semiconductor devices incorporated in static converters

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/0601—Structure

- H01L2224/0603—Bonding areas having different sizes, e.g. different heights or widths

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0618—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/06181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/33—Structure, shape, material or disposition of the layer connectors after the connecting process of a plurality of layer connectors

- H01L2224/331—Disposition

- H01L2224/3318—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/33181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/4847—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond

- H01L2224/48472—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a wedge bond the other connecting portion not on the bonding area also being a wedge bond, i.e. wedge-to-wedge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/42—Conversion of dc power input into ac power output without possibility of reversal

- H02M7/44—Conversion of dc power input into ac power output without possibility of reversal by static converters

- H02M7/48—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/53—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M7/537—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters

- H02M7/5387—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters in a bridge configuration

- H02M7/53871—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters in a bridge configuration with automatic control of output voltage or current

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02P—CONTROL OR REGULATION OF ELECTRIC MOTORS, ELECTRIC GENERATORS OR DYNAMO-ELECTRIC CONVERTERS; CONTROLLING TRANSFORMERS, REACTORS OR CHOKE COILS

- H02P27/00—Arrangements or methods for the control of AC motors characterised by the kind of supply voltage

- H02P27/04—Arrangements or methods for the control of AC motors characterised by the kind of supply voltage using variable-frequency supply voltage, e.g. inverter or converter supply voltage

- H02P27/06—Arrangements or methods for the control of AC motors characterised by the kind of supply voltage using variable-frequency supply voltage, e.g. inverter or converter supply voltage using dc to ac converters or inverters

- H02P27/08—Arrangements or methods for the control of AC motors characterised by the kind of supply voltage using variable-frequency supply voltage, e.g. inverter or converter supply voltage using dc to ac converters or inverters with pulse width modulation

Definitions

- This disclosure relates to power semiconductor devices.

- SiC semiconductor device A semiconductor device using a silicon carbide (SiC) substrate (hereinafter referred to as "SiC semiconductor device”) has a withstand voltage as compared with a semiconductor device using a silicon (Si) substrate (hereinafter referred to as “Si semiconductor device”). And has excellent heat resistance.

- SiC semiconductor devices have been used as MOSFETs (metal-oxide-semiconductor field-effect transistors) or IGBTs (insulated gate bipolar transistors) in order to enable high withstand voltage, low loss, or use in high temperature environments. ), Etc. are applied to semiconductor devices for electric power.

- the SiC semiconductor device can make the withstand voltage layer (drift layer) for achieving the same withstand voltage thinner than that of the Si semiconductor device. Further, the SiC semiconductor device can increase the amount of impurity doping in the pressure-resistant layer as compared with the Si semiconductor device. For these reasons, the SiC semiconductor device can obtain a significantly smaller on-resistance than the Si semiconductor device. For example, the on-resistance of a SiC-MOSFET having a withstand voltage of 1 kV or more and 1.2 kV or less is 5 m ⁇ cm 2 or less, which is less than half the value of a Si-MOSFET or Si-IGBT having the same withstand voltage.

- Si-IGBTs as inverter parts will be replaced with SiC semiconductor devices as the manufacturing cost improves, the process technology improves, and other performance improvements occur.

- trench gate type SiC-MOSFETs or SiC-IGBTs have been developed in order to reduce the loss of the SiC semiconductor device when energized.

- the trench gate type SiC-MOSFET or SiC-IGBT has a problem that a damage layer is generated on the inner wall of the trench during etching for forming the trench.

- Patent Document 1 discloses a method for manufacturing a SiC-MOSFET that removes a damaged layer on the inner wall of a trench. According to the manufacturing method of Patent Document 1, a deposition film having a thickness on the surface of the semiconductor substrate is formed on the surface of the semiconductor substrate and the inner wall of the trench to be thicker than the thickness of the inner wall of the trench. Then, the portion of the sedimentary membrane covering the inner wall of the trench is removed to expose the inner wall of the trench. Next, after growing an oxide film on the inner wall of the trench, the sedimentary film and the oxide film are removed.

- the oxide film is less likely to be formed on the surface of the semiconductor substrate. Therefore, the diffusion layer on the surface of the semiconductor substrate can be maintained.

- the power module includes a power semiconductor device and an energizing wire connected to the power semiconductor device.

- a wire for energization is connected to a trench gate type power semiconductor device, there is a problem that the trench gate is destroyed by the stress applied from the wire to the power semiconductor device at the time of connection, and the power module does not operate.

- the gate electrode since the gate electrode is uniformly formed in the trench, the gate electrode may be displaced from the SiC substrate when stress is applied from the surroundings. appear. This phenomenon is particularly remarkable for stresses in the direction parallel to the trench gate.

- the present disclosure has been made to solve the above-mentioned problems, and an object of the present disclosure is to provide a trench gate type power semiconductor device that does not easily break even when stress is applied.

- the power semiconductor device of the present disclosure includes a SiC substrate, a first conductive type drift layer formed on the SiC substrate, and a second conductive type first different from the first conductive type formed on the surface layer of the drift layer.

- a gate electrode embedded in a V-shaped groove and having a V-shaped groove on the upper surface thereof, and an oxide film formed on the upper surface including the groove of the gate electrode are provided, and the bottom portion of the V-shaped groove is deeper than the first impurity region.

- a first conductive type drift layer is formed on a SiC substrate, and a second conductive type first impurity region different from the first conductive type is formed on the surface layer of the drift layer.

- a first conductive type second impurity region is selectively formed on the surface layer of the first impurity region, and a trench that penetrates the first impurity region and the second impurity region and reaches the drift layer is formed, and the trench is formed.

- a gate electrode having a V-shaped groove is formed on the upper surface, and an oxide film is formed on the upper surface including the groove of the gate electrode.

- volume expansion occurs in the process of forming an oxide film on the surface of the groove of the gate electrode, so that the bonding strength between the gate electrode and the trench via the gate insulating film is improved. As a result, the gate electrode is not easily broken even when stress is applied.

- FIG. It is sectional drawing of the SiC-MOSFET of Embodiment 1.

- FIG. It is a flowchart which shows the manufacturing process of the SiC-MOSFET of Embodiment 1. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1. FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1. FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1. FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1. FIG.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is sectional drawing in the process of manufacturing the SiC-MOSFET of Embodiment 1.

- FIG. It is an enlarged sectional view around the trench gate of the SiC-MOSFET of Embodiment 1.

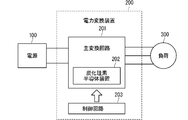

- FIG. It is a block diagram which shows the structure of the power conversion system of Embodiment 4.

- FIG. 1 is a cross-sectional view showing a cell structure of a main part of the SiC-MOSFET 101.

- the SiC-MOSFET 101 is a power semiconductor device of the first embodiment having a trench gate structure.

- the five cell structures are shown in FIG. 1, the number of cells of the SiC-MOSFET 101 is not limited to this. Actually, the cell structure shown in FIG. 1 is continuous in an arbitrary number in the horizontal direction of the paper surface.

- the SiC-MOSFET 101 includes an n-type SiC substrate 1, an n-type SiC drift layer 2, a p-type base region 3, an n-type source region 4, a p-type bottom base region 5, a gate insulating film 6, and a gate. It includes an electrode 7, an oxide film 8, an interlayer insulating film 9, a source electrode 10, and a drain electrode 11.

- the main surface on the upper side of the paper surface of the SiC substrate 1 is referred to as the first main surface (hereinafter, also referred to as “front surface”), and the main surface on the lower side of the paper surface is referred to as the second main surface (hereinafter, also referred to as “back surface”). ).

- the drift layer 2 epitaxially grows on the first main surface of the SiC substrate 1.

- the base region 3 is selectively formed as the first impurity region on the surface layer of the drift layer 2.

- a source region 4 is selectively formed as a second impurity region on the surface layer of the base region 3. From the surface of the source region 4, a trench 19 having a depth that penetrates the source region 4 and the base region 3 and reaches the drift layer 2 is formed.

- a bottom base region 5 is formed as a third impurity region in the drift layer 2 at the bottom of the trench 19.

- a gate insulating film 6 is formed on the inner wall of the trench 19.

- a gate electrode 7 is formed inside the trench 19. The upper surface of the gate electrode 7 is covered with the oxide film 8.

- An interlayer insulating film 9 is formed on the upper part of the oxide film 8 and the upper part of the source region 4.

- a source electrode 10 is formed on the base region 3, the source region 4, and the interlayer insulating film 9.

- a drain electrode 11 is formed on the second main surface of the SiC substrate 1.

- the bottom base region 5 is not limited to the one provided in contact with the bottom of the trench 19, and may be provided in the drift layer 2 below the bottom of the trench 19. Further, the bottom base region 5 is not limited to covering the entire bottom of the trench 19, and may be provided so as to cover at least a part of the bottom of the trench 19. For example, the bottom base region 5 may be periodically arranged at intervals along the stretching direction of the trench 19, or may be provided so as to cover about half of the bottom of the trench 19 in a cross section orthogonal to the stretching direction. It may be. Alternatively, the bottom base region 5 may be configured so that the width of the bottom base region 5 is larger than the width of the trench 19 by covering the entire bottom so as to protrude in the width direction of the trench 19.

- the bottom base region 5 is not limited to the one provided along the stretching direction of the trench 19, and a plurality of bottom base regions 5 are stretched in a direction orthogonal to the stretching direction of the trench 19 to partially provide the bottom of the trench 19 in the stretching direction. May be periodically covered.

- the bottom base region 5 may be provided between the adjacent trenches 19 in the drift layer 2 in parallel with the extending direction of the trench 19.

- the bottom base region 5 is not limited to being provided linearly and continuously, and may be provided periodically at intervals in the extending direction of the trench 19.

- the formation position of the bottom base region 5 may be such that the depth of the drift layer 2 from the outermost layer is the same as the depth of the bottom of the trench 19, and may be shallow or deep.

- FIG. 2 is a flowchart showing a manufacturing process of SiC-MOSFET 101.

- the manufacturing process of the SiC-MOSFET 101 will be described along with the flow of FIG.

- the n-type SiC substrate 1 is prepared (step S1).

- a drift layer 2 made of n-type SiC is formed as an epitaxial film on the front surface of the SiC substrate 1.

- a mask (not shown) made of a resist or the like is formed on the drift layer 2, and p-type impurities are ion-implanted into the drift layer 2 through the opening of the mask.

- a p-type base region 3 is formed on the surface layer of the drift layer 2 (step S2).

- the p-type impurity is, for example, boron (B) or aluminum (Al).

- n-type impurities are ion-implanted into the base region 3 from the opening of the mask.

- a mask (not shown) made of a resist or the like is formed on the base region 3, and n-type impurities are ion-implanted into the base region 3 from the opening of the mask.

- an n-type source region 4 is selectively formed on the surface layer of the base region 3 (step S3).

- the fact that the source region 4 is selectively formed on the surface layer of the base region 3 means that there is a portion of the surface layer of the base region 3 in which the source region 4 is formed and a portion in which the source region 4 is not formed.

- n-type impurities include phosphorus (P) and nitrogen (N).

- the SiC wafer is heat-treated at a high temperature by a heat treatment device (not shown).

- a heat treatment device not shown.

- the p-type impurities and n-type impurities injected into the base region 3 and the source region 4 are electrically activated.

- a mask (not shown) made of resist or the like is formed on the surfaces of the base region 3 and the source region 4.

- the trench 19 is formed as shown in FIG. 6 by dry etching using plasma or the like (step S4).

- an oxide film made of, for example, TEOS is formed on the surfaces of the base region 3 and the source region 4, and the oxide film is used as a resist mask. It may be dry-etched by. This makes it possible to form a deep trench 19.

- p-type impurities are ion-implanted into the bottom of the trench 19.

- a p-shaped bottom base region 5 is formed at the bottom of the trench 19.

- the bottom base region 5 serves to relax the electric field at the bottom of the trench gate.

- the p-type impurity is, for example, boron (B) or aluminum (Al).

- the inner wall of the trench 19 and the surfaces of the base region 3 and the source region 4 are oxidized using a thermal oxidation method.

- the thicker the layer to be oxidized the more plasma damage can be removed, but the base region 3 and the source region 4 are reduced by that amount. Therefore, the thickness of the layer to be oxidized is 20 nm or more and 80 nm or less, more preferably 30 nm or more and 70 nm or less.

- a gate insulating film 6 is formed on the inner wall of the trench 19 by a deposition method such as chemical vapor deposition or a thermal oxidation method (step S5).

- the gate insulating film 6 is formed on the side surface and the bottom surface of the trench 19.

- the gate insulating film 6 on the bottom surface of the trench 19 has a thickness equal to or greater than that of the gate insulating film 6 on the side surface of the trench 19, and is preferably 10% or more thick.

- a gate electrode 7 made of polysilicon is formed on the gate insulating film 6. Then, as shown in FIG. 10, the surplus gate electrode 7 other than the inside of the trench 19 is removed, and the gate electrode 7 is patterned (step S6). It is desirable to use isotropic etching for patterning the gate electrode 7. For example, in the case of dry etching, etching with plasma generated using a gas containing sulfur hexafluoride (SF6) is desirable, and in the case of wet etching, etching with a mixed acid containing hydrofluoric acid and nitric acid is desirable. By these etchings, a V-shaped groove 7a can be formed on the upper surface of the gate electrode 7.

- SF6 sulfur hexafluoride

- an oxide film 8 is formed on the upper surface of the gate electrode 7 including the V-shaped groove 7a by the thermal oxidation method.

- the oxidation temperature at the time of forming the oxide film 8 is preferably 850 ° C. or higher and 1050 ° C. or lower, and more preferably 900 ° C. or higher and 1000 ° C. or lower.

- the thickness of the oxide film 8 is preferably 10 nm or more and 40 nm or less, and more preferably 20 nm or more and 35 nm or less.

- the interlayer insulating film 9 is formed on the base region 3, the source region 4, and the oxide film 8 by using a CVD (chemical vapor deposition) method. Then, the interlayer insulating film 9 is patterned by photoengraving and etching treatment, and as shown in FIG. 12, the interlayer insulating film 9 is left only on the upper part of the oxide film 8 and the source region 4 (step S7). It is also possible to round the corners of the interlayer insulating film 9 by introducing an impurity such as B (boron) or P (phosphorus).

- the material of the interlayer insulating film 9 deposited by the CVD method is, for example, silicon nitride (SixNy) or silicon oxide (SiO2).

- the thickness of the interlayer insulating film 9 is preferably 0.5 ⁇ m or more and 2.0 ⁇ m or less.

- the source electrode 10 is formed into a film as shown in FIG. 13 (step S8).

- the material of the source electrode 10 is, for example, aluminum, an aluminum alloy composed of aluminum and silicon, nickel, or the like.

- a barrier metal made of titanium or a titanium compound such as titanium nitride (TiN) may be appropriately formed between the base region 3 and the source region 4 and the source electrode 10.

- step S9 the back surface of the SiC substrate 1 is ground with a grinding wheel to thin the SiC substrate 1 (step S9).

- a nickel film having a thickness of about 600 nm is formed on the back surface of the SiC substrate 1 as the drain electrode 11 by a sputtering method or the like (step S10).

- a metal that is difficult to oxidize such as gold or silver, can be formed on the surface of the nickel film as a protective film, and a laminated film composed of the nickel film and the protective film can be used as the drain electrode 11.

- the SiC-MOSFET 101 shown in FIG. 1 is completed.

- FIG. 14 is an enlarged cross-sectional view of the trench gate of the SiC-MOSFET 101 and its surroundings.

- the y-axis is taken in the thickness direction of the SiC-MOSFET 101

- the z-axis is taken in the width direction of the trench 19

- the x-axis is taken in the direction perpendicular to the yz plane.

- a V-shaped groove 7a is formed on the upper surface of the gate electrode 7.

- the groove 7a is formed when the excess portion of the gate electrode 7 is removed by isotropic etching.

- Let ⁇ be the angle of the side surface of the groove 7a with respect to the thickness direction (z direction) of the SiC-MOSFET 101.

- ⁇ is the angle at which the vertical direction (z direction) of the paper surface of FIG. 14 intersects with the straight line drawn along the side surface of the groove 7a.

- d be the depth of the groove 7a.

- d is the distance between two midpoints adjacent to the groove 7a on the upper surface of the gate electrode 7 and the bottom of the groove 7a.

- t be the depth of the gate electrode 7.

- t is the distance between two midpoints adjacent to the groove 7a on the upper surface of the gate electrode 7 and the bottom of the gate electrode 7.

- the side surface of the trench 19 in contact with the source region 4 becomes a curved shape bulging outward.

- the outer surface of the gate electrode 7 also has a curved shape in which the portion facing the source region 4 bulges outward along the shape of the side surface of the trench 19.

- the width of the portion of the gate electrode 7 facing the source region 4 increases from the upper surface of the gate electrode 7 in the depth direction, and then decreases again.

- the side surface of the gate electrode 7 has a convex portion in a portion facing the source region 4. At this portion, an anchor effect in the z direction is generated between the gate electrode 7 and the side surface of the trench 19.

- the gate electrode 7 and the trench 19 are compared with each other as compared with the case where the outer surface of the gate electrode 7 is straight.

- the joint strength is improved to each stage.

- the gate insulating film 6 on the side surface of the gate electrode 7 is formed thicker than the gate insulating film 6 on the bottom of the gate electrode 7.

- FIG. 15 is a photomicrograph showing a cross section of SiC-MOSFET 101.

- FIG. 16 is a top view of the SiC-MOSFET 101.

- FIG. 17 is a cross-sectional view taken along the line AA'of FIG. As shown in FIG. 16, there is a terminal region 12 outside the source electrode 10, and a terminal protective film 13 outside the terminal region 12. A part of the upper surface of the SiC-MOSFET 101 becomes the gate connecting portion 14.

- FIG. 18 shows the semiconductor module 110 of the first embodiment.

- the semiconductor module 110 includes a SiC-MOSFET 101, lead frames 15, 17, wires 18, solder 16, and a mold resin (not shown).

- the lead frame 17 is connected to the surface of the SiC-MOSFET 101 with a wire 18.

- the lead frame 15 is connected to the back surface of the SiC-MOSFET 101 with solder 16. After that, the SiC-MOSFET 101 and the lead frames 15 and 17 are sealed with the mold resin to complete the semiconductor module 110.

- FIG. 19 shows the leakage current between the gate electrode 7 and the source electrode 10 after assembling the semiconductor module 110 and d / t when the load when connecting the wire 18 to the SiC-MOSFET 101 is intentionally increased. Shows the relationship. As described above, d represents the depth of the groove 7a of the gate electrode 7, and t represents the depth of the gate electrode 7. According to FIG. 19, it is desirable that the depth d of the groove 7a is 10% or more and 70% or less of the depth t of the gate electrode 7. According to the inventor's analysis, when d is less than 10% of t, the gate electrode 7 moves in the x direction in FIG. 14 and breaks due to the stress when connecting the wire 18 to the SiC-MOSET 101. I found out. Further, when d exceeds 70% of t, it was found that the gate electrode 7 was broken starting from the groove 7a due to the stress when connecting the wire 18 to the SiC-MOSET 101.

- the wire 18 is bonded to the upper surface of the SiC-MOSFET 101, that is, a plane perpendicular to the depth direction (y-axis direction of FIG. 14) of the trench 19 (xz plane of FIG. 14).

- the direction of the wire 18 is not parallel to the plane (yz plane of FIG. 14) consisting of the depth direction of the trench 19 (y-axis direction of FIG. 14) and the width direction of the trench 19 (z-axis direction of FIG. 14)

- the effect of the characteristic trench gate structure of the SiC-MOSFET 101 can be obtained.

- the angle formed by the wire 18 and the trench 19 in the depth direction is 60 degrees or less, the effect of the characteristic trench gate structure of the SiC-MOSFET 101 can be remarkably obtained.

- FIG. 20 shows the relationship between the leakage current between the gate electrode 7 and the source electrode 10 after assembling the semiconductor module 110 and ⁇ .

- ⁇ is the angle formed by the thickness direction (z direction) of the SiC-MOSFET 101 and the side surface of the groove 7a.

- ⁇ is 1 degree or more and 20 degrees or less.

- the gate electrode 7 cracks from the groove 7a toward the lower side of the paper surface due to the stress when connecting the wire 18 to the SiC-MOSFET 101. Has progressed and it has been confirmed that it has been destroyed. Further, when ⁇ exceeds 20 degrees, it was found that the gate electrode 7 was destroyed by moving in the x direction in FIG. 14 due to the stress when connecting the wire 18 to the SiC-MOSFET 101.

- the conductive type of each semiconductor layer of the SiC-MOSFET 101 is clearly described as n-type or p-type.

- the conductive type of each semiconductor layer may be inverted. That is, in the above, the conductive type of the SiC substrate 1, the drift layer 2, and the source region 4 is n-type, and the conductive type of the base region 3 and the bottom base region 5 is p-type, but these are opposite conductive types. Is also good.

- the SiC-MOSFET 101 of the first embodiment is formed on the SiC substrate 1, the first conductive type drift layer 2 formed on the SiC substrate 1, and the first surface layer of the drift layer.

- the base region 3 which is the first impurity region of the second conductive type different from the conductive type

- the source region 4 which is the second impurity region of the first conductive type formed on the surface layer of the first impurity region, and the first impurity region.

- a gate electrode 7 that is embedded in the trench 19 and has a V-shaped groove 7a on the upper surface, and a groove 7a of the gate electrode 7 are included.

- An oxide film 8 formed on the upper surface thereof is provided.

- a first conductive type drift layer 2 is formed on a SiC substrate 1, and a second conductive type first, which is different from the first conductive type, is formed on the surface layer of the drift layer 2.

- a base region 3 which is an impurity region is formed, a source region 4 which is a first conductive type second impurity region is formed on the surface layer of the first impurity region, and drifts through the first impurity region and the second impurity region.

- a trench 19 reaching the layer 2 is formed, a gate electrode 7 having a V-shaped groove 7a on the upper surface is formed in the trench 19, and an oxide film 8 is formed on the upper surface including the groove 7a of the gate electrode 7.

- FIG. 21 is a cross-sectional view showing a cell structure of a main part of the SiC-MOSFET 102.

- the SiC-MOSFET 102 is a power semiconductor device of the second embodiment having a trench gate structure.

- FIG. 21 shows five cell structures, the number of cells of the SiC-MOSFET 102 is not limited to this. Actually, the cell structure shown in FIG. 21 is continuous in an arbitrary number in the lateral direction of the paper surface.

- the depth of the base region 3 is not constant, and there is a shallow portion and a deep portion between two adjacent gate electrodes 7.

- the shallow portion of the base region 3 is also referred to as a first region, and the deep portion is also referred to as a second region. That is, the base region 3 has a first region and a second region deeper than the first region.

- the source region 4 overlaps the entire first region and a part of the second region.

- the second region of the base region 3 contacts the bottom base region 5.

- the SiC-MOSFET 102 is similar to the SiC-MOSFET 101 except for the depth of the base region 3.

- step S2 The manufacturing process of the SiC-MOSFET 102 is as shown in FIG. Since the step of forming the base region 3 (step S2) and the step of forming the source region 4 (step S3) are different from those of the first embodiment, they will be described below.

- the p-type base region 3 is formed on the surface layer of the drift layer 2. (Step S2).

- a shallow base region 3 and a deep base region 3 are formed.

- a mask (not shown) made of a resist or the like is formed on the base region 3, and an n-type impurity is ion-implanted into the base region 3 through the opening of the mask to form an n-type source on the surface layer of the base region 3.

- Region 4 is selectively formed (step S3).

- the source region 4 overlaps the entire shallow region of the base region 3 and a part of the deep region in a plan view.

- the base region 3 and the source region 4 are activated to form the trench 19, and the bottom base region 5 is formed at the bottom of the trench 19 as shown in FIG. 23.

- the gate insulating film 6, the gate electrode 7, the interlayer insulating film 9, the source electrode 10 and the drain electrode 11 are formed in the same manner as in the first embodiment, and the SiC-MOSFET 102 shown in FIG. 21 is completed.

- FIG. 24 is an enlarged cross-sectional view of the trench gate of the SiC-MOSFET 102 and its surroundings. According to the trench gate structure of the SiC-MOSFET 102, the following effects can be obtained in addition to the effects of the trench gate structure of the SiC-MOSFET 101.

- the base region 3 which is the first impurity region has a first region and a second region deeper than the first region.

- the SiC-MOSFET 102 on the left side of the gate electrode 7, the second region of the base region 3 is in contact with the bottom base region 5, which is the third impurity region. As a result, the source electrode 10 and the p-type bottom base region 5 are electrically connected through the p-type base region 3. Therefore, even when a high electric field is applied to the bottom base region 5 due to switching or the like, the on / off operation of the SiC-MOSFET 102 can be ensured.

- FIG. 25 is a cross-sectional view showing the cell structure of the main part of the SiC-MOSFET 103.

- the SiC-MOSFET 103 is a power semiconductor device of the third embodiment having a trench gate structure.

- FIG. 25 shows five cell structures, the number of cells of the SiC-MOSFET 103 is not limited to this. In practice, any number of cell structures shown in FIG. 25 are continuous in the lateral direction of the paper.

- the SiC-MOSFET 103 shown in FIG. 25 includes a source electrode 20 in addition to the configuration of the SiC-MOSFET 101 shown in FIG.

- the SiC-MOSFET 103 may include a source electrode 20 in addition to the configuration of the SiC-MOSFET 102 shown in FIG.

- the source electrode 20 is formed on the source electrode 10.

- the source electrode 10 is also referred to as a first source electrode

- the source electrode 20 is also referred to as a second source electrode.

- FIG. 26 is a flowchart showing a manufacturing process of the SiC-MOSFET 103.

- a plating pretreatment step S11

- a plating treatment step S12

- FIG. 27 is a flowchart showing step S11 and step S12 shown in FIG. 26 in more detail.

- Step S11 in FIG. 26 corresponds to steps S21 to S24 in FIG.

- step S12 in FIG. 26 corresponds to steps S25 and S26 in FIG. 27.

- the source electrode 10 is made of an aluminum alloy, even if the generally known degreasing and pickling are performed, a strong organic residue and an oxide film are still present on the upper surface of the aluminum alloy. Therefore, even if the plating treatment is performed after that, metal diffusion is not sufficiently generated between the aluminum alloy and the plated metal, and a plating layer having a strong adhesive force cannot be formed. Therefore, in step S11, the upper surface of the source electrode 10 is pre-plated before the plating.

- the plating pretreatment is as follows. First, the surface activation treatment is performed in step S21.

- the surface activation treatment is carried out using, for example, plasma.

- plasma cleaning cleans the upper surface of the source electrode 10 by oxidatively decomposing organic residues that are burnt onto the upper surface of the source electrode 10 and cannot be removed by general plating pretreatment, or by knocking them out with plasma. It is possible.

- step S22 the degreasing treatment is performed in step S22.

- the degreasing treatment is performed to remove mild organic contamination or an oxide film remaining on the upper surface of the source electrode 10.

- step S23 acid cleaning is performed in step S23.

- the acid cleaning neutralizes the upper surface of the source electrode 10 and roughens it by etching.

- the acid cleaning enhances the reactivity of the treatment liquid in the subsequent process and improves the adhesive force of the plating film.

- the zincate treatment is a treatment for forming a zinc (Zn) film while removing the aluminum oxide film on the upper surface of the aluminum alloy when the source electrode 10 is made of an aluminum alloy.

- the zincate treatment is a treatment for forming a zinc (Zn) film while removing the aluminum oxide film on the upper surface of the aluminum alloy when the source electrode 10 is made of an aluminum alloy.

- aluminum dissolves as ions because the standard oxidation-reduction potential of zinc is higher than that of aluminum.

- the electrons generated at this time cause zinc ions to receive electrons on the upper surface of the aluminum alloy, forming a zinc film on the upper surface of the aluminum alloy.

- the aluminum oxide film is removed.

- the zincate treatment may be performed multiple times. For example, after performing the first gyere treatment, the gyere formed by the first gyere treatment is peeled off. Then, the second zincate treatment is performed.

- Steps S24 to S27 described above are plating pretreatments. It is necessary to secure a sufficient washing time between each step from step S24 to step S27 so that the treatment liquid or residue of the previous step is not brought into the next step.

- step S12 a plating process, which is a wet film forming method, is performed. Specifically, first, electroless Ni plating is formed in step S25.

- electroless Ni plating is formed in step S25.

- an aluminum alloy in which a zinc film is formed is immersed in a non-electrolytic Ni plating solution, first, nickel is deposited on the upper surface of the aluminum alloy because the standard oxidation-reduction potential of zinc is lower than that of nickel.

- an electroless Ni plating film having a thickness of 5 ⁇ m is formed on the upper surface of the source electrode 10.

- electroless Au plating is formed in step S26.

- the replacement type electroless Au plating is formed on the upper surface of the electroless Ni plating, and utilizes the action of replacing nickel and Au by the action of a complexing agent contained in the plating solution.

- electroless Au plating is a substitution type, the reaction stops when the surface of nickel is covered with Au. Therefore, it is difficult to form a thick electroless Au plating film.

- the thickness of electroless Au plating is at most 0.1 ⁇ m, and is generally about 0.05 ⁇ m in many cases. However, when used for soldering, the thickness of Au plating is not too thin even with the above-mentioned values.

- the film formed by the electroless Ni plating and the electroless Au plating thus formed is the source electrode 20.

- FIG. 28 is a cross-sectional view showing a manufacturing process of the semiconductor module.

- the upper surface and the lower surface of the SiC-MOSFET 103 are connected to the lead frame 27 by using solder 26, respectively.

- the SiC-MOSFET 103 and a part of the lead frame 27 are sealed with the mold resin 22 so that the tip of the lead frame 27 is exposed, and the semiconductor module is completed.

- FIG. 30 is a cross-sectional view showing a cell structure of a main part of SiC-MOSFET 103A, which is a power semiconductor device of the first modification of the first modification of the third embodiment having a trench gate structure.

- the five cell structures are shown in FIG. 30, the number of cells of the SiC-MOSFET 103A is not limited to this. In practice, any number of cell structures shown in FIG. 30 are continuous in the lateral direction of the paper.

- the interlayer insulating film 9 is formed on all the gate electrodes 7 via the oxide film 8, whereas in the SiC-MOSFET 103A, the interlayer insulating film 9 is formed on some of the gate electrodes 7. Not formed.

- the SiC-MOSFET 103A is formed as follows. After forming the gate electrode 7, an interlayer insulating film 9 is formed on the base region 3, the source region 4, and the oxide film 8. Then, when the interlayer insulating film 9 is patterned by photoengraving and etching, as shown in FIG. 30, the interlayer is formed only on a part of the gate electrode 7 and the source region 4 adjacent to the part of the gate electrode 7. The insulating film 9 is left. In the SiC-MOSFET 103A, only the gate electrode 7 on which the interlayer insulating film 9 is formed is used for switching. Therefore, it is possible to control the energization performance of the SiC-MOSFET 103A by patterning the interlayer insulating film 9.

- FIG. 31 is a cross-sectional view showing the cell structure of the main part of the SiC-MOSFET 103B, which is a power semiconductor device of the second modification of the third embodiment having a trench gate structure.

- FIG. 31 shows five cell structures, the number of cells of the SiC-MOSFET 103B is not limited to this. In practice, the cell structures shown in FIG. 31 are continuous in an arbitrary number in the lateral direction of the paper surface.

- the SiC-MOSFET 103B is a SiC-MOSFET 103A in which the drain electrode 21 of the plating film is added on the drain electrode 11.

- the drain electrode 11 is also referred to as a first drain electrode

- the drain electrode 21 is also referred to as a second drain electrode.

- the drain electrode 21 can be formed at the same time as the source electrode 20 in the manufacturing process of the SiC-MOSFET 103 described in ⁇ C-2>.

- the source electrode 20 is thicker than the drain electrode 21.

- the thickness of the source electrode 20 is preferably 1.05 times or more the thickness of the drain electrode 21.

- the solder or wire that joins the SiC-MOSFET 103, or the expansion and contraction of the source electrodes 10 and 20 included in the SiC-MOSFET 103 causes the SiC substrate to be composed of SiC.

- a force in the compressive and tensile directions (hereinafter referred to as "stretching stress”) is generated between the 1 and the drift layer 2 and the gate electrode 7 made of silicon.