WO2021132084A1 - 抵抗デバイス、集積回路装置、体内埋込装置、及び、補正係数決定方法 - Google Patents

抵抗デバイス、集積回路装置、体内埋込装置、及び、補正係数決定方法 Download PDFInfo

- Publication number

- WO2021132084A1 WO2021132084A1 PCT/JP2020/047455 JP2020047455W WO2021132084A1 WO 2021132084 A1 WO2021132084 A1 WO 2021132084A1 JP 2020047455 W JP2020047455 W JP 2020047455W WO 2021132084 A1 WO2021132084 A1 WO 2021132084A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- voltage

- temperature

- transistor

- current

- value

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- A—HUMAN NECESSITIES

- A61—MEDICAL OR VETERINARY SCIENCE; HYGIENE

- A61N—ELECTROTHERAPY; MAGNETOTHERAPY; RADIATION THERAPY; ULTRASOUND THERAPY

- A61N1/00—Electrotherapy; Circuits therefor

- A61N1/02—Details

- A61N1/025—Digital circuitry features of electrotherapy devices, e.g. memory, clocks, processors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45475—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using IC blocks as the active amplifying circuit

-

- A—HUMAN NECESSITIES

- A61—MEDICAL OR VETERINARY SCIENCE; HYGIENE

- A61N—ELECTROTHERAPY; MAGNETOTHERAPY; RADIATION THERAPY; ULTRASOUND THERAPY

- A61N1/00—Electrotherapy; Circuits therefor

- A61N1/02—Details

- A61N1/08—Arrangements or circuits for monitoring, protecting, controlling or indicating

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01K—MEASURING TEMPERATURE; MEASURING QUANTITY OF HEAT; THERMALLY-SENSITIVE ELEMENTS NOT OTHERWISE PROVIDED FOR

- G01K7/00—Measuring temperature based on the use of electric or magnetic elements directly sensitive to heat ; Power supply therefor, e.g. using thermoelectric elements

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is DC

- G05F1/56—Regulating voltage or current wherein the variable actually regulated by the final control device is DC using semiconductor devices in series with the load as final control devices

- G05F1/565—Regulating voltage or current wherein the variable actually regulated by the final control device is DC using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor

- G05F1/567—Regulating voltage or current wherein the variable actually regulated by the final control device is DC using semiconductor devices in series with the load as final control devices sensing a condition of the system or its load in addition to means responsive to deviations in the output of the system, e.g. current, voltage, power factor for temperature compensation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K17/081—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit

- H03K17/08104—Modifications for protecting switching circuit against overcurrent or overvoltage without feedback from the output circuit to the control circuit in field-effect transistor switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45526—Indexing scheme relating to differential amplifiers the FBC comprising a resistor-capacitor combination and being coupled between the LC and the IC

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45544—Indexing scheme relating to differential amplifiers the IC comprising one or more capacitors, e.g. coupling capacitors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K2017/0806—Modifications for protecting switching circuit against overcurrent or overvoltage against excessive temperature

Definitions

- the present invention relates to a resistance device, an integrated circuit device, an implantable device, and a method for determining a correction coefficient.

- the amplifier circuit described in Patent Document 1 includes a field effect transistor as a feedback resistor and a resistance correction unit.

- the resistance correction unit corrects the fluctuation of the resistance between the drain and the source of the field effect transistor due to the temperature change.

- the resistance correction unit applies a gate voltage Vg equal to or less than the threshold voltage Vth to the gate terminal of the field effect transistor so that the difference (Vgs-Vth) between the voltage Vgs and the threshold voltage Vth becomes a constant value. Therefore, the resistance Rds between the drain and the source of the field effect transistor is controlled to be a predetermined value.

- the resistance correction unit has a temperature detection unit.

- the temperature detection unit outputs a voltage or current that changes linearly with respect to a temperature change.

- the resistance correction unit is below the threshold voltage with respect to the gate terminal of the field effect transistor so that the resistance Rds between the drain and the source of the field effect transistor becomes a predetermined value based on the current or voltage output by the temperature detection unit.

- the gate voltage Vg of is applied.

- the resistance correction unit further has a storage unit and a calculation unit.

- the storage unit stores the relationship between the current or voltage output by the temperature detection unit and the temperature of the temperature detection unit. Further, the storage unit stores the relationship between the temperature of the temperature detection unit and the gate voltage Vg applied to the gate terminal of the field effect transistor.

- the relationship between the current or voltage output by the temperature detection unit and the temperature of the temperature detection unit is stored in the storage unit by measuring the relationship between the temperature and the current or voltage output by the temperature detection unit in advance.

- the relationship between the temperature of the temperature detector and the gate voltage Vg applied to the gate terminal of the field effect transistor is the difference between the voltage Vgs between the gate and source of the field effect transistor and the threshold voltage Vth (Vgs-Vth) at each temperature.

- the gate voltage Vg at which is a constant value is determined and stored in the storage unit.

- the calculation unit refers to the relationship between the current or voltage output by the temperature detection unit stored in the storage unit and the temperature of the temperature detection unit, and the temperature of the temperature detection unit is based on the current or voltage output by the temperature detection unit. Ask for. Further, the arithmetic unit refers to the relationship between the temperature of the temperature detection unit stored in the storage unit and the gate voltage Vg applied to the gate terminal of the field effect transistor, and based on the obtained temperature, the gate terminal of the field effect transistor. The gate voltage Vg to be applied to is determined.

- Patent Document 1 does not describe a method for determining the gate voltage Vg at which the difference (Vgs-Vth) between the voltage Vgs and the threshold voltage Vth of the field effect transistor becomes a constant value at a plurality of different temperatures.

- Patent Document 1 states that the temperature dependence of the resistance Rds (an example of a physical quantity relating to the field effect transistor) between the drain and the source of the field effect transistor is reduced so that the resistance Rds becomes a predetermined value. There is no description about the method of determining the correction value when correcting Vg.

- An object of the present invention is a combination of a correction coefficient for correcting a control voltage applied between a gate and a source in order to reduce the temperature dependence of a desired physical quantity for a field effect transistor and a desired physical quantity for a field effect transistor.

- the present invention is to provide a resistance device, an integrated circuit device, an implantable device, and a method for determining a correction coefficient that can efficiently determine the above.

- the resistance device includes a field effect transistor and a voltage application circuit.

- the voltage application circuit applies a control voltage according to the temperature between the gate and the source of the field-effect transistor to control the resistance value between the drain and the source of the field-effect transistor.

- the control voltage indicates a voltage obtained by adding a correction voltage to a reference voltage.

- the correction voltage depends on the temperature and is set to be zero at the first temperature.

- the voltage application circuit preferably includes a temperature detection unit and a control voltage application unit.

- the temperature detection unit preferably outputs a detection signal corresponding to the temperature.

- the control voltage application unit generates the control voltage so that the control voltage includes the correction voltage that changes linearly with respect to the temperature in response to the detection signal, and transfers the control voltage to the field effect transistor of the field effect transistor. It is preferable to apply between the gate and the source.

- the first temperature preferably indicates the temperature when the physical quantity of the field effect transistor is substantially constant with respect to the change of the correction coefficient, which is a coefficient for determining the correction voltage. ..

- the value of the correction coefficient which is a coefficient for determining the correction voltage, is based on the reference voltage when the target physical quantity for the field effect transistor is obtained at the first temperature. It is preferable to show the value when the target physical quantity is obtained at a second temperature different from the temperature.

- the temperature detection unit preferably includes a first current source circuit that generates a first current and a second current source circuit that generates a second current. It is preferable that the temperature dependence of the first current source circuit and the temperature dependence of the second current source circuit are different.

- the first current source circuit and the second current source circuit are preferably connected in series. It is preferable that the difference current between the first current and the second current is the detection signal.

- the first temperature is changed by the first current source circuit changing the current value of the first current and / or the second current source circuit changing the current value of the second current. Is preferable.

- the voltage application circuit applies the control voltage between the gate and the source of the field effect transistor to control the resistance value between the drain and the source in the first operating region of the field effect transistor. It is preferable to do so.

- the first operating region is preferably a region in which the magnitude of the voltage between the gate and the source of the field effect transistor is larger than the magnitude of the threshold voltage.

- the voltage application circuit applies the control voltage between the gate and the source of the field effect transistor to control the resistance value between the drain and the source in the second operating region of the field effect transistor. It is preferable to do so.

- the second operating region is preferably a region in which the magnitude of the voltage between the gate and the source of the field effect transistor is smaller than the magnitude of the threshold voltage.

- the integrated circuit device integrates the field effect transistor and the voltage application circuit of the resistance device.

- the implantable device is implanted in the body.

- the implantable device includes at least one of a stimulator that gives a stimulus signal to a biological tissue and a measuring device that measures the biological signal.

- At least one of the stimulator and the measuring device includes the integrated circuit device described above.

- the correction coefficient determination method determines the correction coefficient when correcting the control voltage applied between the gate and the source of the field effect transistor.

- the control voltage is indicated by "Vgs”

- the reference voltage is indicated by “Vgs0”

- the correction voltage is indicated by "Vc”

- the correction coefficient is indicated by " ⁇ ”

- the variables are used.

- the temperature is indicated by “T”

- the first temperature which is the temperature at which the correction voltage Vc becomes zero, is indicated by "T1".

- the correction coefficient determination method includes a step of determining a specific voltage value which is a voltage value of the reference voltage Vgs0 when a target physical quantity related to the field effect transistor is obtained at the first temperature T1, and a second step different from the first temperature T1. 2.

- the step of determining a specific coefficient value which is a value of the correction coefficient ⁇ when the target physical quantity is obtained at the specific voltage value of the temperature and the reference voltage Vgs0 is included.

- the step of determining the specific voltage value of the reference voltage Vgs0 is a physical quantity relating to the electric field effect transistor while changing the voltage value of the reference voltage Vgs0 at the first temperature T1. And the voltage value of the reference voltage Vgs0 when the physical amount substantially matching the target physical amount is measured among the plurality of physical quantities measured while changing the voltage value of the reference voltage Vgs0. It is preferable to include a step of determining the specific voltage value of the reference voltage Vgs0. In the step of determining the specific coefficient value of the correction coefficient ⁇ , the physical quantity related to the electric field effect transistor is determined while changing the value of the correction coefficient ⁇ at the second temperature and the specific voltage value of the reference voltage Vgs0.

- the correction coefficient is the value of the correction coefficient ⁇ when the physical quantity that substantially matches the target physical quantity is measured among the plurality of physical quantities measured while changing the value of the correction coefficient ⁇ and the step of measuring. It is preferable to include a step of determining the specific coefficient value of ⁇ .

- the first temperature T1 indicates the temperature when the physical quantity of the field effect transistor is substantially constant with respect to the change of the correction coefficient ⁇ .

- the correction voltage Vc preferably has a value based on the difference current between the first current and the second current. It is preferable that the first current represents a current that changes linearly with a change in temperature.

- the second current preferably represents a current that changes linearly with respect to the change in temperature. It is preferable that the temperature dependence of the first current and the temperature dependence of the second current are different.

- the correction coefficient determining method may further include a step of changing the first temperature T1 by changing at least one of the current value of the first current and the current value of the second current. preferable.

- the target physical quantity is a physical quantity including the resistance value of the field effect transistor, which can be measured from an electronic circuit including the field effect transistor, and indicates a physical quantity set as a target value. Is preferable.

- a combination of a correction coefficient for correcting a control voltage applied between a gate and a source in order to reduce the temperature dependence of a desired physical quantity for a field effect transistor and a desired physical quantity for a field effect transistor. Can be provided with a resistance device, an integrated circuit device, an implantable device, and a method for determining a correction coefficient.

- FIG. (A) is a graph showing the Ids-Vgs characteristics in the saturation region at Vgs> Vth of a general NMOS transistor.

- (B) is a graph showing the Ids-Vds characteristics at Vgs> Vth of a general NMOS transistor.

- (A) is a graph showing the Ids-Vgs characteristics in the linear region at Vgs> Vth of a general NMOS transistor.

- (B) is a graph showing the relationship between the resistance value and Vgs in the linear region when Vgs> Vth of a general NMOS transistor. It is a graph which shows the temperature dependence of the drain current in the linear region with Vgs> Vth of a general NMOS transistor.

- (A) is a graph showing the Ids-Vgs characteristics in the saturation region at Vgs> Vth of a general NMOS transistor.

- (B) is a graph showing the temperature dependence of the drain current in the saturation region at Vgs> Vth of a general NMOS transistor.

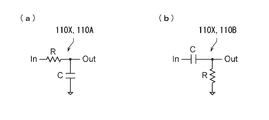

- (A) is a circuit diagram showing a first example of a voltage controlled voltage source according to the first embodiment.

- FIG. (B) is a circuit diagram showing a second example of the voltage controlled voltage source according to the first embodiment. It is a circuit diagram which shows an example of the temperature detection part and the correction voltage generation part which concerns on Embodiment 1.

- FIG. (A) is a graph showing the temperature dependence of the first current and the second current according to the first embodiment.

- (B) is a graph showing the temperature dependence of the differential current according to the first embodiment.

- (C) is a graph showing the temperature dependence of the correction voltage according to the first embodiment.

- (A) is a graph showing the temperature dependence of the first current and the second current when the current value of the first current according to the first embodiment is changed.

- (B) is a graph showing the temperature dependence of the first current and the second current when the current value of the second current according to the first embodiment is changed.

- (C) is a graph showing the temperature dependence of the differential current when the current value of the differential current according to the first embodiment is changed.

- (A) is a graph showing the relationship between the correction coefficient and the resistance value of the transistor at a plurality of different temperatures according to the first embodiment.

- (B) is a graph showing the effect of temperature correction on the temperature dependence of the resistance value of the transistor with respect to the first embodiment.

- (A) is a graph showing an R- ⁇ curve showing a resistance value of a transistor with respect to a correction coefficient at any two different temperatures according to the first embodiment.

- (B) is a graph showing the R- ⁇ curves showing the resistance values of the transistors with respect to the correction coefficients at the first temperature and the second temperature with respect to the first embodiment.

- (A) is a graph showing the relationship between the reference voltage at the first temperature and the resistance value of the transistor with respect to the first embodiment.

- (B) is a graph showing the relationship between the correction coefficient at the second temperature and the resistance value of the transistor with respect to the first embodiment.

- (C) is a graph showing the effect of temperature correction on the temperature dependence of the resistance value of the transistor with respect to the first embodiment.

- (A) is a semi-logarithmic graph showing the Ids-Vgs characteristics of a general NMOS transistor.

- (B) is a graph showing the Ids-Vds characteristics in the subthreshold region of a general NMOS transistor.

- (A) is a graph showing the Ids-Vgs characteristics in the subthreshold region of a general NMOS transistor.

- (B) is a semi-logarithmic graph showing the Ids-Vgs characteristics in the subthreshold region of a general NMOS transistor.

- (C) is a graph showing the relationship between the resistance value and Vgs in the subthreshold region of a general NMOS transistor.

- (A) is a graph showing the temperature dependence of the drain current in the subthreshold region of a general NMOS transistor.

- FIG. 1A is a diagram for explaining a first example of a method for measuring a resistance value of a transistor according to the first embodiment.

- FIG. (B) is a diagram for explaining a second example of the method for measuring the resistance value of the transistor according to the first embodiment.

- (A) is a diagram showing an electronic circuit device including the resistance device according to the first embodiment.

- (B) is a graph generalizing the relationship between the physical quantity measurable from the electronic circuit according to the first embodiment and the correction coefficient.

- (A) is a circuit diagram of an integral filter as an RC filter circuit according to the first embodiment.

- (B) is a circuit diagram of a differential filter as an RC filter circuit according to the first embodiment. It is a circuit diagram of the active filter circuit which concerns on Embodiment 1.

- FIG. It is a flowchart which shows the correction coefficient determination method which concerns on Embodiment 1.

- (A) is a flowchart showing step S3 of FIG. 22.

- (B) is a flowchart showing step S4 of FIG. 22.

- (A) to (d) are diagrams showing resistance devices according to the first modified example to the fourth modified example of the first embodiment. It is a figure which shows the resistance device which concerns on Embodiment 2 of this invention. It is a graph which shows the temperature dependence of the correction voltage which concerns on Embodiment 2.

- (A) is a graph showing the temperature dependence of the first current and the second current according to the second embodiment.

- (B) is a graph showing the temperature dependence of the differential current according to the second embodiment.

- (C) is a graph showing the temperature dependence of the correction voltage according to the second embodiment.

- (A) is a graph showing the R- ⁇ curves showing the resistance values of the transistors with respect to the correction coefficients at the first temperature and the second temperature with respect to the second embodiment, respectively.

- (B) is a graph showing the relationship between the reference voltage at the first temperature and the resistance value of the transistor according to the second embodiment.

- (C) is a graph showing the relationship between the correction coefficient at the second temperature and the resistance value of the transistor with respect to the second embodiment.

- (A) is a circuit diagram showing an example of the voltage application circuit according to the second embodiment.

- (B) is a diagram showing the temperature dependence of the PTAT current according to the second embodiment. It is a circuit diagram which shows an example of the PTAT circuit which concerns on Embodiment 2.

- FIG. 5 is a graph showing that the first temperature at which the PTAT current according to the second embodiment becomes zero can be changed.

- (A) to (d) are diagrams showing resistance devices according to the first modification to the fourth modification of the second embodiment. It is a figure which shows the resistance device which concerns on Embodiment 3 of this invention. It is a figure which shows the brain machine interface apparatus which concerns on Embodiment 4 of this invention. It is a circuit diagram which shows an example of the integrated circuit apparatus which concerns on Embodiment 4.

- the reference code attached to the current may be used as a code representing the "current value” of the current

- the reference code attached to the voltage may be used as the code representing the "voltage value” of the voltage

- the reference code attached to the resistance element may be used as a code indicating the resistance or the "resistance value” of the resistance element.

- FIG. 1 is a diagram showing a resistor device 100 according to the first embodiment.

- the resistance device 100 includes a field effect transistor TN and a voltage application circuit 1.

- the field effect transistor TN is an N-type field effect transistor.

- the field effect transistor TN is an n-type MOSFET (n-type Meter-Oxide-Semiconductor Field-Effective Transistor), that is, an NMOS transistor.

- transistor TN the field effect transistor TN may be referred to as "transistor TN".

- the back gate terminal of the field effect transistor TN may be connected to the source terminal or drain terminal of the field effect transistor TN, or may be connected to the ground or ground.

- the field effect transistor TN functions as a resistance element. Specifically, the field-effect transistor TN functions as a resistance element by utilizing the resistance between the drain and the source of the field-effect transistor TN. That is, the field effect transistor TN functions as a MOS resistor.

- MOS resistor For example, “CAMead,” Analog VLSI and Neural Systems “, Addison-Wesley Publishing Company, 1989.” or “T. Delbruck and CA Mead,” Adaptive photoreceptor with Wide dynamic range ", Proceedings of IEEE International Symposium on Circuits and Systems, 1994.”

- the field-effect transistor TN is a resistance element by utilizing the resistance between the drain and the source in the region (linear region and saturation region) where the gate-source voltage of the field-effect transistor TN is larger than the threshold voltage. Functions as. Further, the field effect transistor TN functions as a resistance element by utilizing the resistance between the drain and the source in the region (subthreshold region) where the voltage between the gate and the source of the field effect transistor TN is smaller than the threshold voltage.

- the MOS resistance MR has a resistance value R corresponding to the resistance value between the drain and the source of the field effect transistor TN.

- a voltage Vds corresponding to the voltage between the drain and the source of the field effect transistor TN is applied to the MOS resistance MR

- the current Ids corresponding to the drain current flowing between the drain and the source of the field effect transistor TN is applied to the MOS resistance MR.

- the resistance value R between the drain and the source of the field effect transistor TN may be described as "the resistance value R of the field effect transistor TN".

- the voltage application circuit 1 applies a control voltage Vgs corresponding to the temperature T between the gate and the source of the field effect transistor TN to control the resistance value R between the drain and the source of the field effect transistor TN.

- "Between the gate and the source of the field effect transistor TN” means "between the gate terminal and the source terminal of the field effect transistor TN”.

- the temperature T indicates the ambient temperature of the resistance device 100.

- the control voltage Vgs has a positive value.

- the control voltage Vgs indicates the voltage between the gate and the source of the field effect transistor TN.

- control voltage Vgs may be described as “gate-source voltage Vgs”. Further, the voltage Vds between the drain and the source may be described as “drain-source voltage Vds”.

- the control voltage Vgs indicates the voltage obtained by adding the correction voltage Vc to the reference voltage Vgs0. Specifically, the control voltage Vgs is represented by the equation (1).

- Vgs Vgs0 + Vc ... (1)

- the correction voltage Vc is a voltage added to the reference voltage Vgs0 in order to reduce the temperature dependence of a desired physical quantity on the field effect transistor TN.

- the physical quantity relating to the field effect transistor TN is a physical quantity including the resistance value R of the field effect transistor TN, which can be measured from an electronic circuit including the field effect transistor TN.

- the physical quantity of the field-effect transistor TN is, for example, the resistance value R between the drain and the source of the field-effect transistor TN, or the cutoff frequency fc of the filter circuit including the field-effect transistor TN.

- "Physical quantity including resistance value R" indicates a physical quantity depending on resistance value R.

- a desired physical quantity relating to the field effect transistor TN may be described as a “target physical quantity”. Therefore, the target physical quantity is a physical quantity including the resistance value R of the field effect transistor TN, which can be measured from an electronic circuit including the field effect transistor TN, and indicates a physical quantity set as a target value.

- the correction voltage Vc is represented by the equation (2).

- ⁇ indicates a correction coefficient

- T indicates a temperature

- T1 indicates a first temperature.

- the correction coefficient ⁇ is a coefficient for determining the correction voltage Vc.

- the correction coefficient ⁇ has a negative value. Therefore, the correction voltage Vc becomes smaller as the temperature T becomes higher.

- the correction coefficient ⁇ is a coefficient for correcting the control voltage Vgs applied between the gate and the source of the field effect transistor TN in order to reduce the temperature dependence of a desired physical quantity with respect to the field effect transistor TN. is there.

- Vc ⁇ (T-T1) ... (2)

- the correction voltage Vc depends on the temperature T and is set to be zero at the first temperature T1.

- the first temperature T1 is the temperature at which the correction voltage Vc becomes zero. Therefore, according to the first embodiment, the effect of the correction is lost at the first temperature T1.

- the correction coefficient ⁇ when correcting the control voltage Vgs applied between the gate and source of the field effect transistor TN and the field effect transistor The combination with the desired physical quantity for TN can be efficiently determined. Details of this point will be described later.

- FIG. 2 is a graph showing the correction voltage Vc.

- the vertical axis represents the correction voltage Vc [V]

- the horizontal axis represents the temperature T [K].

- the correction voltage Vc changes linearly with respect to the temperature T.

- the slope of the straight line indicating the correction voltage Vc indicates the correction coefficient ⁇ .

- a correction voltage Vc that changes linearly according to the temperature T shown in the equation (2) is added to the reference voltage Vgs0 as in the control voltage Vgs shown in the equation (1).

- the reason why the temperature dependence of the field effect transistor TN as the MOS resistance MR can be corrected will be described.

- the “Vgs> Vth” region is the operating region of the NOMS transistor when the magnitude of the gate-source voltage Vgs (voltage between the gate and source) is larger than the magnitude of the threshold voltage Vth.

- the “Vgs> Vth” region corresponds to an example of the “first operating region of the field effect transistor”.

- FIG. 3A is a graph showing the Ids-Vgs characteristics in the saturation region of the "Vgs> Vth" region of a general NMOS transistor.

- the horizontal axis represents the gate-source voltage Vgs [V]

- the vertical axis represents the drain current Ids [ ⁇ A].

- FIG. 3B is a graph showing the Ids-Vds characteristics of a general NMOS transistor.

- the horizontal axis represents the drain-source voltage Vds [V], and the vertical axis represents the drain current Ids [ ⁇ A].

- the region represented by "Vds> Vgs-Vth" in the “Vgs> Vth” region is the saturation region of the NMOS transistor.

- the drain current Ids in the saturation region is represented by Eq. (3).

- Cox indicates the gate capacitance of the NMOS transistor

- ⁇ n indicates the electron mobility of the NMOS transistor.

- L indicates the gate length of the NMOS transistor, and W indicates the gate width of the NMOS transistor.

- the simulation results using the standard circuit parameters according to the equation (3) are shown in the "saturation region" of FIGS. 3 (a) and 3 (b).

- the drain current Ids flows.

- the drain current Ids is saturated to a substantially constant value in the saturation region. That is, in the saturation region, the drain current Ids does not depend on the drain-source voltage Vds.

- the region basically used in an NMOS transistor is the saturation region.

- the region represented by "Vds ⁇ Vgs-Vth" in the “Vgs> Vth” region is the linear region of the NMOS transistor.

- the drain current Ids in the linear region is represented by Eq. (4).

- the "linear region” in FIG. 3 (b) shows the simulation results using the standard circuit parameters according to the equation (4). As shown in FIG. 3B, in the “linear region”, the drain current Ids changes linearly with respect to the drain-source voltage Vds.

- the Ids-Vds characteristics can be linearly approximated, so that an NMOS transistor can be easily used as a MOS resistor as a preferable example.

- the drain current Ids can be controlled by the gate-source voltage Vgs.

- FIGS. 4 (a) and 4 (b) show simulation results using standard circuit parameters based on equation (4).

- the drain current Ids increases linearly as the gate-source voltage Vgs increases in the range of several hundred mV. That is, the drain current Ids is proportional to the gate-source voltage Vgs in the range of several hundred mV.

- the resistance value R of the NMOS transistor as the MOS resistance can be expressed as in the equation (6), the resistance value R is inversely proportional to the gate-source voltage Vgs as shown in FIG. 4 (b).

- the MOS resistance by the NMOS transistor can be used as a linear resistance in the linear region in the “Vgs> Vth” region, for example, MOS.

- the current flowing through the resistor is proportional to the gate-source voltage Vgs

- the cutoff frequency fc of the RC filter composed of the MOS resistor is proportional to the gate-source voltage Vgs. That is, the current flowing through the MOS resistor and the cutoff frequency fc of the RC filter can be linearly controlled by Vgs.

- the threshold voltage Vth and electron mobility ⁇ n of the NMOS transistor are temperature dependent.

- the threshold voltage Vth considering the temperature dependence is expressed by the equation (7).

- ⁇ th indicates the temperature coefficient of the threshold voltage Vth.

- Vth_T0 indicates the threshold voltage Vth at the temperature T0. That is, as in the equation (7), the threshold voltage Vth changes from Vth_T0 according to the change from T0 of the temperature with the threshold voltage Vth_T0 obtained as an observed value at an arbitrary temperature T0 as a boundary.

- the electron mobility ⁇ n considering the temperature dependence is expressed by the equation (8).

- ⁇ indicates the temperature coefficient of electron mobility ⁇ n.

- ⁇ n_T0 indicates the electron mobility ⁇ n at the temperature T0. That is, as shown in the equation (8), the electron mobility obtained as an observed value at an arbitrary temperature T0 changes from ⁇ n_T0 in accordance with the change in temperature from T0 with ⁇ n_T0 as a boundary.

- the drain current Ids reflecting the temperature dependence of both the threshold voltage Vth and the electron mobility ⁇ n in the linear region of the NMOS transistor is determined. It is represented by the equation (9).

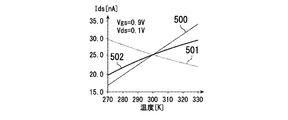

- FIG. 5 is a graph showing the temperature dependence of the drain current Ids in the linear region of the “Vgs> Vth” region of a general NMOS transistor.

- the horizontal axis represents the temperature [K], and the vertical axis represents the drain current Ids [nA].

- Line 502 shows the drain current Ids according to the equation (9) when the temperature dependence of both the electron mobility ⁇ n and the threshold voltage Vth is reflected.

- the drain current is considered only when the temperature dependence of the threshold voltage Vth is considered. Ids increases linearly with increasing temperature. Qualitatively, this is because the threshold voltage Vth decreases as the number of movable charged particles increases with increasing temperature.

- the temperature coefficient ⁇ of the electron mobility ⁇ n in the equations (8) and (9) takes a negative value, only the temperature dependence of the electron mobility ⁇ n is considered as shown by line 501 in FIG. Then, the drain current Ids decreases substantially linearly as the temperature rises. Qualitatively, when the temperature rises, the movement of charged particles is hindered by the thermal vibration of the silicon crystal lattice.

- the drain current Ids reflecting the temperature dependence of the threshold voltage Vth and the drain current Ids reflecting the temperature dependence of the electron mobility ⁇ n can be linearly approximated.

- the drain current Ids that reflect both the temperature dependence of the threshold voltage Vth and the temperature dependence of the electron mobility ⁇ n can also be linearly approximated.

- the drain current Ids increases substantially linearly with increasing temperature.

- the temperature dependence of the threshold voltage Vth has a greater effect on the drain current Ids than the temperature dependence of the electron mobility ⁇ n.

- the influence of the temperature dependence of the threshold voltage Vth is suppressed by the influence of the temperature dependence of the electron mobility ⁇ n.

- the threshold voltage Vth decreases by 85 mV by a temperature rise of 50 degrees. Further, the decrease width (85 mV) of the threshold voltage Vth is narrowed (less than 85 mV) due to the suppression effect due to the temperature dependence of the electron mobility ⁇ n.

- the amount of increase in the drain current Ids when the gate-source voltage Vgs is increased by 100 mV can be linearly approximated.

- the drain current Ids can be reduced by linearly lowering the gate-source voltage Vgs in response to the drain current Ids (line 502 in FIG. 5) that linearly increases as the temperature rises. Temperature dependence can be suppressed. As a result, the temperature dependence of the NMOS transistor as the MOS resistance can be corrected in the linear region of the "Vgs> Vth" region.

- the temperature shown in the equation (2) is set to the reference voltage Vgs0 like the control voltage Vgs shown in the equation (1) applied between the gate and the source of the transistor TN. It can be seen that the temperature dependence of the transistor TN as the MOS resistor MR can be corrected by adding the correction voltage Vc that changes linearly according to T.

- the reference voltage Vgs0 changes linearly according to the temperature T shown in the equation (2), as in the control voltage Vgs shown in the equation (1).

- the correction voltage Vc By adding the correction voltage Vc, the temperature dependence of the transistor TN as a MOS resistor can be corrected. This point will be described with reference to FIGS. 6 (a) and 6 (b).

- FIG. 6 (a) is a graph showing the drain current Ids with respect to the gate-source voltage Vgs in the saturation region in the “Vgs> Vth” region of a general NMOS transistor according to the equation (3).

- the drain current Ids can be linearly approximated in a range of about 100 mV, although there is non-linearity as compared with the linear region of FIG. 4A.

- the drain current Ids in the saturation region of the NMOS transistor reflecting the temperature dependence is represented by the equation (10) based on the equations (3), (7), and (8).

- FIG. 6B is a graph showing the temperature dependence of the drain current Ids in the saturation region of the “Vgs> Vth” region of a general NMOS transistor.

- the horizontal axis represents the temperature [K], and the vertical axis represents the drain current Ids [nA].

- Line 505 shows the drain current Ids according to the equation (10) when the temperature dependence of both the electron mobility ⁇ n and the threshold voltage Vth is reflected.

- the drain reflects both the temperature dependence of the threshold voltage Vth and the temperature dependence of the electron mobility ⁇ n.

- the current Ids can also be linearly approximated.

- the temperature coefficient ⁇ th of the standard threshold voltage Vth is -1.7 mV / K, and due to the effect of suppressing the electron mobility ⁇ n depending on the temperature, the saturation region has the same effect as the linear region.

- the amount of decrease in the threshold voltage Vth with the temperature rise of 50 degrees is less than 85 mV.

- the amount of increase in the drain current Ids when the gate-source voltage Vgs is increased by 100 mV can be linearly approximated.

- the drain current Ids is linearly decreased by linearly lowering the gate-source voltage Vgs in accordance with the drain current Ids (line 505 in FIG. 6B) that increases linearly with the temperature rise.

- the temperature dependence of the current Ids can be suppressed.

- the temperature dependence of the NMOS transistor as the MOS resistance can be corrected in the saturation region in the “Vgs> Vth” region.

- the reference voltage Vgs0 is shown in the equation (2) like the control voltage Vgs shown in the equation (1) applied between the gate and the source of the transistor TN. It can be seen that the temperature dependence of the transistor TN as the MOS resistor MR can be corrected by adding the correction voltage Vc that changes linearly according to the temperature T.

- a correction voltage Vc that changes linearly according to the temperature T shown in the equation (2) is added to the reference voltage Vgs0 like the control voltage Vgs shown in the equation (1) applied between the gate and the source of the transistor TN. Therefore, the temperature dependence of the transistor TN as the MOS resistance MR can be corrected.

- the voltage application circuit 1 is arranged between the gate terminal and the source terminal of the transistor TN.

- the potential of the source terminal (hereinafter, may be referred to as “source potential Vs”) can take any value.

- source potential Vs can take any value.

- the two terminals of the drain terminal and the source terminal of the transistor TN are used as the two terminals at both ends of the MOS resistor MR, they are electrically independent from the ground or ground (0 [V]) ( For example, it is used in a floating state.

- the source potential Vs can take any value.

- the voltage application circuit 1 includes a control voltage application unit 9 and a temperature detection unit 13.

- the temperature detection unit 13 detects the temperature T and outputs a detection signal TM corresponding to the temperature T to the control voltage application unit 9.

- the temperature detection unit 13 detects the temperature T and represents a detection signal TM representing a physical quantity (for example, current or voltage) indicating the temperature T, or a detection representing a physical quantity (for example, current or voltage) correlated with the temperature T.

- the configuration of the temperature detection unit 13 is not particularly limited.

- the temperature detection unit 13 may include a temperature sensor such as a thermistor.

- the temperature detection unit 13 may include a field effect transistor or a bipolar transistor and utilize the temperature-dependent characteristics of the field effect transistor or the bipolar transistor.

- the temperature detection unit 13 may include a PTAT (Proportional To Absolute Temperature) circuit.

- the PTAT circuit outputs a current proportional to the absolute temperature as a detection signal TM.

- the temperature detection unit 13 is configured by a temperature detection circuit that detects the temperature T and outputs the detection signal TM.

- the control voltage application unit 9 applies a control voltage Vgs corresponding to the detection signal TM indicating the temperature T between the gate and the source of the transistor TN. Specifically, the control voltage application unit 9 generates the control voltage Vgs so that the control voltage Vgs includes a correction voltage Vc that changes linearly with respect to the temperature T according to the detection signal TM. Then, the control voltage application unit 9 applies the control voltage Vgs between the gate and the source of the transistor TN. Therefore, according to the first embodiment, the temperature dependence of the resistance value R of the transistor TN can be appropriately reduced according to the detection signal TM indicating the temperature T.

- the control voltage application unit 9 includes a control voltage generation unit 10 and a voltage control voltage source 19. Further, the control voltage generation unit 10 includes a reference voltage generation unit 11, a correction voltage generation unit 15, and an addition unit 17.

- the reference voltage generation unit 11 generates the reference voltage Vgs0 in the equation (1) and outputs the reference voltage Vgs0 to the addition unit 17.

- the correction voltage generation unit 15 generates a correction voltage Vc that changes linearly with respect to the temperature T based on the temperature detection signal TM, and outputs the correction voltage Vc to the addition unit 17.

- the addition unit 17 adds the reference voltage Vgs0 and the correction voltage Vc to generate the control voltage Vgsa which is the addition result. In this way, the control voltage generation unit 10 generates the control voltage Vgsa.

- the control voltage Vgsa may be described as "reference control voltage Vgsa".

- the control voltage Vgsa is represented by the equation (11).

- Vgsa Vgs0 + Vc ... (11)

- the control voltage Vgsa and the control voltage Vgs have the same voltage component (reference voltage Vgs0 and correction voltage Vc) and the same voltage value.

- the correction voltage Vc is represented by the formula (2). As shown in FIG. 2, the correction voltage Vc represented by the formula (2) decreases linearly as the temperature T increases. That is, in the case of the transistor TN, the correction coefficient ⁇ takes a negative value. Then, by changing the correction coefficient ⁇ , the rate of lowering the control voltage Vgsa can be adjusted according to the temperature T.

- the control voltage Vgsa is specifically a voltage based on 0 [V] (that is, a potential difference based on 0 [V]).

- the source potential Vs of the transistor TN can take any value. Therefore, when the control voltage Vgsa is applied directly between the gate and the source, when the source potential Vs of the transistor TN takes an arbitrary value independently of the ground or ground (0 [V]), "Vgsa-Vs" becomes the transistor TN. It becomes the voltage between the gate and the source. As a result, the resistance value R of the transistor TN can change according to the source potential Vs. Therefore, in the first embodiment, the control voltage Vgsa is indirectly applied between the gate and the source of the transistor TN.

- the control voltage application unit 9 has a voltage control voltage source 19.

- the control voltage between the gate and the source of the transistor TN. Vgsa may be applied directly.

- the voltage control voltage source 19 is connected between the gate terminal and the source terminal of the transistor TN.

- the voltage control voltage source 19 has two terminals for input and two terminals for output.

- the voltage control voltage source 19 is a voltage source in which the potential difference between the two output terminals is determined according to the potential difference between the two input terminals.

- the control voltage Vgsa is input as a potential difference by inputting the control voltage Vgsa with reference to 0 [V] and the reference voltage 0 [V] to the voltage control voltage source 19 from the control voltage generation unit 10. Will be done.

- control voltage Vgsa may be input to the voltage control voltage source 19 as a potential difference

- the reference voltage 0 [V] may be set to an arbitrary value. In this case, if the reference voltage is Vref and the output voltage from the control voltage generation unit 10 is "Vgsa + Vref", the potential difference input to the voltage control voltage source 19 becomes Vgsa by "Vgsa + Vref-Vref". ..

- the voltage application circuit 1 of FIG. 1 can apply an arbitrary control voltage Vgs represented by the equation (1) between the gate and the source of the transistor TN.

- the drain current Ids of the MOS resistance MR composed of the transistor TN increases substantially linearly as the temperature T rises (line 502 in FIG. 5 and line 505 in FIG. 6 (b)).

- the correction coefficient ⁇ of the correction voltage Vc (FIG. 2) in the voltage application circuit 1 the voltage application circuit 1 linearly lowers the control voltage Vgs according to the temperature T to reduce the drain current Ids. Decrease linearly.

- the temperature dependence of the drain current Ids can be suppressed. If the temperature dependence of the drain current Ids can be suppressed, the temperature dependence of the physical quantity with respect to the transistor TN can be suppressed.

- FIG. 7A is a circuit diagram showing a first example of the voltage controlled voltage source 19.

- the voltage controlled voltage source 19 according to the first example includes a first switch circuit 191 and a second switch circuit 192, and a capacitor 193.

- the first switch circuit 191 includes terminals t1 to t3.

- the terminal t1 is connected to the control voltage generation unit 10.

- the terminal t2 is connected to the gate terminal of the transistor TN.

- the terminal t3 is connected to one terminal of the capacitor 193.

- the second switch circuit 192 includes terminals t4 to t6.

- the terminal t4 is connected to the control voltage generation unit 10.

- the terminal t5 is connected to the source terminal of the transistor TN.

- the terminal t6 is connected to the other terminal of the capacitor 193.

- the control voltage generation unit 10 generates the control voltage Vgsa.

- the first switch circuit 191 connects the terminal t3 and the terminal t1.

- the second switch circuit 192 connects the terminal t6 and the terminal t4.

- the capacitor 193 holds the control voltage Vgsa.

- the first switch circuit 191 connects the terminal t3 and the terminal t2.

- the second switch circuit 192 connects the terminal t6 and the terminal t5.

- the control voltage Vgsa held in the capacitor 193 is applied as the control voltage Vgs between the gate and the source of the transistor TN.

- FIG. 7B is a circuit diagram showing a second example of the voltage controlled voltage source 19.

- the voltage-controlled voltage source 19 according to the second example further includes an operational amplifier 194 in addition to the configuration of the voltage-controlled voltage source 19 according to the first example.

- the points that the second example differs from the first example will be mainly described.

- the output terminal of the operational amplifier 194 is connected to the node N.

- the node N is located on the line connecting the terminal t2 and the gate terminal of the transistor TN.

- the inverting input terminal of the operational amplifier 194 is connected to the terminal t5.

- the non-inverting input terminal of the operational amplifier 194 is connected to the source terminal of the transistor TN.

- the operation of the voltage controlled voltage source 19 according to the second example is the same as the operation of the voltage controlled voltage source 19 according to the first example.

- the source terminal of the transistor TN is connected to the non-inverting input terminal of the operational amplifier 194

- the influence of the capacitive load of the gate terminal and the source terminal of the transistor TN can be reduced as compared with the first example. ..

- the configuration of the voltage-controlled voltage source 19 is not particularly limited as long as the voltage-controlled voltage source 19 can be inserted between any two terminals that are electrically floating.

- control voltage generation unit 10 is not particularly limited as long as the control voltage Vgsa represented by the equation (11) can be generated, and can be configured by an arbitrary control voltage generation circuit.

- FIG. 1 shows the physical or logical configuration of the control voltage generation unit 10. Therefore, when FIG. 1 shows the physical configuration of the control voltage generation unit 10, for example, the reference voltage generation unit 11 is configured by the reference voltage generation circuit that generates the reference voltage Vgs0, and the correction voltage generation unit 15 is The correction voltage generation circuit that generates the correction voltage Vc based on the detection signal TM of the temperature detection unit 13 is configured, and the addition unit 17 is composed of an addition circuit that adds the correction voltage Vc to the reference voltage Vgs0.

- FIG. 1 shows the logical configuration of the control voltage generation unit 10, for example, when the reference voltage generation unit 11, the correction voltage generation unit 15, and the addition unit 17 are not clearly distinguished as a physical configuration.

- the control voltage generation unit 10 generates the control voltage Vgsa represented by the equation (11), the circuit constituting the control voltage generation unit 10 is not particularly limited.

- FIG. 1 shows the physical or logical configuration of the temperature detection unit 13 and the correction voltage generation unit 15. Therefore, when the temperature detection unit 13 and the correction voltage generation unit 15 represent a logical configuration, for example, the temperature detection unit 13 and the correction voltage generation unit 15 are not clearly distinguished as a physical configuration. Is not particularly limited as long as the correction voltage Vc represented by the equation (2) can be generated, and can be configured by any temperature detection circuit and correction voltage generation circuit.

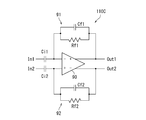

- FIG. 8 is a circuit diagram showing an example of the temperature detection unit 13 and the correction voltage generation unit 15.

- the temperature detection unit 13 and the correction voltage generation unit 15 include a first current source circuit 131, a second current source circuit 133, and a variable resistor Ro.

- the first current source circuit 131 and the second current source circuit 133 are connected in series between the first power supply line PL1 and the second power supply line PL2.

- One terminal of the variable resistor Ro is connected to the node Nc between the first current source circuit 131 and the second current source circuit 133.

- the other terminal of the variable resistor Ro is grounded.

- the potential of the first power supply line PL1 takes a positive value, and for example, the first power supply line PL1 is connected to a positive power supply that supplies a positive power supply voltage.

- the potential of the second power supply line PL2 takes a negative value, and for example, the second power supply line PL2 is connected to a negative power supply that supplies a negative power supply voltage.

- the first current source circuit 131 generates the first current Ip.

- the second current source circuit 133 generates a second current Im.

- a differential current Io flows through the variable resistor Ro.

- the differential current Io is a current indicating the difference between the first current Ip and the second current Im.

- a potential difference Vc is generated between both ends of the variable resistor Ro.

- the temperature detection unit 13 and the correction voltage generation unit 15 are not clearly distinguished, but the temperature dependence between the first current source circuit 131 and the second current source circuit 133 is used for temperature detection.

- a graph showing the temperature dependence of the first current Ip and the second current Im is shown in FIG. 9A.

- the horizontal axis is the temperature T [K]

- the vertical axis is the current value I [A] of each current source circuit.

- each of the first current Ip and the second current Im changes linearly with the change of the temperature T.

- the temperature dependence of the first current Ip and the temperature dependence of the second current Im are different. That is, the temperature dependence of the first current source circuit 131 of the temperature detection unit 13 and the temperature dependence of the second current source circuit 133 are different.

- the temperature dependence of the first current Ip is lower than the temperature dependence of the second current Im. That is, the temperature dependence of the first current source circuit 131 is lower than the temperature dependence of the second current source circuit 133.

- the horizontal axis is the temperature T [K]

- the vertical axis is the differential current value Io [A].

- the differential current Io has a negative temperature characteristic. That is, the slope A of the straight line representing the differential current Io has a negative value. Further, in FIG.

- the differential current Io is represented by the equation (12).

- the first current source circuit 131 and the second current source circuit 133 connected in series constitute the temperature detection unit 13 in FIG. 1.

- the differential current Io may be considered as the detection signal TM of the temperature detection unit 13 in FIG.

- the correction voltage Vc when the differential current Io is input to the variable resistor Ro is expressed by the equation (13).

- a graph showing the temperature dependence of the correction voltage Vc is shown in FIG. 9 (c).

- the horizontal axis is the temperature T [K]

- the vertical axis is the correction voltage Vc [V]. Since the differential current Io has a negative temperature characteristic, the correction voltage Vc also has a negative temperature characteristic as shown in FIG. 9C. That is, it matches the graph of the temperature dependence of the correction voltage Vc shown in FIG. Further, when the temperature is the first temperature T1, the correction voltage Vc becomes zero as shown in FIG. 9C.

- the correction coefficient ⁇ is “Ro ⁇ A” as shown in the equation (13), and takes a negative value like the slope A in the equation (12). Then, when it is desired to change the correction coefficient ⁇ , it can be seen that the variable resistor Ro should be changed.

- the variable resistor Ro may be considered as the correction voltage generation unit 15 in FIG. Further, as is clear from the equation (13), the correction voltage Vc has a value based on the differential current Io.

- the first temperature T1 at which the differential current Io and the correction voltage Vc become zero can be changed by the following method.

- a method of changing the first temperature T1 shown in the formulas (2), (12) and (13) will be described with reference to FIGS. 8 and 10 (a) to 10 (c).

- FIG. 10A shows a graph showing the temperature dependence of the first current Ip and the second current Im when the current value of the first current Ip is changed.

- the temperature at which the first current Ip and the second current Im are equal is the first temperature T1. Therefore, as the current value of the first current Ip increases, so does the first temperature T1. That is, the first temperature T1 can be changed by the first current source circuit 131 changing the current value of the first current Ip.

- the first temperature T1 can also be changed by changing the current value of the second current Im by the second current source circuit 133.

- FIG. 10B shows a graph showing the temperature dependence of the first current Ip and the second current Im when the current value of the second current Im is changed. However, as shown in FIG. 10B, when the current value of the second current Im increases, the first temperature T1 decreases.

- FIG. 10C shows a graph showing the temperature dependence of the differential current Io when the current value of the differential current Io is changed.

- the temperature T is such that the differential current Io becomes zero.

- the first temperature T1 also increases.

- the correction voltage Vc also becomes zero.

- the first current source circuit 131 and the second current source circuit 133 are provided, the first current Ip and / or the second current Im is changed, and the differential current Io is set.

- the first temperature T1 which is the temperature T when the correction voltage Vc becomes zero, can be easily changed.

- the second power supply line PL2 may be grounded.

- one terminal of the variable resistor Ro is connected to the node Nc, and the other terminal of the variable resistor Ro is connected to a reference voltage source that generates a reference voltage Vref (0 ⁇ Vref ⁇ PL1 potential).

- Vref reference voltage

- the slopes of the straight lines representing the first current Ip and the second current Im are both positive values, but they do not necessarily have to be positive values.

- the slope of the second current Im may be larger than the slope of the first current Ip. , The sign of the slope is irrelevant.

- the temperature dependence of the transistor TN can be corrected by appropriately setting the correction coefficient ⁇ of the correction voltage Vc according to the configuration of the resistance device 100 according to the first embodiment shown in FIG.

- the drain current Ids of the transistor TN in the linear region (Vds ⁇ Vgs-Vth) in the “Vgs> Vth” region Is expressed by the equation (14) reflecting the correction coefficient ⁇ .

- the drain current Ids of the transistor TN can be changed in the saturation region (Vds> Vgs-Vth) in the “Vgs> Vth” region. It is expressed by the equation (15) reflecting the correction coefficient ⁇ .

- FIG. 11A is a graph showing the relationship between the correction coefficient ⁇ and the resistance value R of the transistor TN at a plurality of different temperatures.

- the horizontal axis represents the correction coefficient ⁇

- the vertical axis represents the resistance value R [M ⁇ ].

- the reference voltage Vgs0 is 0.9V, and the drain-source voltage Vds is 1.8V.

- the gradients of the R- ⁇ curves G10 to G16 are different from each other depending on the temperature T.

- the R- ⁇ curves G10 to G16 intersect at almost one point P.

- the resistance value R of the transistor TN is substantially independent of the temperature T.

- the correction coefficient ⁇ (Rp) is set.

- the temperature dependence of the transistor TN can be offset by the correction voltage Vc including).

- the resistance value R of the transistor TN can be reduced.

- the resistance value R of the transistor TN can be maintained substantially constant with respect to fluctuations in the temperature T.

- the fact that the resistance value R is substantially independent of temperature may be described as “independent of temperature” or “independent of temperature”.

- the correction coefficient ⁇ (Rp) at least two R- ⁇ curves may be calculated. As can be understood from the equations (15) and (16), when the reference voltage Vgs0 changes, the R- ⁇ curve also changes. Therefore, when the reference voltage Vgs0 changes, the position of the intersection P changes. As a result, when the reference voltage Vgs0 changes, the correction coefficient ⁇ (Rp) also changes.

- the resistance value R of the transistor TN of the resistor device 100 shown in FIG. 1 is actually measured while changing the correction coefficient ⁇ , and an R- ⁇ curve of 2 or more is obtained. Then, the correction coefficient ⁇ (Rp) at the intersection P of two or more R- ⁇ curves is acquired. Further, the correction coefficient ⁇ (Rp) is set to the correction coefficient ⁇ of the correction voltage generation unit 15 of the resistance device 100. In particular, since the R- ⁇ curve is actually measured, the correction coefficient ⁇ (Rp) suitable for the transistor TN actually used can be determined. As a result, the temperature dependence of the resistance value R of the transistor TN can be further reduced.

- the temperature T indicates the ambient temperature of the resistance device 100, for example, the resistance device 100 is arranged in a constant temperature bath, and the temperature T is set by the constant temperature bath.

- the correction coefficient ⁇ (Rp) when the resistance value R does not depend on the temperature T is based on the intersection of the R- ⁇ curves G10 to G16. ) Can be obtained.

- FIG. 12A is a graph showing R- ⁇ curves G21 and G22 showing the resistance value R of the transistor TN with respect to the correction coefficient ⁇ at any two different temperatures T11 and T12, respectively.

- the horizontal axis represents the correction coefficient ⁇

- the vertical axis represents the resistance value R.

- the resistance value R of the transistor TN of the resistance device 100 is measured while changing the correction coefficient ⁇ , and the two R- ⁇ curves G21 and G22 are obtained. Then, the correction coefficient ⁇ (Rr) is acquired from the intersection P of the two R- ⁇ curves G21 and G22.

- the resistance value R when the correction coefficient ⁇ is the correction coefficient ⁇ (Rr) is a resistance value Rr having no temperature dependence. Therefore, when the correction coefficient ⁇ (Rr) is set to the correction coefficient ⁇ of the correction voltage generation unit 15 of the resistance device 100, the temperature dependence of the resistance value R of the transistor TN can be effectively reduced by the correction voltage Vc. As a result, the resistance value R of the transistor TN can be maintained at the resistance value Rr.

- the resistance value Rr having no temperature dependence at the intersection P and the desired resistance value Rd (hereinafter, may be referred to as "target resistance value Rd") basically do not match. This is because, as shown in FIG. 12A, the resistance value R of the transistor TN at arbitrary temperatures T11 and T12 fluctuates according to the correction coefficient ⁇ . Therefore, at the time of obtaining the R- ⁇ curve at each temperature, the intersection point P It is unknown what kind of resistance value Rr will be.

- the resistance value R with respect to the correction coefficient ⁇ is measured at two different temperatures while changing the reference voltage Vgs0, and R-with respect to the reference voltage Vgs0. It is required to repeatedly search for the intersection of the ⁇ curves until the resistance value Rr and the target resistance value Rd at the intersection match.

- the temperature T of 320K corresponds to the first temperature T1.

- FIG. 12B shows an R- ⁇ curve G31 showing the resistance value R of the transistor TN with respect to the correction coefficient ⁇ at the first temperature T1 and R showing the resistance value R of the transistor TN with respect to the correction coefficient ⁇ at the second temperature T2. It is a graph which showed the relationship with - ⁇ curve G32.

- the horizontal axis represents the correction coefficient ⁇

- the vertical axis represents the resistance value R.

- the second temperature T2 is different from the first temperature T1.

- the R- ⁇ curve G31 shows the resistance value R of the transistor TN at the first temperature T1.

- the first temperature T1 indicates the temperature when the physical quantity with respect to the transistor TN is substantially constant with respect to the change in the correction coefficient ⁇ .

- the first temperature T1 indicates the temperature when the resistance value R of the transistor TN is substantially constant with respect to the change of the correction coefficient ⁇ . That is, the first temperature T1 is the temperature at which the correction voltage Vc becomes zero.

- the resistance value R is a resistance value Rr having no temperature dependence.

- the resistance value R of the resistance device 100 is actually measured while changing the reference voltage Vgs0, and the resistance value R becomes the target resistance value Rd.

- the reference voltage Vgs0 (Rd) is obtained.

- the reference voltage Vgs0 is set to the reference voltage Vgs0 (Rd)

- the temperature T is set to the second temperature T2 different from the first temperature T1

- the resistance value R is changed while changing the correction coefficient ⁇ .

- the R- ⁇ curve G32 is obtained by actually measuring.

- the R- ⁇ curve G32 shows the resistance value R of the transistor TN at the second temperature T2.

- the correction coefficient ⁇ (Rr) at the intersection P of the R- ⁇ curve G31 at the first temperature T1 and the R- ⁇ curve G32 at the second temperature T2 is acquired.

- the temperature-independent resistance value Rr corresponding to the correction coefficient ⁇ (Rr) always matches the target resistance value Rd.

- the correction coefficient ⁇ (Rr) at the intersection P also coincides with the correction coefficient ⁇ (Rd) with respect to the target resistance value Rd. Therefore, according to the first embodiment, when the correction coefficient ⁇ (Rd) is set to the correction coefficient ⁇ of the correction voltage generation unit 15 of the resistance device 100, the temperature dependence of the resistance value R of the transistor TN is effective depending on the correction voltage Vc. The resistance value R of the transistor TN can be maintained at the target resistance value Rd.

- the second temperature T2 is set to a value near the temperature at which the transistor TN is actually used to obtain the correction coefficient ⁇ (Rd).

- the second temperature T2 is set to 310K, which is a value near the human body temperature

- the first temperature T1 is set to the first temperature. 2 Set to 320K, which is a value near the temperature T2.

- the intersection of the R- ⁇ curve G11 corresponding to the first temperature T1 of 320K and the R- ⁇ curve G12 corresponding to the second temperature T2 of 310K is corrected.

- the coefficient ⁇ (Rp) is ⁇ 0.00115.

- the correction coefficient ⁇ (Rp) was set to ⁇ 0.00115, and the resistance value R of the transistor TN was calculated from the equations (15) and (16).

- FIG. 11B is a graph showing the effect of temperature correction on the temperature dependence of the resistance value R of the transistor TN.

- the curve 506 shows the case where the temperature correction is not performed, and the curve 507 shows the case where the temperature correction is performed.

- the horizontal axis represents the temperature T [K], and the vertical axis represents the resistance value R [M ⁇ ].

- the correction coefficient ⁇ of the equation (15) was set to zero, the resistance value R was calculated from the equation (16), and the curve 506 was plotted.

- the temperature dependence of the resistance value R is strong when the correction is not performed.

- the correction coefficient ⁇ of the equation (15) is set to ⁇ 0.00115 of the correction coefficient ⁇ (Rp) obtained from FIG. 11 (a), and the equation (16) is used.

- the resistance value R was calculated and the curve 507 was plotted.

- the resistance value R is substantially constant and indicates a value Rp. That is, the temperature dependence of the resistance value R of the transistor TN can be strongly suppressed by the correction based on the correction coefficient ⁇ (Rp).

- the reference voltage Vgs0 described with reference to FIG. 12A is changed.

- the first temperature T1 that does not depend on the correction coefficient ⁇ described with reference to FIG. 12 (b).

- the combination can be determined at a higher speed when it is uniquely determined by the intersection P of the R- ⁇ curve in the above and the R- ⁇ curve at the second temperature T2 different from the first temperature T1.

- a voltage application circuit 1 having a correction voltage generation unit 15 that generates such a correction voltage Vc is suitable.

- the target resistance value Rd corresponds to an example of "target physical quantity related to field effect transistor". That is, the target resistance value Rd is a resistance value of the field effect transistor TN that can be measured from an electronic circuit including the field effect transistor TN, and indicates a resistance value set as the target value.

- the horizontal axis represents the reference voltage Vgs0 [V].

- the horizontal axis represents the correction coefficient ⁇ .

- the vertical axis represents the resistance value R [M ⁇ ].

- the correction coefficient ⁇ is determined by (Procedure 1) and (Procedure 2) shown below.

- the resistance device 100 is placed in a constant temperature bath, and the ambient temperature of the resistance device 100 is set to the first temperature T1 by the constant temperature bath.

- the resistance value R is measured while changing the voltage value of the reference voltage Vgs0.

- the reference voltage Vgs0 (Rd) when the resistance value R indicates the target resistance value Rd is determined.

- the resistance value R of the transistor TN becomes the target resistance value Rd (40 M ⁇ in the example of FIG. 13 (b)) at the second temperature T2 and the reference voltage Vgs0 (Rd).

- the correction coefficient ⁇ (Rd) at the time of becoming is determined.

- the resistance device 100 is placed in a constant temperature bath, and the ambient temperature of the resistance device 100 is set to the second temperature T2 by the constant temperature bath.

- the reference voltage Vgs0 is set to the reference voltage Vgs0 (Rd) determined in (Procedure 1).

- the resistance value R is measured while changing the value of the correction coefficient ⁇ .

- the correction coefficient ⁇ (Rd) when the resistance value R indicates the target resistance value Rd is determined.

- Executing means that in FIG. 12B, the correction coefficient ⁇ at the intersection P of the R- ⁇ curve G31 at the first temperature T1 and the R- ⁇ curve G32 at the second temperature T2 ( Corresponds to acquiring Rd).