KR940001885B1 - 선택적 화학증착법(化學法, cvd법) 및 동법을 사용한 cvd장치 - Google Patents

선택적 화학증착법(化學法, cvd법) 및 동법을 사용한 cvd장치 Download PDFInfo

- Publication number

- KR940001885B1 KR940001885B1 KR1019900005518A KR900005518A KR940001885B1 KR 940001885 B1 KR940001885 B1 KR 940001885B1 KR 1019900005518 A KR1019900005518 A KR 1019900005518A KR 900005518 A KR900005518 A KR 900005518A KR 940001885 B1 KR940001885 B1 KR 940001885B1

- Authority

- KR

- South Korea

- Prior art keywords

- gas

- film

- wafer

- pressure

- reaction chamber

- Prior art date

Links

- 238000005229 chemical vapour deposition Methods 0.000 title claims description 71

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 title claims description 65

- 229910052710 silicon Inorganic materials 0.000 title claims description 65

- 239000010703 silicon Substances 0.000 title claims description 65

- 229910021341 titanium silicide Inorganic materials 0.000 claims description 63

- 238000006243 chemical reaction Methods 0.000 claims description 47

- 238000010926 purge Methods 0.000 claims description 41

- 238000000034 method Methods 0.000 claims description 39

- 229910052751 metal Inorganic materials 0.000 claims description 36

- 239000002184 metal Substances 0.000 claims description 36

- 239000000758 substrate Substances 0.000 claims description 32

- 238000010438 heat treatment Methods 0.000 claims description 28

- XJDNKRIXUMDJCW-UHFFFAOYSA-J titanium tetrachloride Chemical compound Cl[Ti](Cl)(Cl)Cl XJDNKRIXUMDJCW-UHFFFAOYSA-J 0.000 claims description 23

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 claims description 17

- 230000009467 reduction Effects 0.000 claims description 17

- 229910000077 silane Inorganic materials 0.000 claims description 14

- 239000000460 chlorine Substances 0.000 claims description 13

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 claims description 11

- 229910052801 chlorine Inorganic materials 0.000 claims description 11

- 239000012212 insulator Substances 0.000 claims description 8

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 claims description 4

- 239000000203 mixture Substances 0.000 claims description 3

- 229910052990 silicon hydride Inorganic materials 0.000 claims description 3

- 150000004756 silanes Chemical class 0.000 claims 2

- 230000004888 barrier function Effects 0.000 claims 1

- 238000001514 detection method Methods 0.000 claims 1

- 238000005192 partition Methods 0.000 claims 1

- 239000007789 gas Substances 0.000 description 181

- 235000012431 wafers Nutrition 0.000 description 117

- 239000010408 film Substances 0.000 description 109

- 239000010409 thin film Substances 0.000 description 47

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 26

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 15

- 238000002474 experimental method Methods 0.000 description 13

- 230000007246 mechanism Effects 0.000 description 13

- 230000000694 effects Effects 0.000 description 12

- 239000000463 material Substances 0.000 description 10

- 229910021332 silicide Inorganic materials 0.000 description 7

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 7

- 238000012545 processing Methods 0.000 description 6

- 230000008859 change Effects 0.000 description 5

- 239000004065 semiconductor Substances 0.000 description 5

- 238000010306 acid treatment Methods 0.000 description 4

- 238000004140 cleaning Methods 0.000 description 4

- 230000003647 oxidation Effects 0.000 description 4

- 238000007254 oxidation reaction Methods 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 238000004544 sputter deposition Methods 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 3

- 230000003749 cleanliness Effects 0.000 description 3

- 238000011109 contamination Methods 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 238000003475 lamination Methods 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 230000001603 reducing effect Effects 0.000 description 3

- 238000000427 thin-film deposition Methods 0.000 description 3

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 238000011068 loading method Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000008018 melting Effects 0.000 description 2

- 238000002844 melting Methods 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 230000006911 nucleation Effects 0.000 description 2

- 238000010899 nucleation Methods 0.000 description 2

- 238000013021 overheating Methods 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 238000003672 processing method Methods 0.000 description 2

- 238000000746 purification Methods 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 238000011946 reduction process Methods 0.000 description 2

- 238000011160 research Methods 0.000 description 2

- 239000000523 sample Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- IKOKHHBZFDFMJW-UHFFFAOYSA-N 2-[4-[2-(2,3-dihydro-1H-inden-2-ylamino)pyrimidin-5-yl]-3-(2-morpholin-4-ylethoxy)pyrazol-1-yl]-1-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)ethanone Chemical compound C1C(CC2=CC=CC=C12)NC1=NC=C(C=N1)C=1C(=NN(C=1)CC(=O)N1CC2=C(CC1)NN=N2)OCCN1CCOCC1 IKOKHHBZFDFMJW-UHFFFAOYSA-N 0.000 description 1

- VEXZGXHMUGYJMC-UHFFFAOYSA-M Chloride anion Chemical compound [Cl-] VEXZGXHMUGYJMC-UHFFFAOYSA-M 0.000 description 1

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 229910008486 TiSix Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 238000002441 X-ray diffraction Methods 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000001816 cooling Methods 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 238000002003 electron diffraction Methods 0.000 description 1

- 238000013213 extrapolation Methods 0.000 description 1

- 230000009970 fire resistant effect Effects 0.000 description 1

- -1 for example Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000005484 gravity Effects 0.000 description 1

- 230000003760 hair shine Effects 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 229910000041 hydrogen chloride Inorganic materials 0.000 description 1

- IXCSERBJSXMMFS-UHFFFAOYSA-N hydrogen chloride Substances Cl.Cl IXCSERBJSXMMFS-UHFFFAOYSA-N 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 230000006698 induction Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 210000004185 liver Anatomy 0.000 description 1

- 238000003754 machining Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- PDKHNCYLMVRIFV-UHFFFAOYSA-H molybdenum;hexachloride Chemical compound [Cl-].[Cl-].[Cl-].[Cl-].[Cl-].[Cl-].[Mo] PDKHNCYLMVRIFV-UHFFFAOYSA-H 0.000 description 1

- 239000012071 phase Substances 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 239000012495 reaction gas Substances 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- OEIMLTQPLAGXMX-UHFFFAOYSA-I tantalum(v) chloride Chemical compound Cl[Ta](Cl)(Cl)(Cl)Cl OEIMLTQPLAGXMX-UHFFFAOYSA-I 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- SQBBHCOIQXKPHL-UHFFFAOYSA-N tributylalumane Chemical compound CCCC[Al](CCCC)CCCC SQBBHCOIQXKPHL-UHFFFAOYSA-N 0.000 description 1

- KPGXUAIFQMJJFB-UHFFFAOYSA-H tungsten hexachloride Chemical compound Cl[W](Cl)(Cl)(Cl)(Cl)Cl KPGXUAIFQMJJFB-UHFFFAOYSA-H 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

Images

Classifications

-

- H01L21/205—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28556—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table by chemical means, e.g. CVD, LPCVD, PECVD, laser CVD

- H01L21/28562—Selective deposition

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/02—Pretreatment of the material to be coated

- C23C16/0227—Pretreatment of the material to be coated by cleaning or etching

- C23C16/0236—Pretreatment of the material to be coated by cleaning or etching by etching with a reactive gas

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

- H01L21/76879—Filling of holes, grooves or trenches, e.g. vias, with conductive material by selective deposition of conductive material in the vias, e.g. selective C.V.D. on semiconductor material, plating

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Electrodes Of Semiconductors (AREA)

- Chemical Vapour Deposition (AREA)

Abstract

내용 없음.

Description

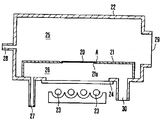

제1도는 본 발명에 따른 CVD법을 응용한 CVD장치의 실시예를 나타낸 단면도.

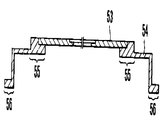

제2도는 제1도에 나타낸 웨이퍼 서셉터(wafer susceptor)의 변형예를 나타내는 단면도.

제3a도∼제3c도는 본 발명에 따른 홀(hole)바닥에서의 티탄(titanium) 실리사이드(silicide)막 형성법을 보여 주는 단면도.

제4도는 웨이퍼 서셉터의 또다른 변형에를 나타내는 단면도.

제5도는 본 발명에 따른 CVD법을 응용한 CVD장치의 또다른 실시예를 나타낸 단면도.

제6도는 티타늄 테트라클로라이드 가스 미세 유동제어기구(fine-flow control mechanism)를 포함하는 제4도에 나타낸 CVD장치의 변형예를 나타내는 계략도.

제7도는 종래기술에 의한 CVD장치의 구조를 나타내는 단면도.

본 발명은 선택적 화학증착법(selective chemical vapor deposition method) 및 동법을 이용한 CVD장치에 관한 것이다.

실리콘 기판을 사용하는 반도체 소자(素子)의 제조공정에 있어서, 배선(配線)금속과 고농도의 불순물로 처리한 실리콘층사이에 옴(ohm)접촉에 대한 접촉저항을 감소시키거나, 배선금속과 실리콘간의 고형화(固型化) 반응을 막기위해 배선금속과 실리콘층간에 실리사이드 박막을 형성시키는 방법이 시도되어 왔다.

또한, 고농도 실리콘층의 판저항(sheet resistance)을 감소시키기 위해 고농도 실리콘위에 실리사이드 박막을 형성시키는 방법이 시도되었다.

낮은 저항성을 갖는 티탄 실리사이드 박막이 이러한 용도에 적합하다. 실리콘 표면에 실리사이드 박막을 형성시키는 종래의 방법들은 실리사이드 전극을 이용한 스퍼터링(sputtering)으로 실리사이드 박막을 부착시키는 방법과 금속 전극을 이용한 스퍼터링으로 실리콘 표면에 금속막을 부착시키는 방법이 있고, 이 금속과 실리콘은 열처리에 의해 실리사이드 박막을 형성한다. 그러나 이런 스퍼터링은 빈약한 피복률(coverage)을 가진다.

따라서, 예를들어 컨택트 홀과 같이 패턴 크기가 작아지면 막은 균일하게 부착되지 않는다. 이런 이유로 스퍼터링법 대신 우수한 피복률로 금속막을 형성할 수 있는 박막 형성법의 필요성이 대두되었다.

이러한 CVD(화학증착법)법에서는 가열된 금속 표면 위에서 소스가스(source gas)가 분해되므로, 컨택트홀의 바닥까지도 박막이 균일하게 형성된다.

이러한 CVD법에서는, 기판의 전 표면에 박막이 균일하게 부착되는 블랭킷 CVD법(blanket CVD method)이 일반적으로 사용되고 있다. 그러나 최근에는 특정재료의 표면에만 박막이 부착되는 선택적 CVD법이 몇몇 물질에 대하여 개발되어 왔다.

이 선택적 CVD법은 고농축 실리콘층의 표면에 티탄 실리사이드 박막을 형성하기 위해 가장 적절하게 사용되고 있다.

선택적 티탄 실리사이드 박막 CVD법은 보트빌(Bouteville)등[전기화학 학회저널 : 고체과학 및 기술. 134권, 제8호, (1987년간) 2080페이지(Journal of Electrochemical Society : SOLID-STATE SCIENCE AND TECHNOLOGY. Vol. 134, No.8,(1987) 2080]과 아일드렘(Ilderem)등[응용물리학지, 53권, 제8호, (1988년간) 688페이지(Applied Physics Letters, Vol. 53, No.8, (1988) 688]에 보고되었다.

그러나 보트빌등에 의해 보고된 방법에 따르면, 수소(H2)가스와 사염화티탄가스(TiCl4)가 소스가스로 쓰이고, 티탄 실리사이드를 만들기 위한 실리콘이 기판의 실리콘으로부터 공급되므로 티탄 실리사이드 박막은 실리콘 기판을 크게 소모한다.

더우기, 이 방법은 박막 성장이 핵으로 시작되는, 즉, 명백한 핵반응(nucleation)의 문제를 가지고 있다.

반면에, 아일드렘등에 의해 보고된 방법에 따르며, 티탄 실리사이드 박막은 실리콘 표면에 직접 선택적으로 부착되지는 않지만, 폴리실리콘 박막은 티탄 실리사이드 박막이 부착되기전에 전 표면에 성장되고, 그후 티탄 실리사이드 박막이 부착된다. 절연필름(insulation film)상의 폴리실리콘은 티탄 실리사이드 박막이 부착되는 동안 부식(ething)되어 제거된다.

이 방법을 사용하여, 매끄러운 표면을 가진 얇은 티탄 실리사이드 박막을 얻었지만, 완전한 선택성을 얻은 것이 아니라, 폴리실리콘이나, 티탄 실리사이드가 절연박막에 남아있다.

그것들은 소스가스로써 TiCl4가스와 실란(SiH4)가스를 사용했지만 밑에 있는 기판 실리콘의 소모를 감소시키지는 못했다.

본 발명가들에 의해 시행된 아일드렘등의 방법을 사용한 유사한 실험에 따르면, 티탄 실리사이드 박막 부착기간이 절연필름상의 잔류물을 감소시키기 위해 연장되었을때, 실리콘위에 부착된 티탄 실리사이드 박막은 밑에 있는 기판 실리콘을 크게 소모한다. 그 결과, 소모량은 티탄 실리사이드 박막 두께의 100%나 그 이상이 되었다.

선택적 CVD법이 표면 특성간의 차이에 의해 선택성을 갖고 있으므로, 박막 부착 조건은 박막 부착(반도체 혹은 도체)을 할 재료(반도체 또는 도체)의 표면상태에 의해 크게 영향을 받는다.

즉, 표면 청결도가 낮다면, 선택적 성장의 특성들은 아무런 박막도 부착되지 않거나, 덩어리로 거칠게 부착되거나, 심한 기복이 있는 박막이 부착되는 등의 문제점이 되는 나쁜 결과로 영향을 미친다. 그런 까닭에 균일한 박막의 부착이 어렵게 된다.

특히 박막을 부착시키기 위한 표면이 실리콘일때, 만약 실리콘이 산소나 수분을 함유한 대기에 노출이 된다면 자연산화막이 즉시 실리콘 표면에 형성된다. 따라서, 균일성 및 선택성이 양호한 박막의 부착이 어렵게 된다.

즉, 실리콘 표면을 가진 기판일지라도 묽은 불산에 담그어 표면의 자연산화막을 제저한 후, 즉시 CVD장치에 장진시켜 진공이나 공지치환을 실시하여도, 실리콘 표면의 산화를 막을수는 없다. 또한, 실리콘 표면의 산화막을 제거하고, 실리콘 표면이 공기에 노출되지 않도록 하여도, 실리콘 표면은 진공이나 가스중의 소량의 수분이나 산소에 의해 산화된다. 티탄 실리사이드 박막 CVD법에 대해 많지 않은 실험이 시행되어 왔다. 그 한가지 이유는 이 목적을 위한 적당한 CVD장치가 개발되지 않았다는 것이다.

티탄 실리사이드 박막 CVD에 있어서, TiCl4가스는 소스가스로써 가장 손쉽게 사용되고 있다. 그러나, TiCl4가스를 사용하여 실리콘상에서 낮은 저항성을 갖는 티탄 실리사이드 박막을 부착시키기 위해서는, 실리콘 기판은 650℃ 또는 그 이상의 고온으로 가열되어야 한다. 또한 우수한 선택성을 얻기 위해서는 콜드월 타입(Cold wall type)의 장치가 사용되어야만 한다.

게다가, 증기상 반응을 제거하고 적절한 성장률을 얻기위해, 소스가스압은 가스유동(gas flow)이 분자유동(molecular flow)으로 바뀌는 저압까지 저하되어야 한다.

티탄 실리사이드 박막이 금속막이므로 유도로(爐)(induction furnace)등은 기판을 가열하기 위해 사용할 수 없다. 또한, 티탄 실리사이드 박막이 빛을 전이하는 것이 아니라 흡수하므로, 단순 램프가열법 등은 사용할 수 없다. TiCl2가스의 분해에 의해 생성된 염소나 염화물은 부식성 가스로, 금속과 같은 것을 부식한다.

이러한 문제점들이 티탄 실리사이드 박막의 CVD 시행을 가능케하는 기구의 발전을 방해하였다.

하기의 장치는 종래의 금속박막 CVD장치의 예가 될 수 있다. 이 CVD장치는 주로 텅스텐(W)의 선택적 CVD를 위해 개발된 것이다.

그 결과, 종래의 콜드월 타입의 단일 웨이퍼 가공장치내에서 웨이퍼 온도를 400℃ 이상으로 가열하여 CVD를 실행하기 위해 종래의 램프가열 타입(lamp heating type) CVD장치의 결점인 창문의 흐림을 방지 할 수 있는 CVD법이 제안되었다.(일본특허 공개 공보 제63-26366호).

제7도에 나타낸 것처럼, 반응실(10)내에 배설된 서셉터(17)에 의해 고정된 웨이퍼(11)를 창(12)을 통해서 램프히터(13)로 가열하고, 소스가스(14)를 도입하여 웨이퍼(11)의 표면에 막을 성장시킬때, 퍼지가스가 퍼지가스유동(16)(purge gas flow)을 형성하기 위해 창(12)과 웨이퍼(11)사이에 설치된 퍼지가스공급부(15)로부터 공급되어진다.

퍼지가스유동(16)은 퍼지가스공급부(15)의 표면을 덮으므로서, 그 결과 소스가스는 퍼지가스공급부(15)나 창(12)의 표면에 접촉되지 않게하여, 그로인해 그들 표면의 흐림이 방지된다.

이 CVD장치 및 방법에 의하면, 콜드월 타입의 장치를 사용하더라도 소스가스의 존재하에서 웨이퍼를 고온으로 가열하여 비교적 높은 재현성이 좋게 CVD를 실행할 수 있다. 그러나, 퍼지가스유동을 이용하여 창의 흐림을 방지하는 상기의 CVD법은 반응실내에서 가스유동이 점성유동(viscous flow)으로 되는 비교적 높은 가스(소스가스+퍼지가스)압 범위내에서만 사용될 수 있다.

가스유동이 분자유동이 되는 낮은 가스압 범위내에서는, 소스 및 퍼지가스들은 서로가 순간적으로 혼합되기 때문에, 소스가스는 퍼지가스공급부(15)나 창(12)의 표면에 접촉된다. 따라서, 표면은 흐림을 방지할 수 없다. 심지어 점성유동 범위내에서라도, 만일 높은 부착특성을 갖는 가스가 소스가스내에 함유되어 있다면, 퍼지가스공급부(15)나 창(12)은 소량의 높은 부착성을 갖는 가스의 유입에 의해 점차적으로 흐려진다.

이것은 그와같은 CVD장치에 있어서 장치의 구조때문에 퍼지 및 소스가스의 압력이 서로 같아지기 때문이며, 따라서 퍼지가스는 소스가스의 유입을 막는데 단지 미미한 효과만을 나타낸다. 그러나, 종래의 단일 한 장씩의 웨이퍼 가공 CVD장치는 높은 부착특성을 가진 염소계(chlorine-based) 소스가스를 사용하고, 가스유동이 분자의 흐름으로 되는 압력내에서 기판을 500℃ 또는 그 이상으로 가열하는 CVD 시행에 높은 생산성을 가진 우수한 질의 얇은 박막을 제조할 수 없었다.

특히, 불순물이나 결정성이 막질에 크게 영향을 끼치기 쉬운 얇은 금속박막을 염소계 소스가스로부터 박막을 성장시키므로서 그들의 부피에 상당하는 조성이나 저항을 가진 높은 품질의 얇은 금속박막을 높게 재생성으로 안정하게 생산하는 것은 어렵다.

본 발명을 요약하면 다음과 같다.

본 발명의 주요한 목적은 우수한 균일성과 선택성으로 실리콘 표면에 금속박막을 부착할 수 있는 선택적 CVD법을 제공하는 것이다.

본 발명의 또다른 목적은 실리콘과 배선금속 간의 접촉저항을 감소시킬 수 있는 선택적 CVD법을 제공하는 데 있다.

또다른 목적은 큰 비중율(aspect ratio)를 갖는 접촉홀의 바닥에 균일한 금속박막을 부착할 수 있는 선택적 CVD방법을 제공하는데 있다.

또다른 목적은 높은 재현성을 갖는 우수한 질의 박막을 제조할 수 있는 선택적 CVD를 위한 CVD장치를 제공하는데 있다.

그밖의 목적은 동일한 성장조건하에서 동일한 질을 갖는 막을 반복적으로 제조할 수 있는 CVD장치를 제공하는데 있다.

상기의 목적들은 박막 성장의 초기 단계에 있어서 성장핵의 밀도가 심지어 Si 표면의 약간의 산화에 의해서도 성장된 박막의 균일성이나 모양을 저하시킬 정도로 감소된다는 발견에 기초하여 본 발명자들에 의해 달성되었다.

본 발명의 원리에 따라, 기판을 가열하여, Si 표면을 자연산화막을 감소 및 제거시키기 위해 실리콘 수소화물로 구성된 가스에 노출되게 한다. 소스가스를 Si 표면에 선택적인 박막을 부착시키기 위해 반응실에 공급된다.

이 방법으로, Si 표면의 자연산화막은 Si 표면온도가 섭씨 수백도 이상까지 증가될때환원되고 제거되기 때문에, 깨끗한 Si 표면을 얻을 수 있다. 이 상태에서 반응실에의 소스가스공급에 의해, 막성장 초기과정에 있어서 Si 표면에, 성장되는 핵의 밀도를 증가시킬 수 있다. 그러기에, 깨끗한 Si 표면을 얻을 수 있기 때문에, 막성장에 있어서 절연체(insulator)와의 사이에 높은 선택성을 얻을 수 있다.

본 발명에 따라 반응실내에 배치되는 웨이퍼상에 기상으로 화학반응을 이용한 막을 형성하는 CVD장치에 있어서, 웨이퍼와의 접촉부가 적어도 석영유리로 되고 그 웨이퍼의 주위만을 접속하여 그 웨이퍼를 유지함과 아울러 상기 반응실을 두개의 영역으로 구분 형성된 구조를 갖는 웨이퍼 서셉터에 의해 두개로 나누어진 반응실의 전기 웨이퍼를 가열하는 쪽의 첫번째 영역에 접속된 퍼지가스공급기구와 상기 두개로 나누어진 반응실의 상기 웨이퍼를 가열하는 쪽과는 반대쪽의 두번째의 영역에 접속된 소스가스공급기구 및 배기기구와, 상기 첫번째의 영역내 또는 그 첫번째의 영역쪽의 반응실 외측에 설치된 상기 웨이퍼를 가열하는 가열기구와를 구비하고, 상기 웨이퍼 서셉터에 의해 두개로 나누어진 상기 첫번째 및 두번째의 영역간의 간격을 될 수 있는 한 적게하여 상기 가열기류의 발열체에서 발생되는 복사광이 상기 웨이퍼에 직접 흡수되게 하였다.

상기의 CVD장치를 사용하는 본 발명의 방법은 웨이퍼를 가열하면서 상기 첫번째의 영역에는 소스가스의 압력보다 높은 압력이 되도록 퍼지가스를 공급함과 아울러 소스가스로서 염소가 함유된 가스를 상기 두번째의 영역에 공급함으로서, 그 소스가스의 압력을 분자흐름이 되는 압력으로 유지하여 상기 웨이퍼상의 막을 형성하는 것이다.

그런 까닭에, 본 발명의 CVD장치에 있어서, 웨이퍼 서셉터는 반응실을 두영역으로 나누고, 나뉘어진 첫번째와 두번째 영역사이에 간격이 최소화되도록 설치한다. 따라서, 소스가스압이 분자유동을 형성할 만큼 유지되더라도, 첫번째 영역으로의 소스가스의 유입은 막을 수 있다.

또 첫번째 영역에 소스가스압보다 더 높은 압력을 갖고 있는 퍼지가스가 충전되므로, 소스가스 유입방지 효과가 상승될 수 있다.

또한, 서셉터의 웨이퍼 접촉부가 석영유리로 이루어져 있어 그로인해 웨이퍼와 웨이퍼의 주변부가 고온으로 가열될지라도 작은 열팽창 계수를 가지기 때문에 이 부분은 덜 변형된다. 따라서, 이 부분에 큰 간격이 형성되지 않아 첫번째 영역으로의 소스가스의 침입을 막을 수 있다.

이런식으로, 높은 부착특성을 가진 염소계의 소스가스로 사용된다고 할지라도, 첫번째 영역으로의 가스의 침입은 막을 수 있다. 더우기. 서셉터의 재료인 석영유리는 염소에 대해 높은 부식이 되지 않는다.

본 발명을 도면에 도시된 실시예에 따라 상세히 설명하면 하기와 같다.

제1도는 본 발명에 콜드월 타입의 CVD장치의 실시예를 나타낸 것이다.

제1도에 나타낸, 웨이퍼(20)의 외측은 절연물질로 구성된 웨이퍼 서셉터(이하, 서셉터로 칭함. 21)에 의해 고정되어 있고, 그것의 이면은 원주형의 금속반응실(22) 외측에 위치한 램프히터(발열체, 23)에서 발생되는 빛에 의해 창(24)을 통해 가열된다.

반응실(22)의 내부에 웨이터(20), 서셉터(21)등(본 실시예에서는, 실(chamber)은 그것의 축방향으로 나뉘어졌다.)에 의해 두개의 영역(25와 26)으로 나뉘어졌다.

한쪽 영역(26)은 원주형 반응실(22)의 원주형 벽내에 설치된 퍼지가스도입구(27)로부터 도입되는 퍼지가스로 충전된다. 다른쪽 영역(25)은 반응실(22)의 축방향으로 한쪽 끝부분에 설치된 소스가스도입구(28)로부터 도입되는 소스가스로 충전된다. 소스가스가 영역(25)쪽으로 노출된 웨이퍼(20)의 표면에 접촉할때, 웨이퍼(20)의 표면위에 막이 성장된다. 소스가스와 막의 서장에 의해 생성된 반응가스 및 웨이퍼와 서셉터(21)가 중복된 부분에 형성된 간격등으로 영역(25)쪽으로 누출되는 퍼지가스는 배기구(29)로부터 배기된다. 퍼지가스배기구(30)는 영역(26)내에서 침입하는 소스가스를 퍼지가스와 같이 배기하여 영역(26)내의 청정을 유지하기 위해 또한 배기구(30)는 퍼지가스의 압력을 일정하게 유지하기 위해 설치되어 있다.

그러나, 만일 침입된 퍼지가스의 양이 미량이고 무시할 정도이거나, 퍼지가스배기구가 없어도 퍼지가스의 압력을 일정하게 유지시킬 수 있다면, 퍼지가스배기구를 만들 필요는 없다.

본 실시예의 CVD장치에서, 반응실(22)은 웨이퍼(20)와 서셉터(21)로 구분하여 영역 25와 26으로 나뉘며, 소스가스가 영역(26)으로 유입되는 것을 막아 창(24) 표면의 흐림을 방지한다.

영역(26)으로 유입되는 소스가스의 양을 최소로 하기 위해, 웨이퍼(20)와 서셉터(21)의중복부분에 형성된 간격과 서셉터(21)와 반응실(22)의 내벽사이에 형성된 간격이 최소로 되어야 한다. 이들의 간격에 있어서, 서셉터(21)와 반응실(22) 내벽사이의 간격을 적게하는 것은 이들 부분이 직접적으로 가열되지 않고 따라서, 이들 부분의 온도도 상승되지 않기 때문에 비교적 용이하게 최소화할 수 있다. 즉, 이들 부분의 가공 정밀도를 좋게할 필요가 있다.

그러나, 웨이퍼(20)가 서셉터(21)의 중복부분은 램프히터(23)로부터의 빛이나 웨이퍼(20)로부터의 열에 의해 고온으로 가열된다. 따라서, 서셉터(21)의 열변형으로 인해 큰 간격이 쉽게 형성된다.

그런 연유로, 본 실시예에서는 가공된 석영유리를 서셉터(21) 재료로 사용한다. 높은 정밀도를 갖는 석영유리를 가공하기 위해 초음파 가공법(ultrosoic processing method)이 적당하다. 석영유리가 서셉터(21) 재료로 사용될때, 석영유리의 열팽창 계수가 매우 작기 때문에(약 0.3ppm), 나머지부분이 저온으로 유지되는 관계로 웨이퍼(20)에 접촉된 부분의 근처가 고온으로 가열된다고 할지라도 서셉터(21)의 형상은 거의 변형이 일어나지 않는다.

따라서, 웨이퍼(20)와 서셉터(21)의 중복부분에 큰 간격이 형성되지 않는다. 그러나, 서셉터(21)가 금속으로 만들어진다면, 금속의 열팽창 계수는 크기 때문에(수 ppm에서 수십 ppm까지), 서셉터 일부분이 고온으로 가열되면 그 부분이 팽창하고 변형되어, 웨이퍼와 서셉터의 중복부분에 커다란 간격이 형성되어 벌어진다. 서셉터(21)가 석영유리로 형성되었을때, 웨이퍼(20)와 서셉터(21)의 중복부분에 형성된 간격의 전도도는 하기와 같다.

이 실험은 퍼지가스배기구(30)는 닫고, 웨이퍼(20)에는 지름이 4인치경인 0.5㎜ 두께의 Si 웨이퍼를 사용하며, 웨이퍼 외측이 5㎜ 폭으로 중복되도록 하며, 서셉터(21)의 두께를 5㎜가 되도록한 상태에서 시행했다.

퍼지가스도입구(27)로부터 Ar가스를 0.01SCCM의 유량으로 도입하고 배기구(29)로부터 1000L/sec의 능력을 가진 펌프에 의해 배기하면, 영역(26)내의 Ar가스의 압력은 약 0.1Torr이 되고, 영역(25)내의 압력은 약 2×10-5Torr이 되었다.

즉, 웨이퍼(20)와 서셉터(21)의 중복부분의 간격의 전도도는 약 1.3CC/sec 또는 그 이하로 극히 작았다. 이 간격의 전도도는 서셉터등의 가공 정밀도에 따라 변한다.

그러나, 본 실험에서, 서셉터등은 통상의 가공법, 예를들면, 특별한 고정밀 가공이 필요하지 않은 방법에 의해 가공되었다. 웨이퍼(20)가 가열될때, 영역(26)내의 Ar가스도 가열되고, 따라서 가스압력도 그 만큼 약간 증가된다. 그러나, 영역(25)내의 Ar압력은 사실상 변화되지 않는다. 이러한 경향은 웨이퍼(20)의 온도가 약 800℃까지 증가될때에도 변하지 않는다. 이것은 웨이퍼(20)가 고온으로 가열될때라도 웨이퍼(20)와 서셉터(21)의 중복부분내의 간격(전도도)이 증가되지 않는다는 것을 나타낸다. 그러나, 만약 같은 조건에서 서셉터(21)의 재료를 금속, 예를들어 두께 5㎜인 티탄으로 하면 웨이퍼와 서셉터의 온도가 증가됨에 따라 영역(26)내의 압력은 저하되어 버린다.

이것은 금속 서셉터의 열변형(thermal strain)으로 인해 중복부분의 간격이 넓어지는 것을 의미한다. 금속은 열변형으로 인해 가공 변형이 일어날때, 때때로 금속은 그것의 원래 모양으로 복원되지 않은 때가 있다. 이 변형은 금속의 판두께가 얇을수록 그러한 변형이 현저하게 일어난다.

제1도에서 나타낸 것처럼, 서셉터(21)는, 웨이퍼(20)를 주위만 접촉하도록 중심부에 홀(21a)이 뚫어져 있고 웨이퍼(20)의 외측만이 접촉하도록 서셉터(21)내에서 형성된다. 이 구조는 하기의 이유때문이다.

소스가스가 웨이퍼(20)와 서셉터(21)의 중복부분으로 유동하고, 중복부분의 서셉터의 표면에서 막이 성장되므로, 만약 성장된 막이 히터로부터 발생된 방사광에 대해 불투명할때는, 그 막에 열이 흡수되고, 이 부분의 위에 있는 웨이퍼의 온도는 하강된다.

따라서, 본 실시예에 따른 CVD장치에 있어서는, 웨이퍼(20)와 서셉터(21)의 중복부분의 넓이를 최소화하고, 두영역(25와 26)사이에 간격을 최소화하기 위해 웨이퍼(20)의 외측만이 서셉터에 접속하도록 한 것이다.

서셉터(21)의 구조는 제1도에 나타낸 것으로 국한되는 것은 아니다. 예를들어, 제2도에서 나타낸 것처럼, 구조를 고온으로 가열되는 부분에만 석영유리부(53)를 사용하고, 고온으로 가열되지 않는 부분에는 금속부(54)를 사용하는 것과 같이 수정될 수도 있다. 석영유리부(53)와의 접촉부(55)나 반응실벽과의 접촉부(56)등의 높은 표면등 정밀도를 요구하는 부분은 선반을 이용한 가공이 적당하다. 금속부(51)는 열팽창을 억제하기 위해 물로 냉각시킬 수 있다. 영역(25)에 소스가스를 도입하여 CVD를 실행할때 반응실(22)의 영역(26)측 원주형 벽에 설치된 창(24) 표면의 흐름을 막기 위해, 영역(26)의 퍼지가스압은 영역(25)의 퍼지가스압보다 더 높게 증가시켜두면 된다.

비록 압력차이를 증가시킴으로서 영역(26)내로 소스가스의 유입을 보다 효과적으로 막을 수 있다고 하더라도, 통상적으로 압력차이는 약 0.1Torr 정도면 충분하다. 만일 퍼지가스압이 너무 많이 상승되면, 웨이퍼(20)가 이 압력에 의해 부유하게 된다.

제4도에서 나타낸 것처럼, 퍼지가스압을 높일 경우에, 웨이퍼(20)가 부유하지 않도록서셉터(21)상에 위치한 웨이퍼(20)의 외주연을 웨이퍼 홀더(50)로 눌려서 고정한다.

『더우기 여기서 작업시에 세개의 압력준위가 존재한다.

명확히 : (1) 잔류가스가 제거될때 1차 압력

(2) 실란과 디실란가스가 공급될때 1차 압력

(3) 소스가스가 공급될때 3차 압력

보다 좋은 형태로서, 이들 압력은 다음에 상응한다.

(1) 통상 평형이하 압력, 예를들어 10-6Torr 또는 그 이하

(2) 평형 압력, 예를들어 0.1∼10mTorr

(3) 소스가스가 공급될때 실란과 디실린가스의 압력보다 높거나 낮게 될 수 있는 압력』

서셉터가 석영유리로 구성될때 얻어지는 또 다른 이점을 하기에 기술한다.

후술될 것처럼, 본 발명의 또다른 측면으로, 상술한 CVD장치를 사용하는 CVD법에 있어서, 4염화 티탄(TiCl4)가스가 소스가스로 사용된다.

막 형성시의 반응에 있어서, TiCl4는 분해되어 염소(Cl2)나 염화수소(HCl)를 생성한다. Cl2나 HCl은 높은 부식성(corrosiveness)을 가지며, 예를들어 Si, SiO2를 부식시키기 위한 부식가스로 사용되지만, 염소계 가스에 대해서는 높은 부식 저항성을 갖는다. 석영유리는 SiO2로 구성되므로 염소계 가스에 의해 부식되지 않는다는 이점이 있다.

상기한 구성을 가진 CVD장치를 이용하여, 실리콘 표면과 절연체 표면을 가지는 기판의 실리콘 표면에 선택적으로 박막을 성장하는 방법을 하기에 기술한다.

상술한 로드록기구(load locking mechanism)는 본 장치에 설치되고, 웨이퍼(20)가 가열된 상태라도 반응실내의 잔여가스가 압력이 2×10-6Torr 또는 그 이하로 감소되도록 배기한다. 홀(28)로부터 공급된 소스가스는 염소함유 가스를 사용하고, 장치는 소스가스유동이 분자유동이 되는 낮은 압력범위내에서도 고온에서 사용에 견딜 수 있게 되어 있다.

소스가스의 유입을 막기 위해, 소스가스보다 더 높은 압력을 갖는 퍼지가스가 홀(27)로부터 공급된다.

막의 성장에 있어서, 기판으로서 Si(100) 웨이퍼(20)가 사용된다. 그 Si 웨이퍼는 열에 의해 산화시킨후, 그 결과 포토리도그래피(photolithography) 및 습식엣칭(wet etching)(제3a도)에 의해 열산화막이 만들어졌다. 결과로 생성된 웨이퍼를 묽은 불화수소산에 담궈 Si 표면(제3a도에 51로 표시되어 있음)의 자연산화막을 제거한뒤, 수세, 건조시킨후, 공기중에 소정시간동안 방치했다.

이 웨이퍼는 상술한 CVD장치에 장진되어 약 720℃로 가열하여, 소스가스인 실란(SiH4)가스와 4염화티탄(TiCl4)가스가 동시에 공급되어 티탄 실리사이드 막(TiSix)이 Si표면에만 선택적으로 성장되었다.

SiH4의 공급유량은 10SCCM이고, 압력은 1mTorr이었으며, TiCl4가스의 압력은 5∼10×10-6Torr였다.

약 1분의 성장시간동안에, 높이 200∼300Å의 핵 또는 박막이 성장됐다. 그 결과, 묽은 불화수소산으로 처리한 웨어퍼를 공기중에 방치하는 시간의 장단이 성장하는 티탄 실리사이드의 핵밀도에 큰 영향을 미치는 것을 발견했다.

즉, 웨이퍼가 공기중에 장시간 방치되어 Si표면의 소수성이 약해지거나 상실될때, 핵밀도는 매우 낮은데, 예를들면 수㎛에서 수십 ㎛의 변으로된 사각영역에서 단 한개의 핵도 성장되지 않지만 웨이퍼가 공기중에 방치시간이 단지 수분동안으로 Si표면의 소수성이 강할때에는, 핵밀도가 매우 높은데, 예를들면, 0.1 내지 1㎛미만의 변으로된 사각영역에서 한개 정도의 핵이 성장된다.

묽은 불화수소산 처리후, 수분동안 공기중에 방치한 웨이퍼를 상기의 CVD장치에 장진하여 티탄 실리사이드를 성장시키기전에, 웨이퍼를 약 720℃로 가열하고, SiH4가스를 반응실에만 공급하여, 그것에 의해 SiH4가스의 자연산화막(제3b도)에 대한 환원작용을 이용하여 묽은 불화수소산처리후 Si표면에 성장된 자연산화막을 환원, 제거한후, 계속해서, SiH4가스를 이용한 자연산화막의 환원처리를 시행하지않은 상기의 성장법과 같은 공정이 시행되었다.

즉, 소스가스로서 SiH4가스와 TiCl4가스를 동시에 공급하여 Si표면(제3c도)에만 티탄 실리사이드 막을 선택적으로 성장시켰다.

SiH4가스를 이용한 자연산화막의 환원처리가 시행된 후, 티탄 실리사이드 막이 선택적으로 성장되었다.

본 실시예의 방법에 따라 성장된 티탄 실리사이드의 핵밀도는 SiH4가스를 이용한 자연산화막의 환원처리를 시행하지 않았을때 보다 더 높았다.

SiH4가스를 이용한 환원처리를 시행했을때와 시행하지 않았을때에 얻어진 결과를 비교해보면, 묽은 불화수소산 처리후 생긴 Si표면의 약간의 산화나 오염이 티탄 실리사이드 성장핵 밀도에 악영향을 미치는것이 발결되었다.

상기의 첫번째 실험에서 사용된 Si웨이퍼와는 표면상태가 다른 Si웨이퍼를 사용한 두번째 실험을 기술한다.

Si웨이퍼(100)는 열산화하고, 결과 포토리드그래피(photolithography)와 드라이엣칭(dry etching)에 의해 열산화 막이 만들어진다.

웨이퍼를 묽은 불화수소산에 담궈 Si 표면의 자연산화막을 제거하고 세정, 건조후, 공기중에서 소정의 시간동안 방치했다.

이 웨이퍼의 표면상태는, 묽은 불화수소산에 침적시켜 Si표면으로부터 자연산화막을 제거한 시점에서는 Si표면의 소수성이 명료하게 확인될 수 있었다.

그러나, 웨이퍼를 세정한 후에는 소수성이 완전히 상실되었다.

이 웨이퍼를 사용하여 첫번째 실험과 동일한 조건하에서 티탄 실리사이드 막을 선택적으로 성장시키기 위해 사용되었다.

그 결과 웨이퍼를 묽은 불화수소산으로 처리한후 공기중에 방치하는 시간의 장단에 상관없이 핵밀도는 매우 낮고, 즉, 수십㎛의 변으로된 사각영역내에 단지 한 개 정도의 핵이 성장됐다.

그에 반하여 묽은 불화수소산 처리후 수분동안 공기중에 방치된 웨이퍼를 상술한 SiH4가스를 이용한 자연산화막의 환원처리와 같은 방법에 의해 환원하고나서 티탄 실리사이드 막을 선택적으로 성장시킨때는, 1㎛ 미만의 변으로된 사각영역내에 한개정도의 핵이 치밀하게 성장되었다.

또한, 묽은 불화수소산 처리후 수시간동안 공기중에 방치한 웨이퍼상에 부착된 자연 산화막일지라도 SiH4가스에 의해 환원시킬 수 있음을 알었다.

티탄 실리사이드 막이 이 웨이퍼상에 선택적으로 성장되었을때, 1㎛ 미만의 변으로된 사각 영역내에 한개정도의 치밀하게 핵이 부착되었다. Si기판의 매우 높은 진공상태에서 고온으로 가열될때, Si표면의 자연산화막이 증발되어 깨끗한 Si표면이 만들어진다는 사실은 잘 알려져 있다.

그러나, 본 발명의 효과는 하기의 실험에서도 나타내는 바와같이 이 고온 가열에 의한 효과가 아님을 알게되었다. 즉, 두번째 실험에서 행한 공정과 마찬가지로 웨이퍼를 묽은 불화수소산 처리후, 세정, 건조후 수분동안 공기중에 방치한후, 반응실내에서 소스가스 공급을 하지않고, SiH4가스를 이용한 자연산화막을 환원하는데 필요한 시간의 3배 이상의 시간동안 자연산화막 환원시와 동일한 온도까지 가열했다.

그후, SiH4가스와 TiCl4가스를 동시에 공급하여 티탄 실리사이드를 성장시킬때, 이경우, 핵밀도는 그렇게 많이 증가되지는 않았지만 대체로 가열시간이 짧았을때 얻은것과 비슷했다.

이 결과에서 가열됐을때는 자연산화막의 환원이 웨이퍼의 진공중 가열로서는 일어나지 않았다는것을 보여준다.

SiH4가스의 환원작용은 900℃ 이상의 고온에서 잘 일어난다는것이 공지되어있다.

그러나, 상기의 실험에 의하면, 환원작용은 약 700℃ 내지 750℃에서 일어난다는것이 명확해졌다.

SiH4가스가 계속적으로 공급될때, Si가 우수한 결정성을 가지고 Si표면에서 적층적으로 성장되므로 SiH4가스가 자연산화막을 환원한다는 사실을 확인할 수 있다.

자연산화막이 Si표면에 잔재한다면, Si가 우수한 결정성을 가진 적층적 성장이 되지않고, 쌍결정이나 다결정 Si가 형성된다고 추측된다.

그와같은 저온에서의 자연산화막에 대한 SiH4가스의 환원작용은 핫 월 타입(hot wall type) CVD장치를 이용하여 초청정대기(ultra clean atmosphere)중에서 얻은 Si적층성장의 실험결과에 근거를 둔 무로타(Murota)등에 의해서도 제안되었다.["전자정보통신 학회 기술연구보고", 88권, 제162호, 9∼13페이지, 1988년간(SDM 88-3)("Electronic Data Communication Society Technical Research Report", Vol. 88, No.162, PP.9 13, 1988(SDM 88-3))과 "응용물리학지", 54권, 제11호, (1989년간), 1007페이지 ("Applied Physics Letters", Vol.54, No.11,(1989), 1007)]

티탄 실리사이드 막의 선택적성장 및 Si의 선택적 적층성장에 대한 상기의 실험에 의거해서, 본 발명자들은 저온에서 SiH4가스가 자연산화막 환원작용을 가졌음을 확인했다.

SiH4가스에 의해 행해진 자연산화막의 환원의 종료시점은 반응실벽에 설치된 유리창을 통해 웨이퍼의 Si표면에 He-Ne레이저광을 비추워두거나 Si의 적층성장이 시작될때 Si핵 성장에 의해 생기는 레이저광의 산란광을 검지하는것에 의해 결정했다. 이 산란광은 SiH4가스가 반응실에 공급된후 수십초 내지 수분의 오프세트(offset)시간의 경과한 후에 서서히 나타난다. 자연산화막의 환원은 이 오프세트시간중에 이루어진다고 추축된다.

Si핵성장은 웨이퍼의 면의 방위(orientation)에 따라 현저하거나 또는 미미하게 이루어진다.

(100)기판이 이 실험에 사용될때, 부착은 현저하게 이루어진다.

이 경우에, 기판표면에 대해 경사진 표면의 부착속도가 빠르므로, 성장을 계속할수록 대체로 매우 평평한 막을 얻을 수 있다. 이 막 성장상태에서 Si막이 우수한 결정성을 가지고 적층적으로 성장됨을 알 수 있다.

Si막이 성장의 초기과정에서는 핵의 형태에서도, Si막이 쌍결정이나 다결정을 동반하지않으며, 우수한 결정성을 가지고 적층적으로 성장됨을 전자선회절(electron diffraction)을 이용한 분석으로 확인된다.

상술한 바와같이, 티탄 실리사이드의 선택적 CVD에서 Si표면의 청정도에 의해 막 성장의 초기과정에서의 핵밀도는 크게 악영향을 받는다는것이 판명되었다.

막 성장 초기과정에서, 티탄 실리사이드의 핵 밀도가 낮다면, 얇고 치밀한 막은 성장될 수 없다.

만일 두꺼운 막이 형성될지라도, 형성된 막은 심한 굴곡을 갖는다.

만약 Si표면의 자연산화막이 너무 두껍거나 심하게 오염되었다면, 티탄 실리사이드 막을 선택적으로 성장시키는것은 곤란하다.

선택적 CVD법에 있어서 그와같은 표면 청정도의 영향을 트리부틸알루미늄가스를 사용하는 알루미늄의 선택적 CVD법(일본 특허공개공보 제 63-33569호)이나 텅스텐의 선택적 CVD법에서도 볼 수 있다.

Si표면의 청정도간의 근소한 차이가 막 성장 초기의 핵밀도에 크게 악영향을 준다는 것이 발견된 실험이 본 발명의 실시예와 함께 기술되었다.

그러나, 본 발명은 상술한 실시예에 대해서만 국한되지는 않는다.

SiH4가스의 자연산화막의 환원/제거 효과는 SiH4가스의 공급유량이나 압력 및 기판온도에 대해 큰 차가 있다.

이 차이는 SiH4가스에 의해 자연산화막이 붙은 Si표면상에 Si가 적층적으로 성장될 수 있는 유량, 압력 및 기판온도의 범위와 대체로 동일하다고 추측된다.

SiH4가스대신에 디실란(Si2H6)가스를 사용해서도 비슷한 결과를 얻을 수 있다.

상기의 실시예에서 처럼 티탄 실리사이드 막을 선택적으로 성장시키기는 경우는, SiH4가스를 사용한 자연산화막의 환원과 제거할때의 기판온도와 티탄 실리사이드를 성장시키는 기판온도와 동일하게 할 수 있다.

또한, SiH4가스의 유량 및 압력도 티탄 실리사이드를 부탁 시키기위한 유량 및 압력과 동일하게 할 수 있다.

따라서, 이 경우에, 기판온도, SiH4가스의 유량 및 압력을 일정하게 유지하여 자연산화막의 환원종점을 검출한 직후, TiCl4가스를 공급하여 티탄 실리사이드 막을 성장시킬 수 있다.

웨이퍼의 가열계(heating system)로 램프히터등의 온도변화가 시간정수가 짧은 것을 사용하면 SiH4가스를 이용한 자연산화막의 환원 처리시의 기판온도와 그후에 막이 선택성장시에 기판온도가 달라지는 경우에도 급속히 기판온도가 변화될 수 있다.

따라서, Si표면의 산화 및 오염을 최소한으로하여 막을 성장시킬 수 있다.

본 발명의 또다른 관점에 따른 CVD장치의 또다른 구성을 제5도에 나타낸다.

제5도에 있어서, 제1도에서와 동일한 것은 동일번호를 부쳐서 그것의 상세한 설명은 생략한다.

이 구성에서 제1실시예의 구성과는 다른점은 창(24)뿐만 아니라 램프히터(23)도 사용하지 않고, 그 대신 영역(26)내에 히터(발열체, 60)와 열반사판(61)이 설치되어있는 것이다.

히터(60)는 절연체(62)등에 의해 고정되어 있다.

히터(60)로부터의 복사광이 웨이퍼(20)의 이면에 직접적으로 도달하여 웨이퍼(20)를 가열한다.

열반사판(61)은 히터(60)로부터 나오는 복사광을 반사하거나 재복사하므로서, 그것으로 인한 반응실 벽등의 과열을 막기위해 설치되어 있다.

히터(60)의 재료로 적당한 것은 탄탈(Ta)과 텅스텐(W)이다.

이러한 재료로 만들어진 선을 코일형태로 조밀하게 감아서 표면적으로 크게하여 복사광의 양을 증가되도록 한다.

열반사판(61)은 몰리브덴(Mo), 탄탈(Ta) 및 텅스텐(W)과 같은 고융점인 내화성(refractory)금속들이 적당하다.

또 절연체(62)는 고융점인 내화성 절연체이면 사용될 수 있으나, 히터(60)의 온도가 너무 높게 상승되지 않는다면, 석영 유리도 사용될 수 있다.

예를들면, 히터(60)에 Ta, 열반사판(61)에 Mo, 절연체(62)에 석영유리를 사용할때, Si웨이퍼(20)는 약 1000℃까지 가열될 수 있다.

제5도에 나타낸 구성에서 히터(60)에 높은 전압을 공급하여 열을 발생시키도록 설계된다면, 반응실(22)의 영역(26)이 퍼지가스로 채워질때 방전에 의해 히터(60)가 쉽게 파괴될 수 있다.

따라서, 이 경우에 퍼지가스의 압력이 너무 높게 증가되지 않음이 좋다.

상기의 첫번째와 두번째 실시예에 따른 CVD장치들간의 주요한 차이점은 히터들의 복사광의 파장분포가 서로 다르다는 것이다.

즉, 램프히터(23)를 사용한 첫번째 실시예에 있어서는, 발열체의 온도를 높게할 수 있어 가시성분을 많게 할 수 있다.

그러나, 코일히터(60)등을 사용한 두번째 실시예에서는, 퍼지가스에 의한 냉각효과가 거의 없으므로, 절연체(62)등의 국부적 과열로 인해 쉽게 고장날 수 있다.

따라서, 발열체의 휘도(brightness)(輝度)는 크게 높일 수 없고, 즉 발열체를 적외선 성분이 많은 상태에서 사용한다.

이 차이는 웨이퍼(20)로서 긴 파장의 적외선광을 잘 투과시키는 Si웨이퍼가 사용할때 현저해진다.

즉, 두번째 실시예에 있어서, Si웨이퍼를 투과하는 적외선광의 양이 증가되고, 그 적외선광은 Si웨이퍼의 표면에 금속막이 성장될때, 금속막에 흡수되어 그 온도가 상승되는 작용을 한다.

따라서, 증착동안에 금속막의 성장중에 표면온도를 일정하게 유지할때는 첫번째 실시예에 따른 장치가 쉽게 제어될 수 있다고 본다.

제1도 및 제5도에 나타낸 각각의 실시예에서, 웨이퍼(20)의 표면(즉, 소스가스에 노출되는 쪽의 표면)은 위쪽을 향하도록 표시하였으나, 그러나, 히터나 서셉터등의 상하를 꺼꾸로 하여 웨이퍼의 표면을 향하게 하는 배열로 아래쪽을 향할 수 있게 할 수 있다.

이 경우에는, 히터나 서셉터는 고정되어있고, 웨이퍼는 제3도에 나타낸 웨이퍼 홀더(40)와 같은 것으로 서셉터(21)에 압압하도록하면 된다.

웨이퍼의 표면은 옆을 향하고 있으므로 웨이퍼를 똑바로 세우기위해 웨이퍼 고정부를 약간 개조할 수 있다.

티탄 실리사이드 막의 저항성을 제어하는 상세한 방법과 티탄 실리사이드 막 성장으로 인한 하부의 실리콘 소모량을 제어하는 방법을 하기에 기술한다.

하기 실시예에서 상세히 기술된 바와같이, 다른 CVD에서 사용되는 다수의 소스가스 유량비와 비교해서, 반응실에 공급되는 사염화티탄 가스의 유량대 실란가스의 유량비를 극도로 감소시킴으로써 하부실리콘의 소모량을 감소시킬 수 있다.

본 실시예에는, 제6도에 나타낸 CVD장치를 설명한다.

이 장치가 제5도에 나타낸 CVD장치와 다른것은 티탄 실리사이드 가스 미세 유동제어기구(fine-flow control mechanism)를 부가한 점이다.

제6도에 있어서, 제5도와 동일한 참고번호를 동일한 부분에 표시하며, 그것의 상세한 설명은 생략한다.

제6도를 보면, 참고번호 42는 액화 사염화티탄을 저장하고있는 탱크를 나타내며, 43은 탱크에 연결된 질량 유동 제어기(mass-flow controller), 44는 질량유동제어기(43)의 배출부와 반응실(22)의 소스가스 도입구(28)사이에 위치한 미세유동제어기를 나타낸다.

미세유동제어기(44)는 밸브(45와 46), 컨덕턴스밸브(47과 48), 진공배기펌프(49) 및 압력계(pressure gauge)(50)로 구성된다.

이 배열에서, 액화 사염화티탄(12)으로부터 증발된 사염화 티탄가스는 그것의 유량이 질량 유동제어기(43)에 의해 제어되는 동안 미세유동제어기(44)에 공급된다.

미세유동제어기(44)는 컨덕턴스밸브(47과 48)의 개방각도(컨덕턴스)를 설정하여 사염화티탄가스의 유량을 조절한다.

사염화티탄가스가 공급될 때, 밸브(45)는 압력계(50)로 측정되는 사염화티탄가스의 압력을 일정하게 유지하기위해 계속 열려있다.

반응실(22)로의 사염화티탄가스 공급은 개폐 밸브(48)에 의해 시작되거나 중단된다.

진공배기펌프(49)로는 터보 분자펌프(trubo molecular pump)와 같이 진공배기를 실행할 수 있는 펌프가 적당하다.

그와같은 가스유동제어기구를 사용함으로써, 매우 낮은 유속의 사염화티탄가스를 공급할 수 있다.

실란가스(51)의 유량이 상대적으로 높기때문에, 일반적으로 사용되는 질량유동제어기(52)는 유량을 제어할 수 있다.

상기의 CVD장치는 매우 낮은 유속의 사염화티탄가스를 제어하기 위해 사용됐는데, 이것에 의해 실리콘 웨이퍼의 표면에 티탄 실리사이드 막이 성장된다.

실리콘 웨이퍼로는, (100)의 방위와 습식엣칭에 의해 열산화막에 형성된 창을 가진 단결정 웨이퍼가 사용되었다.

(111)의 방위를 가진 웨이퍼에 의해 동일한 결과가 얻어졌다.

즉, 실리콘의 방위 의존도는 티탄 실리사이드 막성장에 별 영향을 미치지 못한다.

티탄 실리사이드 막의 형성에 앞서, 실리콘 웨이퍼를 묽은 불화수소산에 담궈 표면의 자연산화막을 제거시켰다.

그 결과 웨이퍼는 부하차단기구에 의해 반응실(22)내의 웨이퍼 서셉터에 장진되어 650℃ 내지 720℃까지 가열되었고, 실란가스만을 10SCCM 및 1mTorr 상태에서 공급했는데, 이것에 의해 실리콘 표면이 깨끗해진다.

정화에 필요한 시간은 10초 내지 4분이 소요된다. 계속해서, 웨이퍼 온도의 변화없이, 사염화티탄가스가 0.05 내지 0.3 SCCM 및 2 내지 13×10-5Torr상태에서 공급되었고, 실란가스가 50 SCCM 및 2mTorr에서 공급하면, 약 5분간에 600내지 1,200Å의 두께의 티탄 실리사이드 막이 성장되었다.

반응실에 공급된 사염화티탄가스의 유량은 공지의 유량과 반응실에서의 유량은 압력에 비례한다는 것에 추정한, 공지의 압력을 이용한 외삽법(外揷法)으로 얻었다.

표1과 2는 상기의 성장조건들, 즉, 사염화티탄가스의 공급유량에 작용에 따른 막의 비저항(resistivity)(표1)과 실리콘소모(티탄 실리사이드의 깊이/티탄 실리사이드 막두께 백분율로 나타낸 부착전의 시릴콘 표면으로부터 티탄 실리사이드 막 부착후의 실리콘 계면(界面)(표2)에 의해 얻은 티탄 실리사이드에 대한 데이타를 나타내는 그래프이다.

티탄 실리사이드 막의 비저항은 4점 탐침(探針)(four-point probe)으로 측정했고, 실리콘 소모는 주사(走査) 전자망원경(scanning electron microssore)을 이용한 샘플의 단면을 관찰하여 측정했다.

표 1에서, 커브(Curve)(a), (b), 및 (c)는 웨이퍼온도가 약 720℃인 상태에서 실리콘 표면 노출면적이 각각 약 2, 8, 및 24㎠였을때 얻은 값을 나타낸다.

사염화티탄의 유량이 감소될때, 비저항은 급격히 증가된다.

실리콘 표면 노출면적이 증가함에 따라, 비저항을 증가시키는 유량이 증가된다.

그와같은 실리콘 표면 노출면적에 따른 비저항의 변화는 부하효과(loading effect)의 존재를 의미한다.

표 2의 커브(e), (f), 및 (g)는 표 1에 나타낸 커브(a), (b), 및 (c)에 각각 상응하는 실리콘 소모를 나타낸다.

표 2에 나타낸것처럼, 부하효과는 비저항에서처럼 실리콘 소모에도 관계된다.

표 1과 2는 티탄 실리사이드 막의 저항률이 낮고, 실리콘 소모가 작은 상태에서의 사염화티탄가스의 유량은 비저항이 증가되기 시작할때의 유량이라는 사실을 나타낸다.

이 경우, 실리콘 소모는 약 50%이다.

표1과 2의 커브(d)와 (h)는 각각 웨이퍼온도가 약 650℃, 실리콘 표면 노출면적이 약 8㎠였을때 얻은 데이타를 나타낸다.

이 데이타는 웨이퍼 온도가 낮을때, 낮은 비저항을 갖는 티탄 실리사이드 막을 부착시키기 위해 사염화티탄가스의 유량이 증가되어져야만 한다는 것을 나타낸다.

게다가, 표1과 2의 커브(d)와 (h)는 각각, 웨이퍼온도가 높을때의 실리콘 소모보다 비저항이 증가되기 시작할때의 실리콘 소모가 작음(약 20%까지)을 나타낸다.

웨이퍼 온도가 약 650℃일때, 실리콘 표면은 실란가스에 의해 깨끗해질 수 있다.

청정에 필요한 시간은 고온에서, 보다 더 연장되는 경향이 있을지라도 수분정도이다.

비록 웨이퍼온도가 낮을지라도, 실란가스를 사용한 정화를 수행함으로서 낮은 비저항을 가진 미세한 티탄 실리사이드 막을 부착시킬 수 있다.

상기의 실시예에서, 티탄 실리사이드 막은 절연막상에는 부착되지않고 실리콘표면의 노출된 부분에서만 부착되었다.

부착된 티탄 실리사이드 막의 X-선 회절 패턴은 C54타입 TiCl4이다.

본 발명의 CVD장치에서, 티탄 실리사이드 막이 상기의 실시예에서처럼 반복적으로 부착됐을때라도, 영역(26)으로의 소스가스의 유입은 거의 일어나지 않았다.

따라서, 창(24)의 오염뿐만아니라 히터(60)의 절연파손도 일어나지 않았다.

게다가, 대체로 동일한 특성을 가진 티탄 실리사이드 막이 동일한 부착조건하에서 반복적으로 만들어질 수 있었다.

본 발명에 따른 CVD장치를 이용한 방법의 상기 실시예에서는 단지 티탄 실리사이드 막의 성장막을 기술했다는것에 주목해야 한다.

본 발명의 CVD장치는 상기 실시예에만 국한되는 것이 아니라 예를들어 오염화몰리브덴(MoCl5), 육염화텅스텐(WCl6), 오염화탄탈(TaCl5)등과 같은 가스를 사용하는 다양한 형태의 금속막이나 금속 실리사이드막의 성장에도 적절히 적용될 수 있다.

상기 실시예의 효과를 요약하면 다음과 같다.

(1)본 발명에 사용된 선택적 CVD법에서, 수소화규소로 구성된 가스를 사용해서 실리콘 표면의 자연 산화막을 환원하여 제거시키기위해 반응실내에 장진된 실리콘 모재를 가열하고, 계속해서 소스가스를 반응실내에 공급하며, 이에 의해 실리콘 표면에만 막이 선택적으로 성장된다.

따라서, 본 발명이 반도체 장치의 얕은 접합상에 얇은 금속막을 선택적으로 성장시키기위해 적용될때, 약간의 굴곡을 갖는 균일한 막이 우수한 선택성을 가지고 성장될 수 있다.

그 결과, 낮은 접촉저항과 낮은 접합 누전전류가(junction leak current value)를 갖는 고성능 반도체 장치를 만들 수 있다.

게다가, 본 발명은 금속으로 큰 비중률를 갖는 홀전체를 덮었을때, 홀은 균일하게 덮혀질 수 있으므로 제조수율은 증가될 수 있다.

(2) 본 발명에 사용된 CVD장치에서, 반응실이 석영유리로 구성되었으며 웨이퍼 접속부를 웨이퍼의 외측에만 접촉되도록 웨이퍼를 고정시키는 웨이퍼 서셉터에 의해 두 영역으로 나누어지고, 퍼지가스는 분리된 반응실의 웨이퍼 가열측의 첫번째 영역으로 공급되며, 소스가스가 분리된 반응실의 웨이퍼 가열측의 반대측 두번째 영역으로 공급될때 배기기구가 접속된다.

웨이퍼 서셉터에 의해 분리된 첫번째와 두번째 영역간의 간격이 최소화되어 가열기구의 발열체로부터 방출된 복사광은 웨이퍼에 의해 직접 흡수되므로, CVD는 소스가스유동이 분자유동으로 되는 압력범위내에서라도 강한 부착성을 갖는 염소계 가스를 사용하여 고온에서 실행될 수 있다.

게다가, 아주 소량의 소스가스만이 창이나 히터가 설치된 부분으로 유입되므로, 이 부분은 대체로 오염되지 않는다.

따라서, 동일한 박막특성을 갖는 금속막이 동일한 부착 조건하에서 반복적으로 성장될 수 있다.

그 결과, 높은 생산성을 가진 우수한 품질의 금속막을 제조할 수 있는 CVD가 실행될 수 있다.

Claims (12)

- 잔류가스를 제거하여 1차 저압상태인 반응실내에 실리콘 표면과 절연체표면을 갖는 기판을 장진하고, 이 기판을 실리콘표면상의 자연산화막을 실란으로 구성된 그룹으로 부터 선택된 가스에 의해 환원되는 온도까지 가열하고, 실리콘표면의 자연산화막을 환원 제거하기 위해 실란으로 구성된 그룹으로부터 선택된 가스를 2차 저압의 반응실에 공급하여 상기 실리콘표면에만 선택적으로 금속막 또는 금속질의 막을 형성하기위해 소스가스를 상기 반응실의 3차 저압시에 연속적으로 공급하는 단계로 구성되는 선택적화학증착방법.

- 제1항에 있어서, 소스가스를 650∼750℃로 가열된 실리콘표면상에만 공급하는 방법.

- 제1항에 있어서, 소스가스가 실란가스 및 디실란가스로 구성된 그룹으로부터 선택된 가스를 사용하는 방법.

- 제1항에 있어서, 환원의 종점이 실리콘 표면상에서 복사된 빛의 산란광의 검출에 의해 결정되는 것을 특징으로하는 방법.

- 제1항에 있어서, 반응실은 첫번째와 두번째 영역으로 나누어지고, 그 나누어진 부분에 기판이 간막이벽(partition member)의 일부가 배설되고, 기판의 한면은 복사광으로 기판을 가열하기 위한 첫번째 영역을 향하고, 이 첫번째 영역으로 퍼지가스가 공급되며, 기판의 다른쪽 면이 향하고 있는 두번째영역으로는 소스가스가 공급되고 배기되도록 배설되게 하는 방법.

- 제5항에 있어서, 반응실의 외측에 배설된 가열원 또는 반응실의 첫번째 영역내측에 배설된 가열원에 의해 가열하는 방법.

- 제5항에 있어서, 퍼지가스는 퍼지가스압이 소스가스압보다 높게 되게 첫번째 영역에 공급되어지고, 염소를 함유한 소스가스는 소스가스의 흐름이 분자유동이 되도록 소스가스압을 유지하기 위해 두번째 영역에 공급하여 실리콘 표면에 막을 성장시키는 방법.

- 제5항에 있어서, 간막이 벽이 기판과 기판에 장착된 서셉터에 의해 구성되게 하는 방법.

- 제1항에 있어서, 소스가스가 수소화규소 및 사염화티탄가스로 구성된 가스의 혼합물인 것과 실리콘 표면상에만 선택적으로 부착된 막이 티탄 실리사이드 막으로 되게 하는 방법.

- 제1항에 있어서, 소스가스가 실란가스와 사염화티탄가스의 가스혼합물이고, 실리콘표면상에만 선택적으로 성장된 막을 티탄 실리사이드 막으로 되게 하는 방법.

- 제10항에 있어서, 반응실에 공급되어지는 사염화티탄가스의 유량과 실란가스의 유량비가 임의적으로 매우 작은 값으로 고정되고, 그것에 의해 티탄 실리사이드 막의 성장에 있어서 실리콘의 소모량을 적정량으로 억제하는 방법.

- 제1항에 있어서, 1차 저압상태는 통상평형이하 압력, 예를들어 10-6Torr 또는 그 이하, 2차 저압상태를 평형압력, 예를들어 0.1∼10mTorr, 3차 저압상태를 소스가스가 공급될 때 실란과 디실란가스의 압력보다 높거나 낮게 될 수 있는 압력으로 하는 방법.

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP1-100078 | 1989-04-21 | ||

| JP89-100078 | 1989-04-21 | ||

| JP10007889 | 1989-04-21 | ||

| JP89-207829 | 1989-08-14 | ||

| JP1-207829 | 1989-08-14 | ||

| JP20782989 | 1989-08-14 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR900017107A KR900017107A (ko) | 1990-11-15 |

| KR940001885B1 true KR940001885B1 (ko) | 1994-03-10 |

Family

ID=26441167

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019900005518A KR940001885B1 (ko) | 1989-04-21 | 1990-04-20 | 선택적 화학증착법(化學法, cvd법) 및 동법을 사용한 cvd장치 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US5104694A (ko) |

| JP (1) | JP2939500B2 (ko) |

| KR (1) | KR940001885B1 (ko) |

| DE (1) | DE4013143A1 (ko) |

Families Citing this family (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3469251B2 (ja) * | 1990-02-14 | 2003-11-25 | 株式会社東芝 | 半導体装置の製造方法 |

| US5284521A (en) * | 1990-09-21 | 1994-02-08 | Anelva Corporation | Vacuum film forming apparatus |

| FR2675309A1 (fr) * | 1991-03-22 | 1992-10-16 | Siemens Ag | Procede pour eliminer localement des couches isolantes transparentes aux ultraviolets, situees sur un substrat semiconducteur. |

| TW203633B (ko) * | 1991-06-03 | 1993-04-11 | L Air Liquide Sa Pour L Expl Des Proce | |

| KR970009274B1 (ko) * | 1991-11-11 | 1997-06-09 | 미쓰비시덴키 가부시키가이샤 | 반도체장치의 도전층접속구조 및 그 제조방법 |

| JP3109687B2 (ja) * | 1992-03-09 | 2000-11-20 | 三菱電機株式会社 | 半導体装置の導電層接続構造の製造方法 |

| US5393565A (en) * | 1992-06-08 | 1995-02-28 | Fujitsu Limited | Method for deposition of a refractory metal nitride and method for formation of a conductive film containing a refractory metal nitride |

| US5240739A (en) * | 1992-08-07 | 1993-08-31 | Micron Technology | Chemical vapor deposition technique for depositing titanium silicide on semiconductor wafers |

| EP0606751B1 (en) * | 1993-01-13 | 2002-03-06 | Applied Materials, Inc. | Method for depositing polysilicon films having improved uniformity and apparatus therefor |

| US5652180A (en) * | 1993-06-28 | 1997-07-29 | Kawasaki Steel Corporation | Method of manufacturing semiconductor device with contact structure |

| DE69421465T2 (de) * | 1993-07-30 | 2000-02-10 | Applied Materials, Inc. | Verfahren zur Ablagerung von Silzium-Nitrid auf Siliziumoberflächen |

| JPH07176627A (ja) * | 1993-12-17 | 1995-07-14 | Nec Corp | 半導体装置の製造方法 |

| US6001729A (en) * | 1995-01-10 | 1999-12-14 | Kawasaki Steel Corporation | Method of forming wiring structure for semiconductor device |

| JPH08191054A (ja) * | 1995-01-10 | 1996-07-23 | Kawasaki Steel Corp | 半導体装置及びその製造方法 |

| WO1996024401A1 (en) * | 1995-02-09 | 1996-08-15 | Puritan-Bennett Corporation | Piston based ventilator |

| KR100224654B1 (ko) * | 1995-09-19 | 1999-10-15 | 윤종용 | 반도체장치의 커패시터 형성방법 |

| KR100269311B1 (ko) * | 1997-10-10 | 2000-10-16 | 윤종용 | 웨이퍼스트립방법 |

| US5856237A (en) * | 1997-10-20 | 1999-01-05 | Industrial Technology Research Institute | Insitu formation of TiSi2/TiN bi-layer structures using self-aligned nitridation treatment on underlying CVD-TiSi2 layer |

| US6068441A (en) * | 1997-11-21 | 2000-05-30 | Asm America, Inc. | Substrate transfer system for semiconductor processing equipment |

| US6293749B1 (en) | 1997-11-21 | 2001-09-25 | Asm America, Inc. | Substrate transfer system for semiconductor processing equipment |

| US6019839A (en) * | 1998-04-17 | 2000-02-01 | Applied Materials, Inc. | Method and apparatus for forming an epitaxial titanium silicide film by low pressure chemical vapor deposition |

| US6429101B1 (en) * | 1999-01-29 | 2002-08-06 | International Business Machines Corporation | Method of forming thermally stable polycrystal to single crystal electrical contact structure |

| US6494959B1 (en) | 2000-01-28 | 2002-12-17 | Applied Materials, Inc. | Process and apparatus for cleaning a silicon surface |

| KR100517911B1 (ko) * | 2000-05-19 | 2005-10-04 | 주식회사 하이닉스반도체 | 하부전극과 스토리지 노드 콘택간의 오정렬 및확산방지막의 산화를 방지할 수 있는 반도체 장치 제조 방법 |

| JP3626115B2 (ja) * | 2001-06-14 | 2005-03-02 | 沖電気工業株式会社 | チタン化合物を含有するcvdチタン膜の形成方法 |

| KR100434698B1 (ko) * | 2001-09-05 | 2004-06-07 | 주식회사 하이닉스반도체 | 반도체소자의 선택적 에피성장법 |

| WO2004010480A1 (en) * | 2002-07-24 | 2004-01-29 | Applied Materials, Inc. | Apparatus and method for thermally isolating a heat chamber |

| KR100725098B1 (ko) * | 2005-11-17 | 2007-06-04 | 삼성전자주식회사 | 반도체 제조설비의 유량조절기 오동작 감지장치 및 그 방법 |

| US8362503B2 (en) * | 2007-03-09 | 2013-01-29 | Cree, Inc. | Thick nitride semiconductor structures with interlayer structures |

| JP5250470B2 (ja) * | 2009-04-22 | 2013-07-31 | 株式会社日立ハイテクノロジーズ | 試料ホールダ,該試料ホールダの使用法、及び荷電粒子装置 |

| WO2011013812A1 (ja) * | 2009-07-31 | 2011-02-03 | 株式会社 アルバック | 半導体装置の製造装置及び半導体装置の製造方法 |

| DE102011080202A1 (de) * | 2011-08-01 | 2013-02-07 | Gebr. Schmid Gmbh | Vorrichtung und Verfahren zur Herstellung von dünnen Schichten |

| US11942365B2 (en) * | 2017-06-02 | 2024-03-26 | Eugenus, Inc. | Multi-region diffusion barrier containing titanium, silicon and nitrogen |

| US10535527B2 (en) * | 2017-07-13 | 2020-01-14 | Applied Materials, Inc. | Methods for depositing semiconductor films |

| US20220084842A1 (en) * | 2020-09-11 | 2022-03-17 | Applied Materials, Inc. | Antifragile systems for semiconductor processing equipment using multiple special sensors and algorithms |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3211752C2 (de) * | 1982-03-30 | 1985-09-26 | Siemens AG, 1000 Berlin und 8000 München | Verfahren zum selektiven Abscheiden von aus Siliziden hochschmelzender Metalle bestehenden Schichtstrukturen auf im wesentlichen aus Silizium bestehenden Substraten und deren Verwendung |

| JPS59112611A (ja) * | 1982-12-17 | 1984-06-29 | Matsushita Electric Ind Co Ltd | 気相成長装置 |

| US4557943A (en) * | 1983-10-31 | 1985-12-10 | Advanced Semiconductor Materials America, Inc. | Metal-silicide deposition using plasma-enhanced chemical vapor deposition |

| US4629635A (en) * | 1984-03-16 | 1986-12-16 | Genus, Inc. | Process for depositing a low resistivity tungsten silicon composite film on a substrate |

| US4668530A (en) * | 1985-07-23 | 1987-05-26 | Massachusetts Institute Of Technology | Low pressure chemical vapor deposition of refractory metal silicides |

| US4647494A (en) * | 1985-10-31 | 1987-03-03 | International Business Machines Corporation | Silicon/carbon protection of metallic magnetic structures |

| GB2195663B (en) * | 1986-08-15 | 1990-08-22 | Nippon Telegraph & Telephone | Chemical vapour deposition method and apparatus therefor |

-

1990

- 1990-04-16 US US07/509,873 patent/US5104694A/en not_active Expired - Fee Related

- 1990-04-20 DE DE4013143A patent/DE4013143A1/de active Granted

- 1990-04-20 KR KR1019900005518A patent/KR940001885B1/ko not_active IP Right Cessation

- 1990-04-20 JP JP10287890A patent/JP2939500B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| DE4013143C2 (ko) | 1992-07-09 |

| DE4013143A1 (de) | 1990-10-31 |

| JP2939500B2 (ja) | 1999-08-25 |

| JPH03224223A (ja) | 1991-10-03 |

| US5104694A (en) | 1992-04-14 |

| KR900017107A (ko) | 1990-11-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR940001885B1 (ko) | 선택적 화학증착법(化學法, cvd법) 및 동법을 사용한 cvd장치 | |

| US4957777A (en) | Very low pressure chemical vapor deposition process for deposition of titanium silicide films | |

| US6245647B1 (en) | Method for fabrication of thin film | |

| US7166165B2 (en) | Barrier coating for vitreous materials | |

| US5942282A (en) | Method for depositing a titanium film | |

| US6383302B2 (en) | Apparatus and method for manufacturing semiconductor device | |

| JPS59177968A (ja) | 窒化チタンmosデバイスゲ−ト電極 | |

| EP0425090B1 (en) | Film deposition method and apparatus | |

| US20080226822A1 (en) | Precoat film forming method, idling method of film forming device, loading table structure, film forming device and film forming method | |

| JPS60200966A (ja) | 複合被膜 | |

| JPH1055973A (ja) | 半導体ディバイス製造装置及びこれを用いた多結晶シリコン膜の製造方法 | |

| Uhm et al. | TiN diffusion barrier grown by atomic layer deposition method for Cu metallization | |

| US6942892B1 (en) | Hot element CVD apparatus and a method for removing a deposited film | |

| US20060144336A1 (en) | Heater of chemical vapor deposition apparatus for manfuacturing a thin film | |

| Chiou et al. | Copper chemical vapor deposition from Cu (hexafluoroacetylacetonate) trimethylvinylsilane | |

| JP2001358077A (ja) | 薄膜作製装置 | |

| JP3194256B2 (ja) | 膜成長方法と膜成長装置 | |

| JP2002299259A (ja) | 薄膜形成方法 | |

| Bouteville et al. | Selective RTLPCVD of TiSi2 without substrate consumption | |

| JPH11326257A (ja) | 薄膜ガスセンサ | |

| JPH11222679A (ja) | Cvd装置および半導体装置の製造方法 | |

| KR940010412B1 (ko) | 박막형성방법 | |

| JPH10284421A (ja) | Cvd装置及びcvd装置用のサセプタ | |

| Westberg et al. | Laser-assisted chemical vapour deposition of TiSi2: aspects of deposition and etching | |

| JP2000323465A (ja) | 枚葉式減圧cvd方法及びその装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20030219 Year of fee payment: 10 |

|

| LAPS | Lapse due to unpaid annual fee |