KR20160136070A - 발광 소자 - Google Patents

발광 소자 Download PDFInfo

- Publication number

- KR20160136070A KR20160136070A KR1020150069775A KR20150069775A KR20160136070A KR 20160136070 A KR20160136070 A KR 20160136070A KR 1020150069775 A KR1020150069775 A KR 1020150069775A KR 20150069775 A KR20150069775 A KR 20150069775A KR 20160136070 A KR20160136070 A KR 20160136070A

- Authority

- KR

- South Korea

- Prior art keywords

- electrode

- pattern

- semiconductor layer

- light emitting

- connection groove

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/831—Electrodes characterised by their shape

- H10H20/8314—Electrodes characterised by their shape extending at least partially onto an outer side surface of the bodies

-

- H01L33/36—

-

- H01L33/12—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/831—Electrodes characterised by their shape

- H10H20/8312—Electrodes characterised by their shape extending at least partially through the bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/831—Electrodes characterised by their shape

- H10H20/8316—Multi-layer electrodes comprising at least one discontinuous layer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/85—Packages

- H10H20/857—Interconnections, e.g. lead-frames, bond wires or solder balls

-

- H01L2924/12041—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/032—Manufacture or treatment of electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/811—Bodies having quantum effect structures or superlattices, e.g. tunnel junctions

- H10H20/812—Bodies having quantum effect structures or superlattices, e.g. tunnel junctions within the light-emitting regions, e.g. having quantum confinement structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/819—Bodies characterised by their shape, e.g. curved or truncated substrates

- H10H20/82—Roughened surfaces, e.g. at the interface between epitaxial layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/822—Materials of the light-emitting regions

- H10H20/824—Materials of the light-emitting regions comprising only Group III-V materials, e.g. GaP

- H10H20/825—Materials of the light-emitting regions comprising only Group III-V materials, e.g. GaP containing nitrogen, e.g. GaN

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/832—Electrodes characterised by their material

- H10H20/835—Reflective materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/84—Coatings, e.g. passivation layers or antireflective coatings

Landscapes

- Led Devices (AREA)

Abstract

Description

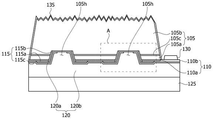

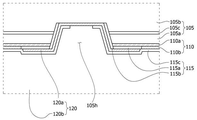

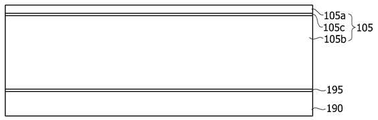

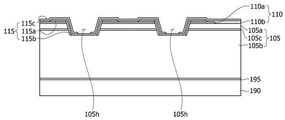

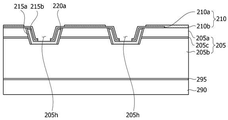

도 1b는 도 1a의 A 영역의 확대도이다.

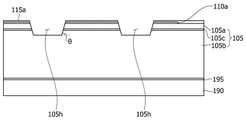

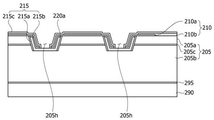

도 2는 일반적인 발광 소자의 단면도이다.

도 3a는 제 1 전극과 제 2 전극의 간격에 따른 구동 전압을 나타낸 그래프이다.

도 3b는 제 1 전극과 제 2 전극의 간격에 따른 광 출력을 나타낸 그래프이다.

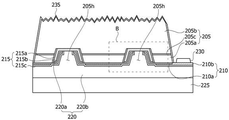

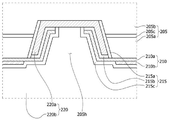

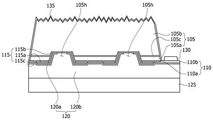

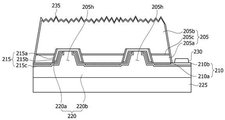

도 4a는 본 발명 다른 실시 예의 발광 소자의 단면도이다.

도 4b는 도 4a의 B 영역의 확대도이다.

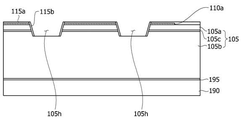

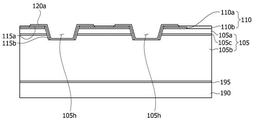

도 5a 내지 도 5i는 본 발명 실시 예의 발광 소자의 제조 방법을 나타낸 공정 단면도이다.

도 6a 내지 도 6i는 본 발명 다른 실시 예의 발광 소자의 제조 방법을 나타낸 공정 단면도이다.

도 7은 본 발명 실시 예의 발광 소자를 포함하는 발광 소자 패키지의 단면도이다.

20b: 제 2 리드 프레임 25: 와이어

30: 몰딩부 100: 발광 소자

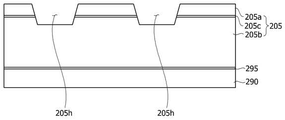

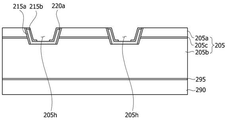

105, 205: 발광 구조물 105a, 205a: 제 1 반도체층

105b, 205b: 제 2 반도체층 105c, 205c: 활성층

105h, 205h: 접속 홈 110, 210: 제 1 전극

110a, 210a: 제 1 전극 패턴 110b, 210b: 제 2 전극 패턴

115, 215: 절연 패턴 115a, 215a: 제 1 절연 패턴

115b, 215b: 제 2 절연 패턴 115c, 215c: 제 3 절연 패턴

120, 220: 제 2 전극 120a, 220a: 콘택 전극

120b, 220b: 본딩 전극 125, 225: 지지 기판

130, 230: 전극 패드 135, 235: 보호층

190, 290: 베이스 기판 195, 295: 분리층

Claims (20)

- 지지 기판;

상기 지지 기판 상에 배치되며, 제 1 반도체층, 활성층 및 제 2 반도체층을 포함하는 발광 구조물;

상기 발광 구조물이 제거되어 상기 제 2 반도체층을 노출시키는 바닥면과 상기 제 1 반도체층, 활성층 및 제 2 반도체층을 노출시키는 측면을 포함하는 복수 개의 접속 홈;

상기 제 1 반도체층과 접촉하도록 상기 발광 구조물 상에 배치되며, 끝단이 상기 접속 홈의 가장자리까지 연장된 제 1 전극 패턴 및 상기 제 1 전극 패턴 상에 배치된 제 2 전극 패턴을 포함하는 제 1 전극;

상기 접속 홈의 바닥면 및 측면을 감싸도록 상기 제 1 반도체층의 상부면까지 연장된 콘택 전극 및 복수 개의 상기 콘택 전극과 연결된 본딩 전극을 포함하는 제 2 전극; 및

상기 제 1 전극과 상기 제 2 전극 사이에 배치된 절연 패턴을 포함하는 발광 소자. - 제 1 항에 있어서,

상기 절연 패턴은 상기 제 1 반도체층 상에서 상기 콘택 전극과 상기 제 1 전극 패턴 사이에 배치된 제 1 절연 패턴;

상기 접속 홈의 측면에서 상기 콘택 전극과 상기 제 1 전극 패턴 사이에 배치된 제 2 절연 패턴; 및

상기 발광 구조물 상에서 상기 본딩 전극과 상기 제 2 전극 패턴 사이에 배치된 제 3 절연 패턴을 포함하는 발광 소자. - 제 2 항에 있어서,

상기 콘택 전극과 상기 제 1 전극 패턴은 상기 제 1 반도체층 상에서 상기 제 1 절연 패턴을 사이에 두고 중첩되는 발광 소자. - 제 2 항에 있어서,

상기 접속 홈의 가장자리에서 상기 제 1 전극 패턴과 상기 제 1 절연 패턴이 상기 제 2 절연 패턴과 접촉하는 발광 소자. - 제 2 항에 있어서,

상기 콘택 전극과 상기 제 1 전극 패턴, 상기 콘택 전극과 상기 활성층 및 상기 콘택 전극과 상기 제 1 반도체층은 상기 제 2 절연 패턴을 통해 서로 절연된 발광 소자. - 제 2 항에 있어서,

상기 제 3 절연 패턴이 상기 접속 홈 내부의 상기 콘택 전극을 노출시켜, 상기 콘택 전극과 상기 본딩 전극이 상기 접속 홈 내부에서 전기적으로 연결된 발광 소자. - 제 2 항에 있어서,

상기 제 3 절연 패턴은 상기 접속 홈 내부의 상기 콘택 전극을 노출시키며 상기 제 1 전극의 하부면 전면에 배치된 발광 소자. - 제 1 항에 있어서,

상기 접속 홈의 상기 측면과 상기 바닥면 사이의 경사각이 60°이상이며 90°이하인 발광 소자. - 제 1 항에 있어서,

상기 제 1 전극 패턴은 상기 활성층에서 발생한 광을 상기 제 2 반도체층으로 반사시키는 반사층인 발광 소자. - 제 1 항에 있어서,

상기 지지 기판은 상기 제 2 전극과 전기적으로 연결된 발광 소자. - 지지 기판;

상기 지지 기판 상에 배치되며, 제 1 반도체층, 활성층 및 제 2 반도체층을 포함하는 발광 구조물;

상기 발광 구조물이 제거되어 상기 제 2 반도체층을 노출시키는 바닥면과 상기 제 1 반도체층, 활성층 및 제 2 반도체층을 노출시키는 측면을 포함하는 복수 개의 접속 홈;

상기 제 1 반도체층과 전기적으로 연결되며, 상기 접속 홈의 내부까지 연장된 제 1 전극 패턴 및 상기 제 1 전극 패턴 상에 배치된 제 2 전극 패턴을 포함하는 제 1 전극;

상기 접속 홈의 바닥면 및 측면을 감싸도록 상기 접속 홈의 가장자리까지 연장된 콘택 전극 및 복수 개의 상기 콘택 전극과 연결된 본딩 전극을 포함하는 제 2 전극; 및

상기 제 1 전극과 상기 제 2 전극 사이에 배치된 절연 패턴을 포함하는 발광 소자. - 제 11 항에 있어서,

상기 제 1 전극 패턴과 상기 콘택 전극은 상기 접속 홈 내부에서 상기 절연 패턴을 사이에 두고 서로 중첩되는 발광 소자. - 제 11 항에 있어서,

상기 절연 패턴은 상기 접속 홈의 측면에서 상기 발광 구조물과 상기 콘택 전극 사이에 배치된 제 1 절연 패턴;

상기 제 1 전극 패턴과 상기 콘택 전극 사이에 배치된 제 2 절연 패턴; 및

상기 발광 구조물 상에서 상기 본딩 전극과 상기 제 1 전극 사이에 배치된 제 3 절연 패턴을 포함하는 발광 소자. - 제 13 항에 있어서,

상기 콘택 전극과 상기 활성층 및 상기 콘택 전극과 상기 제 1 반도체층은 상기 제 1 절연 패턴을 통해 서로 절연된 발광 소자. - 제 13 항에 있어서,

상기 콘택 전극의 끝단은 상기 접속 홈의 가장자리에서 상기 제 1 절연 패턴과 상기 제 2 절연 패턴에 의해 감싸진 발광 소자. - 제 13 항에 있어서,

상기 제 2 절연 패턴과 제 3 절연 패턴이 상기 접속 홈의 바닥면에서 상기 콘택 전극을 노출시켜, 상기 콘택 전극과 상기 본딩 전극이 상기 접속 홈 내부에서 전기적으로 연결된 발광 소자. - 제 13 항에 있어서,

상기 제 3 절연 패턴은 상기 접속 홈 내부의 상기 콘택 전극을 노출시키며 상기 제 1 전극의 하부면 전면에 배치된 발광 소자. - 제 11 항에 있어서,

상기 접속 홈의 상기 측면과 상기 바닥면 사이의 경사각이 60°이상이며 90°이하인 발광 소자. - 제 11 항에 있어서,

상기 제 1 전극 패턴은 상기 활성층에서 발생한 광을 상기 제 2 반도체층으로 반사시키는 반사층인 발광 소자. - 제 11 항에 있어서,

상기 지지 기판은 상기 제 2 전극과 전기적으로 연결된 발광 소자.

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150069775A KR102371326B1 (ko) | 2015-05-19 | 2015-05-19 | 발광 소자 |

| CN201680029225.7A CN107636846B (zh) | 2015-05-19 | 2016-04-22 | 发光元件 |

| PCT/KR2016/004245 WO2016186330A1 (ko) | 2015-05-19 | 2016-04-22 | 발광 소자 |

| US15/575,242 US10333029B2 (en) | 2015-05-19 | 2016-04-22 | Light-emitting element |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020150069775A KR102371326B1 (ko) | 2015-05-19 | 2015-05-19 | 발광 소자 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20160136070A true KR20160136070A (ko) | 2016-11-29 |

| KR102371326B1 KR102371326B1 (ko) | 2022-03-07 |

Family

ID=57320412

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020150069775A Expired - Fee Related KR102371326B1 (ko) | 2015-05-19 | 2015-05-19 | 발광 소자 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US10333029B2 (ko) |

| KR (1) | KR102371326B1 (ko) |

| CN (1) | CN107636846B (ko) |

| WO (1) | WO2016186330A1 (ko) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102018124341B4 (de) * | 2018-10-02 | 2024-05-29 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Bauelement mit vergrößerter aktiver Zone und Verfahren zur Herstellung |

| CN112038883B (zh) * | 2020-10-29 | 2021-05-28 | 锐驰智光(北京)科技有限公司 | 激光发射模块及具有此的激光雷达 |

| CN112711008B (zh) * | 2021-03-26 | 2021-06-25 | 锐驰智光(北京)科技有限公司 | 激光发射模块及具有此的激光雷达 |

| US20250228042A1 (en) * | 2024-01-08 | 2025-07-10 | Lumileds Llc | Light emitting devices having aluminum indium gallium phosphide die with embedded contacts |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20110102630A (ko) * | 2010-03-11 | 2011-09-19 | 삼성엘이디 주식회사 | 질화물 반도체 발광소자 및 그 제조방법 |

| KR20110136111A (ko) * | 2010-06-14 | 2011-12-21 | 서울옵토디바이스주식회사 | 발광 소자 및 그것을 제조하는 방법 |

| JP2013201411A (ja) * | 2012-02-24 | 2013-10-03 | Stanley Electric Co Ltd | 半導体発光装置 |

| US20140209952A1 (en) * | 2010-03-31 | 2014-07-31 | Seoul Viosys Co., Ltd. | High efficiency light emitting diode and method for fabricating the same |

| KR20140102509A (ko) * | 2013-02-14 | 2014-08-22 | 엘지이노텍 주식회사 | 발광소자, 발광소자 패키지 및 라이트 유닛 |

| WO2014195420A1 (de) * | 2013-06-06 | 2014-12-11 | Osram Opto Semiconductors Gmbh | Leuchtdiode mit passivierungsschicht |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3322300B2 (ja) | 1997-11-14 | 2002-09-09 | 日亜化学工業株式会社 | 窒化ガリウム系半導体発光素子と受光素子 |

| JP6023660B2 (ja) * | 2013-05-30 | 2016-11-09 | スタンレー電気株式会社 | 半導体発光素子及び半導体発光装置 |

| KR20160149363A (ko) * | 2015-06-17 | 2016-12-28 | 삼성전자주식회사 | 반도체 발광소자 |

-

2015

- 2015-05-19 KR KR1020150069775A patent/KR102371326B1/ko not_active Expired - Fee Related

-

2016

- 2016-04-22 WO PCT/KR2016/004245 patent/WO2016186330A1/ko not_active Ceased

- 2016-04-22 CN CN201680029225.7A patent/CN107636846B/zh active Active

- 2016-04-22 US US15/575,242 patent/US10333029B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20110102630A (ko) * | 2010-03-11 | 2011-09-19 | 삼성엘이디 주식회사 | 질화물 반도체 발광소자 및 그 제조방법 |

| US20140209952A1 (en) * | 2010-03-31 | 2014-07-31 | Seoul Viosys Co., Ltd. | High efficiency light emitting diode and method for fabricating the same |

| KR20110136111A (ko) * | 2010-06-14 | 2011-12-21 | 서울옵토디바이스주식회사 | 발광 소자 및 그것을 제조하는 방법 |

| JP2013201411A (ja) * | 2012-02-24 | 2013-10-03 | Stanley Electric Co Ltd | 半導体発光装置 |

| KR20140102509A (ko) * | 2013-02-14 | 2014-08-22 | 엘지이노텍 주식회사 | 발광소자, 발광소자 패키지 및 라이트 유닛 |

| WO2014195420A1 (de) * | 2013-06-06 | 2014-12-11 | Osram Opto Semiconductors Gmbh | Leuchtdiode mit passivierungsschicht |

Also Published As

| Publication number | Publication date |

|---|---|

| KR102371326B1 (ko) | 2022-03-07 |

| WO2016186330A1 (ko) | 2016-11-24 |

| US10333029B2 (en) | 2019-06-25 |

| CN107636846B (zh) | 2020-06-16 |

| CN107636846A (zh) | 2018-01-26 |

| US20180138366A1 (en) | 2018-05-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10411166B2 (en) | Light emitting device and lighting apparatus | |

| US8450762B2 (en) | Light emitting device | |

| US7919784B2 (en) | Semiconductor light-emitting device and method for making same | |

| KR101752663B1 (ko) | 발광소자 및 발광소자 제조방법 | |

| KR101014071B1 (ko) | 발광 소자, 발광 소자 제조방법, 발광 소자 패키지 및 조명 시스템 | |

| KR101034144B1 (ko) | 발광 소자, 발광 소자 제조방법, 발광 소자 패키지 및 조명 시스템 | |

| US20110084306A1 (en) | Semiconductor light emitting device | |

| JP2011519161A (ja) | 半導体発光素子 | |

| KR101769048B1 (ko) | 발광 소자, 이를 포함하는 발광소자 패키지 및 조명 장치 | |

| KR101803569B1 (ko) | 발광 소자 | |

| KR20170083353A (ko) | 발광소자 | |

| US10333029B2 (en) | Light-emitting element | |

| CN108431970B (zh) | 发光元件 | |

| US9741903B2 (en) | Light-emitting device and light emitting device package having the same | |

| KR102371327B1 (ko) | 발광 소자 | |

| KR101826979B1 (ko) | 발광 소자 및 발광 소자 패키지 | |

| US10236417B2 (en) | Light-emitting element | |

| KR101776302B1 (ko) | 발광 소자 및 발광 소자 패키지 | |

| KR20170095675A (ko) | 발광 소자 | |

| KR102234117B1 (ko) | 발광소자 및 조명시스템 | |

| KR20120037100A (ko) | 발광 소자 및 발광 소자 패키지 | |

| KR101710889B1 (ko) | 발광 소자 | |

| KR20170105996A (ko) | 발광 소자 | |

| KR101786081B1 (ko) | 발광 소자 및 발광 소자 패키지 | |

| KR20110118380A (ko) | 발광 소자, 발광 소자 제조방법, 발광 소자 패키지, 조명 시스템 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-2-2-P10-P22-nap-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| A201 | Request for examination | ||

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| N231 | Notification of change of applicant | ||

| PN2301 | Change of applicant |

St.27 status event code: A-3-3-R10-R13-asn-PN2301 St.27 status event code: A-3-3-R10-R11-asn-PN2301 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20250303 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| H13 | Ip right lapsed |

Free format text: ST27 STATUS EVENT CODE: N-4-6-H10-H13-OTH-PC1903 (AS PROVIDED BY THE NATIONAL OFFICE); TERMINATION CATEGORY : DEFAULT_OF_REGISTRATION_FEE Effective date: 20250303 |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20250303 |