KR20130139829A - 컴퓨터 시스템들의 지능형 유연 관리 및 감시를 위한 시스템들 및 방법들 - Google Patents

컴퓨터 시스템들의 지능형 유연 관리 및 감시를 위한 시스템들 및 방법들 Download PDFInfo

- Publication number

- KR20130139829A KR20130139829A KR1020137000400A KR20137000400A KR20130139829A KR 20130139829 A KR20130139829 A KR 20130139829A KR 1020137000400 A KR1020137000400 A KR 1020137000400A KR 20137000400 A KR20137000400 A KR 20137000400A KR 20130139829 A KR20130139829 A KR 20130139829A

- Authority

- KR

- South Korea

- Prior art keywords

- computer system

- power

- computer

- information

- systems

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/30—Monitoring

- G06F11/3058—Monitoring arrangements for monitoring environmental properties or parameters of the computing system or of the computing system component, e.g. monitoring of power, currents, temperature, humidity, position, vibrations

- G06F11/3062—Monitoring arrangements for monitoring environmental properties or parameters of the computing system or of the computing system component, e.g. monitoring of power, currents, temperature, humidity, position, vibrations where the monitored property is the power consumption

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/22—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/18—Packaging or power distribution

- G06F1/181—Enclosures

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/18—Packaging or power distribution

- G06F1/183—Internal mounting support structures, e.g. for printed circuit boards, internal connecting means

- G06F1/184—Mounting of motherboards

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/18—Packaging or power distribution

- G06F1/183—Internal mounting support structures, e.g. for printed circuit boards, internal connecting means

- G06F1/185—Mounting of expansion boards

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/16—Constructional details or arrangements

- G06F1/18—Packaging or power distribution

- G06F1/189—Power distribution

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/263—Arrangements for using multiple switchable power supplies, e.g. battery and AC

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/30—Monitoring

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/30—Monitoring

- G06F11/3003—Monitoring arrangements specially adapted to the computing system or computing system component being monitored

- G06F11/3031—Monitoring arrangements specially adapted to the computing system or computing system component being monitored where the computing system component is a motherboard or an expansion card

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

Abstract

컴퓨터 시스템들의 지능형 유연 관리 및 감시를 위한 시스템들 및 방법들은 컴퓨터 시스템의 회로 기판들 상에 위치된 플랫폼 관리 컨트롤러들(PMC들)을 사용하여 제공된다. PMC들은 증대된 회로 기판 인증 및 보안, 증대된 시스템들 감시 및 보고, 및 증대된 시스템들 제어를 제공한다. PMC들은 또한 프로세서 기반 디바이스들의 에뮬레이션을 가능하게 하고 교체된 디바이스들 및 제공된 기능성에 비해서 저전력이고, 저비용이며 매우 빠르다. 전원 트래킹 장치는 연산 회로의 제 1 전력 입력이 연산 회로의 제 2 전력 입력에 대해 미리 정의된 관계를 유지하는 것을 보증하는데 도움이 된다. 컴퓨터 시스템들 진단 정보를 수신하고 진단 감시 디바이스로부터 그러한 정보를 커스터마이즈가능하게 표시하기 위한 시스템들 및 방법들은 컴퓨터 시스템에 통합된다. 감시된 컴퓨터 시스템 정보는 예컨대 적외선에 의해 또는 새로운 일시적 유선 연결에 의해 진단 ㄷ디바이스에 송신된다.

Description

관련 출원들에 대한 상호 참조

본 출원은 2011년 6월 6일자로 출원되고 발명의 명칭이 "SYSTEMS AND METHODS FOR INTELLIGENT AND FLEXIBLE MANAGEMENT OF AND MONITORING OF COMPUTER SYSTEMS"인 미국 특허 출원 제13/154,436호의 이익을 주장하고, 2010년 6월 7일자로 출원되고 발명의 명칭이 "Systems and Methods for Intelligent and Flexible Management and Monitoring of Computer Systems"인 미국 특허 가출원 제61/352,362호, 2010년 6월 7일자로 출원되고 발명의 명칭이 "Tracking Apparatus"인 미국 특허 가출원 제61/352,357호, 2010년 6월 7일자로 출원되고 발명의 명칭이 "Systems and Methods for Wirelessly Receiving Computer System Diagnostics Information"인 미국 특허 가출원 제61/352,381호, 및 2010년 6월 7일자로 출원되고 발명의 명칭이 "Systems and Methods for Providing Connectivity"인 미국 특허 가출원 제61/352,379호의 이익을 주장하며, 이로써 모든 발명을 위해 그 전체들의 참조에 의해 이전 가출원들 각각을 참고문헌으로 통합한다. 게다가, 본 출원은 참조된 가출원들의 참조에 의해 통합된 추가 출원들 및 특허들 각각을 모든 발명을 위해 그 전체들의 참고문헌으로 통합한다.

본 발명은 컴퓨터 시스템들의 지능형 유연 관리 및 감시를 위한 시스템들 및 방법들에 관한 것으로, 특히 컴퓨터 시스템 동작을 유연하게 감시 및 관리하고 외부 사용을 위해 컴퓨터 시스템 동작에 관한 정보를 송신 및 수신하는 시스템들 및 방법들에 관한 것이다.

컴퓨터 시스템들은 이러한 증가하는 복잡성의 다양한 결과로써 점점 복잡해지고 있다. 증가하는 복잡성의 하나의 결과는 문제들이 발생할 때 컴퓨터 시스템들 내에서 문제들을 진단하는 것이 보다 어려워진다는 점이다. 컴퓨터 시스템의 한 부분에 있어서의 문제들이 컴퓨터 시스템의 다른 부분들에 있어서의 손상 또는 문제들을 일으키는 것을 방지하는 방식으로 컴퓨터 시스템들을 정확하게 관리하는 것도 보다 어려워진다.

진단들을 요구할 수 있는 문제들을 포함하는 컴퓨터 시스템들에 있어서의 문제들은, 그 수명 중 임의의 시간에서 발생할 수 있고, 또한 문제들의 가능성은 컴퓨터 시스템들의 복잡성에 있어서 증가되고 있다. 다양한 문제들은 제조시에 최초로 발생할 수 있다. 그러한 문제들은 제조시에 적절히 검출되어야 하거나, 또는 제조업자는 고객 불만족 및 고객 이탈의 위험을 각오할 수 있다. 다른 문제들은 컴퓨터 시스템들의 사용 중 나중에 발생하고, 컴퓨터 시스템들의 기능을 감소시키거나 완전히 손상할 수 있다. 컴퓨터 시스템들의 제조시 및 사용중 모두에서의 컴퓨터 시스템에 있어서의 문제들을 검출하고 처리하기 위한 현재의 방법들은 불충분하다.

컴퓨터 시스템들의 발전 및 복잡성에 의해 기인되는 다른 어려움은 컴퓨터 기술의 어떤 측면들의 구식화의 결과이다. 컴퓨터 기술의 어떤 측면들이 점점 구식화됨에 따라, 컴퓨터 기술의 보다 오래된 측면들을 최적으로 처리하는 방법을 결정하는 것이 어려워진다. 컴퓨터 시스템들의 복잡성 때문에, 의도하지 않은 현저한 문제들이 컴퓨터 시스템에 발생하게 하지 않게 컴퓨터 시스템들로부터 노후한 기술을 제거하는 것조차 어려울 수 있다. 그러므로, 노후한 및 사용하지 않는 기술들은 기술들을 안전하게 제거하는 데 관련된 작업이 바람직하다고 간주되지 않기 때문에 컴퓨터 시스템들 및 운영 시스템들 내에 남아있다. 안타깝게, 노후한 기술을 충분히 처리하는 데 실패한 결과는 불필요하게 보다 비용이 많이 드는 시스템들 및 보다 느리게 동작하는 컴퓨터 시스템들을 포함한다.

상기 논의된 어려움들은 컴퓨터 문제들을 진단하고 처리하기 위한 전통적인 자원들로부터 떨어진 위치들에 위치될 수 있는 내장 시스템들 내에서 더 악화될 수 있다. 내장 시스템들에 대한 필요가 증가함에 따라, 그러한 문제들을 처리하기 위한 메커니즘들에 대한 필요만이 증가할 것이다. 따라서, 다른 기술로서 현재 기술을 발전시키는 것 및 다른 기술로 현재 기술을 대체하는 것도 본 기술 분야에서 개선이 될 것이다.

전자 시스템들, 및 특히 컴퓨터 시스템들은 유니쿼터스(ubiquitous)화되고 있다. 기능을 위해, 전자 시스템들은 입력 전력을 요구한다. 전자 시스템들은 종종 전원을 포함하고, 그것은 미가공 입력 전력(예를 들어, 상업적 메인(main)들로부터 공급되는 교류)을 시스템 내에 필수적인 내부 공급 전압들(예를 들어, 5 볼트, 3.3 볼트 등과 같은, 직류 전압)로 변환한다.

증가된 전력 소비가 증가된 열 및 동작 비용으로 이어짐에 따라, 전자 시스템들 내의 전력 소비가 고려 사항이 되고 있다. 따라서, 많은 전자 시스템들 내에서 전력 소비를 감소시키기 위한 노력이 존재해 왔다. 전력 소비를 감소시키기 위한 하나의 기술은 보다 낮은 전압들을 사용하는 것이다. 예를 들어, 디지털 로직 시스템(digital logic system)들에 대해 5 볼트 전원들의 사용은 다년간 표준이었다. 트렌드들은 3.3 볼트, 2.5, 볼트, 및 심지어 1.8 볼트와 같은, 보다 낮은 전압들을 사용해 왔다. 또한, 전력 소비를 감소시키는 것뿐만 아니라, 보다 낮은 전압들의 사용은 부가적인 이점들 제공해왔다.

일부 경우들에서, 전자 회로(예를 들어, 집적 회로 내에서)는 적절히 동작하기 위해 다중 전압들을 요구한다. 예를 들어, 일부 집적 회로들은 내부 회로에 전력을 공급하기 위해 상대적으로 낮은 전압들(예를 들어, 1.8 볼트)을 사용하지만, 입력/출력 회로는 보다 높은 전압(예를 들어, 3.3 볼트)에서 동작한다. 일부 집적 회로들은 2개 이상의 상이한 전압들의 조합을 사용할 수 있다.

불행하게도, 다중 전압들을 요구하는 집적 회로들은 보통 전압들의 상대적인 값에 대해 다수의 규칙들 또는 제약을 두고 있다. 그러한 제약들은 파워 업(power up) 또는 파워 다운(power down) 시퀀싱(sequencing) 동안 적용될 수 있다. 불행하게도, 전원들은 시간의 한정된 기간을 넘어 램프 업(ramp up)되는 경향이 있고, 따라서 그러한 제약들이 파워 업 또는 파워 다운 동안 유지되는 것을 보장하는 것은 어려울 수 있다. 전력 제약들의 위반은 부정확한 동작(예를 들어, 래치 업(latch-up)으로 인한) 또는 심지어 집적 회로들의 고장(예를 들어, 부적절한 순방향 바이어스 접합(forward-biased junction)들을 통한 오버 전류로 인한)을 발생시킬 수 있다.

구체적 예로서는, 모두 3.3 볼트 및 1.8 볼트를 사용하여 동작하고 (1) 3.3 볼트 전력 입력은 1.8 볼트 전력 입력보다 항상 높아야 하고, (2) 3.3 볼트 전력 입력은 1.8 볼트 전력 입력보다 높고 2.1 볼트 이상일 수 없는 것을 요구하는 디바이스(device)를 고려한다. 3.3 볼트 전력 입력이 너무 느리게 램프 업하면, 그것은 1.8 볼트 전력 입력보다 뒤떨어질 수 있고, 제 1 요건을 위반할 수 있다. 반대로, 3.3 볼트 전력 입력이 너무 빨리 램프 업하면, 그것은 1.8 볼트 전력 입력을 너무 앞설 수 있고, 제 2 요건을 위반할 수 있다.

고장이 발생하는 경우, 요구된 제약들을 유지하는 것이 훨씬 더 어려울 수 있다. 예를 들어, 다중 전압들을 발생시키는 다중 전원들을 갖는 시스템에서, 하나의 전원의 고장은 수개의 제약들의 동시 또는 일련의 위반을 발생시킬 수 있다.

일부 집적 회로 제조업자들은 제약들의 일부가 충족되는 것을 보증하는 전원들의 시퀀싱을 제어하는 소위 "기준(reference)" 설계들을 제공해왔다. 그러나 일부 기준 설계들은, 제약들이 모든 가능한 동작 시나리오(scenario)들에서 충족되는 것을 보증하지 못한다. 더욱이, 대부분의 기준 설계들은 제조 환경들에 대해 최적화되지 않는다. 전형적으로, 기준 설계들은 많은 수의 구성요소들을 포함하고, 대량의 보드(board) 영역을 요구하고, 디버깅(debugging)하는데 상대적으로 복잡하다. 더욱이, 일부 경우들에서, 기준 설계들은 부가적인 집적 회로들이 동일한 집적 회로 제조업자로부터 구입되는 것을 요구한다.

전자 컴퓨터 시스템들 내에서의 고장의 가장 일반적인 유형은 전원들 내에서의 고장이라는 것을 발명자들은 경험해 왔다. 다중 전원들을 요구하는 전자 시스템에서(예를 들어, 컴퓨터 시스템), 하나의 전원의 고장은 시스템 내에 일부 집적 회로들에 대한 전력 제약들의 위반을 발생시킬 수 있다. 이는 집적 회로들의 고장들을 일으킬 수 있고, 심지어 일련의 단계적인 고장을 일으킨다. 따라서, 다른 기술로서 현재 기술을 발전시키는 것 및 다른 기술로 현재 기법을 대체하는 것도 본 기술 분야에서 개선일 것이다.

인쇄 회로 기판들(PCB: printed circuit boards)은 다른 전기 디바이스들 뿐만 아니라 많은 컴퓨터 로직 시스템들로 이루어진 기반의 핵심 구성요소이다. 제조 프로세스 동안, PCB들은 프로그램(program)되거나, 디버깅되거나 또는 그 외 데이터(data)를 송신 또는 수신하기 위해 통신될 수 있다. 이러한 프로세스 동안 PCB와 연관된 디바이스들 사이에 일정한 연결을 용이하게 하기 위해, PCB들은 보통 나중에 스냅 오프(snap off)되거나 그 외 제거될 수 있는 탭(tab)을 가지므로, PCB는 보다 큰 컴퓨터 또는 전기 시스템 내에 편리하게 설치될 수 있다. 그러나 제거에 앞서, 탭은 프로그래밍 및 디버깅을 용이하게 하기 위해 PCB와 연관된 외부 제조 디바이스들 사이의 반영구적인 연결을 용이하게 하도록 사용된다. 대안적으로, PCB는 프로그램되거나, 디버깅되거나 또는 그 외 복잡한 자동화된 디바이스들을 통해 통신될 수 있고, 그것은 PCB 상의 동시에 수많은 위치들에 전기적으로 접촉한다. PCB의 비용을 감소시키기 위해 및 많은 최종 사용자들이 현장에서 추가로 PCB를 프로그래밍하지 않기 때문에, 제조시, 프로그래밍 커넥터들은 전형적으로 PCB 상에 포함되지 않는다.

그러나, 최초 제조 프로세스 다음에, 많은 목적들 또는 이유들을 위해 PCB와 통신하도록 PCB에 일시적으로 연결되는 것이 때때로 바람직하다. 예를 들어, 부가적인 또는 대안적인 프로그래밍을 업로드(upload)하도록 PCB와 통신하는 것, PCB를 추가로 디버깅하는 것, PCB를 진단 및/또는 수리하는 것 또는 그 외 PCB와 연관된 데이터를 송신 또는 수신하도록 PCB와 통신하는 것이 바람직할 수 있다. 그러나, 상기 논의된 바와 같이 탭의 제거 다음에 및 정교한 자동화의 부재시, 일시적으로 PCB와 연결됨으로써 PCB와 직접 통신하는 것은 어렵다. 그 결과로서, 다양한 포트(port)들 또는 다른 전자 커넥터들이 PCB 상에 종종 땜납되어, 외부 디바이스들은 PCB의 포트들 또는 전기 커넥터들에서 적절한 와이어(wire)들 및 상응하는 커넥터들을 통해 PCB에 편리하게 연결될 수 있다. 예를 들어, PCB 포트 또는 커넥터는 표준 전기 "수(male)" 구성요소일 수 있고, PCB에 연결되도록 의도된 디바이스는 상응하는 표준 "암(female)" 구성요소 또는 그 위에 칼라(collar)를 갖는 와이어가 구비될 수 있다(역 또한 가능). "암" 칼라가 "수" 구성요소와 짝을 이루므로, PCB는 효과적으로 접촉되고 통신될 수 있다.

다양한 포트들 및 커넥터들을 갖는 PCB를 구비하는 것은 PCB와 다른 외부 디바이스들 사이에 일시적으로 통신을 용이하게 하도록 작용하지만, PCB에 땜납된 포트들 또는 커넥터들은, 원하는 연결이 완료된 후 일반적으로 방치된다. 이는 증가된 비용들을 발생시킨다. 이러한 비용들은 다중 포트들 또는 커넥터들이 가변적 목적들을 위한 연결들을 용이하게 하도록 종종 요구되고-종종 방치된 다중 포트들/커넥터들을 발생시킨다는 사실로 인해 증가된다. 게다가, 현대 기술에서 공통적인 점점 작은 컴퓨팅 및 전기 디바이스들에 있어서, 연관 디바이스 내에 설치될 때, 소정의 PCB 상에 보유된 부피가 큰 또는 공간 소비적인 포트들/커넥터들을 갖는 것은 종종 바람직하지 않다. 그러나, 포트들/커넥터들의 제거는 PCB에 대한 손상을 발생시키고, 마찬가지로 나중에 필요하면 또는 원한다면, PCB가 추가의 프로그래밍, 디버깅 및 기타 동등한 것을 위해 현장에서 차후에 연결될 수 있는 편리성을 감소시킨다.

PCB의 포트들/커넥터들이 그대로 방치된다면, 부가적인 단점이 존재한다. 복잡하거나 정교한 PCB들에서 특정 목적을 완수하도록 적절한 포트 또는 커넥터와 위치하는 것 및/또는 짝을 이루는 것이 종종 부담스럽거나 어려울 수 있다. 게다가, 최종 사용자가 PCB에 연결하는 것을 원한다면, 연관된 와이어링 및 상응하는 커넥터는 사용자에게 부가적인 비용들을 필수적으로 발생시킨다. 그러한 비용들은 상당할 수 있다. 게다가, 그들을 짝을 이루도록 시도할 시 사용자가 PCB 포트/커넥터 또는 상응하는 와이어링 또는 커넥터를 손상한다면, 이는 부가적인 비용들을 발생시킬 수 있다. 궁극적으로, 현재 기법들 하에서 제조 프로세스가 완료된 후 PCB에 연결하는 것과 관련된 비용들은 최소한, 두 개의 커넥터들 즉, PCB 상에 하나 및 와이어 상에 다른 하나를 포함한다. 사용자가 임의의 실수들을 행한다면, 비용들은 상당히 상승한다.

본 발명의 구현은 컴퓨터 시스템들 및 컴퓨터 시스템 동작의 다양한 측면들의 지능형 유연 관리 및 감시를 위한 시스템들 및 방법들을 제공한다. 본 발명의 구현들은 다양한 범용 컴퓨터 시스템들 및 다양한 특수 용도 컴퓨터 시스템들을 포함하는, 다양한 기존 및 장래의 컴퓨터 시스템들에 적용가능하다. 본 발명이 다양한 방법들로 구현될 수 있는 컴퓨터 시스템의 하나의 분류 또는 구성은 발명의 명칭이 Non-Peripherals Processing Control Module Having Improved Heat Dissipating Properties인 미국 특허 제7,256,991호, 발명의 명칭이 Robust Customizable Computer Processing System인 제7,242,574호, 및 발명의 명칭이 Systems and Methods for Providing a Dynamically Modular Processing Unit인 제7,075,784호에 개시되어 있으며, 그들은 모든 발명을 위해 본 출원에 참고문헌으로 명백히 통합되어 있다.

복수의 상호 접속 회로 기판들을 갖고 사용하도록 구성된 컴퓨터 시스템에서, 본 발명의 어떤 구현들은 인증된 회로 기판들만이 컴퓨터 시스템에 사용되는 것을 보증하기 위한 시스템을 제공한다. 상기 시스템은 각각의 상기 회로 기판들 상에 위치된 인증 칩(chip)을 포함한다. 각 인증 칩은 1) 기능을 위한 상기 컴퓨터 및 기능을 위한 상기 인증 칩이 위치되는 상기 회로 기판에 필요한 핵심 기능 및 2) 상기 컴퓨터 시스템에서 적절히 기능하기 위해 상기 회로 기판이 테스트되어 인증된 것을 전달하는 인증 기능을 포함한다. 또한, 상기 시스템은 상기 시스템에 통합된 각 회로 기판의 인증된 상태를 검증하기 위해 각각의 상기 인증 칩들이 서로 통신하는 것을 가능하게 하는 인증 통신들 버스를 포함한다. 적어도 일부 그러한 시스템들에 있어서, 상기 인증 칩이 없는 회로 기판이 상기 컴퓨터 시스템에 부착되면, 각각의 인증 칩은 상기 컴퓨터 시스템이 기능하는 것을 방지하도록 구성된다.

어떤 구현들에서, 각 인증 칩은 그의 각 회로 기판상에서 조건들을 감시하도록 구성된다. 상기 인증 칩들은 상기 회로 기판들 상에서 감시된 조건들의 기록을 유지할 수 있고, 각 인증 칩은 그의 각 회로 기판상에서 조건들의 보고들을 송신하도록 구성될 수 있다.

각 인증 칩이 상기 컴퓨터 시스템에 대한 전력 제어에 지능적으로 관여하도록 구성되는 일부 구현들에서, 상기 인증 칩들은 상기 컴퓨터 시스템에 대한 복수의 전원들을 턴 온 및 오프하는 타이밍(timing)에 협력적으로 관여한다. 일부 그러한 실시예들에 있어서, 상기 인증 칩들은 상기 컴퓨터의 전원들을 칩 안전 순서로 순차적으로 턴 온함으로써 및 순차적인 순서로 이전의 모든 전원들이 적절히 턴 온된 것을 검증한 후에만, 상기 컴퓨터 시스템의 칩들을 파괴할 위험이 있는 것으로 알려져 있는 상기 컴퓨터 시스템 내의 전력 조건들의 존재를 공동으로 방지한다. 추가적으로 또는 대안적으로, 상기 인증 칩들은 상기 컴퓨터 시스템 내의 전원 고장의 검출 시에 방치되면 칩들에 손상을 초래할 수 있는 전원들을 신속히 턴 오프함으로써, 상기 컴퓨터 시스템의 칩들을 파괴할 위험이 있는 것으로 알려져 있는 상기 컴퓨터 시스템 내의 전력 조건들의 상기 존재를 공동으로 방지한다.

적어도 일부 구현들에 있어서, 상기 인증 칩들은 전력 제어를 감시하고 상기 전원들의 활성화 및 비활성화를 제어하도록 구성된 로직 게이트(logic gate)들을 포함하며, 그것에 의해 전원의 고장시 다른 전원들의 비활성화는 상기 컴퓨터 시스템에 대한 손상을 방지하기 위해 충분히 신속해진다. 적어도 일부 실시예들에 있어서, 다른 전원들의 비활성화는 수개 내지 소수의 클록 사이클(clock cycle)들 내에서 발생한다.

구현된 바와 같이, 상기 컴퓨터 시스템이 턴 오프될지라도, 상기 인증 칩들은 상기 컴퓨터 시스템이 전원에 연결되어 있는 임의의 시간에 동작할 수 있다. 상기 인증 칩들은 상기 컴퓨터 시스템들의 측파대(sideband) 관리를 수행하고, 로직 게이트들만을 사용하여 그렇게 행할 수 있다.

어떤 구현들에서, 고장 이벤트들이 상기 인증 칩들 내의 로직 게이트들에 의해 검출되어 기록되고, 그 후에 상기 인증 칩들은 상기 고장 이벤트들을 협력적으로 로그(log)하고 상기 컴퓨터 시스템을 셧 다운(shut down)하도록 구성된다. 상기 인증 칩들은 다음 파워 온(power-on) 시도 중 하나 이상에, 및 고장시 언제라도 상기 고장 이벤트들의 기록을 송신하도록 구성될 수 있다.

일부 구현들에서, 상기 컴퓨터 시스템이 실행되고 있을 때, 상기 인증 칩들은 내부 집적 회로(I2C: inter-integrated circuit) 버스, 및 낮은 핀 카운트(LPC: low pin count) 버스와 같은, 상기 컴퓨터 시스템의 하나 이상의 버스들 상에 발생하는 통신들을 스누프(snoop)하도록 구성된다. 상기 인증 칩들은 입력/출력(I/O: inout/output) 통신들 및 포스트 코드(post code)들과 같은, 스누프된 통신들에 응답하도록 구성될 수 있다.

본 발명의 구현들에서, 하나 이상의 상기 인증 칩들은 로직 게이트들을 사용하여 실시간 프로세서 에뮬레이션(emulation)을 제공하도록 구성된다. 실시간 프로세서 에뮬레이션을 제공하는 상기 하나 이상의 인증 칩들은 선택된 입력들을 위해 특정하게 선택된 출력들을 자동으로 및 신속히 제공할 수 있다. 어떤 경우들에서, 상기 하나 이상의 인증 칩들은 키보드 컨트롤러(keyboard controller) 및 비디오 컨트롤러(video controller) 중 하나에 에뮬레이션을 제공한다.

어떤 구현들에서, 상기 인증 칩들은, 전원이 초기에 상기 컴퓨터 시스템에 연결될 때, 상기 컴퓨터 시스템이 턴 온되어 사용되는 것을 가능하게 하기 전에 각각이 활성화되어 기능할 준비가 되는 것을 보증하기 위해 상기 인증 칩들이 서로에 통신들을 제공하도록 구성된다.

어떤 구현들은 컴퓨터 시스템에서 나타나고, 여기서 상기 컴퓨터 시스템의 통합된 측파대 관리를 제공하기 위한 시스템은 상기 컴퓨터 시스템에 통합되고 로직 게이트들만을 사용하여 상기 컴퓨터 시스템의 측파대 관리를 제공하는 측파대 관리 디바이스를 사용하여 제공된다. 상기 측파대 관리 디바이스는 파워 업 시에 상기 컴퓨터 시스템의 전원들의 활성화의 적절한 시퀀싱을 보증하는 파워 온 관리를 제공할 수 있다. 상기 측파대 관리 디바이스는 부적절하고, 잠재적으로 손상되는, 전압 조합들이 상기 컴퓨터 시스템에서 발생하는 것을 방지하는 방법으로 전원들의 활성화만이 발생하는 것을 보증할 수 있다. 상기 측파대 관리 디바이스는 전원 시퀀싱을 중단하고, 상기 컴퓨터 시스템을 턴 오프하며, 하나 이상의 전원들이 활성화되지 않을 때 결함 상태의 상세를 로그하도록 구성될 수 있다.

어떤 구현들의 측파대 관리 디바이스는 상기 컴퓨터 시스템의 다중 회로 기판들에 걸쳐서 분배된 복수의 디바이스들을 포함할 수 있다. 그럼에도 불구하고, 상기 측파대 관리 디바이스는 상기 컴퓨터 시스템이 턴 오프될 때 전원 공급된 채로 남아 있을 수 있다. 어떤 구현들에 있어서, 상기 컴퓨터 시스템은 단일 컴퓨터 디바이스이고, 상기 측파대 관리 디바이스는 상기 컴퓨터 디바이스의 적어도 하나의 회로 기판에 통합되며, 그것에 의해 상기 측파대 관리 디바이스는 개별 프로세서 또는 컴퓨터 디바이스를 포함하지 않는다.

본 발명의 구현들은 컴퓨터 시스템의 기능에 필요한 상이한 전압들의 복수의 전원들을 포함하는 상기 컴퓨터 시스템에서 전원들의 활성화를 제어하기 위한 방법을 제공한다. 상기 방법은 상기 복수의 전원들 중 하나 이상의 활성화를 선택적으로 지시하는 단계 및 활성화되도록 지시된 상기 전원 및 전원들이 적절히 턴 온되는지를 감시하는 단계를 포함한다. 활성화되도록 지시된 상기 전원들 중 하나 이상이 설정 시간 내에 적절히 턴 온되지 않을 때, 상기 방법은 고장 이벤트를 로그하는 것 및 상기 컴퓨터 시스템을 턴 오프하는 단계를 포함한다.

상기 방법의 일부 구현들에 있어서, 전원들은 부적절한 전압 시퀀스들에 의해 초래되는 상기 컴퓨터 시스템의 구성요소들에 대한 손상을 방지하도록 설계된 시퀀스에서 활성화되고, 각 전원의 활성화는 활성화의 시퀀스가 연속되기 전에 적절한 활성화를 위해 감시된다. 적어도 일부 실시예들에 있어서, 상기 컴퓨터 시스템을 턴 오프하는 것은 부적절한 전압 시퀀스들에 의해 초래되는 상기 컴퓨터 시스템의 구성요소들에 대한 손상을 방지하는 순서로 실행가능해지는 임의의 전원들을 비활성화하는 것을 포함한다.

본 발명의 구현들은 복수의 회로 기판들을 갖는 컴퓨터 시스템을 위해 전력 관리 시스템을 제공한다. 상기 전력 관리 시스템은 상기 컴퓨터 시스템의 상기 회로 기판들에 걸쳐서 확장되는 전력 관리 버스 및 상기 전력 관리 버스에 통신적으로 결합된 복수의 플랫폼(platform) 관리 컨트롤러들을 포함하며, 여기서 각 플랫폼 관리 컨트롤러는 상이한 회로 기판 상에 위치되고 그의 각 회로 기판 상에서 전원들을 제어하도록 구성된다.

적어도 일부 구현들에 있어서, 각 플랫폼 관리 컨트롤러는 전적으로 로직 게이트들로 구현된다. 상기 플랫폼 관리 컨트롤러들은 컴퓨터가 턴 온되는지에 관계없이, 상기 컴퓨터 시스템이 입력 전원에 연결되는 언제라도 동작하도록 구성될 수 있다. 또한, 상기 플랫폼 관리 컨트롤러들은 상기 컴퓨터 시스템의 임의의 전원들이 활성화되는 것을 가능하게 하기 전에 다른 플랫폼 관리 컨트롤러들이 활성되는 것을 보증하도록 구성될 수 있다. 상기 플랫폼 관리 컨트롤러들은 상기 전력 관리 버스를 사용하여 다른 컨트롤러들이 활성될 때 수신되는 바와 같이 다른 컨트롤러들에 통과되어 다른 컨트롤러들에 의해 전달되는 컨트롤러 특정 키(key)들을 발생시킴으로써 다른 플랫폼 관리 컨트롤러들이 활성화되는 것을 결정할 수 있으며, 그것에 의해 각 컨트롤러가 그 자체의 키를 다시 수신할 때 그것은 모든 컨트롤러들이 활성되는 것을 인식한다.

본 발명의 구현은 컴퓨터 시스템의 속도를 개선하면서 상기 컴퓨터 시스템 내의 프로세서 기반 컴퓨터 구성요소를 에뮬레이션하기 위한 시스템을 제공한다. 상기 프로세서 기반 컴퓨터 구성요소를 에뮬레이션하기 위한 시스템은 로직 게이트들만을 사용하여 프로세서 기반 컴퓨터 구성요소를 에뮬레이션하도록 구성된 로직 게이트 기반 디바이스를 포함하며, 여기서 상기 로직 게이트들은 프로세서 기반 컴퓨터 구성요소에 의해 통상 취급되는 명령들의 세트를 수신하고 단지 훨씬 더 빠른 속도로 상기 프로세서 기반 컴퓨터 구성요소에 의해 통상 출력되는 출력을 제공하도록 구성된다. 일부 구현들에 있어서, 상기 로직 게이트들은 상기 프로세서 기반 컴퓨터 구성요소에 의해 통상 취급되는 모든 가능한 명령들의 서브세트(subset)만을 인지하고 응답하도록 구성된다. 상기 로직 게이트 기반 디바이스는 상기 컴퓨터 시스템에 의해 활성적으로 사용되지 않는 레거시(legacy) 컴퓨터 디바이스의 에뮬레이션을 제공할 수 있지만 그의 존재는 1) 상기 컴퓨터 시스템의 기본 입력/출력 시스템(BIOS: basic input/output system) 및 2) 컴퓨터 시스템의 운영 체제(OS: operating system) 중 하나의 적절한 동작에 요구된다.

본 발명의 어떤 구현들은 디지털 통신들을 인코딩(encoding), 송신, 및 디코딩(decoding)하기 위한 방법을 제공하며, 여기서 통신의 데이터 부분들은 본래 추가 데이터 비트(bit)들를 필요로 하지 않고 수신된 데이터 부분들의 유효성에 관한 체크섬(checksum) 정보를 포함한다. 상기 방법은 디지털 데이터의 어떤 패턴(pattern)들이 무효인 방식을 사용하여 정보를 디지털 스트림(digital stream)으로 인코딩하는 단계 및 송신기를 반복적으로 사용하여 상기 디지털 스트림을 송신하는 단계를 포함한다. 수신기는 수신된 정보를 수신하고, 상기 수신된 정보는 유효 및 무효 패턴들에 대해 평가된다. 유효 개시 패턴 다음에 하나 이상의 유효 데이터 패턴들이 뒤따를 때, 상기 수신된 정보는 단지 유지되고 디코딩된다.

상기 개시 패턴은 상기 데이터 스트림에 포함되는 데이터의 유형에 관한 정보를 포함할 수 있다. 또한, 상기 개시 패턴은 상기 디지털 스트림이 반복된 횟수에 관한 정보를 포함할 수 있다.

본 발명의 구현은 컴퓨터 시스템에 통합된 플랫폼 관리 컨트롤러를 사용하여 상기 컴퓨터 시스템의 시동 및 기능을 감시하기 위한 방법을 제공한다. 상기 방법은 컴퓨터 시스템에 플랫폼 관리 컨트롤러를 제공하는 단계를 포함하며, 여기서 상기 플랫폼 관리 컨트롤러는 상기 컴퓨터 시스템의 전력을 관리하고 상기 컴퓨터 시스템의 기능에 관한 정보를 상기 컴퓨터 시스템으로부터 획득할 수 있도록 상기 컴퓨터 시스템에 연결되고, 여기서 상기 플랫폼 관리 컨트롤러는 송신기에 동작적으로 연결된다. 또한, 상기 방법은 상기 컴퓨터 시스템의 시동 및 동작을 감시하기 위해 상기 플랫폼 관리 컨트롤러를 사용하는 단계, 상기 컴퓨터 시스템의 시동 및 동작 중 적어도 하나에 관한 이벤트들에 로그하기 위해 상기 플랫폼 관리 컨트롤러를 사용하는 단계, 및 상기 송신기를 사용하여 로그된 이벤트들을 송신하기 위해 상기 플랫폼 관리 컨트롤러를 사용하는 단계를 포함한다.

상기 로그된 이벤트들은 시동시 상기 컴퓨터 시스템에 의해 발생된 포스트 코드들을 포함할 수 있다. 상기 로그된 이벤트들이 포스트 코드들을 포함할 때, 상기 플랫폼 관리 컨트롤러는 시동시 언제라도 상기 포스트 코드들을 송신할 수 있다. 상기 로그된 이벤트들은 셧다운(shutdowm) 시간 및 검출된 비정상 온도의 시간 중 하나에서 상기 컴퓨터 시스템으로부터 획득된 온도 판독을 추가적으로 또는 대안적으로 포함할 수 있다. 일부 구현들에 있어서, 상기 컴퓨터 시스템의 운영 시스템은 외부 송신을 위해 상기 플랫폼 관리 컨트롤러에 메시지들을 전송하도록 구성된다.

본 발명의 구현들은 전원 트래킹 장치를 제공하기 위한 기술에 관한 것이다. 특히, 본 발명의 적어도 일부 구현들은 연산 회로의 제 1 전력 입력이 상기 연산 회로의 제 2 전력 입력에 대해 미리 정의된 관계를 유지하는 것을 보증하기 위한 전원 트래킹 장치에 관한 것이다.

본 발명의 구현은 기준 전압원, 비교기, 및 스위치를 갖는 전원 트래킹 장치를 포함한다. 상기 기준 전압원은 기준 전압을 비교기의 제 1 입력에 제공한다. 상기 비교기의 제 2 입력은 제 1 전력 입력에 결합된다. 상기 비교기의 출력은 상기 기준 전압 및 상기 제 1 전력 입력의 상대 전압의 함수로서 상태를 스위칭한다. 상기 비교기의 상기 출력은 스위치를 제어하고, 따라서 상기 기준 전압 및 상기 제 1 전력 입력의 상기 상대 전압에 따라 상기 스위치를 개방 및 폐쇄한다. 상기 스위치는 전원과 상기 제 2 전력 입력 사이에 배치된다. 따라서, 상기 제 2 전력 입력은 상기 제 1 전력 입력에 대해 미리 정의된 관계로 유지될 수 있다.

본 발명의 구현들의 방법들 및 프로세스들은 개인용 컴퓨팅 엔터프라이즈(enterprise)들의 영역에 특히 유용한 것으로 증명되었을지라도, 당업자들은 제어 시스템들 또는 스마트 인터페이스 시스템(smart-interface system)들을 사용하는 임의의 산업에 대한 엔터프라이즈들 및/또는 그러한 디바이스들의 상기 구현으로 이득을 얻는 엔터프라이즈들을 포함하는, 커스터마이즈(customize) 가능 엔터프라이즈들을 산출하기 위해, 본 발명의 상기 방법들 및 프로세스들이 각종 상이한 애플리케이션들 및 각종 상이한 제조 영역들에 사용될 수 있다는 것을 인식할 것이다. 그러한 산업들의 예들은 자동차 산업들, 항공 전자 산업들, 유압 제어 산업들, 오토/비디오 제어 산업들, 전기통신 산업들, 의료 산업들, 특수 용도 산업들, 및 가전 기기 산업들을 포함하지만, 이들에 제한되지 않는다. 따라서, 본 발명의 상기 시스템들 및 방법들은 현재 컴퓨터 기술에 의해 종래에 이용되지 않았던 마켓(market)들을 포함하는 많은 상이한 마켓들에 이점들을 제공할 수 있다.

본 발명의 구현은 컴퓨터 시스템들 진단 정보를 무선으로 수신하고 그러한 정보를 커스터마이즈 가능하게 표시하기 위한 시스템들 및 방법들을 제공한다. 상기 정보는 다양한 범용 컴퓨터 시스템들 및 다양한 특수 용도 컴퓨터 시스템들을 포함하는, 다양한 기존 및 장래의 컴퓨터 시스템들로부터 수신될 수 있다. 본 출원에 개시된 바와 같이, 컴퓨터 시스템에 통합된 플랫폼 관리 컨트롤러(PMC: platform management controller) 또는 유사한 디바이스는 컴퓨터 시스템 정보를 감시하고 상기 감시된 정보를, 예컨대 적외선에 의해 송신하거나 그 외 전달한다. 본 발명의 실시예들은 상기 송신된 정보를 수신하므로, 그것은 본 출원에 개시된 것과 같은 다양한 목적들에 이용될 수 있다.

본 발명의 구현들에 있어서, PMC 또는 다른 유사한 디바이스에 의해 송신된 복수의 로그된 이벤트들은 무선 진단 디바이스와 같은 진단 디바이스에 의해 수신 및 감시될 수 있다. 본 발명의 적어도 일부 구현들에 있어서, 진단 디바이스의 프로세싱 특징들은 주로 또는 전적으로 로직 게이트들로 구현된다. 그러한 구현은 본 출원에서 더 상세히 논의되는 바와 같이 어떤 장점들을 제공한다.

본 발명의 구현은 일시적 전기 연결들에 관한 것이다. 특히, 본 발명은 인쇄 회로 기판(PCB)로부터 또는 PCB에 정보를 수신 또는 송신하기 위해, 외부 디바이스를 PCB에 일시적으로 연결하기 위한 시스템들 및 방법들에 관한 것이다.

본 발명의 구현은 상기 연결을 통해서 데이터의 상기 전송을 용이하게 하기 위해 외부 소스와 PCB 사이의 일시적 전기 연결들과 관련하여 실시된다. 적어도 하나의 구현에 있어서, 일시적 전기 시스템은 PCB의 하나 이상의 에지(edge)들에 인접하여 배치된 전기 접촉 패드들을 갖는 PCB를 포함한다. 상기 전기 접촉 패드들은 차례로 PCB 상의 특정 위치들에 전기적으로 연결된다. 상기 시스템들은 와이어 리본(wire ribbon) 및 상기 PCB의 상기 에지(들) 상에 배치된 상기 전기 패드들에 대응하는 하나 이상의 전기 접촉 패드들이 배치된 전선 리본(electrical wire ribbon)의 원위 단부의 헤드(head)를 차례로 포함하는 일시적 전기 커넥터 장치를 더 포함한다.

추가 구현에 있어서, PCB와 일시적으로 전기적으로 연결되도록 적응된 장치는 전선 리본을 포함한다. 상기 장치는 하나 이상의 전기 접촉 패드들이 배치된 상기 전선 리본의 상기 원위 단부에 헤드를 더 포함한다. 또한, 일부 구현들에 있어서, 상기 헤드는 그 위에 배치된 접착제를 가지며, 이는 전기 접촉 패드들을 실질적으로 둘러싼다. 사용 전에, 상기 접착제는 사용시에 제거될 수 있는 논-스틱 페이퍼 백킹(non-stick paper backing) 등에 의해 보호된다. 다른 구현에 있어서, 상기 헤드는 상기 헤드를 팽팽하게 하도록 조작될 수 있는 압축 피팅(compression fitting)을 포함하여, 그것은 PCB와 같은 대응하는 표면에 고정된 채로 일시적으로 남아 있는다. 또 다른 구현들에 있어서, 상기 헤드는 상기 헤드 및 PCB와 같은 대응하는 표면 사이에서 일시적 연결을 용이하게 하는데 사용될 수 있는 핀(pin)들 또는 다른 로케이터(locator)들을 포함한다. 더 다른 구현에 있어서, 상기 헤드는 조우(jaw)들을 폐쇄된 위치에서 바이어스(biase)하는 동작 스프링(spring)에 의해 연결된 2개의 대향하는 조우들로 구성되어, 상기 조우들은 사용자에 의해 선택적으로 개방될 수 있고 상기 헤드는 PCB와 같은 대응하는 표면에 일시적으로 "클립(clip)"된다. 또 다른 구현들에 있어서, 헤드는 PCB의 폭을 연계하여 분리한 2개의 대향하는 고정 표면들로 구성되어, 상기 헤드는 이에 일시적으로 고정된 채로 남아 있기 위해 상기 PCB의 상기 에지에 걸쳐서 일시적으로 슬립(slip)될 수 있다.

본 발명의 구현의 방법들 및 프로세스들은 일시적 PCB 연결들의 영역에 특히 유용한 것으로 증명되었을지라도, 당업자들은 일시적이고, 편리하며 저렴한 전기 연결들을 산출하기 위해 상기 방법들 및 프로세스들이 각종 상이한 애플리케이션들 및 각종 상이한 제조 영역들에 사용될 수 있다는 것을 인식할 수 있다.

본 발명의 목적들 및 특징들은 첨부 도면들과 병용되는, 이하의 설명 및 첨부된 청구항들로부터 더 완전히 명백해질 것이다. 이 도면들은 본 발명의 전형적인 실시예들만을 도시하고, 따라서 그의 범위를 제한하는 것으로 간주되지 않아야 한다는 이해 하에, 본 발명은 첨부 도면들의 사용을 통해서 추가적으로 구체적으로 및 상세하게 기재 및 설명될 것이다.

도 1은 본 발명의 실시예들에 사용되는 다른 대표적인 컴퓨터 시스템의 예시로서, 원래의 참조 번호가 보존된, 미국 특허 제7,075,784호의 도 1의 카피(copy)를 도시한다.

도 2는 본 발명의 실시예들에 사용되는 대표적인 컴퓨터 시스템의 대표적인 회로 기판 구성을 도시하는, 원래의 참조 번호가 보존된, 미국 특허 제7,075,784호의 도 3의 카피를 도시한다.

도 3은 본 발명의 실시예들에 사용되는 대표적인 컴퓨터 시스템을 도시한다.

도 4는 본 발명의 실시예들에 사용되는 대표적인 네트워크 컴퓨터 시스템을 도시한다.

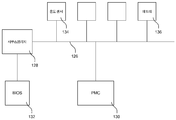

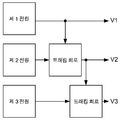

도 5는 다수의 플랫폼 관리 컨트롤러들 사이의 대표적인 연결들의 개략도를 도시한다.

도 6은 컴퓨터 시스템 내의 대표적인 플랫폼 관리 컨트롤러와 다른 디바이스들 사이의 연결들의 개략도를 도시한다.

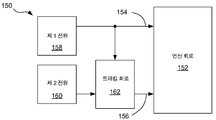

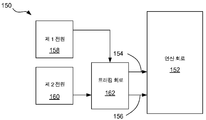

도 7은 본 발명의 일부 실시예들에 따른 트래킹 회로(tracking circuit)를 갖는 전자 시스템의 대표적인 블록도를 예시한다.

도 8은 본 발명의 일부 실시예들에 따른 트래킹 회로를 갖는 전자 시스템의 대표적인 블록도를 예시한다.

도 9는 본 발명의 일부 실시예들에 따른 트래킹 회로의 대표적인 블록도를 예시한다.

도 10은 본 발명의 일부 실시예들에 따른 트래킹 회로의 대표적인 블록도를 예시한다.

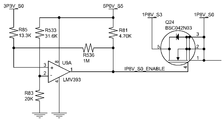

도 11은 본 발명의 일부 실시예들에 따른 트래킹 회로의 대표적인 개략도를 예시한다.

도 12는 본 발명의 일부 실시예들에 따른 트래킹 회로들의 대표적인 병렬 배치를 예시한다.

도 13은 본 발명의 일부 실시예들에 따른 트래킹 회로들의 대표적인 직렬 배치를 예시한다.

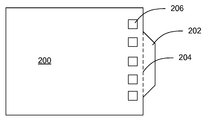

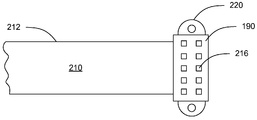

도 14는 생산 프로세스 동안의 대표적인 PCB의 평면도를 예시한다.

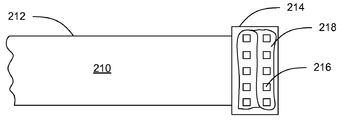

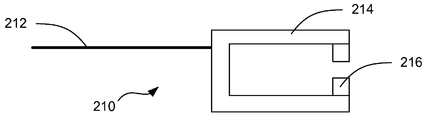

도 15는 생산 후의 대표적인 PCB의 평면도를 예시한다.

도 16은 본 발명의 실시예들에 의해 예상되는 대표적인 일시적 전기 연결 장치의 상단의 평면도를 예시한다.

도 17은 접착제를 갖는 일시적 전기 연결 장치의 다른 대표적인 실시예의 하측의 평면도를 예시한다.

도 18은 헤드(head)의 양 측면들 상에 로케이터(locator)들을 갖는 일시적 전기 연결 장치의 다른 대표적인 실시예의 하측의 평면도를 예시한다.

도 19는 로케이터들에 핀(pin)들을 갖는 도 18의 것과 유사한 대표적인 실시예의 정면도를 예시한다.

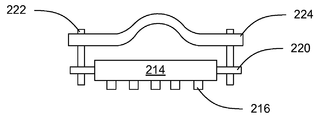

도 20은 로케이터들에 핀들을 갖고 이에 부착된 압축 피팅(compression fitting)을 갖는 도 18의 것과 유사한 대표적인 실시예의 정면도를 예시한다.

도 21은 대향하는 바이어스(bias)된 조우(jaw)들을 갖는 일시적 전기 연결 장치의 대표적인 실시예의 측면도를 예시한다.

도 22는 도 21의 대표적인 실시예의 정면도를 예시한다.

도 23은 PCB의 폭을 연계하여 분리한 두 개의 대향하는 고정 표면들을 갖는 일시적 전기 연결 장치 헤드의 다른 대표적인 실시예의 측면도를 예시한다.

도 24는 도 23의 대표적인 실시예의 정면도를 예시한다.

도 1은 본 발명의 실시예들에 사용되는 다른 대표적인 컴퓨터 시스템의 예시로서, 원래의 참조 번호가 보존된, 미국 특허 제7,075,784호의 도 1의 카피(copy)를 도시한다.

도 2는 본 발명의 실시예들에 사용되는 대표적인 컴퓨터 시스템의 대표적인 회로 기판 구성을 도시하는, 원래의 참조 번호가 보존된, 미국 특허 제7,075,784호의 도 3의 카피를 도시한다.

도 3은 본 발명의 실시예들에 사용되는 대표적인 컴퓨터 시스템을 도시한다.

도 4는 본 발명의 실시예들에 사용되는 대표적인 네트워크 컴퓨터 시스템을 도시한다.

도 5는 다수의 플랫폼 관리 컨트롤러들 사이의 대표적인 연결들의 개략도를 도시한다.

도 6은 컴퓨터 시스템 내의 대표적인 플랫폼 관리 컨트롤러와 다른 디바이스들 사이의 연결들의 개략도를 도시한다.

도 7은 본 발명의 일부 실시예들에 따른 트래킹 회로(tracking circuit)를 갖는 전자 시스템의 대표적인 블록도를 예시한다.

도 8은 본 발명의 일부 실시예들에 따른 트래킹 회로를 갖는 전자 시스템의 대표적인 블록도를 예시한다.

도 9는 본 발명의 일부 실시예들에 따른 트래킹 회로의 대표적인 블록도를 예시한다.

도 10은 본 발명의 일부 실시예들에 따른 트래킹 회로의 대표적인 블록도를 예시한다.

도 11은 본 발명의 일부 실시예들에 따른 트래킹 회로의 대표적인 개략도를 예시한다.

도 12는 본 발명의 일부 실시예들에 따른 트래킹 회로들의 대표적인 병렬 배치를 예시한다.

도 13은 본 발명의 일부 실시예들에 따른 트래킹 회로들의 대표적인 직렬 배치를 예시한다.

도 14는 생산 프로세스 동안의 대표적인 PCB의 평면도를 예시한다.

도 15는 생산 후의 대표적인 PCB의 평면도를 예시한다.

도 16은 본 발명의 실시예들에 의해 예상되는 대표적인 일시적 전기 연결 장치의 상단의 평면도를 예시한다.

도 17은 접착제를 갖는 일시적 전기 연결 장치의 다른 대표적인 실시예의 하측의 평면도를 예시한다.

도 18은 헤드(head)의 양 측면들 상에 로케이터(locator)들을 갖는 일시적 전기 연결 장치의 다른 대표적인 실시예의 하측의 평면도를 예시한다.

도 19는 로케이터들에 핀(pin)들을 갖는 도 18의 것과 유사한 대표적인 실시예의 정면도를 예시한다.

도 20은 로케이터들에 핀들을 갖고 이에 부착된 압축 피팅(compression fitting)을 갖는 도 18의 것과 유사한 대표적인 실시예의 정면도를 예시한다.

도 21은 대향하는 바이어스(bias)된 조우(jaw)들을 갖는 일시적 전기 연결 장치의 대표적인 실시예의 측면도를 예시한다.

도 22는 도 21의 대표적인 실시예의 정면도를 예시한다.

도 23은 PCB의 폭을 연계하여 분리한 두 개의 대향하는 고정 표면들을 갖는 일시적 전기 연결 장치 헤드의 다른 대표적인 실시예의 측면도를 예시한다.

도 24는 도 23의 대표적인 실시예의 정면도를 예시한다.

본 발명의 실시예들의 설명은 도면들을 참조하면서 아래에서 주어질 것이다. 본 발명은 많은 다른 형태들 및 형상들을 취할 수 있고, 따라서 다음 발명은 예시적이며 제한이 아닌 것으로 의도되고, 본 발명의 범위는 첨부된 청구항들을 참조함으로써 결정되어야 하는 것이 기대된다.

본 발명의 실시예들은 컴퓨터 시스템들 및 컴퓨터 시스템 동작의 다양한 측면들의 지능형 유연 관리 및 감시를 위한 시스템들 및 방법들을 제공한다. 본 발명의 실시예들은 다양한 범용 컴퓨터 시스템들 및 다양한 특수 용도 컴퓨터 시스템들을 포함하는, 다양한 기존 및 장래의 컴퓨터 시스템들에 적용가능하다. 본 발명이 다양한 방법들로 구현될 수 있는 컴퓨터 시스템의 하나의 분류 또는 구성은 발명의 명칭이 Non-Peripherals Processing Control Module Having Improved Heat Dissipating Properties인 미국 특허 제7,256,991호, 발명의 명칭이 Robust Customizable Computer Processing System인 제7,242,574호, 및 발명의 명칭이 Systems and Methods for Providing a Dynamically Modular Processing Unit인 제7,075,784호에 개시되어 있으며, 그들은 모든 발명을 위해 본 출원에 참고문헌으로 명백히 통합되어 있다.

상기 참조된 특허들에 개시된 것과 같은 복수의 상호 접속 회로 기판들을 갖고 사용하도록 구성된 컴퓨터 시스템에서, 본 발명의 어떤 실시예들은 인증된 회로 기판들만이 컴퓨터 시스템에 사용되는 것을 보증하기 위한 시스템을 제공한다. 시스템은 각각의 회로 기판들 상에 위치된 인증 칩(chip)을 포함한다. 각 인증 칩은 1) 기능을 위한 컴퓨터 및 기능을 위한 인증 칩이 위치되는 회로 기판 중 하나에 필요한 핵심 기능 및 2) 컴퓨터 시스템에서 적절히 기능하기 위해 회로 기판이 테스트되어 인증된 것을 전달하는 인증 기능을 포함한다. 또한, 시스템은 시스템에 통합된 각 회로 기판의 인증된 상태를 검증하기 위해 각각의 인증 칩들이 서로 통신하는 것을 가능하게 하는 인증 통신들 버스를 포함한다. 적어도 일부 그러한 시스템들에 있어서, 인증 칩이 없는 회로 기판이 컴퓨터 시스템에 부착되면 각 인증 칩은 컴퓨터 시스템이 기능하는 것을 방지하도록 구성된다.

어떤 실시예들에 있어서, 각 인증 칩은 그의 각 회로 기판상에서 조건들을 감시하도록 구성된다. 인증 칩들은 회로 기판들 상에서 감시된 조건들의 기록을 유지할 수 있고, 각 인증 칩은 그의 각 회로 기판상에서 조건들의 보고들을 송신하도록 구성될 수 있다.

각 인증 칩이 컴퓨터 시스템에 대한 전력 제어에 지능적으로 관여하도록 구성되는 일부 실시예들에 있어서, 인증 칩들은 컴퓨터 시스템에 대한 복수의 전원들을 턴 온 및 오프하는 타이밍에 협력적으로 관여한다. 일부 그러한 실시예들에 있어서, 인증 칩들은 컴퓨터의 전원들을 칩 안전 순서로 순차적으로 턴 온함으로써 및 순차적인 순서로 이전의 모든 전원들이 적절히 턴 온된 것을 검증한 후에만 컴퓨터 시스템의 칩들을 파괴할 위험이 있는 것으로 알려져 있는 컴퓨터 시스템 내의 전력 조건들의 존재를 공동으로 방지한다. 추가적으로 또는 대안적으로, 인증 칩들은 컴퓨터 시스템 내의 전원 고장의 검출시에 방치되면 칩들에 손상을 초래할 수 있는 전원들을 신속히 턴 오프함으로써 컴퓨터 시스템의 칩들을 파괴할 위험이 있는 것으로 알려져 있는 컴퓨터 시스템 내의 전력 조건들의 존재를 공동으로 방지한다.

적어도 일부 실시예들에 있어서, 인증 칩들은 전력 제어를 감시하고 전원들의 활성화 및 비활성화를 제어하도록 구성된 로직 게이트(logic chip)들을 포함하며, 그것에 의해 전원의 고장시 다른 전원들의 비활성화는 컴퓨터 시스템에 대한 손상을 방지하기 위해 충분히 신속해진다. 적어도 일부 실시예들에 있어서, 다른 전원들의 비활성화는 수개 내지 소수의 클록 사이클(clock cycle)들 내에서 발생한다.

구현된 바와 같이, 컴퓨터 시스템이 턴 오프될지라도, 인증 칩들은 컴퓨터 시스템이 전원에 연결되어 있는 언제라도 동작할 수 있다. 인증 칩들은 컴퓨터 시스템들의 측파대(sideband) 관리를 수행하고, 로직 게이트들만을 사용하여 그렇게 행할 수 있다.

어떤 실시예들에 있어서, 고장 이벤트들이 인증 칩들 내의 로직 게이트들에 의해 검출되어 기록되고, 그 후에 인증 칩들은 고장 이벤트들을 협력적으로 로그하고 컴퓨터 시스템을 셧 다운(shut down)하도록 구성된다. 인증 칩들은 다음 파워 온(power-on) 시도 중 하나 이상에, 및 고장시 언제라도 고장 이벤트들의 기록을 송신하도록 구성될 수 있다.

일부 실시예들에 있어서, 컴퓨터 시스템이 실행되고 있을 때, 인증 칩들은 내부 집적 회로(I2C: inter-integrated circuit) 버스, 및 낮은 핀 카운트(LPC: low pin count) 버스와 같은, 컴퓨터 시스템의 하나 이상의 버스들 상에 발생하는 통신들을 스누프(snoop)하도록 구성된다. 인증 칩들은 입력/출력(I/O: input/output) 통신들 및 포스트 코드들과 같은, 스누프된 통신들에 응답하도록 구성될 수 있다.

본 발명의 실시예들에 있어서, 하나 이상의 인증 칩들은 로직 게이트들을 사용하여 실시간 프로세서 에뮬레이션을 제공하도록 구성된다. 실시간 프로세서 에뮬레이션을 제공하는 하나 이상의 인증 칩들은 선택된 입력들을 위해 특정하게 선택된 출력들을 자동으로 및 신속히 제공할 수 있다. 어떤 경우들에서, 하나 이상의 인증 칩들은 PS/2 키보드 컨트롤러 및 비디오 컨트롤러 중 하나에 에뮬레이션을 제공한다.

어떤 실시예들에 있어서, 인증 칩들은 전원이 초기에 컴퓨터 시스템에 연결될 때, 컴퓨터 시스템이 턴 온되어 사용되는 것을 가능하게 하기 전에 각각이 활성화되어 기능할 준비가 되는 것을 보증하기 위해 인증 칩들이 서로에 통신들을 제공하도록 구성된다.

어떤 실시예들은 컴퓨터 시스템에서 나타나고, 여기서 컴퓨터 시스템의 통합된 측파대 관리를 제공하기 위한 시스템은 컴퓨터 시스템에 통합되고 로직 게이트들만을 사용하여 컴퓨터 시스템의 측파대 관리를 제공하는 측파대 관리 디바이스를 사용하여 제공된다. 측파대 관리 디바이스는 파워 업(power-up) 시 컴퓨터 시스템의 전원들의 활성화의 적절한 시퀀싱을 보증하는 파워 온 관리를 제공할 수 있다. 측파대 관리 디바이스는 부적절하고, 잠재적으로 손상되는, 전압 조합들이 컴퓨터 시스템에서 발생하는 것을 방지하는 방법으로 전원들의 활성화만이 발생하는 것을 보증할 수 있다. 측파대 관리 디바이스는 전원 시퀀싱을 중단하고, 컴퓨터 시스템을 턴 오프하며, 하나 이상의 전원들이 활성화되지 않을 때 결함 상태의 상세를 로그(log)하도록 구성될 수 있다.

어떤 실시예들의 측파대 관리 디바이스는 컴퓨터 시스템의 다중 회로 기판들에 걸쳐서 분배된 복수의 디바이스들을 포함할 수 있다. 그럼에도 불구하고, 컴퓨터 시스템이 턴 오프될 때 측파대 관리 디바이스는 전원 공급된 채로 남아 있을 수 있다. 어떤 실시예들에 있어서, 컴퓨터 시스템은 단일 컴퓨터 디바이스이고 측파대 관리 디바이스는 컴퓨터 디바이스의 적어도 하나의 회로 기판에 통합되며, 그것에 의해 측파대 관리 디바이스는 개별 프로세서 또는 컴퓨터 디바이스를 포함하지 않는다.

본 발명의 실시예들은 컴퓨터 시스템의 기능에 필요한 상이한 전압들의 복수의 전원들을 포함하는 컴퓨터 시스템에서 전원들의 활성화를 제어하기 위한 방법을 제공한다. 방법은 복수의 전원들 중 하나 이상의 활성화를 선택적으로 지시하는 단계 및 활성화되도록 지시된 전원들이 적절히 턴 온되는지를 감시하는 단계를 포함한다. 활성화되도록 지시된 전원들 중 하나 이상이 설정 시간 내에 적절히 턴 온되지 않을 때, 방법은 고장 이벤트를 로그하는 것 및 컴퓨터 시스템을 턴 오프하는 단계를 포함한다.

방법의 일부 실시예들에 있어서, 전원들은 부적절한 전압 시퀀스들에 의해 초래되는 컴퓨터 시스템의 구성요소들에 대한 손상을 방지하도록 설계된 시퀀스에서 활성화되고, 각 전원의 활성화는 활성화의 시퀀스가 연속되기 전에 적절한 활성화를 위해 감시된다. 적어도 일부 실시예들에 있어서, 컴퓨터 시스템을 턴 오프하는 단계는 부적절한 전압 시퀀스들에 의해 초래되는 컴퓨터 시스템의 구성요소들에 대한 손상을 방지하는 순서로 실행가능해지는 임의의 전원들을 비활성화하는 단계를 포함한다.

본 발명의 실시예들은 복수의 회로 기판들을 갖는 컴퓨터 시스템을 위해 전력 관리 시스템을 제공한다. 전력 관리 시스템은 컴퓨터 시스템의 회로 기판들에 걸쳐서 확장되는 전력 관리 버스 및 전력 관리 버스에 통신적으로 결합된 복수의 플랫폼 관리 컨트롤러들(PMCs: platform management controllers)을 포함하며, 여기서 각 PMC는 상이한 회로 기판상에 위치되고, 그의 각 회로 기판상에서 전원들을 제어하도록 구성된다.

적어도 일부 실시예들에 있어서, 각 PMC는 전적으로 로직 게이트들로 구현된다. PMC들은 컴퓨터가 턴 온되는지에 관계없이, 컴퓨터 시스템이 입력 전원에 연결되는 언제라도 동작하도록 구성될 수 있다. 또한, PMC들은 컴퓨터 시스템의 임의의 전원들이 활성화되는 것을 가능하게 하기 전에 다른 PMC들이 활성화되는 것을 보증하도록 구성될 수 있다. PMC들은 전력 관리 버스를 사용하여 다른 컨트롤러들이 활성화될 때 수신되는 바와 같이 다른 컨트롤러들에 통과되어 다른 컨트롤러들에 의해 전달되는 컨트롤러 특정 키(key)들을 발생시킴으로써 다른 PMC들이 활성화되는 것을 결정할 수 있으며, 그것에 의해 각 컨트롤러가 그 자체의 키를 다시 수신할 때 그것은 모든 컨트롤러들이 활성화되는 것을 인식한다.

본 발명의 실시예들은 컴퓨터 시스템의 속도를 개선하면서 컴퓨터 시스템 내의 프로세서 기반 컴퓨터 구성요소를 에뮬레이션하기 위한 시스템을 제공한다. 프로세서 기반 컴퓨터 구성요소를 에뮬레이션하기 위한 시스템은 로직 게이트들만을 사용하여 프로세서 기반 컴퓨터 구성요소를 에뮬레이션하도록 구성된 로직 게이트 기반 디바이스를 포함하며, 여기서 로직 게이트들은 프로세서 기반 컴퓨터 구성요소에 의해 통상 취급되는 명령들의 세트를 수신하고 단지 훨씬 더 빠른 속도로 프로세서 기반 컴퓨터 구성요소에 의해 통상 출력되는 출력을 제공하도록 구성된다. 일부 실시예들에 있어서, 로직 게이트들은 프로세서 기반 컴퓨터 구성요소에 의해 통상 취급되는 모든 가능한 명령들의 서브세트만을 인지하고 응답하도록 구성된다. 로직 게이트 기반 디바이스는 컴퓨터 시스템에 의해 활성적으로 사용되지 않는 레거시(legacy) 컴퓨터 디바이스의 에뮬레이션을 제공할 수 있지만, 그의 존재는 1) 컴퓨터 시스템의 기본 입력/출력 시스템(BIOS: basic input/output system) 및 2) 컴퓨터 시스템의 운영 체제(OS: operating system) 중 하나의 적절한 동작에 요구된다.

본 발명의 어떤 실시예들은 디지털 통신들을 인코딩(encoding), 송신, 및 디코딩(decoding)하기 위한 방법을 제공하며, 여기서 통신의 데이터 부분들은 본래 추가 데이터 비트(bit)들을 필요로 하지 않고 수신된 데이터 부분들의 유효성에 관한 체크섬(checksum) 정보를 포함한다. 방법은 디지털 데이터의 어떤 패턴(pattern)들이 무효인 방식을 사용하여 정보를 디지털 스트림(digital stream)으로 인코딩하는 단계 및 송신기를 반복적으로 사용하여 디지털 스트림을 송신하는 단계를 포함한다. 수신기는 수신된 정보를 수신하고, 수신된 정보는 유효 및 무효 패턴들에 대해 평가된다. 유효 개시 패턴 다음에 하나 이상의 유효 데이터 패턴들이 뒤따를 때, 수신된 정보는 단지 유지되고 디코딩된다.

개시 패턴은 데이터 스트림에 포함되는 데이터의 유형에 관한 정보를 포함할 수 있다. 또한, 개시 패턴은 디지털 스트림이 반복된 횟수에 관한 정보를 포함할 수 있다.

본 발명의 실시예들은 컴퓨터 시스템에 통합된 PMC를 사용하여 컴퓨터 시스템의 시동 및 기능을 감시하기 위한 방법을 제공한다. 방법은 컴퓨터 시스템에 PMC를 제공하는 단계를 포함하며, 여기서 PMC는 컴퓨터 시스템의 전력을 관리하고 컴퓨터 시스템의 기능에 관한 정보를 컴퓨터 시스템으로부터 획득할 수 있도록 컴퓨터 시스템에 연결되고, 여기서 PMC는 송신기에 동작적으로 연결된다. 또한, 방법은 컴퓨터 시스템의 시동 및 동작을 감시하기 위해 PMC를 사용하는 단계, 컴퓨터 시스템의 시동 및 동작 중 적어도 하나에 관한 이벤트들에 로그하기 위해 PMC를 사용하는 단계, 및 송신기를 사용하여 로그된 이벤트들을 송신하기 위해 PMC를 사용하는 단계를 포함한다.

로그된 이벤트들은 시동시 컴퓨터 시스템에 의해 발생된 포스트 코드들을 포함할 수 있다. 로그된 이벤트들이 포스트 코드들을 포함할 때, PMC는 시동시 언제라도 포스트 코드들을 송신할 수 있다. 로그된 이벤트들은 셧다운(shutdown) 시간 및 검출된 비정상 온도의 시간 중 하나에서 컴퓨터 시스템으로부터 획득된 온도 판독을 추가적으로 또는 대안적으로 포함할 수 있다. 일부 실시예들에 있어서, 컴퓨터 시스템의 운영 체제는 외부 송신을 위해 PMC에 메시지(message)들을 전송하도록 구성된다.

본 발명의 실시예들은 전원 트래킹 장치를 제공하기 위한 기술에 관한 것이다. 특히, 본 발명의 적어도 일부 실시예들은 연산 회로의 제 1 전력 입력이 연산 회로의 제 2 전력 입력에 대해 미리 정의된 관계를 유지하는 것을 보증하기 위한 전원 트래킹 장치에 관한 것이다.

본 발명의 실시예들은 기준 전압원, 비교기, 및 스위치(switch)를 갖는 전원 트래킹 장치를 포함한다. 기준 전압원은 기준 전압을 비교기의 제 1 입력에 제공한다. 비교기의 제 2 입력은 제 1 전력 입력에 결합된다. 비교기의 출력은 기준 전압 및 제 1 전력 입력의 상대 전압의 함수로서 상태를 스위칭한다. 비교기의 출력은 스위치를 제어하고, 따라서 기준 전압 및 제 1 전력 입력의 상대 전압에 따라 스위치를 개방 및 폐쇄한다. 스위치는 전원과 제 2 전력 입력 사이에 배치된다. 따라서, 제 2 전력 입력은 제 1 전력 입력에 대한 미리 정의된 관계로 유지될 수 있다.

본 발명의 실시예들의 방법들 및 프로세스들은 개인용 컴퓨팅 엔터프라이즈들의 영역에 특히 유용한 것으로 증명되었을지라도, 당업자들은 제어 시스템들 또는 스마트 인터페이스 시스템(smart-interface system)들을 사용하는 임의의 산업에 대한 엔터프라이즈들 및/또는 그러한 디바이스들의 실시예들로부터 이득을 얻는 엔터프라이즈들을 포함하는 커스터마이즈(customize) 가능 엔터프라이즈들을 산출하기 위해 본 발명의 방법들 및 프로세스들이 각종 상이한 애플리케이션들 및 각종 상이한 제조 영역들에 사용될 수 있다는 것을 인식할 것이다. 그러한 산업들의 예들은 자동차 산업들, 항공 전자 산업들, 유압 제어 산업들, 오토/비디오 제어 산업들, 전기통신 산업들, 의료 산업들, 특수 용도 산업들, 및 가전 기기 산업들을 포함하지만, 이들에 제한되지 않는다. 따라서, 본 발명의 시스템들 및 방법들은 현재 컴퓨터 기술에 의해 종래에 이용되지 않았던 마켓(market)들을 포함하는 많은 상이한 마켓들에 이점들을 제공할 수 있다.

본 발명의 실시예들은 컴퓨터 시스템들 진단 정보를 무선으로 수신하고 그러한 정보를 커스터마이즈 가능하게 표시하기 위한 시스템들 및 방법들을 제공한다. 정보는 다양한 범용 컴퓨터 시스템들 및 다양한 특수 용도 컴퓨터 시스템들을 포함하는, 다양한 기존 및 장래의 컴퓨터 시스템들로부터 수신될 수 있다. 본 출원에 개시된 바와 같이, 컴퓨터 시스템에 통합된 플랫폼 관리 컨트롤러(PMC) 또는 유사한 디바이스는 컴퓨터 시스템 정보를 감시하고 감시된 정보를, 예컨대 적외선에 의해 송신하거나 그 외 전달한다. 본 발명의 실시예들은 송신된 정보를 수신하므로, 그것은 본 출원에 개시된 것과 같은 다양한 목적들에 이용될 수 있다.

본 발명의 실시예들에 있어서, PMC 또는 다른 유사한 디바이스에 의해 송신된 복수의 로그된 이벤트들은 무선 진단 디바이스와 같은 진단 디바이스에 의해 수신 및 감시될 수 있다. 본 발명의 적어도 일부 실시예들에 있어서, 진단 디바이스의 처리 특징들은 주로 또는 전적으로 로직 게이트들로 구현된다. 그러한 실시예들은 본 출원에서 더 상세히 논의되는 어떤 장점들을 제공한다. 본 출원에서 논의되는 진단 디바이스들의 어떤 실시예들은 로직 게이트 디바이스들을 사용하여 구현될지라도, 진단 디바이스들은 이 기술분야에 현재 공지되어 있거나 장래에 발명될 유형들의 각종 다른 컴퓨터 시스템들에 정보를 제공하거나 정보를 전달한다는 것이 인식될 것이다. 예를 들어, 적어도 일부 실시예들에 있어서, 진단 디바이스는 범용 직렬 버스(USB: universal serial bus) 연결, 이더넷(Ethernet) 연결 등과 같은, 유선 또는 무선 연결을 사용하여 외부 컴퓨터 시스템에 연결될 수 있다. 그러한 연결은 통신들이 PMC 또는 다른 유사한 디바이스로부터 수신되는 시간, 또는 어느 나중의 시간을 포함하는, 진단 디바이스의 사용 동안 언제든지 이루어질 수 있다. 그러므로, 이하의 논의는 어떤 이유로 진단 디바이스와 함께 사용되거나 진단 디바이스에 연결될 수 있는 컴퓨터 시스템들을 설명하도록 의도된다.

본 발명의 실시예들은 일시적 전기 연결들에 관한 것이다. 특히, 본 발명은 인쇄 회로 기판(PCB)로부터 또는 PCB에 정보를 수신 또는 송신하기 위해 외부 디바이스를 PCB에 일시적으로 연결하기 위한 시스템들 및 방법들에 관한 것이다.

본 발명의 실시예들은 연결을 통해서 데이터의 전송을 용이하게 하기 위한 외부 소스와 PCB 사이의 일시적 전기 연결들과 관련하여 실시된다. 적어도 하나의 실시예들에 있어서, 일시적 전기 시스템은 PCB의 하나 이상의 에지(edge)들에 인접하여 배치된 전기 접촉 패드들을 갖는 PCB를 포함한다. 전기 접촉 패드들은 차례로 PCB 상의 특정 위치들에 전기적으로 연결된다. 시스템들은 전선 리본(electrical wire ribbon) 및 PCB의 에지(들) 상에 배치된 전기 패드들에 대응하는 하나 이상의 전기 접촉 패드들이 배치된 전선 리본의 원위 단부의 헤드(head)를 차례로 포함하는 일시적 전기 커넥터 장치를 더 포함한다.

추가 실시예들에 있어서, PCB와 일시적으로 전기적으로 연결되도록 적응된 장치는 전선 리본을 포함한다. 장치는 하나 이상의 전기 접촉 패드들이 배치된 전선 리본의 원위 단부에 헤드를 더 포함한다. 또한, 일부 실시예들에 있어서, 헤드는 그 위에 배치된 접착제를 가지며, 이는 전기 접촉 패드들을 실질적으로 둘러싼다. 사용 전에, 접착제는 사용 시에 제거될 수 있는 논-스틱 페이퍼 백킹(non-stick paper backing) 등에 의해 보호된다. 다른 실시예들에 있어서, 헤드는 헤드를 팽팽하게 하도록 조작될 수 있는 압축 피팅(compression fitting)을 포함하여, 그것은 PCB와 같은 대응하는 표면에 고정된 채로 일시적으로 남아 있는다. 또 다른 실시예들에 있어서, 헤드는 헤드 및 PCB와 같은 대응하는 표면 사이에서 일시적 연결을 용이하게 하는데 사용될 수 있는 핀(pin)들 또는 다른 로케이터들을 포함한다. 더 다른 실시예들에 있어서, 헤드는 조우(jaw)들을 폐쇄된 위치에서 바이어스(bias)하는 동작 스프링(spring)에 의해 연결된 두 개의 대향하는 조우들로 구성되어, 조우들은 사용자에 의해 선택적으로 개방될 수 있고 헤드는 PCB와 같은 대응하는 표면에 일시적으로 "클립(clip)"된다. 또 다른 실시예들에 있어서, 헤드는 PCB의 폭을 연계하여 분리한 두 개의 대향하는 고정 표면들로 구성되어, 헤드는 이에 일시적으로 고정된 채로 남아 있기 위해 PCB의 에지에 걸쳐서 일시적으로 슬립(slip)될 수 있다.

본 발명의 실시예들의 방법들 및 프로세스들은 일시적 PCB 연결들의 영역에 특히 유용한 것으로 증명되었을지라도, 당업자들은 일시적이고, 편리하며 저렴한 전기 연결들을 산출하기 위해 방법들 및 프로세스들이 각종 상이한 애플리케이션들 및 각종 상이한 제조 영역들에 사용될 수 있다는 것을 인식할 수 있다.

본 발명의 실시예들의 측면들은 논의 및 명료성을 위해 다양한 표제들을 사용하여 논의될 것이다. 표제들은 예시된 실시예들의 측면들을 용이하게 하는 것으로만 제공되고, 어떤 방식을 제한하는 것으로 의도되지 않는다.

대표적인 컴퓨터 시스템들

상술한 바와 같이, 본 발명의 실시예들은 다양한 컴퓨터 시스템들 및 구성들로 구현될 수 있고, 발명의 명칭이 Non-Peripherals Processing Control Module Having Improved Heat Dissipating Properties인 미국 특허 제7,256,991호, 발명의 명칭이 Robust Customizable Computer Processing System인 제7,242,574호, 및 발명의 명칭이 Systems and Methods for Providing a Dynamically Modular Processing Unit인 제7,075,784호에 개시된 것들과 유사한 시스템들 및 구성들을 포함한다. 단지 예시로서, 도 1 및 도 2는 원래의 번호가 유지된 미국 특허 제7,075,784호의 도 1 및 도 3의 카피(copy)들이다. 이 도면들 및 대응하는 논의(본질적으로 이하에 재현됨)는 본 발명의 적어도 어떤 실시예들이 구현될 수 있는 동작 실시예를 제공할 수 있는 대표적인 컴퓨터 시스템의 제 1 예를 다음과 같이 제공한다.

도 1 및 대응하는 논의는 본 발명의 실시예들에 따른 적절한 작동 환경의 일반적인 설명을 제공하도록 의도된다. 이하에서 더 논의되는 바와 같이, 본 발명의 실시예들은 이하에 논의되는 바와 같이, 네트워크(network) 또는 조합 구성에서 포함하는, 다양한 커스터마이즈 가능 엔터프라이즈 구성들에서 하나 이상의 동적 모듈식 프로세싱 유닛들의 사용을 포함한다.

본 발명의 실시예들은 비일시적 및/또는 유형(tangible) 컴퓨터 판독가능 매체를 포함하는, 하나 이상의 컴퓨터 판독가능 매체를 포함하며, 여기서 각 매체는 데이터를 조작하기 위한 데이터 또는 컴퓨터 실행가능 명령어들을 그 위에 포함하거나 포괄하도록 구성될 수 있다. 컴퓨터 실행가능 명령어들은, 각종 상이한 기능들을 수행할 수 있는 범용 모듈식 프로세싱 유닛과 관련된 것 또는 제한된 수의 기능들을 수행할 수 있는 특수 용도 모듈식 프로세싱 유닛과 관련된 것과 같은, 하나 이상의 프로세서들에 의해 액세스(access)될 수 있는 데이터 구조들, 객체들, 프로그램들, 루틴(routine)들, 또는 다른 프로그램 모듈(program module)들을 포함한다.

컴퓨터 실행가능 명령어들은, 엔터프라이즈의 하나 이상의 프로세서들로 하여금 특정 기능 또는 기능들의 그룹을 수행하게 하고, 처리 방법들에 대한 단계들을 구현하기 위한 프로그램 코드 수단의 예들이다. 더욱이, 실행가능 명령어들의 특정 시퀀스는 그러한 단계들을 구현하는데 사용될 수 있는 대응하는 작업들의 일례를 제공한다.

컴퓨터 판독가능 매체의 예들은 랜덤 액세스 메모리("RAM": random-access memory), 읽기 전용 메모리("ROM": read-only memory), 프로그램가능 읽기 전용 메모리("PROM": programmable read-only memory), 소거가능 프로그램가능 읽기 전용 메모리("EPROM": erasable programmable read-only memory), 전기적 소거가능 프로그램가능 읽기 전용 메모리("EEPROM": electrically erasable programmable read-only memory), 콤팩트 디스크 읽기 전용 메모리("CD-ROM": compact disk read-only memory), 임의의 솔리드 스테이트(solid-state) 저장 디바이스(예를 들어, 플래시 메모리(flash memory), 스마트 미디어(smart media) 등), 또는 프로세싱 유닛(processing unit)에 의해 액세스될 수 있는 데이터 또는 실행가능 명령어들을 제공할 수 있는 임의의 다른 디바이스 또는 구성요소를 포함한다.

도 1을 참조하면, 대표적인 엔터프라이즈는 범용 또는 특수 용도 프로세싱 유닛으로서 사용될 수 있는 모듈식 프로세싱 유닛(modular processing unit)(10)을 포함한다. 예를 들어, 모듈식 프로세싱 유닛(10)은 단독으로 또는 개인용 컴퓨터, 노트북 컴퓨터(notebook computer), 개인 휴대 정보 단말기("PDA"; personal digital assistant) 또는 다른 핸드헬드 디바이스(hand-held device), 워크스테이션(workstation), 미니컴퓨터(minicomputer), 메인프레임(mainframe), 슈퍼컴퓨터(supercomputer), 멀티프로세서 시스템(multi-processor system), 네트워크 컴퓨터(network computer), 프로세서 기반 소비자 디바이스(processor-based consumer device), 스마트 가전 또는 디바이스, 제어 시스템 등과 같은, 하나 이상의 유사한 모듈식 프로세싱 유닛들과 함께 사용될 수 있다. 다수의 프로세싱 유닛들을 동일한 엔터프라이즈에서 사용하는 것은 증가된 프로세싱 능력들들을 제공한다. 예를 들어, 엔터프라이즈의 각 프로세싱 유닛은 특정 태스크(task)에 전용될 수 있거나 분산 프로세싱에 공동으로 관여할 수 있다.

도 1에서, 모듈식 프로세싱 유닛(10)은 그의 다양한 구성요소들을 연결하도록 구성될 수 있는 하나 이상의 버스(bus)들 및/또는 인터커넥트(interconnect)(들)(12)를 포함하고, 데이터가 2개 이상의 구성요소들 사이에서 교환될 수 있게 한다. 버스(들)/인터커넥트(들)(12)는 다양한 버스 아키텍처들 중 어느 하나를 사용하는 메모리 버스(memory bus), 주변 버스(peripheral bus), 또는 로컬 버스(local bus)를 포함하는 다양한 버스 구조들 중 하나를 포함할 수 있다. 버스(들)/인터커넥트(들)(12)에 의해 연결된 전형적인 구성요소들은 하나 이상의 프로세서들(14) 및 하나 이상의 메모리들(16)을 포함한다. 다른 구성요소들은 이하 "데이터 조작 시스템(들)(18)"으로서 지칭되는 로직, 하나 이상의 시스템들, 하나 이상의 서브시스템들 및/또는 하나 이상의 I/O 인터페이스들의 사용을 통해서 버스(들)/인터커넥트(들)(12)에 선택적으로 연결될 수 있다. 더욱이, 다른 구성요소들은 로직, 하나 이상의 시스템들, 하나 이상의 서브시스템들 및/또는 하나 이상의 I/O 인터페이스들의 사용을 통해서 버스(들)/인터커넥트(들)(12)의 외부에 연결될 수 있으며, 및/또는 모듈식 프로세싱 유닛(들)(30) 및/또는 전용 디바이스(들)(34)와 같은 로직, 하나 이상의 시스템들, 하나 이상의 서브시스템들 및/또는 하나 이상의 I/O 인터페이스들로서 기능할 수 있다. I/O 인터페이스들의 예들은 하나 이상의 대용량 저장 디바이스 인터페이스들, 하나 이상의 입력 인터페이스들, 하나 이상의 출력 인터페이스들 등을 포함한다. 따라서, 본 발명의 실시예들은 하나 이상의 I/O 인터페이스들을 사용하는 능력 및/또는 사용된 로직 또는 다른 데이터 조작 시스템에 기초하여 제품의 유용성을 변경하는 능력을 포함한다.

로직은 인터페이스, 시스템의 일부, 서브시스템에 결합될 수 있으며, 및/또는 특정 태스크를 수행하는데 사용될 수 있다. 따라서, 로직 또는 다른 데이터 조작 시스템은 예를 들어 IEEE 1394(파이어와이어(firewire))를 가능하게 할 수 있으며, 여기서 로직 또는 다른 데이터 조작 시스템은 I/O 인터페이스이다. 대안적으로 또는 추가적으로, 모듈식 프로세싱 유닛이 다른 외부 시스템 또는 서브시스템에 결합되는 것을 가능하게 하는 로직 또는 다른 데이터 조작 시스템이 사용될 수 있다. 예를 들어, 외부 시스템 또는 서브시스템은 특수 I/O 연결을 포함하거나 포함하지 않을 수 있다. 대안적으로 또는 추가적으로, 로직 또는 다른 데이터 조작 시스템이 사용될 수 있으며, 여기서 어떤 외부 I/O도 로직과 관련되지 않는다. 또한, 본 발명의 실시예들은 차량들의 ECU들, 유압 제어 시스템들 등을 위한 것과 같은, 특수 로직 및/또는 특정 하드웨어를 제어하는 방법을 프로세서에 통지하는 로직의 사용을 포함한다. 더욱이, 당업자들은 본 발명의 실시예들이 로직, 시스템들, 서브시스템들 및/또는 I/O 인터페이스들을 사용하는 다양한 상이한 시스템들 및/또는 구성들을 포함하는 것을 인식할 것이다.

상기 제공된 바와 같이, 본 발명의 실시예들은 하나 이상의 I/O 인터페이스들을 사용하는 능력 및/또는 사용된 로직 또는 다른 데이터 조작 시스템에 기초하여 제품의 유용성을 변경하는 능력을 포함한다. 예를 들어, 모듈식 프로세싱 유닛(10)은 데스크톱 컴퓨터(desktop computer)로서의 사용을 위해 설계된 하나 이상의 I/O 인터페이스들 및 로직을 포함하는 개인용 컴퓨팅 시스템의 일부인 경우, 로직 또는 다른 데이터 조작 시스템은 2개의 표준 RCA들을 통해서 아날로그 오디오(analog audio)를 취하여 그들을 IP 어드레스(address)에 방송하기 원하는 뮤직 스테이션(music station)을 위한 오디오 인코딩을 수행하기 위해 플래시 메모리 또는 로직을 포함하는 것으로 변경될 수 있다. 따라서, 모듈식 프로세싱 유닛(10)은 모듈식 프로세싱 유닛(10)의 백 플레인(back plane) 상에서 데이터 조작 시스템(들)(예를 들어, 로직, 시스템, 서브시스템, I/O 인터페이스(들) 등)에 이루어진 수정으로 인해 컴퓨터 시스템이라기보다는 오히려 기구로서 사용되는 시스템의 일부일 수 있다. 따라서, 백 플레인 상에서의 데이터 조작 시스템(들)의 수정은 모듈식 프로세싱 유닛의 적용을 변경할 수 있다. 따라서, 본 발명의 실시예들은 충분히 적응가능한 모듈식 프로세싱 유닛들(10)을 포함한다.

상기 제공된 바와 같이, 프로세싱 유닛(10)은 중앙 프로세서와 같은 하나 이상의 프로세서들(14) 및 선택적으로 특정 기능 또는 태스크를 수행하도록 설계된 하나 이상의 다른 프로세서들을 포함한다. 그것은 전형적으로 메모리(들)(16), 자기 하드 디스크(magnetic hard disk), 제거가능 자기 디스크, 자기 카세트(magnetic cassette), 광 디스크(optical disk)와 같은, 컴퓨터 판독가능 매체 상에, 또는 통신 연결로부터 제공되는 명령어들을 실행하고, 컴퓨터 판독가능 매체로 간주될 수도 있는 프로세서(14)이다.

메모리(들)(16)는 데이터를 조작하기 위한 데이터 또는 명령어들을 그 위에 포함하거나 포괄하도록 구성될 수 있고, 버스(들)/인터커넥트(들)(12)를 통해서 프로세서(들)(14)에 의해 액세스될 수 있는 하나 이상의 컴퓨터 판독가능 매체를 포함한다. 메모리(들)(16)는 예를 들어, 정보를 영속적으로 저장하는데 사용되는 ROM(들)(20), 및/또는 정보를 일시적으로 저장하는데 사용되는 RAM(들)(22)을 포함할 수 있다. ROM(들)(20)은 예컨대 모듈식 프로세싱 유닛(10)의 시동 동안 통신을 수립하는데 사용되는 하나 이상의 루틴들을 갖는 기본 입력/출력 시스템("BIOS")을 포함할 수 있다. 동작 동안, RAM(들)(22)은 하나 이상의 운영 체제들과 같은 하나 이상의 프로그램 모듈들, 애플리케이션 프로그램들, 및/또는 프로그램 데이터를 포함할 수 있다.

예시된 바와 같이, 본 발명의 적어도 일부 실시예들은 각종 상이한 애플리케이션들에서 유닛의 사용을 가능하게 하는 보다 강고한 프로세싱 유닛을 제공하는 비-주변 포장(encasement)을 포함한다. 도 1에서, 하나 이상의 대용량 저장 디바이스 인터페이스들(데이터 조작 시스템(들)(18)으로서 예시됨)은 하나 이상의 대용량 저장 디바이스들(24)을 버스(들)/인터커넥트(들)(12)에 연결하는데 사용될 수 있다. 대용량 저장 디바이스들(24)은 모듈식 프로세싱 유닛(10) 주변에 있고, 모듈식 프로세싱 유닛(10)이 대량의 데이터를 유지하는 것을 가능하게 한다. 대용량 저장 디바이스들의 예들은 하드 디스크 드라이브(hard disk drive)들, 자기 디스크 드라이브들, 테이프 드라이브(tape drive)들, 광 디스크 드라이브들, 및 솔리드 스테이트 드라이브들을 포함한다.

대용량 저장 디바이스(24)는 자기 하드 디스크, 제거가능 자기 디스크, 자기 카세트, 광 디스크, 솔리드 스테이트 메모리, 또는 다른 컴퓨터 판독가능 매체로부터 판독되며 및/또는 이들에 기록될 수 있다. 대용량 저장 디바이스들(24) 및 그들의 대응하는 컴퓨터 판독가능 매체는 운영 체제와 같은 하나 이상의 프로그램 모듈들, 하나 이상의 애플리케이션 프로그램들, 다른 프로그램 모듈들, 또는 프로그램 데이터를 포함할 수 있는 데이터 및/또는 실행가능 명령어들의 비휘발성 스토리지(storage)를 제공한다. 그러한 실행가능 명령어들은 본 출원에 개시된 방법들을 위한 단계들을 구현하기 위한 프로그램 코드 수단의 예들이다.

데이터 조작 시스템(들)(18)은 데이터 및/또는 명령어들이 하나 이상의 대응하는 주변 I/O 디바이스들(26)을 통해서 모듈식 프로세싱 유닛(10)과 교환될 수 있게 하는데 사용될 수 있다. 주변 I/O 디바이스들(26)의 예들은 키보드(keyboard)와 같은 입력 디바이스들 및/또는 마우스(mouse), 트랙볼(brackball), 광 펜(light pen), 스타일러스(stylus), 또는 다른 포인팅 디바이스(pointing device), 마이크로폰(microphone), 조이스틱(joystick), 게임 패드(game pad), 위성 방송 수신 안테나, 스캐너(scanner), 캠코더(camcorder), 디지털 카메라(digital camera), 센서 (sensor)등과 같은 대체 입력 디바이스들, 및/또는 모니터(monitor) 또는 표시 화면, 스피커(speaker), 프린터(printer), 제어 시스템 등과 같은 출력 디바이스들을 포함한다. 유사하게, 주변 I/O 디바이스들(26)을 버스(들)/인터커넥트(들)(12)에 연결하는데 사용될 수 있는 특수 로직과 결합되는 데이터 조작 시스템(들)(18)의 예들은 직렬 포트, 병렬 포트, 게임 포트, 범용 직렬 버스("USB"), 파이어와이어(IEEE 1394), 무선 수신기, 비디오 어댑터(video adapter), 오디오 어댑터, 병렬 포트, 무선 송신기, 임의의 병렬 또는 직렬화된 I/O 주변 장치들 또는 다른 인터페이스를 포함한다.

데이터 조작 시스템(들)(18)은 하나 이상의 네트워크 인터페이스들(28)을 통해서 정보의 교환을 가능하게 한다. 네트워크 인터페이스들(28)의 예들은 정보가 프로세싱 유닛들 사이에서 교환될 수 있게 하는 연결, 근거리 통신망("LAN": local area network) 또는 모뎀(modem)에 연결하기 위한 네트워크 어댑터, 무선 링크, 또는 인터넷(Internet)과 같은 광역 통신망("WAN": wide area network))에 연결하기 위한 다른 어댑터를 포함한다. 네트워크 인터페이스(28)는 모듈식 프로세싱 유닛(10)과 통합되거나 주변에 있을 수 있고, LAN, 무선 네트워크, WAN 및/또는 프로세싱 유닛들 사이의 임의의 연결과 결합될 수 있다.

데이터 조작 시스템(들)(18)은 모듈식 프로세싱 유닛(10)이 정보를 하나 이상의 다른 로컬 또는 리모트(remote) 모듈식 프로세싱 유닛들(30) 또는 컴퓨터 디바이스들과 교환할 수 있게 한다. 모듈식 프로세싱 유닛(10)과 모듈식 프로세싱 유닛(30) 사이의 연결은 하드와이어(hardwire) 및/또는 무선 링크들을 포함할 수 있다. 따라서, 본 발명의 실시예들은 직접적인 버스 투 버스(bus-to-bus) 연결들을 포함한다. 이것은 대형 버스 시스템의 제작을 가능하게 한다. 또한, 그것은 엔터프라이즈의 직접적인 버스 투 버스 연결들로 인해 현재 공지되어 있는 해킹(hacking)을 제거한다. 더욱이, 데이터 조작 시스템(들)(18)은 모듈식 프로세싱 유닛(10)이 정보를 하나 이상의 전용 I/O 커넥트들(32) 및/또는 하나 이상의 전용 디바이스들(34)과 교환할 수 있게 한다.

프로세싱 유닛에 액세스가능한 프로그램 모듈들 또는 그의 일부들은 리모트 메모리 저장 디바이스에 저장될 수 있다. 더욱이, 네트워크 시스템 또는 조합된 구성에서, 모듈식 프로세싱 유닛(10)은 기능들 또는 태스크들이 복수의 프로세싱 유닛들에 의해 수행되는 분산 컴퓨팅 환경에 관여할 수 있다. 대안적으로, 조합된 구성/엔터프라이즈의 각 프로세싱 유닛은 특정 태스크에 전용될 수 있다. 따라서, 예를 들어, 엔터프라이즈의 하나의 프로세싱 유닛은 비디오 데이터에 전용될 수 있고, 그렇게 함으로써 종래의 비디오 카드를 대체하고, 그러한 태스크들을 종래 기술을 통해서 수행하기 위해 증가된 프로세싱 능력들을 제공한다.

당업자들은 본 발명의 실시예들이 다양한 구성들을 포함할 수 있는 것을 인식할지라도, 내구성 있고 동적인 모듈식 프로세싱 유닛의 대표적인 실시예를 예시하는 도 2에 대한 참조가 이루어진다. 도 2의 예시된 실시예에 있어서, 프로세싱 유닛(40)은 내구성 있고 동적인 모듈러(modular)이다. 예시된 실시예에 있어서, 유닛(40)은 냉각 팬(cooling fan)에 대한 임의의 요구를 제거하는, 진보한 열역학 냉각 모델을 사용하는 대략 3-1/2-인치(8.9 cm) 큐브 플랫폼(cube platform)이다.

그러나, 본 출원에 제공된 바와 같이, 본 발명의 실시예들은 강제 공기 냉각 프로세스 및/또는 액체 냉각 프로세스와 같은, 열역학 냉각 프로세스에 더하여 또는 이 대신에 다른 냉각 프로세스들의 사용을 포함한다. 더욱이, 예시된 실시예가 3-1/2-인치 큐브 플랫폼을 포함할지라도, 당업자들은 본 발명의 실시예들이 3-1/2-인치 큐브 플랫폼보다 크거나 작은 모듈식 프로세싱 유닛의 사용을 포함하는 것을 인식할 것이다. 유사하게, 다른 실시예들은 큐브와 다른 형상들의 사용을 포함한다.

또한, 프로세싱 유닛(40)은 프로세싱 및 메모리 비율들을 최적화하는 적층 마더보드(motherboard) 구성, 및 능력들을 증대시키고 하드웨어 및 소프트웨어 안정성 둘 다를 증가시키는 버스 아키텍처를 포함한다. 또한, 당업자들은 본 발명의 다른 실시예들이 비-적층 마더보드들을 포함하는 것을 인식할 것이다. 더욱이, 본 발명의 다른 실시예들은 내장 마더보드 구성들을 포함하며, 여기서 마더보드의 구성요소들은 구성요소들 사이에 절연(insulation)을 제공하고 하나 이상의 재료들에 구성요소들을 매립시키는 하나 이상의 재료들에 내장되고, 하나 이상의 마더보드 구성요소들은 기계, 광학, 전기 또는 전자 기계적이다. 더욱이, 내장 마더보드 구성들의 실시예들의 적어도 일부는 3차원 스테릴(sterile) 환경에 고정되는 기계, 광학, 전기 및/또는 전자 기계 구성요소들을 포함한다. 그러한 재료들의 예들은 폴리머들(polymers), 고무들, 에폭시들(eposies), 및/또는 임의의 비-전도(non-conducting) 임베딩 화합물(들)을 포함한다.

본 발명의 실시예들은 프로세싱 다양성의 제공을 포함한다. 예를 들어, 본 발명의 적어도 일부 실시예들에 따르면, 프로세싱 부담들은 확인된 후, 처리 전력을 선택적으로 전용 및/또는 할당함으로써 해결된다. 예를 들어, 특정 시스템은 특정 요구들에 따라 정의되어, 프로세싱 전력의 전용 또는 할당이 제어된다. 따라서, 하나 이상의 모듈식 프로세싱 유닛들은 그러한 특정 요구들(예를 들어, 비디오, 오디오, 하나 이상의 시스템들, 하나 이상의 서브시스템들 등)에 프로세싱 전력을 제공하기 위해 전용될 수 있다. 일부 실시예들에 있어서, 처리 전력을 제공할 수 있는 것은 중앙 유닛에 관한 부하를 감소시킨다. 따라서, 처리 전력은 요구된 영역들에 공급된다.

예시된 실시예에서, 프로세싱 유닛(40)이 2 GHz 프로세서 및 1.5 GB의 RAM을 포함할지라도, 당업자들은 본 발명의 다른 실시예들이 보다 빠른 또는 보다 느린 프로세서 및/또는 다소의 RAM의 사용을 포함하는 것을 인식할 것이다. 본 발명의 적어도 일부 실시예들에 있어서, 프로세싱 유닛의 프로세서의 속도 및 RAM의 용량은 프로세싱 유닛이 사용되는 종류에 의존한다.

매우 동적이고, 커스터마이즈 가능하며, 교환 가능한 백 플레인(44)은 주변 장치들 및 수직적 애플리케이션(vertical application)들에 지지를 제공한다. 예시된 실시예에 있어서, 백 플레인(44)은 포장(42)에 선택적으로 결합되고, 유닛(40)을 동적으로 커스터마이즈 가능하게 할 수 있는 하나 이상의 특징들, 인터페이스들, 능력들, 로직 및/또는 구성요소들을 포함할 수 있다. 예시된 실시예에 있어서, 백 플레인(44)은 DVI 비디오 포트(46), 이더넷 포트(48), USB 포트들(50)(50a 및 50b), SATA 버스 포트들(52)(52a 및 52b), 전력 버튼(54), 및 전력 포트(56)를 포함한다. 또한, 백 플레인(44)은 위에서 표시된 바와 같이 전체 시스템의 프로세싱 능력들을 증가시키기 위해, 및 이하에 더 개시되는 바와 같은 스케일링(scaling) 프로세싱을 제공하기 위해 2개 이상의 모듈식 프로세싱 유닛들을 함께 전기적으로 결합하는 메커니즘을 포함할 수 있다.

당업자들은 그의 대응하는 특징들, 인터페이스들, 능력들, 로직 및/또는 구성요소들을 갖는 백 플레인(44)은 단지 대표적이고, 본 발명의 실시예들은 각종 상이한 특징들, 인터페이스들, 능력들 및/또는 구성요소들을 갖는 백 플레인들을 포함하는 것을 인식할 것이다. 따라서, 프로세싱 유닛은 사용자가 프로세싱 유닛의 로직, 특징들 및/또는 능력들을 선택적으로 수정하는 것을 가능하게 하기 위해, 어떤 백 플레인이 다른 백 플레인에 의해 대체되는 것을 가능하게 함으로써 동적으로 커스터마이즈 가능해진다.

더욱이, 본 발명의 실시예들은 하나 이상의 모듈식 프로세싱 유닛들(40)의 사용을 각종 상이한 환경들에서 가능하게 하기 위해 임의의 수 및/또는 유형의 로직 및/또는 커넥터들을 포함한다. 예를 들어, 환경들은 차량들(예를 들어, 자동차들, 트럭들, 오토바이들 등), 유압 제어 시스템들, 및 다른 환경들을 포함한다. 백 플레인 상에서의 데이터 조작 시스템(들)의 변경은 이하에 더 논의되는 바와 같이, 다양한 환경들에 대한 스케일링을 수직적으로 및/또는 수평적으로 가능하게 한다.

더욱이, 본 발명의 실시예들은 모듈식 프로세싱 유닛들의 다양한 형상들 및 사이즈들을 포함한다. 예를 들어, 도 2에서, 모듈식 프로세싱 유닛(40)은 다양한 이유들로 종래의 프로세싱 유닛들보다 작은 큐브이다.

당업자들에 의해 인식되는 바와 같이, 본 발명의 실시예들은 예를 들어, 사용된 재료들, 사이즈 및/또는 형상, 로직의 유형 및/또는 주변 장치들 기반 포장의 제거 때문에 종래 기술보다 지지하기 더 용이하다.

예시된 실시예에 있어서, 전력 버튼(54)은 3개의 상태들, 즉 전력 부팅(power booting)에 대한 온, 오프 및 대기를 포함한다. 전력이 턴 온되어 수신될 때, 유닛(40)은 메모리에 지원된 운영 체제를 로딩(loading) 및 부팅하라고 지시한다. 전력이 턴 오프될 때, 프로세싱 제어 유닛(40)은 임의의 진행 중인 프로세싱을 중단하고 대기 상태 전에 수행되는 셧 다운 시퀀스를 개시할 것이며, 여기서 시스템은 활성화될 전력 온 상태를 대기한다.

USB 포트들(50)은 주변 입력/출력 디바이스들을 프로세싱 유닛(40)에 연결하도록 구성된다. 그러한 입력 또는 출력 디바이스들의 예들은 키보드, 마우스 또는 트랙볼, 모니터, 프린터, 다른 프로세싱 유닛 또는 컴퓨터 디바이스, 모뎀, 및 카메라를 포함한다.

SATA 버스 포트들(52)은 프로세싱 유닛(40) 주변에 있는 대용량 저장 디바이스들을 전자적으로 결합 및 지원하도록 구성된다. 그러한 대용량 저장 디바이스들의 예들은 플로피 디스크 드라이브들(floppy disk drives), CD-ROM 드라이브들, 하드 드라이브들, 테이프 드라이브들 등을 포함한다.

상기 제공된 바와 같이, 본 발명의 다른 실시예들은 당업자에 의해 인식되는 바와 같이, 주변 디바이스들을 연결하기 위한 추가적인 포트들 및 수단의 사용을 포함한다. 그러므로, 본 출원에서 구체적으로 식별 및 설명되는 것을 연결하기 위한 특정 포트들 및 수단은 단지 예시적이고 어떤 방식을 제한하지 않는 것으로 의도된다.

본 출원에 제공된 바와 같이, 다양한 장점들은 대형의, 주변 팩(pack) 컴퓨터 유닛들에 걸쳐서 비주변 프로세싱 유닛의 사용을 통해 존재한다. 예로서, 사용자는 엔터프라이즈를 수용하는데 필요한 공간을 선택적으로 감소시킬 수 있고, 및 보다 작은 전체 공간을 더 요구하지 않고 프로세싱 유닛들을 시스템에 추가함으로써 증가된 프로세싱 전력을 더 제공할 수 있다. 더욱이, 프로세싱 유닛들 각각은 브레이크다운(break down)되기 쉬운 시스템들보다는 오히려 솔리드 스테이트 구성요소들을 포함하므로, 개별 유닛들은 은닉될 수 있다(예를 들어, 벽, 가구, 벽장, 시계와 같은 장식 디바이스 내에).

개별 프로세싱 유닛들/큐브들의 내구성은 프로세싱이 종래 기술에서 다르게 생각될 수 없는 위치들에서 발생하는 것을 가능하게 한다. 예를 들어, 프로세싱 유닛들은 지중에 매립되고, 수중에 위치되고, 해중에 매립되고, 지중으로 수백 피트(feet)를 구동하는 드릴 비트(drill bit)들의 헤드들, 가구 내의 불안정한 표면들 등 상에 배치될 수 있다. 잠재적인 프로세싱 위치들은 무한이다. 다른 장점들은 노이즈(noise) 및 열의 감소, 가구, 설치물들, 차량들, 구조들, 지지체들, 기구들, 설비, 개인 아이템들 등과 같은, 소비자들이 이용가능한 다양한 디바이스들에 커스터마이즈 가능한 "스마트(smart)" 기술을 제공하는 능력 등을 포함한다.

도 2에서, 도면은 비주변 기반 포장(42), 냉각 프로세스(예를 들어, 열역학 대류 냉각, 강제 공기, 및/또는 액체 냉각), 최적화된 적층 회로 기판 구성, 및 동적 백 플레인(44)을 보다 완전히 예시하기 위해 제거된 큐브의 측벽들을 갖는 프로세싱 유닛(40)을 예시한다. 예시된 실시예에 있어서, 다양한 기판들은 기판들의 우발적인 분리를 방지하고 교환가능성을 가능하게 하는, 억지 끼워맞춤(force fit) 기술을 사용함으로써 함께 결합된다. 기판들은 증대된 EMI 분배 및/또는 칩/로직 배치를 제공한다. 당업자들은 본 발명의 실시예들이 임의의 수의 기판들 및/또는 구성들을 포함하는 것을 인식할 것이다. 더욱이, 기판 구조들은 하나 이상의 애플리케이션들 및/또는 특징들에 기초하여 특정 이점 및/또는 요구에 대해 수정될 수 있다. 도 2에서, 프로세싱 유닛(40)은 2개의 평행 측면 기판들(62)(62a 및 62b)을 포함하는 적층 회로 기판/마더보드 구성(60) 및 측면 기판들(62)을 가로지르고 이들을 전자적으로 결합하는 중앙 기판(64)을 포함한다. 예시된 실시예는 트리보드(tri-board) 구성을 제공할지라도, 당업자들은 본 발명의 실시예들이 3개보다 작은 기판들을 갖는 기판 구성들, 및 3개보다 많은 기판들을 갖는 적층 기판 구성들을 포함하는 것을 인식할 것이다. 더욱이, 본 발명의 실시예들은 서로 직각을 이루는 기판들 이외의, 회로 기판들의 다른 구성들을 포함한다.

예시된 실시예에 있어서, 적층 마더보드(60)는 마더보드(60)를 포장(42)에 결합하기 위한 수단을 사용하여 포장(42) 내에서 지지된다. 예시된 실시예에 있어서, 마더보드(60)를 포장(42)에 결합하기 위한 수단은 마더보드(60)의 적어도 일부를 선택적으로 수용하도록 및 마더보드(60)를 적소에 유지하도록 구성되는 다양한 채널 슬롯(channel slot)들을 포함한다. 개선 기술에 업그레이드(upgrade)가 필요하므로, 예컨대 프로세서(66)가 개선된 프로세서로 대체되어야 할 때, 대응하는 기판(예를 들어, 중앙 기판(64))은 포장(42)으로부터 제거되고, 새로운 프로세서를 갖는 새로운 기판은 업그레이드를 가능하게 하기 위해 삽입된다. 따라서, 본 발명의 실시예들은 필요에 따라 업그레이들을 용이하게 하고 커스터마이즈 가능 및 동적 프로세싱 유닛을 제공하는 것으로 증명되었다.

또한, 프로세싱 유닛(40)은 하나 이상의 태스크들을 수행하도록 구성되는 하나 이상의 프로세서들을 포함한다. 도 2에서, 하나 이상의 프로세서들은 중앙 기판(64)에 결합되는 프로세서(66)로서 예시된다. 기술이 향상됨에 따라, 프로세싱 유닛(40)의 사용자가 프로세서(66)를 업그레이된 프로세서로 대체하기를 원하는 시기가 존재할 수 있다. 따라서, 중앙 기판(64)은 포장(42)으로부터 제거될 수 있고, 업그레이드된 프로세서를 갖는 새로운 중앙 기판은 유닛(40)과 공동으로 설치 및 사용될 수 있다. 따라서, 본 발명의 실시예들은 용이하게 업그레이드되는 동적 커스터마이즈 가능 프로세싱 유닛들을 포함하고, 따라서 종래 기술과 대조적으로 오래 지속되는 플랫폼을 제공한다.

도 3 및 대응하는 논의는 본 발명의 적어도 어떤 실시예들이 구현될 수 있는 다른 적절한 동작 환경의 일반적인 설명을 제공하도록 의도된다. 당업자는 본 발명의 실시예들이 하나 이상의 컴퓨팅 디바이스들에 의해 및 네트워크 구성을 포함하는 다양한 시스템 구성들에서 실시될 수 있는 것을 인식할 것이다. 그러나, 본 발명의 방법들 및 프로세스들이 범용 컴퓨터를 포함하는 시스템과 관련하여 유용한 것으로 증명되었을지라도, 본 발명의 실시예들은 범용 프로세싱 유닛들, 디지털/미디어 신호 프로세서들(DSP/MSP: digital/media signal processors), 주문형 집적회로들(ASIC: application specific integrated circuits), 독립형 전자 디바이스들을 갖는 내장 시스템들을 포함하는 다양한 환경들, 및 다른 그러한 전자 환경들에서의 방법들 및 프로세스들의 이용을 포함한다.

본 발명의 실시예들은 하나 이상의 컴퓨터 판독가능 매체를 포함하며, 여기서 각 매체는 데이터 또는 데이터를 조작하기 위한 컴퓨터 실행가능 명령어들을 그 에 포함하거나 포괄하도록 구성될 수 있다. 컴퓨터 실행가능 명령어들은 각종 상이한 기능들을 수행할 수 있는 범용 컴퓨터와 관련된 것 또는 제한된 수의 기능들을 수행할 수 있는 특수 용도 컴퓨터와 관련된 것과 같은, 프로세싱 시스템에 의해 액세스될 수 있는 데이터 구조들, 객체들, 프로그램들, 루틴들, 또는 다른 프로그램 모듈들을 포함한다. 컴퓨터 실행가능 명령어들은 프로세싱 시스템으로 하여금 특정 기능 또는 기능들의 그룹을 수행하게 하고, 본 출원에 개시된 방법들에 대한 단계들을 구현하기 위한 프로그램 코드 수단의 예들이다. 더욱이, 실행가능 명령어들의 특정 시퀀스는 그러한 단계들을 구현하는데 사용될 수 있는 대응하는 작업들의 일례를 제공한다. 컴퓨터 판독가능 매체의 예들은 랜덤 액세스 메모리("RAM"), 읽기 전용 메모리("ROM"), 프로그램가능 읽기 전용 메모리("PROM"), 소거가능 프로그램가능 읽기 전용 메모리("EPROM"), 전기적 소거가능 프로그램가능 읽기 전용 메모리("EEPROM"), 콤팩트 디스크 읽기 전용 메모리("CD-ROM"), 또는 프로세싱 시스템에 의해 액세스될 수 있는 데이터 또는 실행가능 명령어들을 제공할 수 있는 임의의 다른 디바이스 또는 구성요소를 포함한다. 본 발명의 실시예들이 모든 유형들의 컴퓨터 판독가능 매체의 사용을 포함할지라도, 청구항들에 열거된 어떤 실시예들은 유형(tangible) 및/또는 비-일시적 컴퓨터 판독가능 매체의 사용에 제한될 수 있고, 본 출원에서 사용되는 "유형 컴퓨터 판독가능 매체(tangible computer-readable medium)" 및 "비-일시적 컴퓨터 판독가능 매체(non-transitory computer-readable medium)"(또는 복수의 변형들)라는 구는 일시적인 전파 신호들 그 자체를 배제하도록 의도된다.

도 3을 참조하면, 본 발명의 실시예들과 함께 사용되거나 이들을 구현하는 대표적인 시스템은 범용 또는 특수 용도 컴퓨터 또는 다양한 소비자 전자 디바이스들 중 어느 하나일 수 있는, 컴퓨터 디바이스(70)를 포함한다. 예를 들어, 컴퓨터 디바이스(70)는 개인용 컴퓨터, 노트북 컴퓨터, 넷북(netbook), 개인 휴대 정보 단말기("PDA") 또는 다른 핸드헬드 디바이스, 워크스테이션, 미니컴퓨터, 메인프레임, 슈퍼컴퓨터, 멀티프로세서 시스템, 네트워크 컴퓨터, 프로세서 기반 소비자 전자 디바이스 등일 수 있다.

컴퓨터 디바이스(70)는, 그의 다양한 구성요소들을 연결하도록 구성될 수 있고 데이터가 2개 이상의 구성요소들 사이에서 교환될 수 있게 하는 시스템 버스(system bus)(72)를 포함한다. 시스템 버스(72)는 다양한 버스 아키텍처들 중 어느 하나를 사용하는 메모리 버스 또는 메모리 컨트롤러, 주변 버스, 또는 로컬 버스를 포함하는 다양한 버스 구조들 중 하나를 포함할 수 있다. 시스템 버스(72)에 의해 연결되는 전형적인 구성요소들은 프로세싱 시스템(74) 및 메모리(76)를 포함한다. 다른 구성요소들은 하나 이상의 대용량 저장 디바이스 인터페이스들(78), 입력 인터페이스들(80), 출력 인터페이스들(82), 및/또는 네트워크 인터페이스들(84)을 포함할 수 있고, 그 각각은 이하에 논의될 것이다.

프로세싱 시스템(74)은 중앙 프로세서와 같은 하나 이상의 프로세서들 및 선택적으로 특정 기능 또는 태스크를 수행하도록 설계된 하나 이상의 다른 프로세서들을 포함한다. 그것은 전형적으로 메모리(76), 자기 하드 디스크, 제거가능 자기 디스크, 자기 카세트, 광 디스크와 같은, 컴퓨터 판독가능 매체 상에 또는 통신 연결로부터 제공되는 명령어들을 실행하고, 컴퓨터 판독가능 매체로 간주될 수도 있는 프로세싱 시스템(74)이다.

메모리(76)는, 데이터를 조작하기 위한 데이터 또는 명령어들을 그에 포함하거나 포괄하도록 구성될 수 있고 시스템 버스(72)를 통해서 프로세싱 시스템(74)에 의해 액세스될 수 있는, 하나 이상의 컴퓨터 판독가능 매체를 포함한다. 메모리(76)는 예를 들어, 정보를 영속적으로 저장하는 사용되는 ROM(들)(88), 및/또는 정보를 일시적으로 저장하는데 사용되는 RAM(들)(90)을 포함할 수 있다. ROM(들)(88)은 통신을, 예컨대 컴퓨터 디바이스(70)의 시동 동안 수립하는데 사용되는 하나 이상의 루틴들을 갖는 기본 입력/출력 시스템("BIOS")을 포함할 수 있다. RAM(들)(90)은 하나 이상의 운영 체제들, 애플리케이션 프로그램들, 및/또는 프로그램 데이터와 같은, 하나 이상의 프로그램 모듈들을 포함할 수 있다.

하나 이상의 대용량 저장 디바이스 인터페이스들(78)은 하나 이상의 대용량 저장 디바이스들(86)을 시스템 버스(72)에 연결하는데 사용될 수 있다. 대용량 저장 디바이스들(26)은 컴퓨터 디바이스(70)에 통합될 수 있거나 주변에 있을 수 있고, 컴퓨터 디바이스(70)가 대량의 데이터를 유지하는 것을 가능하게 한다. 선택적으로, 하나 이상의 대용량 저장 디바이스들(86)은 컴퓨터 디바이스(70)로부터 제거될 수 있다. 대용량 저장 디바이스들의 예들은 하드 디스크 드라이브들, 자기 디스크 드라이브들, 테이프 드라이브들, 솔리드 스테이트 드라이브들 및 광 디스크 드라이브들을 포함한다. 대용량 저장 디바이스(86)는 자기 하드 디스크, 제거가능 자기 디스크, 자기 카세트, 광 디스크, 솔리드 스테이트 디바이스, 또는 다른 컴퓨터 판독가능 매체로부터 판독되며 및/또는 이들에 기록될 수 있다. 대용량 저장 디바이스들(86) 및 그들의 대응하는 컴퓨터 판독가능 매체는 운영 체제, 하나 이상의 애플리케이션 프로그램들, 다른 프로그램 모듈들, 또는 프로그램 데이터와 같은, 하나 이상의 프로그램 모듈들을 포함할 수 있는 데이터 및/또는 실행가능 명령어들의 비휘발성 스토리지를 제공한다. 그러한 실행가능 명령어들은 본 출원에 개시된 방법들을 위한 단계들을 구현하기 위한 프로그램 코드 수단의 예들이다.

하나 이상의 입력 인터페이스들(80)은 사용자가 데이터 및/또는 명령어들을 하나 이상의 대응하는 입력 디바이스들(92)을 통해서 컴퓨터 디바이스(70)에 입력할 수 있게 하는데 사용될 수 있다. 그러한 입력 디바이스들의 예들은 키보드 및 마우스, 트랙볼, 광 펜, 스타일러스, 또는 다른 포인팅 디바이스, 마이크로폰, 조이스틱, 게임 패드, 위성 방송 수신 안테나, 스캐너, 캠코더, 디지털 카메라 등과 같은, 대체 입력 디바이스들을 포함한다. 유사하게, 입력 디바이스들(92)을 시스템 버스(72)에 연결하는데 사용될 수 있는 입력 인터페이스들(80)의 예들은 직렬 포트, 병렬 포트, 게임 포트, 범용 직렬 버스("USB"), 집적 회로, 파이어와이어(IEEE 1394), 또는 다른 인터페이스를 포함한다. 예를 들어, 일부 실시예들에 있어서, 입력 인터페이스(80)는 특정 애플리케이션을 위해 설계된 주문형 집적 회로(ASIC)를 포함한다. 추가 실시예에 있어서, ASIC는 내장되고, 기존 회로 빌딩 블록(building block)들을 연결한다.

하나 이상의 출력 인터페이스들(82)은 하나 이상의 대응하는 출력 디바이스들(94)을 시스템 버스(72)에 연결하는데 사용될 수 있다. 출력 디바이스들의 예들은 모니터 또는 표시 화면, 스피커, 프린터, 다기능 주변 장치 등을 포함한다. 특정 출력 디바이스(94)는 컴퓨터 디바이스(70)와 함께 통합되거나 이 주변에 있을 수 있다. 출력 인터페이스들의 예들은 비디오 어댑터, 오디오 어댑터, 병렬 포트 등을 포함한다.

하나 이상의 네트워크 인터페이스들(84)은 컴퓨터 디바이스(70)가 하드와이어 및/또는 무선 링크들을 포함할 수 있는 네트워크(98)를 통해서, 컴퓨터 디바이스들(96)로서 예시된, 하나 이상의 다른 로컬 또는 리모트 컴퓨터 디바이스들과 정보를 교환할 수 있게 한다. 네트워크 인터페이스들의 예들은 근거리 통신망("LAN") 또는 모뎀에 연결하기 위한 네트워크 어댑터, 무선 링크, 또는 인터넷과 같은 광역 통신망("WAN")에 연결하기 위한 다른 어댑터를 포함한다. 네트워크 인터페이스(84)는 컴퓨터 디바이스(70)와 함께 통합되거나 이 주변에 있을 수 있다. 네트워크 시스템에서, 액세스가능 프로그램 모듈들 또는 그의 일부들은 리모트 메모리 저장 디바이스에 저장될 수 있다. 더욱이, 네트워크 시스템 컴퓨터에서, 디바이스(70)는 기능들 또는 태스크들이 복수의 네트워크 컴퓨터 디바이스들에 의해 수행되는, 분산 컴퓨팅 환경에 관여할 수 있다.

따라서, 당업자들이 본 발명의 실시예들이 많은 유형들의 시스템 구성들을 갖는 각종 상이한 환경들에서 실시될 수 있다는 것을 인식할지라도, 도 4는 본 발명의 어떤 실시예들과 관련하여 사용될 수 있는 대표적인 네트워크 시스템 구성을 제공한다. 도 4의 대표적인 시스템은 네트워크(98)를 통해서 하나 이상의 다른 컴퓨터 디바이스들(클라이언트(102) 및 클라이언트(104)로서 예시됨) 및 하나 이상의 주변 디바이스들(106)(다기능 주변 장치(MFP: multifunctional peripheral)와 같음)에 연결되는 클라이언트(100)로서 예시된 컴퓨터 디바이스를 포함한다. 도 4는 네트워크(98)에 연결되는 클라이언트(100), 2개의 추가적인 클라이언트들, 즉 클라이언트(102) 및 클라이언트(104), 하나의 주변 디바이스(106), 및 선택적으로 서버(108)를 포함하는 실시예를 예시할지라도, 대안적인 실시예들은 네트워크(98)에 연결되는 다소의 클라이언트들, 하나보다 많은 주변 디바이스, 주변 디바이스들 없음, 서버(108) 없음, 및/또는 하나보다 많은 서버(108)를 포함한다. 본 발명의 다른 실시예들은 하나 이상의 컴퓨터 디바이스들이 하나 이상의 로컬 또는 리모트 주변 디바이스들에 연결될 수 있는 로컬, 네트워크, 또는 피어 투 피어(peer-to-peer) 환경들을 포함한다. 더욱이, 본 발명에 따른 실시예들은 단일 가전 기기, 무선 네트워크 환경들, 및/또는 인터넷과 같은 광역 네트워크 환경들도 포함한다.

플랫폼 관리

상술된 일반적인 컴퓨터 시스템들은 일반적으로 본 발명의 실시예들과 함께 사용될 수 있는 컴퓨터 시스템들을 나타낸다. 본 발명의 실시예들의 측면들은 위에서 논의되고 본 출원에 참고문헌으로 통합되어 있는, 발명의 명칭이 Non-Peripherals Processing Control Module Having Improved Heat Dissipating Properties인 미국 특허 제7,256,991호, 발명의 명칭이 Robust Customizable Computer Processing System인 제7,242,574호, 및 발명의 명칭이 Systems and Methods for Providing a Dynamically Modular Processing Unit인 제7,075,784호에 개시된 특정 컴퓨터 시스템들의 유형을 더 구체적으로 참조하여, 아래에서 더 상세히 설명될 것이다. 본 발명의 어떤 실시예들은 참조된 특허들에 개시된 컴퓨터 시스템의 유형과 관련된 피처(feature)들에 특히 적용가능할 수 있을지라도, 다른 컴퓨터 시스템 유형들에 적용가능한 본 출원에서 논의되는 본 발명의 다양한 실시예들의 임의의 피처들은 그러한 컴퓨터 시스템 유형들과 함께 사용되도록 의도되는 것이 이해되어야 한다.

참조된 특허들에 개시되고 도 2에 대해 위에서 논의된 컴퓨터 시스템은 특히 수개의 상호 접속 회로 기판들을 포함한다. 본 발명의 실시예들은 인증 및 보안 특징들을 연결된 기판들 각각에 제공한다. 예를 들어, 어떤 실시예들에 있어서, 허가된 및 인증된 회로 기판들만이 서로 사용되는 것을 보증하는 것이 바람직할 수 있다. 컴퓨터 산업에서의 하나의 현재 방해는 특히 다양한 기판 제조업자들을 고려하여, 상호 접속 회로 기판들 사이에서 발생하는 비-호환성들에 대해 발생한다. 많은 경우들에서, 기판들 사이의 비호환성은 그 제조업자가 과실이 없더라도, 어느 기판 제조업자에게 좋지 못하게 영향을 미친다. 비-인증된 및/또는 비-허가된 기판들의 사용을 방지하는 것은 비호환성들이 발생하지 않는 것을 보증할 수 있으며, 그것에 의해 기판의 제조업자(들)의 고객 만족 및 고객들의 전반적인 인상을 개선시킨다.

그러므로, 본 발명의 실시예들은 각 기판 상에 포함된 인증 칩을 제공한다. 본 출원에서 더 상세히 논의되는 바와 같이, 인증 칩들에는 인증 칩의 값을 증대시키는 추가적인 기능이 제공될 수 있으며, 그것에 의해 인증 칩을 각 기판상에 제공하는 것과 관련된 임의의 추가 비용들을 상쇄시킨다. 본 출원에서 더 상세히 논의되는 하나의 그러한 기능은 전력 관리이다. 그러한 것으로서, 인증 칩들은 그러한 경우들에서 플랫폼 관리 컨트롤러들(PMCs)로 간주될 수 있다. 게다가, 본 출원에서 더 상세히 논의되는 바와 같이, 인증 칩들은 칩의 로직 연결들에 의해 전적으로 수행되는 칩들에 의해 기능들이 제공되는 상태에서, 모든 기능이 로직 게이트들에 의해 제공되는 로직 게이트 칩들일 수 있다. 이것은 이하에 더 상세히 논의되는 바와 같이, 인증 칩들이 매우 신속히 기능하는 것을 가능하게 하고, 또한 중단들을 필요로 하지 않고 인증 칩들이 다수의 기능들을 병렬로 수행하는 것을 가능하게 한다.

인증 칩들이 회로 기판들에 통합되는 경우들에서, 제조업자은 기판들이 어떤 호환성 표준들에 따르며 및/또는 각 기판이 연결될 수 있는 모든 다른 기판들과 호환되는 것을 보증하기 위해 테스팅을 수행할 수 있으며, 그것에 의해 인증 칩들을 모두 포함하는 기판들을 포함하는 시스템에 연결될 때 인증 칩을 포함하는 각 기판이 간단히 작동하는 것을 보증한다. 게다가, 인증된 기판들만이 그러한 시스템들에 사용되는 것을 보증하는 것이 바람직할 수 있다. 그러므로, 시스템들(예를 들어 인증 칩들)은 인증된 및/또는 허가된 기판들만이 시스템에 연결되거나 시스템이 기능하지 않는 것을 보증하도록 구성될 수 있다.

이것이 수행될 수 있는 하나의 방법은 컴퓨터 시스템의 키 기능을 인증 칩(들)에 통합하는 것이다. 예를 들어, 나중에 더 상세히 논의되는 바와 같이, 어떤 레거시 구성요소들이 더 이상 BIOS 또는 OS에 의해 사용되지 않더라도, 많은 기본 입력/출력 시스템들(BIOSs) 및 운영 체제들(OSs)은 그러한 구성요소들이 시스템에 존재하는 것을 필요로 한다. 동일한 기능 또는 다른 요구된 기능이 인증 칩(들)에 통합되면, 비인증된 기판(인증 칩이 없는 것)이 시스템에 통합될 때 시스템은 기능하지 않을 것이다.

이것을 달성하는 대안적인 방법은 인증 칩이 컴퓨터 시스템(상술되고 이하에 상세히 논의되는 플랫폼 관리 컨트롤러로서)의 전력을 관리하게 하는 것이다. 인증 칩이 없는 기판이 시스템에 삽입될 때, 요구된 전력 제어 기능이 없을 수 있다. 대안적으로, 인증 칩들은 서로 통신할 수 있고, 모든 요구된 전력 제어 기능이 존재할지라도, 그들은 인증 칩이 없는 것을 검출할 수 있고 전력을 컴퓨터 시스템에 제공하는 것을 거부할 수 있다. 본 출원에서 구체적으로 논의된 것들 이외의 다양한 유사한 인증/허가 제어 기법은 본 발명의 실시예들에 의해 포함된다.

인증/허가 문제들에 더하여, 일부 실시예들에서 인증 칩들은 어떤 소프트웨어 패키지들에 통상 요구되는 것과 같은, 보안/인증 특징들을 제공하는데 사용될 수 있다. 예를 들어, 어떤 소프트웨어 라이선스들은 특정 기계에 설치를 제한한다. 인증 칩들은 칩들의 로직 게이트들에 포함된 고유 일련 번호를 포함할 수 있다. 일부 실시예들에 있어서, 신뢰된 플랫폼 관리의 측면들은 인증 칩들을 사용하여 제어될 수 있고, 제조업자/시스템 키뿐만 아니라 고객 키(예를 들어 소프트웨어 라이선스 등에 의해 제공되는 등)의 제공을 포함할 수 있으며, 그 조합은 시스템이 토큰 파일(tocken file)을 수신 및 해독하는 것을 가능하게 할 수 있고, 그렇게 함으로써 허가된 소프트웨어에 대해서 인가된 시스템을 인증한다. 일련 번호, 제조업자/시스템 키, 고객 키 등은 인증 칩들에 포함될 수 있고, 컴퓨터 시스템 내의 다수의 칩들에 걸쳐서 분배될 수 있으므로 복제 또는 절도를 방지한다.

본 발명의 적어도 일부 실시예들에 있어서, 하나 이상의 플랫폼 관리 컨트롤러들(PMCs)(본 출원에서, 단일 컨트롤러 및/또는 다수의 컨트롤러들에 대한 참조는 원하는 컴퓨터 시스템 구성에 적용가능한 모든 경우의 단일 및/또는 다수의 컨트롤러들을 지칭하는 것으로서 해석되어야 함)은 이 기술분야에서 이전에 이용가능하지 않은 방식으로 측파대 관리를 제공하는 기능을 한다. 이전 측파대 관리 기법들은 연결된 컴퓨터 시스템들을 관리하기 위해 개별 컴퓨터 시스템 및/또는 프로세서에 의존한다. 그러한 측파대 관리 기법들은 개별 컴퓨터 시스템이 파워 온된 채로 남아 있는 것 및 추가적인 컴퓨팅 전력을 요구하는 상황들에 대한 감시를 필요로 한다. 그러한 요구가 검출될 때, 개별 컴퓨터 시스템/프로세서는 요구된 추가적인 컴퓨팅 전력을 제공하기 위해 파워 온 신호들을 다른 컴퓨터들에 제공한다. 기존 측파대 관리기들은 본래 추가적인 컴퓨터 디바이스들이 성공적으로 파워 온되고 이용가능한지의 여부를 단지 판단할 수 있고, 임의의 실패들에 관한 임의의 상세를 제공할 수 없다. 그러한 시스템들의 비용 때문에, 기존 측파대 관리기들은 서버(sever)급 기계들에 제한되어 왔다.

본 발명의 실시예들은 이전에 가능하지 않은 방법들로 저비용이고 강력한 측파대 관리를 제공한다. 본 발명의 실시예들에 따른 PMC는 컴퓨터 시스템이 전원에 연결될 때 언제든지 전원 공급된다. 컴퓨터 시스템의 일부 추가적인 구성요소들(예를 들어, 정적 메모리, 온도 모니터들 등)에는 컴퓨터가 턴 오프될 때에도, PMC를 사용하여 또는 PMC에 의해 전력이 제공될 수도 있다. 이것은 컴퓨터 시스템이 파워 온되지 않거나 시스템 고장으로 인해 파워 온될 수 없을 때에도 컴퓨터 시스템의 안전을 감시하고, 컴퓨터 시스템에 관한 이벤트들에 로그하며, 외부 디바이스들에 컴퓨터 시스템의 상태에 관한 것을 전달하기 위해 추가적인 자원들을 PMC에 제공한다.

측파대 관리는 로직만을 사용하여 수행되기 때문에, 측파대 관리에 대한 전력 요구들은 매우 작다. 게다가, PMC를 사용하는 측파대 관리는 기존 시스템들 이상으로 관리 및 진단 능력들을 크게 증대시킨다. PMC를 사용하는 측파대 관리의 관련 비용은 기존 시스템들에 대해 크게 감소되기 때문에, 그것은 데스크톱, 랩톱, 및 및 워크스테이션 시스템들을 포함하는 이전에 사용되지 않았던 시스템들, 뿐만 아니라, 내장 시스템들에 용이하게 통합될 수 있다.

관리 및 진단 능력들에 관하여, 측파대 관리 시스템은 이전에 가능한 것보다 훨씬 더 상세히 시스템 안전을 감시할 수 있다. PMC는 감시 및 관리되는 컴퓨터 시스템에 강고히 통합되기 때문에, 관리되는 것에서의 큰 유연성이 제공된다. 예를 들어, PMC는 다양한 시스템 버스들, 다양한 전원들/전력 레일(rail)들, 온도 측정 디바이스들 등에 연결될 수 있고, 시스템을 관리하기 위해 이러한 및 다른 소스들 중 어느 하나 또는 모두로부터 정보를 기록 및 사용할 수 있다.

이것의 일례는 전력 제어의 영역에 있다. 기존 관리 시스템들이 일반적으로 컴퓨터 시스템에 대한 전력을 단순히 턴 온하는 경우, 본 발명의 실시예들은 지능적이고, 유연하며, 제어된 전력 관리를 제공한다. 전형적인 컴퓨터 시스템에서, 다양한 전원들, 전압들, 및 전력 레일들이 존재한다. 전형적인 시스템 내의 다수의 컴퓨터 칩들은 어떤 전압들이 어떤 순서로 인가될 필요가 있거나 컴퓨터 칩들에 대한 손상의 위험이 존재한다. 그러므로, 기존 시스템들은 다양한 전원들이 턴 온되는 시퀀스를 제공하지만, 전원들의 활성화의 순서의 단순한 타이밍 이외 시퀀스의 어떤 관리도 전형적으로 존재하지 않는다. 따라서, 전원이 전형적인 시스템에서 고장나면, 시스템은 다른 전원들의 활성화로 더 이동되며, 이는 바람직하지 않은 전압 상황들로 인해 칩 손상을 발생시킬 수 있다.

본 발명의 실시예들의 PMC는 이 문제를 방지하기 위해 전원들을 지능적으로 활성화시킨다. 다양한 전원들은 상이한 회로 기판들 상에 위치되기 때문에(도 2 참조), 다양한 전원들의 제어는 주된 PMC의 감독 하에 다양한 PMC들에 분배될 수 있다. 본 발명의 실시예들에 있어서, 전력을 단순히 턴 온하기보다는 오히려, PMC는 전원들의 활성화를 임의의 필요한 시퀀스로 명령하지만, PMC가 전력 레일들을 감시함으로써 각각 활성화된 전원이 적절히 작동하고 원하는 전압들이 온되어 적절해지는(또는 이하에 더 상세히 논의되는 바와 같이 적절히 램프 온되는) 것을 검증할 때 단지 시퀀스의 다음 단계로 진행한다. 고장이 검출될 때(예를 들어 전원은 어떤 시간의 기간 내에 활성화되지 않음), PMC는 활성화된 임의의 전원들을 턴 오프함으로써 고장에 로그하고 전력을 지능적으로 셧 다운한다.

또한, 적어도 일부 실시예들에 있어서, 전력은 바람직하지 않은 전압 조건들을 방지하도록 설계된 시퀀스에서 지능적으로 셧 다운된다(앞서 논의된 바와 같이 정상적으로 또는 고장의 검출 시에). 유사하게, 하나 이상의 전원들의 정전이 정상 시동 후에 발생할 때, 일부 실시예들에서의 PMC는 고장난 전원의 정지 후에 원하지 않는 전압 조건을 야기할 수 있는 모든 다른 전원들을 신속히 턴 오프함으로써 응답한다. 고장 이벤트는 로그되고, 나머지 전원들은 PMC에 의해 감시 및 제어된 보호 시퀀스에서 셧다운된다. PMC에 의해 취해진 이러한 유형들의 작업들은 원하지 않는 전압 조합들이 시스템에서 발생하지 않게 하고, 그렇게 함으로써 컴퓨터 시스템 구성요소들에 대한 손상을 제한하거나 방지한다. 따라서, 기존 시스템들에 비해서, PMC의 실시예들은 유지 및 복구 비용들을 크게 감소시킬 수 있는 컴퓨터 시스템의 다른 부분들에 대한 부수적인 손상의 가능성을 크게 감소시킨다.

게다가, PMC는 고장의 로그를 포함하기 때문에, 고장을 처리하려고 노력하는 기술자는 정확한 고장의 기록을 가져서 디버길될 회로, 칩, 또는 구성요소를 정확히 인식할 수 있다. 이하에 더 상세히 논의되는 바와 같이, PMC는 고장시 및 다음 파워 온 시도시 언제든지 고장들(및 임의의 다른 기록된 데이터)의 로그의 전부 또는 일부를 송신한다. 컴퓨터 시스템이 턴 오프될 때에도 PMC는 전원 공급되기 때문에, 시스템을 다시 파워 온하려고 시도하기 이전부터 파워 온 신호를 수신하면 그것은 고장들의 로그의 전부 또는 일부를 송신할 수 있다. 따라서, 후속 파워 온 시도가 실패될지라도, PMC는 이전 실패들에 관한 정보를 전달한다. 이 정보는 이하에 더 상세히 논의되는 바와 같이, 다양한 외부 수신 디바이스들에 의해, 예컨대 적외선 신호에 의해 또는 직접적인 전기 연결에 의해 수신될 수 있다.

PMC가 로직 게이트들을 사용하여 전적으로 구현되기 때문에, PMC는 검출된 고장들에 신속히 응답할 수 있다. 예를 들어, PMC는 전형적으로 수 클록 사이클들 내에 응답할 수 있어서(예를 들어, 하나 이상의 전원들을 비활성화시킴), PMC에 의해 제공되는 보호를 더 증대시킨다. 로직 게이트들에 의해 제공되는 병렬 프로세싱 전력은 다른 태스크들이 PMC에 의해 처리되고 있을 때에도, 중단을 필요로 하지 않거나 컴퓨터 시스템상에서 발생하는 다른 작업들에 의해 영향을 받지 않고 그것이 응답할 수 있는 것을 보증한다.

컴퓨터 시스템이 전원에 연결될 때 PMC가 항상 실행 가능할지라도, PMC는 컴퓨터 시스템이 전원으로부터 분리되면 실행 가능하지 않게 될 수 있다. 다중 회로 기판들 상에 다수의 PMC들을 갖는 시스템들에서(예를 들어, 도 2에 도시된 것과 유사한 시스템에서와 같이), PMC들은 컴퓨터 시스템에 대해 임의의 작업을 취하려고 시도하기 전에 모든 PMC들이 활성화되어 기능하는 것을 보증하도록 구성될 수 있다. PMC들 사이에서 통신을 가능하게 하기 위해, 전력 관리 버스(전력 관리 정보를 전달하기 위해) 및 보안 버스(예를 들어, 보안/인증 정보를 전달하기 위해)와 같은, 하나 이상의 버스들은 PMC들 사이에 수립될 수 있다.

상이한 PMC들(110, 112, 114) 사이의 예시적인 연결들의 하나의 도시는 도 5에 도시되어 있다. 각 PMC(110, 112, 114)는 그 자체의 로컬(116, 118, 120) 자원들 및 제어된 요소들에 액세스할 수 있다. 예시된 실시예에 있어서, 하나의 PMC는 "메인(main)" PMC이고, 로그 정보를 저장하기 위한 메모리(122) 및 로그 정보의 에러 보고를 위한 적외선(IR: infrared) 송신기(124)(또는 다른 통신 디바이스)에 액세스할 수 있다. 각 PMC(110, 112, 114)는 매우 작은 사이즈일 수 있으므로, 회로 기판들 상에 최소 면적 자원들을 차지한다. 게다가, 디바이스들은 PMC 고장의 기회가 매우 적어지도록 매우 적은 전력을 사용하고, 본질적으로 파손되지 않으며, 및/또는 매우 신뢰성이 있을 수 있다.

전력이 우선 PMC들에 전달될 때(예를 들어, 전원이 컴퓨터 시스템에 연결됨), 각 활성 PMC(110, 112, 114)는 다른 컨트롤러들에 의해 통신되고 있는 정보가 유효 정보이거나(예를 들어, 다른 컨트롤러들은 적절히 기능하는 시간을 가짐) 시동 동안 다른 컨트롤러들에 의해 통신되고 있는 단지 정크(junk) 정보인지를 판단한다. 이 판단을 달성하는 다양한 방법들이 존재하지만, 하나의 방법은 각 컨트롤러가 고유 키 코드(key code)를 연속적으로 다른 컨트롤러들에 전달함과 동시에 그것이 연속적으로 수신하는 임의의 코드들을 전달하는 것이다. 따라서, 각 컨트롤러가 그 자체의 키 코드를 다시 수신할 때, 그것은 다른 컨트롤러들이 적절히 기능하고 있는 것을 인식하고, 컨트롤러들은 그들 사이의 모든 장래의 데이터 및 정보가 유효한 것을 인식하는 그의 동작을 공동으로 개시할 수 있다.

상술한 바와 같이, 추가적인 기능이 PMC에 추가될 수 있다. 컴퓨터들의 진화하는 성질 때문에, 기존 BIOS들 및 OS들은 더 이상 컴퓨터에 대한 유용한 기능들을 수행하지 않는 레거시 하드웨어 디바이스들로부터 입력을 통상 필요로 한다. 다양한 BIOS들 및 OS들로부터 그러한 레거시 디바이스들에 대한 모든 참조들을 제거하는 것이 복잡하며 및/또는 곤란하므로, 대부분의 하드웨어 제조업자들은 약간의 비용 및 회로 기판 면적의 낭비로 이 디바이스들을 그 설계들에 간단히 계속해서 추가하고 있다.

본 발명의 실시예들에 있어서, PMC는 PS/2 키보드 컨트롤러들 및 비디오 컨트롤러와 같은, 하나 이상의 레거시 디바이스들의 기능을 에뮬레이션하는데 사용된다. 그러한 에뮬레이션은 이 기술분야에서 통상 수행되는 프로세서/마이크로컨트롤러를 사용하는 대신, PMC의 로직 게이트들을 사용하여 스트레이트 로직(straight logic)에서 달성된다. 이 구현은 특히 속도에서 어떤 장점들을 갖는다. 컴퓨터 디바이스의 부팅 시에, BIOS는 통상 비디오 컨트롤러 및 키보드 컨트롤러를 체크(check)한다. 기존 시스템들에서, 질의들은 1/10초와 1/2초 사이에서 취해질 수 있다. PMC의 경우에, 질의들은 수개 내지 소수의(예를 들어 10까지의) 클록 사이클들에서 응답될 수 있어서, 더 빠른 부팅 시간들을 초래한다. 물론, 에뮬레이션된 컨트롤러에 의해 제공되는 응답들을 수락하기 위해 특정 BIOS가 일부 지연을 필요로 하는 것으로 발견되면, 지연은 응답이 제공되기 전에 추가될 수 있다.

다른 예로서, USB 키보드가 시스템에 연결되고 명령이 키보드로부터 수신될 때, 어떤 OS들은 USB 키보드 명령을 중단하기 위해 이동되기 전에 명령이 PS/2 컨트롤러로부터 수신되었는지를 PS/2 키보드 컨트롤러에 다수의 횟수(60회와 동수임) 질의한다. 인식될 수 있는 바와 같이, 이러한 및 유사한 질의는 시동 동안 마주친 상술한 지체에 더하여 사용 동안 시스템을 상당히 느리게 할 수 있다. 그러므로, 신속히 응답하는 PMC의 능력은 시스템 대기 시간(latency)들을 크게 감소시킬 수 있다.

에뮬레이션된 레거시 디바이스들의 실제 기능은 BIOS 또는 OS의 기대들을 만족시키는 것 이외의 컴퓨터 시스템의 동작에 필요하지 않으므로, 레거시 디바이스(들)의 모든 기능의 전체 에뮬레이션은 일반적으로 필요하지 않다. 그 대신에, 명령들이 BIOS/OS에 의해 송출되는 것 및 응답들이 회답으로 예상되는 것에 관한 평가가 이루어질 수 있고, 단지 그 명령들 및 응답들은 PMC의 게이트들로 구성된다. 앞서 논의된 바와 같이, PMC의 병렬 프로세싱 능력들은 컨트롤러가 전력 관리 요구들 및 디바이스 에뮬레이션 요구들(및 임의의 다른 요구들)에 동시에 응답하는 것을 가능하게 해서, 전체 시스템 응답 속도들을 더 증대시킨다.

앞서 논의된 에뮬레이션은 로직 내의 마이크로프로세서 또는 마이크로컨트롤러 에뮬레이션의 단지 일례이다. 본 발명의 실시예들은 로직 게이트들에서 마이크로프로세서들 및 마이크로컨트롤러들의 모든 전부 및 일부 에뮬레이션들을 포함한다. 로직 내의 마이크로프로세서들 및 마이크로컨트롤러들의 에뮬레이션의 다른 장점은 프로세싱의 로직 에뮬레이션이 훨씬 더 적은 전력을 전반적으로 필요로 하므로 효율 절감이다.

앞서 논의된 바와 같이, PMC는 컴퓨터 시스템의 관리 및 고장 진단뿐만 아니라, 고장 보고에도 관여할 수 있다. 이 관리 및 진단 및 에러 보고를 용이하게 하기 위해, PMC에는 컴퓨터 시스템 내의 다양한 버스들에 대한 액세스가 제공되며, 그렇게 함으로써 버스들이 달리 사용되지 않고 있을 때에 어떤 디바이스들과 통신하기 위해 그 버스들에 걸쳐서 통신들을 스누프하고 버스들을 사용할 수 있다. PMC가 연결될 수 있는 버스들의 예들은 낮은 핀 카운트(LPC) 버스 및 내부 집적 회로(I2C) 버스를 포함한다. PMC는 다양한 시스템들 정보를 감시할 수 있으므로, 그것은 검출된 에러 상황들을 더 잘 보고할 수 있고, 그렇게 함으로써 부품 문제들 및 서비스 문제들의 식별을 용이하게 할 수 있다. 비용은 수리 시에, 재설계 시에, 및 특히 문제들을 신속히 지적할 시에 절약된다.

따라서, 고장 이벤트가 발생하고 PMC가 시스템을 셧다운할 때, 로그가 형성됨으로써 고장의 원인에 관한 지식이 획득될 수 있다. 게다가, 컴퓨터 시스템이 오프될 때, PMC는 LPC 버스 및 I2C 버스에 연결된 다양한 디바이스들이 컴퓨터 시스템의 다른 구성요소들에 의해 사용되지 않고 있는 것을 인식하고, 그 후 많은 그러한 디바이스들이 파워 다운 후에도 활성인 채로 남아 있으므로 그러한 디바이스들과 통신할 수 있다. 하나의 그러한 디바이스는 온도 센서일 수 있다. 셧다운 시간 직후에, PMC는 셧다운 시 언제든지 컴퓨터 시스템의 동작 온도를 결정하기 위해 임의의 온도 센서들에 질의할 수 있고, 그것을 셧다운 후에 PMC에 액세스가능한 정적 메모리 내의 관련된 로그에 기록할 수 있다.

컴퓨터 시스템이 실행되고 있을 때, PMC는 로깅 목적들을 위해 중요할 수 있는 정보를 획득하기 위해 그것이 연결되는 다양한 버스들 및 디바이스들로부터 그것이 획득하는 정보에 의존한다. 예를 들어, 컴퓨터 시스템이 실행되고 있을 때, BIOS는 온도 정보를 온도 센서들로부터 수신할 수 있다. 예를 들어, 일부 컴퓨터 시스템들은 어떤 액션들이 취해져야 하는 온도 설정점들을 포함한다. 제 1 온도 설정점이 통과될 때, BIOS는 냉각 팬 속도를 증가시키는 것 및 프로세서 속도를 감소시키는 것과 같은, 온도 제어 노력들을 증가시키는 것을 인식할 수 있다. 제 2 온도 설정점이 통과될 때, BIOS는 컴퓨터를 보호하고 냉각을 가능하게 하기 위해 OS를 적절히 셧다운하는 것을 인식할 수 있다. 제 3 온도 설정점이 통과될 때, BIOS는 시스템을 강제적으로 및 즉시 셧다운할 수 있다. 앞서 논의된 바와 같이, PMC는 BIOS와 온도 센서들 사이의 통신들을 스누프함으로써 그런한 이벤트들에 로그하고, 온도 센서와 직접 통신함으로써 셧다운 시에 온도 판독을 더 획득한다.

PMC가 다양한 버스들에 연결될 때, 그것은 다양한 통신들에 의존할 수 있으며, 그 다수는 PMC로부터 응답을 필요로 하지 않는다. 그러므로, PMC는 로직 특징들을 포함할 수 있고, 그것에 의해 그것은 단지 LPC 버스 및 I2C 버스에 관한 어떤 종류의 통신들을 검사하며 및/또는 통신들에 응답한다. 예를 들어, PMC는 메모리 사이클 통신들을 무시하면서 LPC 버스에 관한 I/O 및 포스트 코드 어드레스된 통신들을 검사할 수 있다. 그러나, 시스템 진단에 대한 것과 같은 일부 경우들에서, PMC가 어떤 다른 작업을 취하지 않더라도, PMC는 각 버스들에 관한 모든 통신들을 스누프하도록 및 그들에 보고하도록 구성될 수 있다.

PMC가 그것이 부착되는 다양한 버스들에 관한 통신들의 서브세트만을 검사하도록 구성되는 경우, 그것은 검사하는 것들의 서브세트만에 실제로 응답할 수 있다. 예를 들어, PMC는 모든 I/O 통신들을 검사할 수 있지만, 앞서 논의된 그 디바이스들의 에뮬레이션의 일부로서 레거시 PS/2 키보드 컨트롤러 및 레거시 비디오 컨트롤러에 어드레스된 I/O 통신들의 서브세트에만 응답한다. 다른 예로서, 시스템 감시가 시동 시에 발생하는 경우들에서, PMC는 BIOS에 의해 발생되는 모든 포스트 코드들을 감시, 검사, 및 심지어 기록 및 보고할 수 있지만, 그들 중 어느 하나에 응답할 수 없다.

이하에 더 상세히 논의되는 바와 같이, PMC는 도 5에 도시된 바와 같이 적외선 송신기(84)를 사용함으로써와 같이, 컴퓨터 시스템 외부의 시스템들과 통신할 수 있다. 외부 디바이스는 본 출원에서 논의된 모든 감시된 이벤트들 및 로그된 엔트리(entry)들을 포함하여, PMC로부터의 통신들에 관한 다양한 메시지들이 표시될 수 있는 진단 목적용 표시 화면을 포함할 수 있다. 게다가, OS는 메시지들을 외부 디바이스에 송신함으로써 작동하는 PMC에 의해 구분 및 이해될 LPC 버스 상에 메시지들을 송신하는 것을 가능하게 하는 정보로 프로그램될 수 있다. 이것은 PMC의 스누핑 능력들이 사용될 수 방법의 다른 예이다.

도 6은 본 출원에서 논의된 어떤 구성요소들의 부분적인 구성의 도면 및 컴퓨터 시스템의 사우스브리지(southbridge)(128)에 연결되는 I2C 버스(126)에 대한 그의 관계를 도시한다. 또한, PMC(130)는 I2C 버스(126)에 연결되므로, 컴퓨터가 온인 동안 I2C 버스(126)에 관한 통신들을 스누프하고 컴퓨터가 오프일 때 통신하기 위해 I2C 버스(126)를 사용할 수 있다. 또한, 사우스브리지(128)는 이 기술분야에 알려져 있는 BIOS(132)에 연결된다. 온도 센서(134) 및 4 킬로바이트 정적 메모리 디바이스와 같은 메모리 디바이스(136)를 포함하는 다양한 디바이스들은 이 예에서 I2C 버스(126)에 연결된다. 컴퓨터 시스템은 이 기술분야에 알려져 있는 바와 같이, 시스템 저장 목적들을 위해 이 메모리 디바이스의 대략 540 바이트를 사용하고, 더 작은 디바이스는 적절히 기능하지 않으므로 가상의 모든 컴퓨터 시스템들은 이 양(예를 들어 4 킬로바이트들)보다 상당히 큰 메모리 디바이스를 사용한다. 적어도 일부 실시예들에 있어서, PMC(130)는 기록된 이벤트들의 로그들 또는 이벤트 코드들을 저장하기 위해 메모리 디바이스(136) 상의 추가 스토리지에 액세스한다. 이벤트 로그가 채워지므로, PMC(130)는 일반적으로 더 이상 관심없는 더 오래된 엔트리들에 겹쳐 쓴다.

온도 센서(134) 및 메모리 디바이스(136)는 컴퓨터 시스템이 오프될 때 대기 전력에 의해 전원 공급되고, PMC(130)는 그렇게 함으로써 감시 및 로깅 목적을 위해 그 디바이스들에 액세스할 수 있다. 컴퓨터 시스템이 다수의 PMC들을 포함할지라도, 다양한 PMC들은 도 5에 대해 앞서 논의된 바와 같이 그들의 정보를 "메인" PMC에 전달하고, 메인 PMC는 보고 목적을 위해 임의의 필요한 로그 이벤트들을 메모리 디바이스(136)에 저장한다. 따라서, 다양한 PMC들은 로컬 정보를 보고하고 필요에 따라 각 기판들에 관한 로컬 조건들을 관리할 수 있을지라도, 그들은 이벤트 로깅 및 보고를 처리하고 메모리 디바이스(136)와 통신하는 메인 또는 마스터(master) PMC 하에 조직화된다.

이 메인 PMC는 I/O PMC로 간주될 수 있고 IR 송신기(124)에 연결되는 도 5 내의 PMC(110)로서 예시된다. IR 송신기(124)는 라이트 플래시들의 패턴을 사용하여 PMC가 진단 시스템들 및 다른 외부 디바이스들과 무선 통신하는 것을 가능하게 한다. PMC(110)는 IR 송신기(124)를 제어하기 위해 로직 게이트들을 사용하기 때문에, 그것은 다른 임무들을 갖는 IR 송신기(124)를 통해서 임의의 통신을 병렬로 수행하고, 컴퓨터 시스템 외부에서 통신하면서 다른 임무들 중 어느 하나를 정지시키는 것을 필요로 하지 않는다. 따라서, 전력 관리 및 감시 기능들은 IR 송신기(124)를 사용하여 PMC(110)가 통신하고 있는 동안 계속되고, 어떤 마이크로컨트롤러도 수반되지 않는다.

다양한 IR 송신 및 통신 기법들이 PMC(110) 및 IR 송신기(124)에 의해 사용될 수 있을지라도, 본 발명의 일부 구현들은 개별 체크섬 또는 유효성 비트들을 필요로 하지 않고 체크섬 또는 유효성 정보를 본래 전달하는 정보 및 데이터를 제공하는 선택 기법들을 사용한다. 또한, 적외선 통신들 기법은 클록 정보를 포함한다. 많은 경우들에서, 이하에 설명되고 발명의 명칭이 Systems and Methods for Wirelessly Receiving Computer System Diagnostics Information인 우선권 출원에서, PMC(110)는 PMC(110)를 통합하는 시스템에 전용되는 외부 디바이스와 통상 통신할 수 있으므로, 상세한 헤더 정보가 요구되지 않는 것이 기대된다. 그러므로, 통신들 기법은 각 통신을 위해 송신되어야 하는 정보의 전체 양을 크게 감소시킨다.

다항식들에 의존하는 표준 데이터 암호화 메커니즘들, 패리티 비트(parity bit)들, 및 체크섬 정보를 나타내기 위해 개별 비트들을 사용하는 다른 기법들과 달리, 본 통신들 암호화 메커니즘은 어떤 본래의 유효 패턴들 및 어떤 본래의 무효 패턴들을 갖는 반복된 메시지를 사용한다. 메시지를 수신하는 수신기는 유효 패턴이 수신되었는지를 판단하기 위해 체크하고, 무효 패턴들을 갖는 통신들을 폐기한다. 메시지가 반복되기 때문에, 송신기와 수신기 사이의 지향성은 무효 정보를 폐기하지 않고 양호한 신호가 획득되고 통신이 적절히 수신될 때까지 변경될 수 있다.

본 발명의 실시예들과 함께 사용되는 특정 기법에서, 유효 패턴들은 3 비트 갭(gap)들에 의해 분리되는 4 및 8 비트 시퀀스들로 존재한다. 그 다음, 수신기는 송신의 개시를 시그널링(signaling)하는 3 비트 갭 전에 있는 유효 4 비트 시퀀스를 찾는다. 개시 시그널링 4 비트 시퀀스 및 3 비트 갭 후에, 하나 이상의 8 비트 시퀀스들이 PMC(110)에 의해 전달되는 메시지의 데이터를 포함한 상태에서 8 비트 시퀀스들이 송신 및 수신된다.

적어도 일부 경우들에서, 4 비트 헤더는 유효 개시를 메시지에 전달하는 것 이외에 2개의 목적들을 서브(serve)한다. 제 1 목적은 네 개의 유형들의 메시지들 중 하나가 헤더의 2 비트들에 의해 전달되고 있는 상태에서, 포스트 코드들, 에러 코드들 등과 같은, 이하의 메시지의 콘텐츠를 전달하는 것이다. 제 2 목적은 IR 송신기(124)를 사용하여 PMC(110)에 의해 4회까지 메시지가 반복되므로 카운터 역할을 하는 것이다. 카운터 기능은 수신 디바이스가 무선 통신 환경 및 링크의 품질을 결정하는 것을 가능하게 하고(예컨대 사용자는 수신 디바이스를 배치시킴), 수신 디바이스가 제 1 반복에 관한 전체 송신을 정확히 수신하면, 그것은 송신을 잘 수신하는 것이다. 양방향 통신이 이용가능하고 양호한 수신이 획득되었을지라도, 일부 실시예들은 수신 디바이스가 그 효과를 PMC(110)에 전달하는 것을 가능하게 할 수 있으며, 그 후에 세션(session) 내의 장래의 메시지들은 단지 2회 반복될 것이다. 대조적으로, 수신 디바이스가 나중의 송신에 관한 전체 송신만을 수신하거나 전혀 수신하지 않으면, 그것은 신호가 약하다는 것 및 디바이스를 재배치하는 것이 유리해질 수 있다는 것을 사용자에게 전달할 수 있다.

2개의 디바이스들 사이의 클록들은 2개의 방식들로 싱크(synch)될 수 있다. 첫반째, 수신 디바이스는 유효 4 비트 헤더를 수신하므로, 그것은 본래 헤더로부터 클록 정보를 수신한다. 두번째, IR 송신기(124)는 간단히 온 및 오프 펄스되지 못하지만, 각각의 온 "펄스(pulse)"는 실제로 어떤 주파수에서 일련의(예를 들어 10) 마이크로 펄스들로 형성될 수 있다. 어떤 실시예들의 IR 송신기(124)는 대략 32,768 Hz의 플래시 주파수에서 송신한다. 수신기는 이러한 또는 매우 가까운 주파수에서(예를 들어, 33 kHz에서) 펄스들을 검출하고, 그 자체의 클록을 각 10 플래시 펄스(ten-flash pulse)에 따라 설정하기 위해 10 플래시 펄스의 검출을 사용한다. 또한, 마이크로 플래시 펄스는 IR 신호와 배경 IR 노이즈를 구별하기 위해 수신 디바이스를 원조한다.

본 출원에서 논의된 것들과 유사한 방식들로, 통신 프로토콜이 제공됨으로써 개별 체크섬 데이터가 제거되고 데이터 스트림은 수신 시에 유효화될 수 있는 데이터 페이로드(payload)를 정확히 포함한다.

PMC의 감시 및 로깅 능력들 및 PMC의 통신 능력들의 조합은 PMC를 통합하는 컴퓨터 시스템들의 진단 및 수리의 설비를 크게 증대시킨다. 이하에 논의되는 바와 같이 및 무선 진단 디바이스들에 대한 우선권 출원에서, 다양한 진단 통신들은 외부 진단 디바이스에 제공될 수 있다. 통신들은 진단 디바이스를 사용하는 사람의 능력 및 숙련에 맞추어질 수 있어서, 덜 숙련된 사람에게는 결함이 발생했고 컴퓨터 디바이스가 숙련된 서비스를 필요로 한다는 단순 메시지가 제공될 수 있는 한편, 더 숙련된 사람에게는 어떤 회로 기판을 교체하라고 지시할 수 있고, 매우 숙련된 사람은 어떤 전원이 고장 났는지를 지시할 수 있다. 메시지가 진단 디바이스에 의해 표시되는 것은 거기에 포함된 프로그래밍에 기초하여 진단 디바이스에 의해 맞추어질 수 있으므로, 더 완전한 설명은 이하의 단락에 남겨 둔다.

따라서, 본 발명의 실시예들은 컴퓨터 시스템의 회로 기판들 상에 위치된 로직 게이트 기반 플랫폼 관리 컨트롤러들(PMCs)을 사용하여 컴퓨터 시스템들의 지능형 유연 관리 및 감시를 위한 시스템들 및 방법들을 제공한다. PMC들은 증대된 회로 기판 인증 및 보안, 증대된 시스템들 감시 및 보고, 및 증대된 시스템들 제어를 제공한다. 또한, PMC들은 프로세서 기반 디바이스들의 에뮬레이션을 가능하게 하고 교체된 디바이스들 및 제공된 기능에 비해서 저전력이고, 저비용이며 고속이다. 본 발명의 다양한 실시예들의 다른 이점들 및 특징들은 본 출원에서 설명되었으며, 및/또는 청구항들에 제시되어 있다.

전력 관리

"플랫폼 관리"라는 표제 하에 앞서 논의된 바와 같이, 본 발명의 일부 실시예들은 지능형 전력 관리 제어를 통합한다. 그러한 제어는 "대표적인 컴퓨터 시스템들"이라는 표제 하에 상술된 컴퓨터 시스템과 같은 전자 시스템 내에 전원들의 지능형 활성화 및 비활성화를 포함할 수 있다. 도 7 내지 도 13 및 수반하는 논의는 전력 관리를 제공하기 위한 어떤 대표적인 방법들 및 시스템들을 설명하도록 의도되지만, 다른 방법들 및 시스템들이 본 발명의 실시예들에 의해 포함된다.

우선 도 7을 참조하면, 본 발명의 일부 실시예들이 유리하게 사용될 수 있는 전자 시스템이 예시된다. 전체적으로 150으로 나타낸 전자 시스템은 연산 회로(152)를 포함한다. 예를 들어, 연산 회로는 컴퓨터 시스템 또는 그의 일부이고, 하나 이상의 집적 회로들을 포함하거나 이들로 구성된다. 연산 회로(152)는 예를 들어, 제 1 전력 입력(154) 및 제 2 전력 입력(156)과 같은, 복수의 전력 입력들을 갖는다. 연산 회로(152)는 제 1 전력 입력(154) 및 제 2 전력 입력(156)에서 제공되는 상대 전압들을 제한하는 제약들 또는 규칙들을 갖는다.

전자 시스템(150)은 예를 들어, 제 1 전원(158) 및 제 2 전원(160)과 같은, 복수의 전원들을 포함한다. 전원들은 이하에 더 상세히 설명되는 바와 같이, 전력을 연산 회로(152)에 제공한다. 전원들은 예를 들어, 선형 전원들 또는 스위칭 전원들이다. 전자 시스템(150)이 각 전원이 단일 이산(discrete) 출력 전압을 제공하는 것처럼 예시될지라도, 다중 전압 출력 전원들도 본 발명의 범위 내에 있는 것이 이해되어야 한다. 예를 들어, 제 1 전원(158) 및 제 2 전원(160)은 2개의 상이한 출력 전압들을 제공하는 단일 전원일 수 있다.

트래킹 회로(162)는 연산 회로(152)의 전력 입력들(154, 156) 중 적어도 하나에 공급되는 전력을 완화하기 위해 전원들(158, 160) 및 연산 회로(152)에 연결된다. 예를 들어, 도 7에 예시된 실시예에 있어서, 트래킹 회로(162)는 전력 입력(156)에만 공급되는 전력을 완화한다. 트래킹 회로(162)는 전력 입력들(154, 156)에 공급되는 전력이 연산 회로(152)에 의해 부과되는 제약들을 따르는 것을 보증하는 기능을 한다. 예를 들어, 이에 제한되지 않지만, 제약들은 이하의 예들을 포함할 수 있다.

V1 > V2

V1 < 미리 정의된 최대 전압

V2 < 미리 정의된 최대 전압

V1-V2 < X, 여기서 X는 미리 정의된 양

여기서 V1은 제 1 전력 입력(154)에서의 전압이고 V2는 제 2 전력 입력(156)에서의 전압이다.

2개보다 많은 전력 입력들의 경우에, 이에 제한되지 않지만 이하의 3개의 전압 예들을 포함하는, 3개 이상의 상이한 전압들을 관련시키는 유사한 제약들이 존재할 수 있다:

V1 > V2 > V3

V1 < V2 < V3

V1-V3 < Y 및 V1-V2 < X, 여기서 X 및 Y는 미리 정의된 양들이다.

본 발명의 실시예들은 이전 예들에 제한되지 않고, 본 발명의 실시예들에 의해 수용될 수 있는 다른 제약들이 포함 또는 사용될 수도 있다. 시스템 상에 부과되는 제약들의 수는 시스템에 의해 사용되는 전원들(또는 다중 전압 전원들에 의해 공급되는 이산 전압들)의 수에 기초하여 적어도 일부 범위까지 증가할 수 있다.

도 7에 예시된 시스템은 연산 회로(152)의 단일 전력 입력(156)에 공급되는 전력을 완화하는 구성을 도시하는 한편, 도 8은 연산 회로(152)의 전력 입력들(154, 156) 모두에 공급되는 전력을 완화하는 대안적인 구성을 도시한다. 예를 들어, 도 7에 예시된 전자 시스템(150)은 제 1 전력 입력(154)에 직접 연결되는 제 1 전원(158)을 포함하는 한편, 도 8에 예시된 전자 시스템(150)은 제 1 전원(158)이 트래킹 회로(162)를 통해서만 제 1 전력 입력(154)에 연결되는 것을 도시한다. 제 1 전원(158)은 양 경우들에서 입력 전력을 트래킹 회로(162)에 공급하지만, 도 8에서 트래킹 회로(162)는 임의의 제약들이 위반될 때 제 1 전원(158)으로부터 제 1 전력 입력(154)으로 전력의 전달을 방지할 수 있다. 도 9 및 도 10은 이 실시예들 각각에 사용될 수 있는 트래킹 회로들을 예시한다.

도 9를 참조하면, 형태 V1 > V2 및 V1 -V2 < X의 제약들이 유지되는 것을 보증하는 트래킹 회로의 일례가 예시된다. 전체적으로 170으로 나타낸 트래킹 회로는 기준 전압원(172), 비교기(174), 및 스위치(176)를 포함한다. 기준 전압원은 비교기(174)의 제 1 입력(180)에 제공되는 기준 전압(178)을 제공한다. 기준 전압원(172)은 예를 들어, 저항 분압기 네트워크(resistor divider network), 전압 기준 디바이스, 역방향 바이어스 제너 다이오드(reverse biased zener diode), 또는 미리 결정된 전압을 발생시킬 수 있는 유사한 디바이스이다. 미리 결정된 전압은 X 미만의 어떤 값에 설정된다. 비교기(174)의 제 2 입력(182)에 트래킹 회로(170)의 입력인 제 1 전원(190)이 결합된다. 예를 들어, 제 1 전원(190)은 도 7의 제 1 전원(158) 및 제 1 전력 입력(154)이거나 이들에 결합된다.

비교기(174)는 입력들(180, 182)에서의 상대 전압의 함수로서 제 1 상태 및 제 2 상태 사이를 스위칭하는 출력(184)을 제공한다. 예를 들어, 제 2 입력(182)(예를 들어 제 1 전원(190)으로부터)이 제 1 입력(180)에서의 기준 전압(178)보다 높을 때, 비교기 출력(184)은 저출력으로부터 고출력으로 스위칭된다. 예를 들어, 연산 증폭기, 비교기 칩들 등을 포함하는 다양한 유형들의 비교기들이 사용될 수 있다.

비교기 출력(184)은 스위치(176)를 제어하고, 따라서 제 2 전원(192)이 전력 출력(194)에 연결될 때 제어한다. 제 2 전원(192)은 트래킹 회로(170)의 입력이다. 예를 들어, 제 2 전원(192)은 도 7의 제 2 전원(158)이거나 이에 연결된다. 전력 출력(194)은 트래킹 회로(170)로부터의 출력이고, 예를 들어, 도 7의 연산 회로(152)의 제 2 전력 입력(156)에 연결된다. 예를 들어, 바이폴라 트랜지스터(bipolar transistor), 전계 효과 트랜지스터(field effect transistor)(예를 들어, MOSFET), 릴레이(relay) 등을 포함하는 다양한 유형들의 스위치들이 사용될 수 있다.

대표적인 동작은 이하와 같을 수 있다. 파워 업 동안, 제 1 전원(190) 및 제 2 전원(194)은 둘 다 램프 업되는 것으로 기대될 수 있다. 초기에, 스위치(176)는 비교기(174)에 의해 개방 유지될 수 있다. 그러므로, 전력 출력(194)은 제 2 전원(192)으로부터 분리될 수 있다. 이것은 전력 출력(194)(예를 들어, 제 2 전력 입력(156)) 전압이 제 1 전원(190)(예를 들어, 제 1 전력 입력(154))의 전압 미만으로 유지되어, 연산 회로(152)의 제약들을 만족하는 것을 보증할 수 있다. 제 1 전원(190)dl 미리 정의된 값(X) 이상의 전압까지 램프 업되면, 비교기(174)는 스위치(176)를 폐쇄하는 상태를 스위칭할 수 있다. 이것은 전력 출력(194)을 제 2 전원(192)에 연결할 수 있다. 전력 출력(194)(예를 들어, 제 2 전력 입력(156))은 램프 업하기 시작할 수도 있으므로, 전력 출력(194)(예를 들어, 제 2 전력 입력(156))의 전압이 제 1 전원(190)의 전압 미만의 X 볼트보다 크지 않아야 하는 것을 보증한다.

파워 다운 동안, 프로세스는 역으로 동작할 수 있다. 전원들이 램프 다운하기 시작하므로, 제 1 전원(190)이 미리 정의된 값 미만으로 강하할 때, 비교기(174)는 전력 출력(194)(예를 들어, 제 2 전력 입력(156))을 제 2 전원(192)(예를 들어, 제 2 전원(160))으로부터 분리하는 상태를 스위칭할 수 있다.

동작 동안 제 1 전원(158)이 고장나면, 이 회로는 적절히 동작할 수도 있는 것에 주목한다. 그러한 경우에, 비교기(174)는 전력 출력(194)을 제 2 전원(192)으로부터 분리하는 스위치(176)를 개방할 수 있다. 따라서, 트래킹 회로(170)는 제 2 전력 입력(156)이 제 1 전력 입력(154)과 트랙 업 또는 다운되게 하는 효과를 가질 수 있다.

도 9는 도 7에 예시된 연산 회로(152)에 단일 전력 입력의 관리를 제공하는 시스템에 관하여 트래킹 회로(170)를 예시하는 한편, 도 10은 도 8에 예시된 바와 같이, 연산 회로에 다중 전력 입력들의 관리 및 그 사이의 관계들을 제공하는 대안적인 실시예를 예시한다. 이 실시예에 있어서, 제 1 전원(190)(예를 들어 제 1 전원(158))은 연산 회로(152)에 직접 결합되지 않는다. 그 대신에, 제 1 전원(190)과 연산 회로(152)(예를 들어 제 1 전력 입력(154)) 사이의 연결은 트래킹 회로(170)에 의해 완화된다. 이것은 제 1 전력 입력(154)과 제 2 전력 입력(156) 사이의 최대 차이에 관한 제약이 제 2 전원(192)의 고장 시에 위반되지 않는 것을 보증하도록, 제 2 전원(192)의 고장 시 제 1 전원(190)이 제 1 전력 입력(154)으로부터 분리되어야 하는 경우에 트래킹 회로(170)가 응답하는 것을 가능하게 한다.

그러므로, 도 10에 예시된 바와 같이, 전력 출력(194)은 트래킹 회로(170)의 제 2 전력 출력(예를 들어 제 2 전력 입력(156)에 연결된 전력 출력)으로 간주될 수 있고, 제 1 전력 출력(196)(제 1 전력 입력(154)에 연결됨)이 제공된다. 전력 출력(194)은 상술한 바와 같이 스위치(176)에 더 연결되고, 그의 동일한 기능을 유지한다. 그러나, 제 2 스위치(186)는 제 1 전력 출력(196)에서 전력을 완화하기 위해 제 1 전원(190)과 제 1 전력 출력(196) 사이에 개재되어 있다. 스위치(186)는 이 경우에 제 2 전원(192)에 의해 직접 제어될 수 있어서, 제 2 전원(192)의 고장 시, 스위치(186)는 제 1 전원(190)을 제 1 전력 출력(196)으로부터 분리한다. 물론, 도 10에 도시된 구성은 2개의 전원들의 연결을 통한 제어를 2개의 입력들에 제공하는 단지 하나의 방법이고, 본 발명의 실시예들과 관련된 개념들을 단지 예시하는 것으로 간주되어야 한다.

도 11은 트래킹 회로의 실시예의 일례 구현의 전기 구성요소 개략도를 제공한다. 트래킹 회로는 3.3 V 전원에 기초하여 1.8 V 전원의 트래킹을 제공한다. 트래킹 회로는 개별 5 V 전원으로부터 동작된다.

R533 및 R83으로 구성되는 저항 전압 분압기는 비교기(U9A)의 입력 핀(2)에서 기준 전압을 제공한다. 이 예를 들어, 전압 분압기에 전력 공급하기 위해 5V 전원(5P0V_S5)을 사용하면 1.94V의 기준 전압이 된다. 전압 분압기는 다른 능력을 제공하고 따라서 상이한 제약들을 실시하는, 예를 들어, 3.3V 또는 1.8V 공급을 포함하는 다른 소스들로부터 전원 공급될 수 있다.

3.3V 입력은 양의 피드백 저항기(positive feedback resistor)(R536)와 조합하여, 소량의 히스테리시스(hysteresis)를 비교기(U9A)에 제공하는, 비교기의 입력 핀(3)에 저항기(R85)를 통해서 제공된다. 따라서, 전력이 램프 업되고, 3.3V 공급이 1.96376 볼트를 초과할 때, 비교기(U9A)는 1.8v 전원 인에이블 신호(1P8V_S0_ENABLE)를 어서트(assert)할 수 있다(로직 하이(high), 또는 대략 5 볼트). 반대로, 전력이 램프 다운되고, 3.3V 공급이 1.89745 볼트 미만으로 강하할 때, 비교기는 1.8V 전원 인에이블 신호를 디어서트(de-assert)할 수 있다(로직 로우(low) 또는 대략 0V). 따라서, 비교는 램프 업 동안 스위칭을 제어하는 제 1 미리 정의된 전압 및 램프 다운 동안 스위칭을 제어하는 제 2 미리 정의된 전압을 사용하는, 2개의 상이한 미리 정의된 전압들에 대한 것이다. 따라서, 이 예는 트래킹 회로가 상대 전압들에 관한 제약을 충족할 시에 추가적인 마진(margin)을 제공하거나, 대안적으로 파워 업 및 파워 다운 동안 적용하는 상이한 제약들을 실시할 수 있는 방법을 예시한다.

MOSFET(Q24)는 스위칭 기능을 제공하고, 비교기 출력(1P8V_S0_ENABLE)에 의해 제어된다. 스위칭 온될 때, MOSFET는 1.8V 출력(1P8V_S0)이 1.8V 전원(1P8V_S3)으로부터 공급되는 것을 가능하게 한다.