KR20130076791A - 탄화규소 반도체 장치의 제조 방법 및 탄화규소 반도체 장치의 제조 장치 - Google Patents

탄화규소 반도체 장치의 제조 방법 및 탄화규소 반도체 장치의 제조 장치 Download PDFInfo

- Publication number

- KR20130076791A KR20130076791A KR1020127012240A KR20127012240A KR20130076791A KR 20130076791 A KR20130076791 A KR 20130076791A KR 1020127012240 A KR1020127012240 A KR 1020127012240A KR 20127012240 A KR20127012240 A KR 20127012240A KR 20130076791 A KR20130076791 A KR 20130076791A

- Authority

- KR

- South Korea

- Prior art keywords

- semiconductor device

- forming

- silicon carbide

- oxide film

- sic semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02167—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon carbide not containing oxygen, e.g. SiC, SiC:H or silicon carbonitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02057—Cleaning during device manufacture

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/02227—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process

- H01L21/0223—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate

- H01L21/02233—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer

- H01L21/02236—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a process other than a deposition process formation by oxidation, e.g. oxidation of the substrate of the semiconductor substrate or a semiconductor layer group IV semiconductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02299—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment

- H01L21/02301—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment in-situ cleaning

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/0445—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising crystalline silicon carbide

- H01L21/0455—Making n or p doped regions or layers, e.g. using diffusion

- H01L21/046—Making n or p doped regions or layers, e.g. using diffusion using ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/0445—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising crystalline silicon carbide

- H01L21/048—Making electrodes

- H01L21/049—Conductor-insulator-semiconductor electrodes, e.g. MIS contacts

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/01—Manufacture or treatment

- H10D12/031—Manufacture or treatment of IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/83—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge

- H10D62/832—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge being Group IV materials comprising two or more elements, e.g. SiGe

- H10D62/8325—Silicon carbide

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Plasma & Fusion (AREA)

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Recrystallisation Techniques (AREA)

Abstract

SiC 반도체 장치(200)를 제조하는 방법은, 적어도 일부에 불순물이 주입된 제1 표면(100a)을 포함하는 탄화규소 반도체(100)를 준비하는 공정과, 탄화규소 반도체(100)의 제1 표면(100a)을, 수소 가스를 포함하는 가스를 이용하여 드라이 에칭함으로써, 제2 표면(100b)을 형성하는 공정과, 제2 표면(100b) 상에, SiC 반도체 장치(200)를 구성하는 산화막(126)을 형성하는 공정을 포함한다.

Description

본 발명은, 탄화규소(SiC) 반도체 장치의 제조 방법 및 SiC 반도체 장치의 제조 장치에 관한 것으로, 보다 특정적으로는 산화막을 갖는 SiC 반도체 장치의 제조 방법 및 이 제조 방법에 이용되는 제조 장치에 관한 것이다.

종래부터, 반도체 장치를 구성하는 재료로서 규소(Si)가 널리 채택되고 있다. Si 반도체 디바이스, 예를 들어, MOSFET(Metal Oxide Semiconductor Field Effect Transistor : 전계 효과 트랜지스터)는, 이하와 같이 하여 제조할 수 있다.

즉, 우선, 실리콘(Si) 기판 상에 에피택셜층을 형성하여 Si 반도체를 제작한다. 다음으로, Si 반도체에 불순물(도펀트)을 도입할 목적으로 이온 주입 공정을 행하고, 이어서, 도입된 불순물을 활성화시킬 목적으로, 상기 Si 반도체를 가열 처리(활성화 어닐링 처리)한다. 그리고, 가열 처리 후의 Si 반도체의 표면에 게이트 산화막을 형성하고, 그 위에 전극을 형성한다.

상기와 같은 종래의 Si 반도체 장치의 제조에서는, Si 기판의 표면에 부착되어 있는 파티클이나 금속 불순물 등의 불순물과 같은 부착물을 제거하기 위한 세정이 행해지고 있다. 이러한 세정 방법으로서, RCA 세정과 같은 약액을 이용한 세정 방법이 널리 채택되고 있다.

RCA 세정에서는, 우선, Si 기판의 표면을 황산 및 과산화수소를 포함하는 약액으로 세정함으로써 Si 기판의 표면에 Si 산화막을 형성한다. 이 Si 산화막의 내부나 표면에는 파티클 및 금속 불순물이 도입된다. 다음으로, 이 Si 기판을 희불산 수용액으로 세정하여, Si 산화막을 에칭 제거하고 파티클 및 금속 불순물을 제거한다.

또한, 다른 세정 방법으로서, 예를 들어, 일본 특허 공개 평6-314679호 공보(특허문헌 1), 일본 특허 공개 평4-354334호 공보(특허문헌 2)에는, 오존수를 이용하여 Si 기판의 표면을 산화하고, 그 후 산화막을 제거함으로써 Si 기판 상의 파티클 및 금속 불순물을 제거하는 방법이 개발되어 있다.

SiC는, 밴드갭이 크고, 또 최대 절연 파괴 전계 및 열전도율이 Si와 비교하여 큰 한편, 캐리어의 이동도가 Si와 동일한 정도로 크고, 전자의 포화 드리프트 속도 및 내압도 크다. 이 때문에, 고효율화, 고내압화 및 대용량화가 요구되는 반도체 장치에 대한 적용이 기대된다. 이와 관련하여, 본 발명자는 SiC 반도체를 반도체 장치에 이용하는 것에 착안했다. 그리고, 본 발명자는, 보다 품질이 높은 SiC 반도체 장치를 제조하기 위해, SiC 반도체에서, SiC 반도체 장치를 구성하는 산화막을 형성하기 위한 표면을 청정화하는 것에 착상했다.

그러나, 상기 종래의 세정 방법을 SiC 반도체에 적용하면, SiC가 Si보다 열적으로 안정된 화합물이기 때문에, SiC 반도체의 표면이 산화되기 어려운 것을 본 발명자가 처음으로 밝혔다. 즉, 상기 세정 방법은, Si의 표면을 산화할 수는 있지만, SiC의 표면을 충분히 산화할 수는 없다. 이 때문에, SiC의 표면으로부터 파티클이나 불순물을 제거할 수 없게 되어, SiC 표면을 충분히 청정화할 수 없다. SiC 반도체의 표면이 청정화되지 않으면, 청정화된 SiC 반도체 상에 산화막을 형성할 수 없기 때문에, 결과적으로, 제조되는 SiC 반도체 장치의 품질이 저하되어 버린다.

따라서, 본 발명의 목적은, 고품질의 SiC 반도체 장치를 제조하는 방법 및 이 방법에 이용되는 제조 장치를 제공하는 것이다.

고품질의 SiC 반도체 장치를 제조하기 위해, SiC 반도체의 표면을 청정화하는 것에 착안하여 예의 연구한 바, 본 발명의 완성에 이르렀다. 즉, 본 발명은, SiC 반도체 장치를 제조하는 방법으로서, 적어도 일부에 불순물(도펀트)이 주입된 제1 표면을 포함하는 SiC 반도체를 준비하는 공정과, SiC 반도체의 제1 표면을, 수소 가스를 포함하는 가스를 이용하여 드라이 에칭함으로써 제2 표면을 형성하는 공정과, 제2 표면 상에 SiC 반도체 장치를 구성하는 산화막을 형성하는 공정을 포함하는 SiC 반도체 장치의 제조 방법이다.

본 발명의 SiC 반도체 장치의 제조 방법에 의하면, SiC 반도체의 적어도 일부에 불순물이 주입된 제1 표면을, 수소 가스를 포함하는 가스를 이용하여 드라이 에칭(이하, 「수소 에칭」이라고도 함)한다. 이에 따라, 제1 표면에 부착되어 있던 불순물, 파티클 등을 제거할 수 있어, 청정화된 제2 표면을 형성할 수 있다. 그리고, 이 청정화된 제2 표면 상에 SiC 반도체 장치를 구성하는 산화막을 형성함으로써, 고품질의 SiC 반도체 장치를 제조할 수 있다. 또, SiC 반도체는 안정된 화합물이기 때문에, 수소 에칭을 행하더라도 SiC 반도체에 미치는 손상이 적다. 따라서, 표면 특성이 양호해지도록 SiC 반도체를 청정화할 수 있다. 따라서, 고품질의 SiC 반도체 장치를 제조할 수 있다.

상기 SiC 반도체 장치의 제조 방법에서 바람직하게는, 제2 표면을 형성하는 공정 후에, 액상을 이용한 세정을 하지 않고, 산화막을 형성하는 공정을 실시한다.

이에 따라, 액상을 이용한 세정에 기인하는 불순물의 부착을 방지할 수 있다. 따라서, 보다 고품질의 SiC 반도체 장치를 제조할 수 있다.

상기 SiC 반도체 장치의 제조 방법에서 바람직하게는, 제2 표면을 형성하는 공정에서 수소 에칭을 1300℃ 이상 1650℃ 이하의 온도 범위에서 행한다.

수소 에칭을 1300℃ 이상의 온도에서 행함으로써 에칭률을 높일 수 있고, 1650℃ 이하의 온도에서 행함으로써 에칭률이 지나치게 높아지는 것을 억제할 수 있기 때문에, 용이하게 제어할 수 있다. 즉, 수소 에칭을 상기 온도 범위 내에서 행함으로써 바람직한 에칭률로 제어할 수 있기 때문에, 정밀도를 높여 제1 표면을 에칭할 수 있으므로, SiC 반도체 장치의 품질을 보다 높일 수 있다.

상기 SiC 반도체 장치의 제조 방법에서 바람직하게는, 산화막을 형성하는 공정에서는, 제2 표면 상에 규소(Si)를 포함하는 막을 형성하고, 상기 Si를 포함하는 막을 산화함으로써 산화막을 형성한다.

본 발명자는, SiC 반도체의 적어도 일부에 불순물(도펀트)이 주입된 제2 표면에서는, 불순물(도펀트) 농도 및 불순물(도펀트)의 종류가 상이하기 때문에 깊이 방향의 산화율에 변동이 생기고, 결과적으로 불균일한 산화막이 형성되는 것에 착안하여, 상기 발명을 완성했다. Si를 포함하는 막이 제2 표면 상에 형성되기 때문에, Si를 포함하는 막의 품질에 대한 제2 표면 상태의 영향을 저감할 수 있다. 이 때문에, Si를 포함하는 막의 품질의 균일화를 도모할 수 있다. 따라서, SiC 반도체 장치의 품질을 더욱 높일 수 있다.

상기 SiC 반도체 장치의 제조 방법에서 바람직하게는, 제2 표면을 형성하는 공정에서, 가스는 염화수소 가스를 더 포함한다.

SiC 반도체의 제1 표면을 수소 에칭할 때, 수소 가스와 함께 염화수소 가스를 이용함으로써 SiC 반도체의 에칭률을 크게 할 수 있다. 따라서, SiC 반도체 장치의 제조 택트를 짧게 할 수 있다.

상기 SiC 반도체 장치의 제조 방법에서 바람직하게는, 제2 표면을 형성하는 공정에서, 가스는 탄화수소 가스를 더 포함한다.

SiC 반도체의 제1 표면을 수소 에칭할 때, 수소 가스와 함께 탄화수소 가스를 이용함으로써, SiC 반도체의 표면 모폴로지를 양호하게 할 수 있다. 따라서, SiC 반도체 장치의 품질을 보다 높일 수 있다.

상기 SiC 반도체 장치의 제조 방법에서 바람직하게는, 제2 표면을 형성하는 공정과 산화막을 형성하는 공정 사이에서, SiC 반도체는 대기 차단된 분위기 내에 배치된다.

이에 따라, 청정한 제2 표면이 형성된 SiC 반도체를, 대기에 노출시키지 않고, 다음 공정인 SiC 반도체 장치를 구성하는 산화막을 형성하는 공정에 제공할 수 있다. 이 때문에, 청정화된 SiC 반도체의 표면이 대기에 의해 오염되는 것을 방지할 수 있어, SiC 반도체 장치의 품질을 더욱 높일 수 있다.

또, 본 발명은, SiC 반도체에서, 적어도 일부에 불순물(도펀트)이 주입된 제1 표면을 수소 가스를 포함하는 가스를 이용한 드라이 에칭에 의해 제거하기 위한 제거부와, SiC 반도체에서 제1 표면이 제거됨으로써 형성된 제2 표면에 SiC 반도체 장치를 구성하는 산화막을 형성하기 위한 형성부와, SiC 반도체를 반송할 수 있게 제거부와 형성부를 접속하는 접속부를 포함하고, 접속부에서의 SiC 반도체를 반송시키는 영역은 대기의 차단이 가능한 SiC 반도체 장치의 제조 장치이다.

이 제조 장치에 의하면, SiC 반도체에서, 적어도 일부에 불순물이 주입된 제1 표면을 제거부로 수소 에칭할 수 있다. 그리고, 제거부로 수소 에칭된 후의 SiC 반도체를, 대기로부터 차단된 분위기하의 접속부를 통해 형성부로 반송할 수 있다. 또한, 형성부에서, 제2 표면에 SiC 반도체 장치를 구성하는 산화막을 형성할 수 있다. 즉, 수소 에칭에 의해 SiC 반도체를 청정화하는 공정으로부터 산화막을 형성하는 공정까지의 일련의 공정을 대기로부터 차단된 상태에서 행할 수 있다. 따라서, 이 제조 장치에 의하면 고품질의 SiC 반도체 장치를 제조할 수 있다.

이상 설명한 바와 같이, 본 발명의 SiC 반도체 장치의 제조 방법 및 이것에 이용하는 제조 장치에 의하면, SiC 반도체가 청정화를 발현할 수 있는 SiC 반도체의 세정 방법을 이용하여, 고품질의 SiC 반도체 장치를 제조할 수 있다.

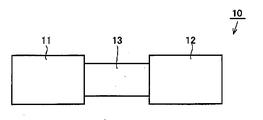

도 1은 본 발명의 실시형태 1에서의 SiC 반도체 장치의 제조 장치의 모식도이다.

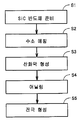

도 2는 본 발명의 실시형태 1에서의 SiC 반도체 장치의 제조 방법을 나타내는 플로우차트이다.

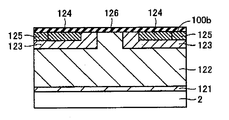

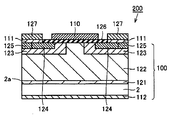

도 3은 본 발명의 실시형태 1에서 준비하는 SiC 반도체를 개략적으로 나타내는 단면도이다.

도 4는 본 발명의 실시형태 1에서 준비하는 SiC 반도체의 제작 공정을 설명하기 위한 도면이다.

도 5는 본 발명의 실시형태 1에서 산화막이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이다.

도 6은 본 발명의 실시형태 1에서 소스 컨택트 전극 및 드레인 전극이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이다.

도 7은 본 발명의 실시형태 1에서 제조되는 SiC 반도체 장치를 개략적으로 나타내는 단면도이다.

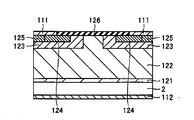

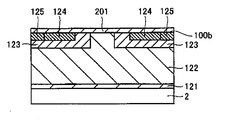

도 8은 본 발명의 실시형태 2에서 SiC 반도체의 주면(主面) 상에 반도체막이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이다.

도 9는 실시예 1, 비교예 1 및 비교예 2에서 이용하는 에피택셜 웨이퍼를 개략적으로 나타내는 단면도이다.

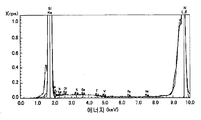

도 10은 비교예 1의 SiC 반도체의 표면을 TXRF로 측정한 결과를 나타내는 스펙트럼이다.

도 11은 비교예 2의 SiC 반도체의 표면을 TXRF로 측정한 결과를 나타내는 스펙트럼이다.

도 2는 본 발명의 실시형태 1에서의 SiC 반도체 장치의 제조 방법을 나타내는 플로우차트이다.

도 3은 본 발명의 실시형태 1에서 준비하는 SiC 반도체를 개략적으로 나타내는 단면도이다.

도 4는 본 발명의 실시형태 1에서 준비하는 SiC 반도체의 제작 공정을 설명하기 위한 도면이다.

도 5는 본 발명의 실시형태 1에서 산화막이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이다.

도 6은 본 발명의 실시형태 1에서 소스 컨택트 전극 및 드레인 전극이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이다.

도 7은 본 발명의 실시형태 1에서 제조되는 SiC 반도체 장치를 개략적으로 나타내는 단면도이다.

도 8은 본 발명의 실시형태 2에서 SiC 반도체의 주면(主面) 상에 반도체막이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이다.

도 9는 실시예 1, 비교예 1 및 비교예 2에서 이용하는 에피택셜 웨이퍼를 개략적으로 나타내는 단면도이다.

도 10은 비교예 1의 SiC 반도체의 표면을 TXRF로 측정한 결과를 나타내는 스펙트럼이다.

도 11은 비교예 2의 SiC 반도체의 표면을 TXRF로 측정한 결과를 나타내는 스펙트럼이다.

이하, 도면에 기초하여 본 발명의 실시형태를 설명한다. 이하의 도면에서 동일하거나 해당하는 부분에는 동일한 참조 부호를 붙이고, 그 설명은 반복하지 않는다.

(실시형태 1)

도 1은, 본 발명의 실시형태 1에서의 SiC 반도체 장치의 제조 장치의 모식도이다. 도 1을 참조하여, 본 발명의 일실시형태에서의 SiC 반도체 장치의 제조 장치를 설명한다.

도 1에 나타낸 바와 같이, SiC 반도체 장치의 제조 장치(10)는, 제거부(11)와, 형성부(12)와, 접속부(13)를 포함하고 있다. 제거부(11)와 형성부(12)는 접속부(13)에 의해 접속되어 있다. 제거부(11), 형성부(12) 및 접속부(13)의 내부는 대기로부터 차단되어 있고, 내부는 서로 연통 가능하다.

제거부(11)는, SiC 반도체에서의 적어도 일부에 불순물이 주입된 제1 표면을 수소 에칭함으로써 제2 표면을 형성한다. 제거부(11)에는 수소 에칭 장치가 이용된다. 제거부(11)에서 이용하는 수소 에칭 장치는 특별히 한정되지 않고, 예를 들어 고주파 가열로 등을 이용할 수 있다.

형성부(12)는, 제2 표면 상에 SiC 반도체 장치를 구성하는 산화막을 형성한다. 형성부(12)에는 산화막 형성 장치가 이용된다. 형성부(12)에서 이용하는 산화막 형성 장치는 특별히 한정되지 않고, 예를 들어, 드라이 산화(열산화) 장치, 스퍼터 장치 및 CVD(Chemical Vapor Deposition : 화학 증착) 장치, 수증기를 포함하는 산소 분위기 중에서 가열하는 웨트 산화 장치, 파이로제닉 산화 장치를 이용할 수 있고, 드라이 산화 장치를 이용하는 것이 바람직하다.

접속부(13)는, SiC 반도체를 반송할 수 있게 제거부(11)와 형성부(12)를 접속한다. 접속부(13)에서 에피택셜 웨이퍼를 반송시키는 영역(내부 공간)은 대기의 차단이 가능하다.

여기서, 대기의 차단(대기를 차단한 분위기)이란, 대기가 혼입되지 않는 분위기를 의미하며, 예를 들어 질소 가스, 수소 가스 및 불활성 가스 중 1종류 이상의 가스를 포함하는 분위기 또는 진공이다. 구체적으로는, 대기를 차단한 분위기는, 예를 들어 질소(N), 수소(H), 헬륨(He), 네온(Ne), 아르곤(Ar), 크립톤(Kr), 크세논(Xe), 라돈(Rn) 또는 이들의 조합을 포함하는 가스가 충전된 분위기 또는 진공이다.

접속부(13)는, 제거부(11)의 내부와 형성부(12)의 내부를 연통시킨다. 접속부(13)는, 제거부(11)로부터 반출되는 SiC 반도체를 형성부(12)로 반송하기 위한 공간을 내부에 갖는다. 즉, 접속부(13)는, SiC 반도체를 대기에 개방하지 않도록, 제거부(11)로부터 형성부(12)로 반송하기 위해 설치되어 있다.

접속부(13)는, 내부에서 SiC 반도체를 반송할 수 있는 크기를 갖는다. 또 접속부(13)는, SiC 반도체를 서셉터에 배치한 상태로 반송할 수 있는 크기를 가질 수도 있다. 접속부(13)는, 예를 들어 제거부(11)의 출구와 형성부(12)의 입구를 연결하는 로드록실이다.

또, 제조 장치(10)는, 접속부(13)의 내부에 배치되고, SiC 반도체를 제거부(11)로부터 형성부(12)로 반송하기 위한 제1 반송부를 더 포함하고 있어도 좋다. 제조 장치(10)는, 형성부(12)에서 게이트 산화막(126)이 형성된 SiC 반도체를, 제조 장치(10)의 외부로 반출하거나, 또는 전극을 형성하는 전극 형성부로 대기를 차단한 분위기에서 반송하기 위한 제2 반송부를 더 포함하고 있어도 좋다. 제1 반송부와 제2 반송부는 동일할 수도 있고 상이할 수도 있다.

또, 제조 장치(10)는, 제거부(11)와 접속부(13) 사이에 배치되고 제거부(11)의 내부와 접속부(13)의 내부를 차단하기 위한 차단부를 더 포함하고 있어도 좋다. 또, 제조 장치(10)는, 형성부(12)와 접속부(13) 사이에 배치되고 형성부(12)의 내부와 접속부(13)의 내부를 차단하기 위한 차단부를 더 포함하고 있어도 좋다. 차단부는, 예를 들어 각각의 연통부를 막는 것이 가능한 밸브나 도어 등을 이용할 수 있다.

또, 제조 장치(10)는, 내부의 분위기 가스를 배출하기 위한 진공 펌프나, 내부의 분위기 가스를 치환하기 위한 치환 가스 봄베를 더 포함하고 있어도 좋다. 진공 펌프나 치환 가스 봄베는, 제거부(11), 형성부(12) 및 접속부(13)의 각각에 접속되어 있어도 좋고, 어느 하나 이상에 접속되어 있어도 좋다.

제조 장치(10)는, 상기 이외의 여러 요소, 예를 들어 산화막 상에 전극을 형성하기 위한 전극 형성부를 포함하고 있어도 좋지만, 설명의 편의상 이들 요소의 도시 및 설명은 생략한다.

또, 도 1에서는, 접속부(13)로서 제거부(11)와 형성부(12) 사이만을 연결하는 형상을 나타냈지만, 특별히 이것에 한정되지 않는다. 예를 들어 접속부(13)로서, 예를 들어 대기를 차단한 챔버를 이용하고, 이 챔버 내에 제거부(11) 및 형성부(12)가 배치되어 있어도 좋다.

계속해서, 도 1∼도 7을 참조하여 본 실시형태에서의 SiC 반도체 장치의 제조 방법에 관해 설명한다. 도 2는, 본 발명의 실시형태 1에서의 SiC 반도체 장치의 제조 방법을 나타내는 플로우차트이다. 도 3∼도 6은, 본 발명의 실시형태 1에서의 SiC 반도체 장치의 제조 방법의 각 공정에서 형성되는 SiC 반도체의 구성을 나타낸 도면이다. 구체적으로는, 도 3은, 준비하는 SiC 반도체를 개략적으로 나타내는 단면도이고, 도 4는, 준비하는 SiC 반도체의 제작 공정을 설명하기 위한 도면이다. 도 5는, 산화막이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이고, 도 6은, 소스 컨택트 전극 및 드레인 전극이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이다. 그리고, 도 7은, 본 발명의 실시형태 1에서 제조되는 SiC 반도체 장치를 개략적으로 나타내는 단면도이다. 본 실시형태에서는, SiC 반도체로서, 도 7에 나타내는 SiC 반도체 장치(200)를 제조하는 방법을 설명한다. 또, 본 실시형태에서는, 도 1에 나타내는 SiC 반도체 장치의 제조 장치(10)를 이용한다.

도 2 및 도 3에 나타낸 바와 같이, 우선, 적어도 일부에 불순물이 주입된 제1 표면(100a)을 포함하는 SiC 반도체로서의 에피택셜 웨이퍼(100)를 준비한다(단계 S1). 본 공정에서는, SiC 반도체로서, 도 2에 나타낸 바와 같이, SiC 기판(2)의 표면(2a) 상에, 불순물이 주입된 영역을 갖는 에피택셜층(120)이 형성된 에피택셜 웨이퍼(100)를 준비한다. 상기 SiC 기판(2)은 특별히 한정되지 않지만, 예를 들어 이하의 방법에 의해 준비할 수 있다.

구체적으로는, 예를 들어, 승화법, CVD법 등의 기상 성장법, 액상 성장법 등에 의해 성장된 SiC 잉곳을 준비한다. 그 후, SiC 잉곳으로부터 표면을 갖는 SiC 기판을 잘라낸다. 잘라내는 방법은 특별히 한정되지 않고, SiC 잉곳으로부터 슬라이스 등에 의해 SiC 기판을 잘라낸다.

이어서, 잘라낸 SiC 기판의 표면을 연마한다. 연마하는 면은, 표면만이어도 좋고, 표면과 반대측의 이면을 더 연마해도 좋다. 연마하는 방법은 특별히 한정되지 않지만, 표면을 평탄하게 하고, 상처 등의 손상을 저감하기 위해, 예를 들어 CMP(Chemical Mechanical Polishing : 화학 기계 연마)를 행한다. CMP에서는, 연마제로서 콜로이달실리카, 고정제로서 접착제, 왁스 등을 이용한다. CMP와 더불어, 혹은 연마에 대신해서, 전계 연마법, 화학 연마법, 기계 연마법 등의 다른 연마를 더 행해도 좋다. 또 연마를 생략해도 좋다. 이상의 조작에 의해, 표면(2a)을 갖는 SiC 기판(2)을 준비할 수 있다. 이러한 SiC 기판(2)으로서, 예를 들어 도전형이 n형이고, 저항이 0.02 Ωcm인 기판을 이용한다.

또, 상기 SiC 기판(2) 상의 에피택셜층(120)은, 예를 들어 이하의 방법에 의해 형성할 수 있다. 우선, 도 4에 나타낸 바와 같이, SiC 기판(2)의 표면(2a) 상에 버퍼층(121)을 형성한다. 버퍼층(121)은, 예를 들어 도전형이 n형인 SiC로 이루어지고, 예를 들어 두께가 0.5 ㎛인 에피택셜층이다. 또 버퍼층(121)에서의 n형의 도전성 불순물의 농도는, 예를 들어 5×1017 cm-3이다. 그 후, 버퍼층(121) 상에 드리프트층(122)을 형성한다. 드리프트층(122)으로서, 기상 성장법, 액상 성장법 등에 의해, 도전형이 n형인 SiC로 이루어진 층을 형성한다. 드리프트층(122)의 두께는, 예를 들어 10 ㎛이다. 또 드리프트층(122)에서의 n형의 도전성 불순물의 농도는, 예를 들어 5×1015 cm-3이다.

다음으로, 에피택셜층에 불순물을 주입한다. 본 실시형태에서는, 도 3에 나타낸 바와 같이, p 보디 영역(123)과, n 소스 영역(124)과, p+ 영역(125)을, 이하와 같이 형성한다. 우선 도전형이 p형인 불순물을 드리프트층(122)의 일부에 선택적으로 주입함으로써 보디 영역(123)을 형성한다. 그 후, n형의 도전성 불순물을 정해진 영역에 선택적으로 주입함으로써 소스 영역(124)을 형성하고, 또 도전형이 p형인 도전성 불순물을 정해진 영역에 선택적으로 주입함으로써 p+ 영역(125)을 형성한다. 도전성 불순물의 선택적인 주입은, 예를 들어 산화막으로 이루어진 마스크를 이용하여 행해진다.

상기 불순물의 주입 공정에서, 각 주입 프로파일에 대하여, 후술하는 단계 S2에서의 수소 에칭에 의해 제거되는 두께가 고려된다. 즉, 수소 에칭하는 단계 S2에서 에피택셜층의 제1 표면(100a)을 제거했을 때, p 보디 영역(123), n 소스 영역(124) 및 p+ 영역(125)을 포함하는 불순물 확산 영역이 원하는 배치가 되도록, 이온 주입을 제어한다.

이러한 주입 공정후, 활성화 어닐링 처리가 행해져도 좋다. 예를 들어, 아르곤 분위기 중, 가열 온도 1700℃에서 30분간의 어닐링이 행해진다.

이러한 공정에 의해, SiC 기판(2)과, SiC 기판(2) 상에 형성된 에피택셜층(120)을 포함하는 에피택셜 웨이퍼(100)를 준비할 수 있다.

도 2로 되돌아가, 다음으로, 준비된 에피택셜 웨이퍼(100)의 제1 표면(100a)을 수소 에칭함으로써 제2 표면(100b)(도 5 참조)을 형성한다(단계 S2). 본 실시형태의 단계 S2에서는, 도 1에 나타내는 제조 장치(10)의 제거부(11)로 제1 표면(100a)을 제거한다.

이 단계 S2를 실시하면, 에피택셜층(120)의 제1 표면(100a)이 수소 에칭되고, 이에 따라, 제1 표면(100a)에 부착되어 있는 불순물, 파티클 등을 제1 표면(100a)과 함께 제거할 수 있다. 그리고, 에피택셜 웨이퍼(100)에서, 불순물, 파티클 등이 제거됨으로써 청정한 제2 표면(100b)이 형성된다(도 5 참조).

단계 S2에서, 용이하게 제어되는 에칭량을 고려하여, 에칭 깊이(제1 표면(100a)으로부터 SiC 기판(2)을 향한 방향의 에칭량)는 0.1 ㎛ 이상이 바람직하고, 0.5 ㎛ 이상이 보다 바람직하다.

또, 불순물, 파티클 등의 제거라는 관점에서는, 에칭 깊이는 1분자층 이상 10 nm 이하인 것이 바람직하다. 이 범위의 두께로 제1 표면(100a)을 수소 에칭함으로써, 제1 표면(100a)에 부착되어 있는 불순물, 파티클 등을 확실하게 제거하여, 청정화된 제2 표면(100b)을 형성할 수 있다.

또, 전술한 주입 공정에 의해 Si 반도체의 표면 영역이 손상을 받아 거칠어지는 경우가 있지만, 예를 들어, 에칭 깊이를 10 nm보다 크고 500 nm 이하로 함으로써, 불순물, 파티클 등을 제거하고 거칠어진 표면 영역을 제거할 수 있다. 따라서, 이 범위의 두께로 제1 표면(100a)을 수소 에칭함으로써 손상층을, 불순물, 파티클 등과 함께 제거할 수 있어, 표면 특성이 양호한 제2 표면(100b)을 형성할 수 있다.

또, 수소 에칭을 1300℃ 이상의 온도에서 행함으로써 에칭률을 높일 수 있고, 1650℃ 이하의 온도에서 행함으로써 에칭률이 지나치게 높아지는 것을 억제할 수 있기 때문에, 용이하게 제어할 수 있다. 따라서, 수소 에칭의 온도 조건을 1300℃ 이상 1650℃ 이하로 조정함으로써, 바람직한 에칭률로 제어할 수 있기 때문에, 정밀도를 높여 제1 표면(100a)을 에칭할 수 있으므로, SiC 반도체 장치의 품질을 보다 높일 수 있다. 이러한 온도 설정은, 예를 들어, 에칭 장치(제거부(11)) 내에 배치된 에피택셜 웨이퍼(100)를 1300℃ 이상 1650℃ 이하로 가열하거나, 1300℃ 이상 1650℃ 이하의 에칭용 가스(이하, 「에칭 가스」라고 함)를 장치 내에 도입하거나, 또는 장치 내를 1300℃ 이상 1650℃ 이하로 유지함으로써 가능해진다. 이들을 조합해도 좋다.

또, 수소 에칭시의 수소 가스의 유량은 특별히 제한되지 않지만, 수백 slm(standard liter per minute) 정도인 것이 바람직하고, 수소 에칭시의 압력은 수십 hPa∼수백 hPa 정도인 것이 바람직하다. 이 경우, 바람직한 속도로 에칭을 행하는 것이 가능해진다.

또, 에칭 가스로서, 수소 가스와 다른 가스의 혼합 가스를 이용해도 좋다. 특히, 수소 가스에 염화수소(HCl) 가스를 혼합한 혼합 가스를 이용하는 것이 바람직하다. 이러한 혼합 가스를 이용함으로써 에칭률을 크게 할 수 있다. 혼합 가스 중의 염화수소 가스의 함유율이 지나치게 높으면, 에칭률이 지나치게 커져 에칭의 제어가 어려워지기 때문에, 혼합 가스 중의 염화수소 가스의 함유율은 10% 이하인 것이 바람직하고, 염화수소 가스와 수소 가스를 포함하는 혼합 가스 중의 염화수소 가스의 함유율(염화수소 가스/(염화수소 가스+수소 가스)×100)이 10% 이하인 것이 보다 바람직하다.

또, 수소 가스에 탄화수소 가스를 혼합한 혼합 가스를 이용해도 좋다. 이러한 혼합 가스를 이용함으로써, 에피택셜 웨이퍼(100)의 표면 모폴로지를 양호하게 하면서 에칭할 수 있어, 표면 상태가 양호한 제2 표면(100b)을 형성할 수 있다. 탄화수소로는, 알칸, 알켄 등의 저급 탄화수소를 이용할 수 있고, 예를 들어, 아세틸렌(C2H2)이나 프로판(C3H8) 등을 이용할 수 있다. 이러한 탄화수소 가스는, Si의 액적이 생기는 것을 억제하는 효과를 효과적으로 발휘하기 위해, 1000 ppm 이하로 혼합시키는 것이 바람직하다. 또, 당연히, 수소 가스, 염화수소 가스, 탄화수소 가스 각각을 혼합한 가스를 에칭 가스로 해도 좋다.

다음으로, 도 1을 참조하여, 제거부(11)에서 제2 표면(100b)이 형성된 에피택셜 웨이퍼(100)를, 형성부(12)로 반송한다. 이 때, 에피택셜 웨이퍼(100)는 대기 차단된 분위기인 접속부(13) 내에서 반송된다. 환언하면, 제2 표면(100b)을 형성하는 단계 S2와 게이트 산화막(126)을 형성하는 단계 S3 사이에서, 에피택셜 웨이퍼(100)는 대기 차단된 분위기 내에 배치된다. 이에 따라, 청정화된 제2 표면(100b)이 형성된 후에, 상기 제2 표면(100b)에 대기에 포함되는 불순물이 부착되는 것을 억제할 수 있다.

또, 도 1에 나타내는 제조 장치(10)를 이용함으로써, 제2 표면(100b)을 형성하는 공정(단계 S2) 후에, 액상을 이용한 세정을 하지 않고, 후술하는 산화막을 형성하는 단계 S3을 실시할 수 있다. 이에 따라, 액상을 이용한 세정에 기인하는 불순물(특히 중금속 이온, 알칼리 이온)의 부착을 억제할 수 있다. 액상을 이용한 세정이란, SiC 반도체로서의 에피택셜 웨이퍼(100)를 액상 중에서 세정하는 것을 의미하며, 의도하지 않은 기상 성분을 포함하고 있어도 좋다.

다음으로, 도 2 및 도 5에 나타낸 바와 같이, 제2 표면(100b) 상에 SiC 반도체 장치(200)를 구성하는 게이트 산화막(126)을 형성한다(단계 S3).

이 단계 S3에서는, 산화막을 형성하는 공지의 방법을 이용할 수 있다. 공지의 방법으로는, 예를 들어, 드라이 산화법, 스퍼터법, CVD법, 웨트 산화법, 파이로제닉 산화법 등을 들 수 있다.

단계 S3에서, 제2 표면(100b)은 청정화되어 있기 때문에 게이트 산화막(126)의 절연 특성을 향상시킬 수 있고, 에피택셜 웨이퍼(100)와 게이트 산화막(126)의 계면이나 게이트 산화막(126) 중에 존재하는 불순물, 파티클 등을 저감할 수 있다. 따라서, SiC 반도체 장치(200)의 역방향 전압 인가시의 내압을 향상시킬 수 있고, 순방향 전압 인가시의 동작의 안정성 및 장기간 신뢰성을 향상시킬 수 있다.

다음으로, 도 2에 나타낸 바와 같이, 게이트 산화막(126)을 어닐링 처리한다(단계 S4). 이 단계 S4에서는, 예를 들어, 게이트 산화막(126)에 대하여, 질화 처리와, 불활성 가스 어닐링 처리를 행할 수 있다.

질화 처리에서는, 질소를 포함하는 분위기에서 열처리한다. 질화 처리로서, 예를 들어, 일산화질소(NO) 분위기 중 또는 이질화산소(N2O) 분위기 중, 가열 온도 1200℃에서 120분간의 어닐링을 행할 수 있다. 이에 따라, 에피택셜층(120)과 게이트 산화막(126)의 계면을 포함하는 영역에, 상기 영역에 인접하는 영역에 비해 질소 농도가 높은 고질소 농도 영역(도시하지 않음)이 형성된다.

불활성 가스 어닐링 처리에서는, 불활성 가스를 포함하는 분위기에서 열처리한다. 불활성 가스 어닐링 처리로서, 예를 들어, 아르곤(Ar) 가스 등의 불활성 가스 분위기 중, 가열 온도 1100℃에서 60분간의 어닐링을 행할 수 있다.

상기 질화 처리 및 불활성 가스 어닐링 처리를 행한 경우, SiC 반도체 장치(200)에서, 높은 채널 이동도를 양호한 재현성으로 실현할 수 있는 경향이 커진다. 질화 처리 및 불활성 가스 어닐링 처리 중 어느 것만을 행해도 좋고, 본 공정(단계 S4)이 생략되어도 좋다.

다음으로, 도 2 및 도 7에 나타낸 바와 같이, 게이트 산화막(126)이 형성된 에피택셜 웨이퍼(100)에 대하여, 게이트 전극(110), 소스 전극(127) 및 드레인 전극(112)을 형성한다(단계 S5).

게이트 전극(110) 및 소스 전극(127)은, 예를 들어 이하의 방법에 의해 형성할 수 있다. 즉, 포토리소그래피법에 의해 게이트 산화막(126) 상에 패턴을 갖는 레지스트막을 형성한다. 이 레지스트막을 마스크로서 이용하여, 게이트 산화막(126)을 부분적으로 제거하고, 그 후, 공지의 방법, 예를 들어 증착법에 의해 금속으로 이루어진 도전막을 형성한다. 다음으로, 상기 레지스트막을 제거(리프트오프)함으로써, 레지스트막 상의 도전막을 제거하여 소스 컨택트 전극(111)을 형성한다(도 6 참조). 그 후, 소스 전극(127)을 공지의 방법, 예를 들어 증착법에 의해 소스 컨택트 전극(111) 상에 형성하고, 게이트 전극(110)을 공지의 방법, 예를 들어 증착법에 의해 게이트 산화막(126) 상에 형성한다. 또, 드레인 전극(112)은, SiC 기판(2)의 표면(2a)과 반대의 면에, 공지의 방법, 예를 들어 증착법에 의해 형성할 수 있다. 이상의 공정(단계 S1∼S5)을 실시함으로써, 도 7에 나타내는 SiC 반도체 장치(200)가 제조된다.

여기서, 본 실시형태에서는, 단계 S2와 단계 S3 사이에서, 웨트 세정 등 다른 세정을 하지 않는 방법을 예를 들어 설명했지만, 특별히 한정되지 않고, 웨트 세정, 드라이 세정 등의 다른 세정을 해도 좋다. 다른 세정을 하는 경우에는, 에피택셜 웨이퍼(100)를 반송할 때, 대기 차단된 분위기 내에 배치하는 것이 바람직하다.

단계 S1 후에 필요에 따라서, 약액 세정 공정, 순수 린스 공정, 건조 공정 등을 추가로 실시해도 좋다. 약액으로는, 예를 들어 황산과 과산화수소수를 포함하는 SPM을 들 수 있다. 단계 S2 전에 SPM으로 세정하는 경우에는 유기물을 제거할 수도 있다. 또, 단계 S2 전에 RCA 세정 등을 행해도 좋다.

이상 설명한 바와 같이, 본 실시형태에서의 SiC 반도체 장치의 제조 방법은, 적어도 일부에 불순물이 주입된 제1 표면(100a)을 포함하는 에피택셜 웨이퍼(100)를 준비하는 공정(단계 S1)과, 제1 표면(100a)을 수소 에칭함으로써 제2 표면(100b)을 형성하는 공정(단계 S2)과, 제2 표면(100b) 상에 SiC 반도체 장치(200)를 구성하는 게이트 산화막(126)을 형성하는 공정(단계 S3)을 포함한다.

본 발명자는, 상기 종래의 세정 방법을 에피택셜 웨이퍼(100)에 적용하면, SiC가 Si보다 안정된 화합물이기 때문에, 에피택셜 웨이퍼(100)의 표면이 산화되기 어렵고, 그 때문에, 에피택셜 웨이퍼(100)의 표면을 충분히 청정화할 수 없는 것을 처음으로 밝혔다.

그러나, 본 발명자는 에피택셜 웨이퍼(100)가 화학적으로 안정되어 있는 것에 착안하여, 에피택셜 웨이퍼(100)에 Si에서는 손상이 생기는 방법을 이용하더라도, 에피택셜 웨이퍼(100)에는 손상이 생기기 어려운 것을 발견했다. 따라서, 본 발명자는, 에피택셜 웨이퍼(100)의 표면을 청정화하는 조건을 예의 연구한 결과, 전술한 본 실시형태에서의 에피택셜 웨이퍼(100)의 제조 방법을 발견했다.

따라서, 본 실시형태에서는, 단계 S2에서 에피택셜 웨이퍼(100)의 제1 표면(100a)을 수소 에칭함으로써, 제1 표면(100a)에 부착되어 있던 불순물, 파티클 등을 제거하여, 청정화된 제2 표면(100b)을 형성할 수 있다. 또한, 단계 S3에 의해, 청정화된 제2 표면(100b) 상에 게이트 산화막(126)을 형성할 수 있으므로, 반도체 디바이스에서의 게이트 산화막(126)의 절연 특성을 향상시킬 수 있고, 에피택셜 웨이퍼(100)와 게이트 산화막(126)의 계면이나 게이트 산화막(126) 중에 존재하는 불순물, 파티클 등을 저감할 수 있다. 따라서, SiC 반도체 장치(200)의 역방향 전압 인가시의 내압을 향상시킬 수 있고, 순방향 전압 인가시의 동작의 안정성 및 장기간 신뢰성을 향상시킬 수 있다. 이와 같이, 본 실시형태에 따른 SiC 반도체 장치의 제조 방법에 의하면, 고품질의 SiC 반도체 장치(200)를 제조할 수 있다. 또한, 수소 에칭에 의한 에피택셜 웨이퍼(100)의 손상이 적기 때문에, 표면 특성이 양호한 제2 표면(100b)을 형성할 수 있다. 따라서, 결과적으로 고품질의 SiC 반도체 장치(200)를 제조할 수 있다.

또, 이온 주입 공정이나 활성화 어닐링 처리에 의해 제1 표면(100a)이 손상된 경우, 종래에는, 액상을 이용한 세정에 의해 희생 산화막의 형성 및 희생 산화막의 제거가 행해졌다. 이 액상을 이용한 세정에 의해 제1 표면(100a)에 형성된 손상층을 제거하기 위해서는, 15시간 정도의 세정 시간이 필요하였다. 이에 비해, 액상을 이용한 세정을 포함하지 않는 수소 에칭에서는, 4시간 정도로 제1 표면(100a)에 형성된 손상층을 파티클, 불순물 등과 함께 제거할 수 있다. 따라서, 본 실시형태에 따른 SiC 반도체 장치의 제조 방법에서, 단계 S2와 단계 S3 사이에 액상을 이용한 세정을 행하지 않는 것에 의해 제조 택트를 단축할 수 있다.

「제2 표면(100b)을 형성하는 공정(단계 S2) 후에, 액상을 이용한 세정을 하지 않고, 게이트 산화막(126)을 형성하는 공정(단계 S3)을 실시한다」란, 단계 S2와 단계 S3 사이에 액상을 이용한 세정 공정을 포함하지 않는 것을 의미하며, 단계 S2와 단계 S3 사이가 단속적으로 행해져도(시간이 경과해도) 좋다. 또, 단계 S2와 단계 S3을 연속하여 행해도 좋다.

또, 본 발명자는 예의 검토를 거듭한 바, 에피택셜 웨이퍼(100)를 액상을 이용하여 세정한 경우, 에피택셜 웨이퍼(100)의 세정이 불충분할 뿐만 아니라, 오히려 불순물이 부착되어 버리는 것을 알았다.

따라서, 본 실시형태에 따른 SiC 반도체 장치의 제조 방법에서, 제2 표면(100b)을 형성하는 공정(단계 S2) 후에, 액상을 이용한 세정을 하지 않고, 게이트 산화막(126)을 형성하는 공정(단계 S3)을 실시하는 것이 바람직하다. 제2 표면(100b)을 형성하는 공정 후에, 액상을 이용한 세정을 하지 않고, 게이트 산화막(126)을 형성함으로써, 액상을 이용한 세정에 기인하는 불순물의 부착을 방지할 수 있다. 이에 따라, 보다 고품질의 SiC 반도체 장치(200)를 제조할 수 있다.

본 실시형태에 따른 SiC 반도체 장치의 제조 방법은, 청정화된 에피택셜 웨이퍼의 표면에 산화막을 형성함으로써 산화막의 특성을 향상시킬 수 있기 때문에, 산화막을 갖는 반도체 디바이스에 바람직하게 이용할 수 있다. 따라서, 본 실시형태에서는, MOSFET을 제조하는 경우에 관해 설명했지만, 그 밖에, IGBT(Insulated Gate Bipolar Transistor : 절연 게이트 바이폴라 트랜지스터) 등의 절연 게이트형 전계 효과부를 갖는 반도체 디바이스나, JFET(Junction Field-Effect Transistor : 접합 전계 효과 트랜지스터) 등에 바람직하게 이용할 수 있다.

(실시형태 2)

도 8은, 본 발명의 실시형태 2에서 SiC 반도체의 주면(主面) 상에 반도체막이 형성된 SiC 반도체를 개략적으로 나타내는 단면도이다. 도 2∼도 8을 참조하여, 실시형태 2의 SiC 반도체 장치의 제조 방법을 설명한다.

우선, 도 2 및 도 3에 나타낸 바와 같이, SiC 기판(2)의 표면(2a) 상에, 불순물(도펀트)이 주입된 영역을 갖는 에피택셜층(120)이 형성된 에피택셜 웨이퍼(100)를 준비한다(단계 S1). 단계 S1은 실시형태 1과 동일하기 때문에, 그 설명은 반복하지 않는다.

다음으로, 도 2에 나타낸 바와 같이, 준비된 에피택셜 웨이퍼(100)의 제1 표면(100a)을 수소 에칭함으로써 제2 표면(100b)을 형성한다(단계 S2). 단계 S2는 실시형태 1과 동일하기 때문에, 그 설명은 반복하지 않는다.

다음으로, 도 2 및 도 8에 나타낸 바와 같이, 제2 표면(100b) 상에 규소(Si)를 포함하는 반도체막(201)을 형성하고, 그 후, 도 5에 나타낸 바와 같이, 상기 반도체막(201)을 산화하여 게이트 산화막(126)을 형성한다(단계 S3).

제2 표면(100b) 상에 Si를 포함하는 반도체막(201)을 형성하는 방법에는, 공지의 에피택셜 성장법, 예를 들어 CVD법을 이용할 수 있다.

본 공정에서, Si로 이루어진 반도체막(201)을 형성해도 좋고, 탄화규소(SiC)로 이루어진 반도체막(201)을 형성해도 좋다. 반도체막(201)이 Si로 이루어진 경우, 에피택셜 웨이퍼(100)와 게이트 산화막(126)의 계면이나 게이트 산화막(126) 중에 탄소가 존재하는 것을 억제할 수 있기 때문에, 제조하는 반도체 장치의 품질을 보다 높일 수 있다. 반도체막(201)이 SiC로 이루어진 경우, 하지인 에피택셜층(120)과 형성하는 반도체막(201)의 결정이 동일하기 때문에, 반도체막(201)을 용이하게 형성할 수 있다.

이 단계 S3에서는, 게이트 산화막(126)의 두께를 결정하여, (반도체막(201) 아래의 에피택셜 웨이퍼(100)를 산화시키지 않고) 반도체막(201)을 모두 산화했을 때, 결정한 게이트 산화막(126)의 두께가 되도록 반도체막(201)의 두께를 제어하는 것이 바람직하다. 즉, 반도체막(201)을 모두 산화하여 이루어진 게이트 산화막(126)의 두께에 따라서, 반도체막(201)의 두께를 결정하는 것이 바람직하다. 이것은, 예를 들어, 반도체막(201)이 산화되어 게이트 산화막(126)이 될 때, 산소(O)를 도입함에 따라 막두께가 증가하는 것을 고려하여, 반도체막(201)의 두께를 계산 등에 의해 제어함으로써 실현한다.

예를 들어, 반도체막(201)이 Si로 이루어진 경우, 원하는 산화막의 두께의 0.44배 정도의 두께가 되도록 형성하는 것이 바람직하다. 이와 같이 반도체막(201)의 두께를 설계함으로써, 반도체막(201)이 산화되어 게이트 산화막(126)이 되는 경우에, 산소의 도입에 따라 막두께가 증가하더라도, 게이트 산화막(126)의 두께를 설계 두께로 할 수 있다. 또한, 이때, 이온 주입된 에피택셜 웨이퍼(100)의 불순물을 포함하지 않도록, 에피택셜 웨이퍼(100)를 산화시키지 않고, 반도체막(201)만을 산화하여, 게이트 산화막(126)을 형성하는 것이 바람직하다. 이에 따라, 에피택셜 웨이퍼(100)의 이온 주입 프로파일에 미치는 영향을 저감할 수 있다.

반도체막(201)의 산화의 방법은 특별히 한정되지 않고, 예를 들어, 드라이 산화법, 웨트 산화법, 파이로제닉 산화법 등을 이용할 수 있다.

다음으로, 도 2에 나타낸 바와 같이, 게이트 산화막(126)을 어닐링 처리한다(단계 S4). 단계 S4는 실시형태 1과 동일하기 때문에, 그 설명은 반복하지 않는다.

다음으로, 도 2 및 도 7에 나타낸 바와 같이, 게이트 산화막(126)이 형성된 에피택셜 웨이퍼(100)에 대하여, 게이트 전극(110), 소스 전극(127) 및 드레인 전극(112)을 형성한다(단계 S5). 단계 S5는 실시형태 1과 동일하기 때문에, 그 설명은 반복하지 않는다. 이상의 공정(단계 S1∼S5)을 실시함으로써, 도 7에 나타내는 SiC 반도체 장치(200)가 제조된다.

이상 설명한 바와 같이, 본 실시형태에서의 SiC 반도체 장치의 제조 방법은, 적어도 일부에 불순물이 주입된 제1 표면(100a)을 포함하는 에피택셜 웨이퍼(100)를 준비하는 공정(단계 S1)과, 제1 표면(100a)을 수소 에칭함으로써 제2 표면(100b)을 형성하는 공정(단계 S2)과, 제2 표면(100b) 상에 SiC 반도체 장치(200)를 구성하는 게이트 산화막(126)을 형성하는 공정(단계 S3)을 포함한다. 그리고, 게이트 산화막(126)을 형성하는 공정(단계 S3)은, 제2 표면(100b) 상에 Si를 포함하는 반도체막(201)을 형성하고, 반도체막(201)을 산화함으로써 게이트 산화막(126)을 형성한다.

본 발명자는, 적어도 일부에 불순물이 주입된 제2 표면(100b)을 산화하여 게이트 산화막(126)을 형성할 때, 게이트 산화막(126)이 균일하게 형성되지 않는 경우가 있는 것에 착안했다. 구체적으로는, 이온 주입 영역을 갖는 제2 표면(100b)은, 불순물이 주입되어 있는 영역과 불순물이 주입되지 않은 영역을 갖는다. 또, 불순물이 주입되어 있는 영역에서도, 주입되는 불순물이 상이하고 또 그 농도도 상이하다. 불순물의 농도, 불순물의 종류에 따라 SiC 반도체의 산화율이 상이하기 때문에, 상기와 같은 제2 표면(100b)을 갖는 에피택셜 웨이퍼(100)를 산화하는 경우, 면내의 각 위치에서 깊이 방향의 산화율에 변동이 생겨 버린다.

따라서, 본 발명자는 게이트 산화막(126)을 균일하게 형성하기 위해, 더욱 예의 검토를 거듭한 바, 제2 표면(100b) 상에 Si를 포함하는 막을 형성하고, 이것을 산화하여 게이트 산화막(126)을 형성함으로써, 균일한 게이트 산화막(126)을 형성할 수 있는 것을 알아냈다.

따라서, 본 실시형태에서는, 단계 S2에서 에피택셜 웨이퍼(100)의 제1 표면(100a)을 수소 에칭하여 제2 표면(100b)을 형성한 후, 제2 표면(100b) 상에 Si를 포함하는 반도체막(201)을 형성한다. 그리고, 이 반도체막(201)을 산화하여 게이트 산화막(126)으로 한다. 이에 따라, 청정화된 제2 표면(100b)에, 제2 표면(100b)의 불순물의 농도나 종류에 의존하지 않고, 반도체막(201)을 형성할 수 있다. 또 반도체막(201)에는 불순물이 주입되지 않았기 때문에, 반도체막(201)의 품질은 균일해져, 반도체막(201)의 면내의 각 위치에서의 깊이 방향의 산화율은 균일해진다. 따라서, 청정한 제2 표면(100b) 상에, 보다 균일한 품질의 게이트 산화막(126)을 형성할 수 있어, SiC 반도체 장치(200)의 품질을 보다 향상시킬 수 있다.

이와 같이, 본 실시형태에 의하면, 게이트 산화막(126)의 절연 특성을 향상시킬 수 있고, 에피택셜 웨이퍼(100)와 게이트 산화막(126)의 계면이나 게이트 산화막(126) 중에 존재하는 불순물, 파티클 등을 저감할 수 있다. 또한, 게이트 산화막(126)의 품질의 균일성을 향상시킬 수 있다. 따라서, SiC 반도체 장치(200)의 품질을 보다 향상시킬 수 있다.

본 실시형태에서, 도 1의 제조 장치(10)를 이용하는 경우에는, 제거부(11) 및 형성부(12) 중 어느 것에, Si 원소를 포함하는 반도체막(201)을 형성하는 장치, 바람직하게는 CVD 장치가 포함된다. 상기 반도체막(201)을 형성하는 장치를 설치하는 위치는, 제거부(11) 내 또는 형성부(12)에 한정되지 않고, 예를 들어, 제거부(11)와 접속부(13) 사이, 또는 접속부(13)와 형성부(12) 사이에 별도로 설치되어도 좋다. 이 경우, 반도체막(201)을 형성하는 장치의 내부와 다른 연결부 사이에서, 에피택셜 웨이퍼(100)가 대기에 차단된 분위기 내에 배치되는 것이 바람직하다.

이에 따라, 제2 표면(100b)을 대기에 노출시키지 않고 반도체막(201)을 형성할 수 있고, 또 반도체막(201)을 대기에 노출시키지 않고 산화할 수 있다. 따라서, 보다 고품질의 SiC 반도체 장치(200)를 제조할 수 있다.

실시예

(실시예 1)

본 실시예 1에서는, SiC 반도체로서, 도 9에 나타내는 에피택셜 웨이퍼(130)를 이용하고, 상기 에피택셜 웨이퍼(130)의 제1 표면(130a)을 수소 에칭하여 청정화하는 것의 효과에 관해 조사했다. 도 9는, 실시예 1, 비교예 1 및 비교예 2에서 이용하는 에피택셜 웨이퍼를 개략적으로 나타내는 단면도이다.

구체적으로는, 우선, SiC 기판(2)으로서, 표면(2a)을 갖는 4H-SiC 기판을 준비했다. 다음으로, 에피택셜층(120)을 구성하는 층으로서, 10 ㎛의 두께를 가지며, 1×1016 cm-3의 불순물 농도를 갖는 n형 SiC층(131)을 CVD법에 의해 성장시켰다.

다음으로, SiO2를 마스크로서 이용하고, 알루미늄(Al)을 p형 불순물로 하여 2×1016 cm-3의 도펀트 농도를 갖는 p 보디 영역(123)을 형성하고, 또한 인(P)을 n형 불순물로 하여 1×1019 cm-3의 불순물 농도를 갖는 n+ 소스 영역(124)을 형성했다. 또, 알루미늄(Al)을 p형 불순물로 하여 1×1019 cm-3의 불순물 농도를 갖는 p+ 영역(125)을 형성했다.

다음으로, 활성화 어닐링 처리를 행했다. 이 활성화 어닐링 처리로는, Ar 가스를 분위기 가스로서 이용하여, 가열 온도 1700∼1800℃, 가열 시간 30분의 조건으로 했다. 이에 따라, 제1 표면(130a)을 갖는 에피택셜 웨이퍼(130)를 준비했다(단계 S1).

다음으로, 준비된 에피택셜 웨이퍼(100)의 주면의 제1 표면(130a)을 수소 에칭에 의해 제거했다(단계 S2).

구체적으로는, 에피택셜 웨이퍼(130)를 반응로 내에 수용하여, 상기 에피택셜 웨이퍼(130)를 1300℃ 이상 1650℃ 이하로 제어된 배치대에서 가열하면서, 제1 표면(130a)을 수소 에칭했다. 수소 에칭의 조건은, 반응로 내에 도입되는 수소 가스의 유량이 50∼200 slm이고, 로내 압력이 20∼150 hPa이고, 반응 시간은 1시간으로 했다.

(비교예 1)

비교예 1은, 기본적으로는 실시예 1과 동일했지만, 단계 S2의 수소 에칭을 행하지 않은 점에서 상이했다. 즉, 비교예 1에서는, 단계 S1에서 준비한 에피택셜 웨이퍼(130)에 대해서는 세정 처리를 행하지 않았다.

(비교예 2)

비교예 2는 기본적으로는 실시예 1과 동일했지만, 단계 S2에서, 수소 에칭 대신 액상을 이용한 약액 세정에 의해 SiC 반도체의 표면을 세정한 점에서 상이했다. 액상으로서, 황산(H2SO4):과산화수소수(H2O2)를 5:1의 체적비로 혼합한 혼합 용액 1과, 암모니아수:과산화수소수:순수를 1:1:5의 체적비로 혼합한 혼합 용액 2와, 염화수소(HCl):과산화수소:순수를 1:1:6의 체적비로 혼합한 혼합 용액 3과, 10%의 불화수소(HF) 용액을 이용했다. 즉, 비교예 2에서는, 준비한 에피택셜 웨이퍼(130)를 혼합 용액 1에 0.5시간 침지한 후, 혼합 용액 2에 10분간 침지하고, HF 용액에 10분간 침지하고, 혼합 용액 3에 10분간 침지하고, 혼합 용액 2에 10분간 침지하고, HF 용액에 10분간 침지하여, 약액 세정을 행했다. 약액 세정 후의 에피택셜 웨이퍼(130)는, Ar건 또는 N2건을 이용하여, 아르곤 가스 또는 N2 가스로 블로우함으로써 건조시켰다.

(표면의 불순물의 측정)

실시예 1, 비교예 1 및 비교예 2의 에피택셜 웨이퍼(130)의 표면을, TXRF(전반사 형광 X선 분석법)에 제공했다. TXRF에서, 여기원으로서 W(텅스텐)-Lβ선을 이용했다.

TXRF에 의해 실시예 1, 비교예 1 및 비교예 2의 에피택셜 웨이퍼(130)의 표면의 불순물을 측정했다. 실시예 1에서의 수소 에칭 후의 에피택셜 웨이퍼(130)의 표면은, 수소 에칭을 행하지 않은 비교예 1의 표면과 비교하여, 불순물이 저감되었다. 따라서, 수소 에칭 후의 에피택셜 웨이퍼(130)에 게이트 산화막 및 전극을 형성하여 SiC 반도체 장치를 제조함으로써, 고품질의 SiC 반도체 장치를 제조할 수 있다는 것을 알았다.

또, 비교예 2에서의 액상을 이용하여 세정한 후의 에피택셜 웨이퍼(130)의 표면은, 비교예 1보다 불순물이 더 많아진 것을 알았다. 이 결과를 도 10 및 도 11에 나타낸다.

도 10은, 비교예 1의 SiC 반도체의 표면을 TXRF로 측정한 결과를 나타내는 스펙트럼이고, 도 11은, 비교예 2의 SiC 반도체의 표면을 TXRF로 측정한 결과를 나타내는 스펙트럼이다. 각 도면에서, 횡축은 에너지 강도를, 종축은 스펙트럼 강도를 나타내고 있고, 피크의 높이가 클수록 그 원소가 많이 검출된 것이 된다. 또, 예를 들어, 도 10 중의 세로에 기재되는 「Cl, Ka」란, Cl-Kα선이 검출된 것을 나타내고, 다른 기재도 마찬가지이다. 또, 에너지 강도가 9.67 eV 부근인 피크는 여기선원인 W-Lβ선의 피크이다.

도 10 및 도 11을 비교하면, 비교예 1에서, 염소(Cl)만이 검출된 데 비해, 비교예 2에서는, 염소(Cl), 칼슘(Ca), 니켈(Ni) 및 철(Fe)이 검출되었다. 이에 따라, 에피택셜 웨이퍼(130)의 표면을 종래의 세정 처리에 제공한 경우, 표면이 청정화되지 않을 뿐만 아니라, 반대로 불순물이 부착되어 버리는 것을 알 수 있다.

따라서, 실시예 1에서의 수소 에칭 후의 에피택셜 웨이퍼(130)에 대하여 액상을 이용한 세정을 하지 않고, 산화막 및 전극을 형성하여 SiC 반도체 장치를 제조함으로써, 비교예 2의 SiC 반도체 장치와 비교하여, 보다 고품질의 SiC 반도체 장치를 제조할 수 있다는 것을 알았다.

이상과 같이 본 발명의 실시형태 및 실시예에 관해 설명했지만, 각 실시형태 및 실시예의 특징을 적절하게 조합하는 것도 당초부터 예정하였다. 또, 이번에 개시된 실시형태 및 실시예는 모든 점에서 예시이며 제한적인 것은 아니라고 생각되어야 한다. 본 발명의 범위는 상기 실시형태 및 실시예가 아니라 청구범위에 의해 나타나며, 청구범위와 균등한 의미 및 범위 내에서의 모든 변경이 포함되는 것이 의도된다.

2 : SiC 기판 2a : 표면

10 : 제조 장치 11 : 제거부

12 : 형성부 13 : 접속부

100, 130 : 에피택셜 웨이퍼 100a, 130a : 제1 표면

100b : 제2 표면 110 : 게이트 전극

111 : 소스 컨택트 전극 112 : 드레인 전극

120 : 에피택셜층 121 : 버퍼층

122 : 드리프트층 123 : 보디 영역

124 : 소스 영역 125 : p+ 영역

126 : 게이트 산화막 127 : 소스 전극

200 : SiC 반도체 장치 201 : 반도체막

10 : 제조 장치 11 : 제거부

12 : 형성부 13 : 접속부

100, 130 : 에피택셜 웨이퍼 100a, 130a : 제1 표면

100b : 제2 표면 110 : 게이트 전극

111 : 소스 컨택트 전극 112 : 드레인 전극

120 : 에피택셜층 121 : 버퍼층

122 : 드리프트층 123 : 보디 영역

124 : 소스 영역 125 : p+ 영역

126 : 게이트 산화막 127 : 소스 전극

200 : SiC 반도체 장치 201 : 반도체막

Claims (8)

- 탄화규소 반도체 장치(200)를 제조하는 방법으로서,

적어도 일부에 불순물이 주입된 제1 표면(100a)을 포함하는 탄화규소 반도체(100)를 준비하는 공정과,

상기 탄화규소 반도체(100)의 상기 제1 표면(100a)을, 수소 가스를 포함하는 가스를 이용하여 드라이 에칭함으로써 제2 표면(100b)을 형성하는 공정과,

상기 제2 표면(100b) 상에, 상기 탄화규소 반도체 장치(200)를 구성하는 산화막(126)을 형성하는 공정

을 포함하는 탄화규소 반도체 장치(200)의 제조 방법. - 제1항에 있어서, 상기 제2 표면(100b)을 형성하는 공정 후에, 액상을 이용한 세정을 하지 않고, 상기 산화막(126)을 형성하는 공정을 실시하는 것인 탄화규소 반도체 장치(200)의 제조 방법.

- 제1항에 있어서, 상기 제2 표면(100b)을 형성하는 공정에서, 상기 드라이 에칭을 1300℃ 이상 1650℃ 이하의 온도 범위에서 행하는 것인 탄화규소 반도체 장치(200)의 제조 방법.

- 제1항에 있어서, 상기 산화막(126)을 형성하는 공정은, 상기 제2 표면(100b) 상에 규소를 포함하는 막(201)을 형성하고, 상기 규소를 포함하는 막(201)을 산화함으로써, 상기 산화막(126)을 형성하는 것인 탄화규소 반도체 장치(200)의 제조 방법.

- 제1항에 있어서, 상기 제2 표면(100b)을 형성하는 공정에서, 상기 가스는 염화수소 가스를 더 포함하는 것인 탄화규소 반도체 장치(200)의 제조 방법.

- 제1항에 있어서, 상기 제2 표면(100b)을 형성하는 공정에서, 상기 가스는 탄화수소 가스를 더 포함하는 것인 탄화규소 반도체 장치(200)의 제조 방법.

- 제1항에 있어서, 상기 제2 표면(100b)을 형성하는 공정과 상기 산화막(126)을 형성하는 공정 사이에서, 상기 탄화규소 반도체(100)는 대기 차단된 분위기 내에 배치되는 것인 탄화규소 반도체 장치(200)의 제조 방법.

- 탄화규소 반도체(100)에서, 적어도 일부에 불순물이 주입된 제1 표면(100a)을, 수소 가스를 포함하는 가스를 이용한 드라이 에칭에 의해 제거하기 위한 제거부(11)와,

상기 탄화규소 반도체(100)에서 상기 제1 표면(100a)이 제거됨으로써 형성된 제2 표면(100b)에 상기 탄화규소 반도체 장치(200)를 구성하는 산화막(126)을 형성하기 위한 형성부(12)와,

상기 탄화규소 반도체(100)를 반송할 수 있게 상기 제거부(11)와 상기 형성부(12)를 접속하는 접속부(13)를 포함하고,

상기 접속부(13)에서의 상기 탄화규소 반도체(100)를 반송시키는 영역은 대기 차단이 가능한 것인 탄화규소 반도체 장치(200)의 제조 장치(10).

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010136866A JP2012004269A (ja) | 2010-06-16 | 2010-06-16 | 炭化珪素半導体装置の製造方法および炭化珪素半導体装置の製造装置 |

| JPJP-P-2010-136866 | 2010-06-16 | ||

| PCT/JP2011/054010 WO2011158528A1 (ja) | 2010-06-16 | 2011-02-23 | 炭化珪素半導体装置の製造方法および炭化珪素半導体装置の製造装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20130076791A true KR20130076791A (ko) | 2013-07-08 |

Family

ID=45347940

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020127012240A Withdrawn KR20130076791A (ko) | 2010-06-16 | 2011-02-23 | 탄화규소 반도체 장치의 제조 방법 및 탄화규소 반도체 장치의 제조 장치 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US20120214309A1 (ko) |

| EP (1) | EP2584594A4 (ko) |

| JP (1) | JP2012004269A (ko) |

| KR (1) | KR20130076791A (ko) |

| CN (1) | CN102782820A (ko) |

| CA (1) | CA2779426A1 (ko) |

| TW (1) | TW201203391A (ko) |

| WO (1) | WO2011158528A1 (ko) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10256094B2 (en) * | 2009-08-20 | 2019-04-09 | The Government Of The United States Of America, As Represented By The Secretary Of The Navy | Reduction of basal plane dislocations in epitaxial SiC using an in-situ etch process |

| JP2012004275A (ja) | 2010-06-16 | 2012-01-05 | Sumitomo Electric Ind Ltd | 炭化珪素半導体装置の製造方法 |

| WO2013145023A1 (ja) * | 2012-03-30 | 2013-10-03 | 株式会社日立製作所 | 電界効果型炭化珪素トランジスタ |

| US8860040B2 (en) | 2012-09-11 | 2014-10-14 | Dow Corning Corporation | High voltage power semiconductor devices on SiC |

| US9018639B2 (en) | 2012-10-26 | 2015-04-28 | Dow Corning Corporation | Flat SiC semiconductor substrate |

| JP6162388B2 (ja) * | 2012-11-14 | 2017-07-12 | 新日本無線株式会社 | 炭化珪素半導体装置の製造方法 |

| US9017804B2 (en) | 2013-02-05 | 2015-04-28 | Dow Corning Corporation | Method to reduce dislocations in SiC crystal growth |

| US9797064B2 (en) | 2013-02-05 | 2017-10-24 | Dow Corning Corporation | Method for growing a SiC crystal by vapor deposition onto a seed crystal provided on a support shelf which permits thermal expansion |

| US9738991B2 (en) | 2013-02-05 | 2017-08-22 | Dow Corning Corporation | Method for growing a SiC crystal by vapor deposition onto a seed crystal provided on a supporting shelf which permits thermal expansion |

| US8940614B2 (en) | 2013-03-15 | 2015-01-27 | Dow Corning Corporation | SiC substrate with SiC epitaxial film |

| JP6206012B2 (ja) * | 2013-09-06 | 2017-10-04 | 住友電気工業株式会社 | 炭化珪素半導体装置 |

| JP6222771B2 (ja) | 2013-11-22 | 2017-11-01 | 国立研究開発法人産業技術総合研究所 | 炭化珪素半導体装置の製造方法 |

| US9279192B2 (en) | 2014-07-29 | 2016-03-08 | Dow Corning Corporation | Method for manufacturing SiC wafer fit for integration with power device manufacturing technology |

| JP6314965B2 (ja) * | 2015-12-11 | 2018-04-25 | トヨタ自動車株式会社 | 半導体装置の製造方法 |

| EP4266354B1 (en) * | 2020-12-18 | 2025-04-16 | Kyoto University | Sic semiconductor element manufacturing method |

| IT202300010203A1 (it) * | 2023-05-19 | 2024-11-19 | Consiglio Nazionale Ricerche | Un transistor di potenza per un dispositivo a semiconduttore |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6066866A (ja) * | 1983-09-24 | 1985-04-17 | Sharp Corp | 炭化珪素mos構造の製造方法 |

| JP3261683B2 (ja) | 1991-05-31 | 2002-03-04 | 忠弘 大見 | 半導体の洗浄方法及び洗浄装置 |

| JPH06314679A (ja) | 1993-04-30 | 1994-11-08 | Sony Corp | 半導体基板の洗浄方法 |

| JPH0851110A (ja) * | 1994-08-05 | 1996-02-20 | Matsushita Electric Ind Co Ltd | 絶縁膜の形成方法 |

| US5787104A (en) * | 1995-01-19 | 1998-07-28 | Matsushita Electric Industrial Co., Ltd. | Semiconductor light emitting element and method for fabricating the same |

| JPH0952796A (ja) * | 1995-08-18 | 1997-02-25 | Fuji Electric Co Ltd | SiC結晶成長方法およびSiC半導体装置 |

| JPH10261615A (ja) * | 1997-03-17 | 1998-09-29 | Fuji Electric Co Ltd | SiC半導体の表面モホロジー制御方法およびSiC半導体薄膜の成長方法 |

| JP3085272B2 (ja) * | 1997-12-19 | 2000-09-04 | 富士電機株式会社 | 炭化けい素半導体装置の熱酸化膜形成方法 |

| JP2000349081A (ja) * | 1999-06-07 | 2000-12-15 | Sony Corp | 酸化膜形成方法 |

| JP2001332508A (ja) * | 2000-05-23 | 2001-11-30 | Matsushita Electric Ind Co Ltd | 半導体素子の製造方法 |

| JP3534056B2 (ja) * | 2000-08-31 | 2004-06-07 | 日産自動車株式会社 | 炭化珪素半導体装置の製造方法 |

| EP1491662B1 (en) * | 2002-03-19 | 2012-02-22 | Central Research Institute of Electric Power Industry | METHOD FOR PREPARING SiC CRYSTAL |

| JP2006321707A (ja) * | 2005-04-22 | 2006-11-30 | Bridgestone Corp | 炭化ケイ素単結晶ウェハ及びその製造方法 |

| JP2006351744A (ja) * | 2005-06-15 | 2006-12-28 | Fuji Electric Holdings Co Ltd | 炭化珪素半導体装置の製造方法 |

| JP2007053227A (ja) * | 2005-08-18 | 2007-03-01 | Matsushita Electric Ind Co Ltd | 半導体素子およびその製造方法 |

| CN101263589B (zh) * | 2005-09-13 | 2010-08-25 | 大见忠弘 | 半导体装置的制造方法及半导体制造装置 |

| JP2008098200A (ja) * | 2006-10-05 | 2008-04-24 | Kiyoyoshi Mizuno | 成膜体およびその製造方法 |

| US7781312B2 (en) * | 2006-12-13 | 2010-08-24 | General Electric Company | Silicon carbide devices and method of making |

| JP5509520B2 (ja) * | 2006-12-21 | 2014-06-04 | 富士電機株式会社 | 炭化珪素半導体装置の製造方法 |

| JP5125095B2 (ja) * | 2006-12-22 | 2013-01-23 | パナソニック株式会社 | SiCエピタキシャル膜付き基板の製造方法及びSiCエピタキシャル膜付き基板の製造装置 |

| JP5095253B2 (ja) * | 2007-03-30 | 2012-12-12 | 富士通株式会社 | 半導体エピタキシャル基板、化合物半導体装置、およびそれらの製造方法 |

| KR101333337B1 (ko) * | 2009-01-30 | 2013-11-25 | 신닛테츠스미킨 카부시키카이샤 | 에피텍셜 탄화규소 단결정 기판 및 그 제조 방법 |

-

2010

- 2010-06-16 JP JP2010136866A patent/JP2012004269A/ja active Pending

-

2011

- 2011-02-23 EP EP11795436.2A patent/EP2584594A4/en not_active Withdrawn

- 2011-02-23 KR KR1020127012240A patent/KR20130076791A/ko not_active Withdrawn

- 2011-02-23 US US13/503,964 patent/US20120214309A1/en not_active Abandoned

- 2011-02-23 WO PCT/JP2011/054010 patent/WO2011158528A1/ja active Application Filing

- 2011-02-23 CA CA2779426A patent/CA2779426A1/en not_active Abandoned

- 2011-02-23 CN CN2011800047820A patent/CN102782820A/zh active Pending

- 2011-05-10 TW TW100116378A patent/TW201203391A/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| CA2779426A1 (en) | 2011-12-22 |

| TW201203391A (en) | 2012-01-16 |

| WO2011158528A1 (ja) | 2011-12-22 |

| EP2584594A4 (en) | 2014-07-23 |

| JP2012004269A (ja) | 2012-01-05 |

| EP2584594A1 (en) | 2013-04-24 |

| CN102782820A (zh) | 2012-11-14 |

| US20120214309A1 (en) | 2012-08-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20130076791A (ko) | 탄화규소 반도체 장치의 제조 방법 및 탄화규소 반도체 장치의 제조 장치 | |

| US8642476B2 (en) | Method for manufacturing silicon carbide semiconductor device | |

| US20130045592A1 (en) | Method for manufacturing silicon carbide semiconductor device and device for manufacturing silicon carbide semiconductor device | |

| US20120178259A1 (en) | Method of cleaning silicon carbide semiconductor and apparatus for cleaning silicon carbide semiconductor | |

| US9184276B2 (en) | Method and apparatus for manufacturing silicon carbide semiconductor device | |

| US7122488B2 (en) | High density plasma process for the formation of silicon dioxide on silicon carbide substrates | |

| US8785301B2 (en) | Method of cleaning silicon carbide semiconductor | |

| JP2008205296A (ja) | 炭化珪素半導体素子及びその製造方法 | |

| US20110309376A1 (en) | Method of cleaning silicon carbide semiconductor, silicon carbide semiconductor, and silicon carbide semiconductor device | |

| JP3963154B2 (ja) | 炭化珪素ショットキーバリアダイオードの製造方法 | |

| US20120174944A1 (en) | Cleaning method for silicon carbide semiconductor and cleaning apparatus for silicon carbide semiconductor | |

| JP5172426B2 (ja) | Iii−v族化合物半導体の結晶成長方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20120511 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| PC1203 | Withdrawal of no request for examination | ||

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |