KR20100116631A - 선택적 저온 루테늄 증착을 반도체 디바이스의 구리 금속 배선에 통합하는 방법 - Google Patents

선택적 저온 루테늄 증착을 반도체 디바이스의 구리 금속 배선에 통합하는 방법 Download PDFInfo

- Publication number

- KR20100116631A KR20100116631A KR1020107018622A KR20107018622A KR20100116631A KR 20100116631 A KR20100116631 A KR 20100116631A KR 1020107018622 A KR1020107018622 A KR 1020107018622A KR 20107018622 A KR20107018622 A KR 20107018622A KR 20100116631 A KR20100116631 A KR 20100116631A

- Authority

- KR

- South Korea

- Prior art keywords

- metal

- precursor

- metal film

- gas

- vapor

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 120

- 238000000151 deposition Methods 0.000 title claims abstract description 55

- 239000004065 semiconductor Substances 0.000 title claims abstract description 20

- 238000001465 metallisation Methods 0.000 title abstract description 14

- 239000010949 copper Substances 0.000 title description 58

- 230000008021 deposition Effects 0.000 title description 30

- 229910052802 copper Inorganic materials 0.000 title description 6

- 229910052707 ruthenium Inorganic materials 0.000 title description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 title description 3

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 title description 3

- 229910052751 metal Inorganic materials 0.000 claims abstract description 151

- 239000002184 metal Substances 0.000 claims abstract description 151

- 239000000758 substrate Substances 0.000 claims abstract description 101

- 239000002243 precursor Substances 0.000 claims description 128

- 230000008569 process Effects 0.000 claims description 77

- 230000008016 vaporization Effects 0.000 claims description 30

- 238000009834 vaporization Methods 0.000 claims description 28

- 238000010438 heat treatment Methods 0.000 claims description 20

- 239000007787 solid Substances 0.000 claims description 11

- 230000004888 barrier function Effects 0.000 claims description 8

- 238000005019 vapor deposition process Methods 0.000 claims description 5

- 238000000137 annealing Methods 0.000 claims 2

- 238000004519 manufacturing process Methods 0.000 abstract description 9

- 238000012546 transfer Methods 0.000 abstract description 9

- 150000002739 metals Chemical class 0.000 abstract description 2

- 239000007789 gas Substances 0.000 description 80

- 239000010410 layer Substances 0.000 description 54

- 239000010408 film Substances 0.000 description 50

- 239000000463 material Substances 0.000 description 26

- 238000009826 distribution Methods 0.000 description 22

- 230000009977 dual effect Effects 0.000 description 12

- 238000012545 processing Methods 0.000 description 12

- 235000012431 wafers Nutrition 0.000 description 9

- 239000012159 carrier gas Substances 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- 239000012530 fluid Substances 0.000 description 6

- 238000005086 pumping Methods 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- 229910052786 argon Inorganic materials 0.000 description 4

- 239000003989 dielectric material Substances 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 230000008020 evaporation Effects 0.000 description 3

- 238000001704 evaporation Methods 0.000 description 3

- 238000002203 pretreatment Methods 0.000 description 3

- 238000000859 sublimation Methods 0.000 description 3

- 230000008022 sublimation Effects 0.000 description 3

- 238000011282 treatment Methods 0.000 description 3

- ITWBWJFEJCHKSN-UHFFFAOYSA-N 1,4,7-triazonane Chemical compound C1CNCCNCCN1 ITWBWJFEJCHKSN-UHFFFAOYSA-N 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000009833 condensation Methods 0.000 description 2

- 230000005494 condensation Effects 0.000 description 2

- 238000000354 decomposition reaction Methods 0.000 description 2

- 238000007772 electroless plating Methods 0.000 description 2

- 230000005284 excitation Effects 0.000 description 2

- 238000011049 filling Methods 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 229910052743 krypton Inorganic materials 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 229910052754 neon Inorganic materials 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 230000027756 respiratory electron transport chain Effects 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 101100521334 Mus musculus Prom1 gene Proteins 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- FEBFYWHXKVOHDI-UHFFFAOYSA-N [Co].[P][W] Chemical compound [Co].[P][W] FEBFYWHXKVOHDI-UHFFFAOYSA-N 0.000 description 1

- 238000002835 absorbance Methods 0.000 description 1

- 239000003929 acidic solution Substances 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000012790 adhesive layer Substances 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 238000000231 atomic layer deposition Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000006227 byproduct Substances 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 125000002915 carbonyl group Chemical group [*:2]C([*:1])=O 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 238000004590 computer program Methods 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000005383 fluoride glass Substances 0.000 description 1

- -1 for example Chemical class 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 238000011534 incubation Methods 0.000 description 1

- 239000012705 liquid precursor Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 125000000740 n-pentyl group Chemical group [H]C([H])([H])C([H])([H])C([H])([H])C([H])([H])C([H])([H])* 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 239000003921 oil Substances 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 230000002028 premature Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 238000013515 script Methods 0.000 description 1

- ABTOQLMXBSRXSM-UHFFFAOYSA-N silicon tetrafluoride Chemical compound F[Si](F)(F)F ABTOQLMXBSRXSM-UHFFFAOYSA-N 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 238000000427 thin-film deposition Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76843—Barrier, adhesion or liner layers formed in openings in a dielectric

- H01L21/76849—Barrier, adhesion or liner layers formed in openings in a dielectric the layer being positioned on top of the main fill metal

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/02—Pretreatment of the material to be coated

- C23C16/0209—Pretreatment of the material to be coated by heating

- C23C16/0218—Pretreatment of the material to be coated by heating in a reactive atmosphere

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/06—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of metallic material

- C23C16/16—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of metallic material from metal carbonyl compounds

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/448—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for generating reactive gas streams, e.g. by evaporation or sublimation of precursor materials

- C23C16/4481—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for generating reactive gas streams, e.g. by evaporation or sublimation of precursor materials by evaporation using carrier gas in contact with the source material

- C23C16/4482—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for generating reactive gas streams, e.g. by evaporation or sublimation of precursor materials by evaporation using carrier gas in contact with the source material by bubbling of carrier gas through liquid source material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28556—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table by chemical means, e.g. CVD, LPCVD, PECVD, laser CVD

- H01L21/28562—Selective deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

- H01L21/76883—Post-treatment or after-treatment of the conductive material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- General Chemical & Material Sciences (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Organic Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Metallurgy (AREA)

- Mechanical Engineering (AREA)

- Materials Engineering (AREA)

- Electrodes Of Semiconductors (AREA)

- Chemical Vapour Deposition (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

본 발명은 벌크 Cu 금속에서의 전자 이동 및 응력 이동을 향상시키도록, 선택적 저온 Ru 금속 증착을 반도체 디바이스의 제조에 통합하는 방법을 제공한다. 이 방법은, 유전체층(304)에 오목한 피쳐를 갖는 패턴화된 기판으로서, 상기 오목한 피쳐에는 평탄화된 벌크 Cu 금속(322)이 적어도 실질적으로 충전되어 있는 것인 패턴화된 기판을 마련하는 단계와, 상기 벌크 Cu 금속 및 상기 유전체층을 H2, N2, 또는 NH3, 또는 이들의 조합의 존재 하에서 열처리하는 단계, 그리고 열처리된 상기 평탄화된 벌크 Cu 금속 상에 Ru 금속막(324)을 선택적으로 증착하는 단계를 포함한다.

Description

관련 출원에 대한 상호 참조

본 발명은 저저항 구리막 구조 형성 방법(METHOD OF FORMING LOW RESISTIVITY COPPER FILM STRUCTURE)이란 제목의 미국 특허 출원 제11/693,298호와 관련이 있다. 본 발명은 선택적 루테늄 증착을 반도체 디바이스의 제조에 통합하는 방법(METHOD FOR INTEGRATING SELECTIVE RUTHENIUM DEPOSITION INTO MANUFACTURING OF A SEMICONDUCTOR DEVICE)이란 제목의 미국 특허 출원 제11/853,393호와 관련이 있다. 이들 출원의 모든 내용은 본원에 참조로 인용되어 있다. 이들 관련 출원은 일반에 귀속되지 않았다.

본 발명은 반도체 처리와 반도체 디바이스에 관한 것이며, 더 구체적으로는 반도체 디바이스를 제조하기 위해 루테늄 금속막을 선택적으로 증착하는 방법에 관한 것이다.

집적 회로는 다양한 반도체 디바이스와, 이들 반도체 디바이스에 전력을 제공하여 이들 반도체 디바이스가 정보를 공유 및 교환할 수 있도록 하는 복수의 도전성 금속 경로를 포함한다. 집적 회로 내에는, 금속층들을 서로 절연시키는 금속간 또는 층간 유전체층을 사용하여, 금속층들이 서로 적층되어 있다. 일반적으로, 각 금속층은 적어도 하나의 추가적인 금속층과 전기 접촉을 형성해야 한다. 이러한 전기 접촉은, 금속층들을 분리하는 층간 유전체에 구멍(즉, 비아)을 에칭하고, 이로 인해 형성된 비아에 금속을 채워 상호접속을 일으킴으로써 이루어진다. "비아"는 일반적으로, 유전체층 내에 형성되며, 금속으로 충전되는 경우, 유전체층을 통하여 유전체층 아래의 도전층과의 전기 접속을 제공하는, 예컨대 구멍, 라인 또는 그 밖의 다양한 구조 등의 임의의 오목한 피쳐를 지칭한다. 이와 마찬가지로, 두 개 이상의 비아를 접속하는 오목한 피쳐를 일반적으로 트렌치라고 한다.

집적 회로를 제조하는 다층 금속 배선 방법에 구리(Cu) 금속을 사용하면, 해결책을 필요로 하는 몇 가지 문제가 발생하였다. 예를 들어, 유전체 물질 및 Si에서의 Cu 원자의 높은 이동성에 의해, Cu 원자는 이러한 물질 내로 이동할 수 있게 되며, 그 결과 집적 회로를 손상시킬 수 있는 전기적 결함이 형성된다. 따라서, Cu 금속층, Cu 충전 트렌치 및 Cu 충전 비아는, 일반적으로 Cu 원자가 유전체 물질 내로 확산되는 것을 방지하도록 배리어층에 의해 둘러싸인다. 배리어층은 일반적으로 Cu 증착에 앞서 트렌치와 비아의 측벽 및 바닥에 증착되며, 바람직하게는 Cu와 반응 및 혼합되지 않고, 유전체 물질에 대하여 양호한 접착성을 제공하며, 낮은 전기 저항성을 제공할 수 있는 물질을 포함할 수 있다.

집적 회로의 상호접속에서의 전류 밀도는 연이은 기술 노드마다 크게 증가한다. 전자 이동(EM) 및 응력 이동(SM)의 수명은 전류 밀도에 반비례하기 때문에, EM 및 SM은 중대한 과제로 빠르게 부상하였다. Cu 이중 다마신 상호접속 구조에서의 EM 수명은, 벌크 Cu 금속과 주변 물질(예컨대 캡핑 층)의 계면에서의 원자 Cu의 이동에 강하게 의존하며, 이 원자 Cu의 이동은 상기 계면에서의 접착성과 직접 연관되어 있다. 보다 나은 접착성 및 EM 수명을 제공하는 새로운 캡핑 물질들이 광범위하게 연구되고 있다. 예를 들어, 코발트-텅스텐-인(CoWP)층이 무전해 도금 기술을 사용하여 벌크 Cu 금속에 선택적으로 증착되고 있다. CoWP와 벌크 Cu 금속의 계면은, EM 수명을 더 연장시키는 우수한 접착 강도를 갖는다. 그러나, 특히 Cu 배선의 피치가 타이트한 경우에, 벌크 Cu 금속에서 납득할만한 증착 선택성을 유지하는 것과, 양호한 막 균일성을 유지하는 것은, 이러한 복잡한 공정의 채용에 영향을 미친다. 또한, 산성 용액을 이용한 습식 공정 단계는 CoWP의 사용에 불이익을 줄 수 있다.

따라서, Cu에 대한 양호한 접착성 및 벌크 Cu 금속의 향상된 EM 및 SM 특성을 제공하는 금속층을 증착하기 위하여, 새로운 방법이 요구되고 있다. 구체적으로는, 이러한 방법들은 유전체 표면에 비해 금속 표면에의 금속 증착에 양호한 선택성을 제공해야 한다.

본 발명의 실시예는, Cu 금속 배선에서의 전자 이동 및 응력 이동을 향상시키도록, 선택적 저온 Ru 증착을 반도체 디바이스의 제조에 통합하는 방법을 제공한다. 본 발명의 일 실시예에 따르면, 패턴화된 기판이 하나 이상의 트렌치 및 하나 이상의 비아를 갖는 하나 이상의 이중 다마신 상호접속 구조를 포함한다.

본 발명의 일 실시예에 따르면, 상기 방법은, 유전체층에 오목한 피쳐를 갖는 패턴화된 기판으로서, 상기 오목한 피쳐에는 평탄화된 벌크 Cu 금속이 적어도 실질적으로 충전되어 있는 것인 패턴화된 기판을 마련하는 단계; 벌크 Cu 금속 및 유전체층을 H2, N2, 또는 NH3, 또는 이들의 조합의 존재 하에서 열처리하는 단계; 및 열처리된 상기 평탄화된 벌크 Cu 금속 상에 Ru 금속막을 선택적으로 증착하는 단계를 포함한다.

본 발명의 일 실시예에 따르면, 상기 방법은, 유전체층에 오목한 피쳐를 갖는 패턴화된 기판으로서, 상기 오목한 피쳐에는 평탄화된 벌크 Cu 금속이 적어도 실질적으로 충전되어 있는 것인 패턴화된 기판을 마련하는 단계; 벌크 Cu 금속 및 유전체층을 H2의 존재 하에서 기판 온도를 200℃ 미만으로 하여 열처리하는 단계; 및 상기 패턴화된 기판을 Ru3(CO)12 전구체 증기 및 CO 가스를 함유하는 공정 가스에 열화학 기상 증착 공정에서 노출시킴으로써, 열처리된 상기 평탄화된 벌크 Cu 금속 상에 Ru 금속막을 선택적으로 증착하는 단계를 포함한다.

본 발명의 일 실시예에 따르면, 상기 방법은, 유전체층에 오목한 피쳐를 갖는 패턴화된 기판으로서, 상기 오목한 피쳐에는 평탄화된 벌크 Cu 금속이 적어도 실질적으로 충전되어 있는 것인 패턴화된 기판을 마련하는 단계; 벌크 Cu 금속 및 유전체층을 N2, NH3, 또는 이들의 조합의 존재 하에서 기판 온도를200℃ 미만으로 하여 열처리하는 단계; 및 상기 패턴화된 기판을 Ru3(CO)12 전구체 증기 및 CO 가스를 함유하는 공정 가스에 열화학 기상 증착 공정에서 노출시킴으로써, 열처리된 상기 평탄화된 벌크 Cu 금속 상에 Ru 금속막을 선택적으로 증착하는 단계를 포함한다.

본 발명과 이에 수반되는 많은 장점은 이하의 상세한 설명을, 특히 첨부 도면과 함께 고려하면서 참조하면, 쉽게 더 명확히 이해될 것이다.

본 발명에 따르면, 벌크 Cu 금속에서의 전자 이동 및 응력 이동을 향상시킬 수 있는, 선택적 저온 Ru 금속 증착을 반도체 디바이스의 제조에 통합하는 방법이 제공된다.

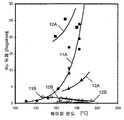

도 1a는 본 발명의 실시예에 따라 Cu 금속 및 저유전상수(low-k) 물질을 포함하는 웨이퍼 상에 증착된 Ru 금속막의 두께를 웨이퍼 온도 및 공정 압력의 함수로 나타낸 것이다.

도 1b는 본 발명의 실시예에 따라 저유전상수 물질 상에 증착된 Ru 금속막의 두께를 웨이퍼 온도 및 전처리 조건의 함수로 나타낸 것이다.

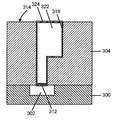

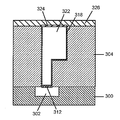

도 2a 내지 도 2c는 본 발명의 실시예에 따라 이중 다마신 상호접속 구조에 선택적으로 증착된 Ru 금속막을 통합하는 것을 개략적으로 보여주는 단면도이다.

도 3은 본 발명의 실시예에 따라 Ru 금속막을 증착하는 열화학 기상 증착(TCVD) 시스템을 개략적으로 나타낸 것이다.

도 4는 본 발명의 다른 실시예에 따라 Ru 금속막을 증착하는 다른 TCVD 시스템을 개략적으로 나타낸 것이다.

도 1b는 본 발명의 실시예에 따라 저유전상수 물질 상에 증착된 Ru 금속막의 두께를 웨이퍼 온도 및 전처리 조건의 함수로 나타낸 것이다.

도 2a 내지 도 2c는 본 발명의 실시예에 따라 이중 다마신 상호접속 구조에 선택적으로 증착된 Ru 금속막을 통합하는 것을 개략적으로 보여주는 단면도이다.

도 3은 본 발명의 실시예에 따라 Ru 금속막을 증착하는 열화학 기상 증착(TCVD) 시스템을 개략적으로 나타낸 것이다.

도 4는 본 발명의 다른 실시예에 따라 Ru 금속막을 증착하는 다른 TCVD 시스템을 개략적으로 나타낸 것이다.

본 발명의 실시예는, Cu 금속 배선에서의 전자 이동(EM) 및 응력 이동(SM)을 향상시키도록, 선택적 저온 Ru 금속 증착을 반도체 디바이스의 제조에 통합하는 방법을 제공한다. Ru 금속막은 Cu 금속 배선의 EM 및 SM 특성을 향상시키도록, 상호접속 구조에서 금속 배선층 및 벌크 Cu 금속과 접촉하는 접착층으로서 이용될 수 있다. 당업자는, 다양한 실시예가 하나 이상의 특정한 세부 사항을 갖지 않고서 실시될 수도 있고, 또는 다른 대체물 및/또는 추가적인 방법, 물질, 또는 구성 요소를 갖고서 실시될 수도 있다는 것을 인지할 것이다. 다른 경우에는, 본 발명의 다양한 실시예의 양태가 모호해지는 것을 피하기 위해, 공지의 구조, 재료, 또는 작업은 상세히 도시 혹은 설명되어 있지 않다. 이와 마찬가지로, 본 발명을 완전하게 이해시키기 위해, 구체적인 수, 재료 및 구성이 설명을 목적으로 기재되어 있다. 또한, 도면에 도시된 다양한 실시예는 실례가 되는 것을 나타낸 것이고, 일정한 축척으로 도시될 필요가 없는 것으로 이해된다.

본 명세서의 전반의 어구 "일 실시예" 또는 "실시예"는, 실시예와 연계되어 설명되는 개개의 피쳐, 구조, 재료, 또는 특징이 본 발명의 적어도 하나의 실시예에 포함된다는 것을 의미하지만, 이들이 모든 실시예에 존재한다는 것을 의미하지는 않는다. 따라서, 본 명세서의 전반의 여러 곳에 나타나 있는 어구 "일 실시예에서" 또는 "실시예에서"는, 본 발명의 동일한 실시예를 거론하는 것은 아니다.

도 1a는 본 발명의 실시예에 따라 Cu 금속 및 Si 함유 저유전상수 물질을 포함하는 웨이퍼 상에 증착된 Ru 금속막의 두께(Å, (10-10m))를 웨이퍼 온도(섭씨, ℃) 및 Ru 금속막 증착용 공정 챔버의 공정 압력의 함수로 나타낸 것이다. Cu 금속 또는 저유전상수 물질(k=2.4)을 포함하는 웨이퍼는, Ru 금속 증착 이전에, H2가스 속에서 3 Torr의 공정 압력으로 1분 동안 열처리함으로써 전처리된다. 전처리 이후에, 기판은 기판 온도 약 115℃ 내지 210℃ 및 공정 압력 500 mTorr(밀리-Torr), 100 mTorr 및 15 mTorr의 조건에서, Ru3(CO)12 전구체 증기 및 CO 가스를 함유하는 공정 가스에 약 10초 동안 노출된다. 첫 번째 예에서, 트레이스(10A)(트레이스 데이터가 중실 사각형으로 표시됨)와 트레이스(10B)(트레이스 데이터가 중공 사각형으로 표시됨)는 각각, 공정 챔버의 공정 압력이 15 mTorr인 경우에서의 Cu 금속 및 저유전상수 물질 상의 Ru 금속 두께를 보여준다. 두 번째 예에서, 트레이스(11A)(트레이스 데이터가 중실원으로 표시됨)와 트레이스(11B)(트레이스 데이터가 중공원으로 표시됨)는 각각, 공정 압력이 100 mTorr인 경우에서의 Cu 금속 및 저유전상수 물질 상의 Ru 두께를 보여준다. 세 번째 예에서, 트레이스(12A)(트레이스 데이터가 중실 삼각형으로 표시됨)와 트레이스(12B)(트레이스 데이터가 중공 삼각형으로 표시됨)는 각각, 공정 압력이 500 mTorr인 경우에서의 Cu 금속 및 저유전상수 물질 상의 Ru 두께를 보여준다. 도 1a는 저유전상수 물질의 바로 위에서가 아니라, Cu 금속의 바로 위에서의 Ru 금속의 초기 증착이, 약 150℃보다 높은 웨이퍼 온도에 대해 매우 선택적이라는 것과, 선택성이 공정 압력의 감소에 따라 증가된다는 것을 보여준다. 이러한 높은 선택성은 Cu 및 다른 금속 상에 초박막(수 Å의 두께) Ru 금속막을 증착하는 데 이용될 수 있다.

도 1b는 본 발명의 실시예에 따라 저유전상수 물질(k=2.4) 상에 증착된 Ru 금속막의 두께를 웨이퍼 온도 및 전처리 조건의 함수로 나타낸 것이다. 기판은 Ru 금속 증착 이전에, 플라즈마 노출을 이용하면서 혹은 플라즈마 노출을 이용하지 않고서 H2가스 속에서 3 Torr의 공정 압력으로 1분 동안 열처리함으로써 전처리된다. 상기 전처리는, "에칭, 애싱 및 성막용 플라즈마 처리 장치(Plasma processing apparatus for etching, ashing, and film- formation)"란 제목의 미국 특허 제5,024,716호에 기술된 바와 같이 슬롯을 갖는 평면 안테나(SPA)를 포함한 플라즈마 처리 챔버에서 수행되며, 이 특허의 내용은 그 전체가 본원에 참조로 인용되어 있다.

상기 전처리 이후에, Ru 금속막은 Ru3(CO)12 전구체 증기 및 CO 가스를 함유하는 공정 가스와 100 mTorr의 공정 압력을 이용하여 증착된다. 트레이스(20A)(트레이스 데이터가 중공 마름모로 표시됨)는 플라즈마 여기된 H2가스로 전처리된 기판 상의 Ru막 두께를 보여주고, 트레이스(20B)(도 1a의 트레이스(10A)와 동일; 트레이스 데이터가 중공원으로 표시됨)는 플라즈마 여기하지 않은 H2가스로 전처리된 기판 상의 Ru막 두께를 보여준다. 도 1b는 플라즈마 여기된 H2가스로 저유전상수 물질을 전처리하면, 플라즈마 여기하지 않은 H2가스로 전처리된 기판에 비해 초기 Ru 금속막 증착율이 크게 증가된다는 것을 보여준다. 본 발명자들은, 플라즈마 여기된 H2가스로 전처리하면 저유전상수 물질의 노출면이 활성화되어, 이 활성화된 저유전상수 물질 상에 Ru 금속을 증착하기 위한 배양 시간이 줄어들고, 서로 다른 물질 상에서의 Ru 금속 증착의 선택성이 줄어든다고 고려한다.

Ru3(CO)12 전구체 증기가 웨이퍼(기판) 표면 상에 흡착되면, Ru3(CO)12 전구체가 표면 상에 흡착된 Ru3(CO)x 및 CO 종으로 부분적으로 분해되게 되고, 뒤이어 흡착된 Ru3(CO)x가 Ru 금속 및 기판으로부터 탈착되는 CO로 더 분해되는 것으로 고려된다.

Ru3(CO)12(g)⇔Ru3(CO)x(ad)+(12-x)CO(ad)⇒3Ru(s)+(12-x)CO(g) (1)

이론에 의해 한정되기를 바라지는 않지만, 본 발명자들은 Cu 또는 텅스텐(W)과 같은 금속 표면에서 Ru 금속의 선택적인 증착이 관찰되는 것이, 금속 표면에 비해 유전체 표면에서 흡착된 CO의 농도가 높은 것에 적어도 부분적으로 기인한다고 고려하며, 이에 따라 흡착된 CO가 Ru3(CO)x와 재결합하여 상기 식 (1)의 Ru3(CO)12가 유전체 표면 상에 재형성되는 것을 선호한다. 금속 표면에서 흡착된 CO의 농도가 낮을수록, 흡착된 Ru3(CO)x가 Ru 금속 및 CO로 유전체 표면에 비해 더 높은 비율로 분해된다.

본 발명의 실시예는, 패턴화된 기판의 전처리된 금속 표면(예컨대, Cu 금속)에 Ru 금속막을 매우 선택적으로 저온 증착하는 시스템 및 방법을 제공한다. 상기 패턴화된 기판은 종횡비가 큰 오목한 피쳐를 포함할 수 있다. 본 발명의 일 실시예에 따르면, 이중 다마신 상호접속 구조는 패턴화된 기판에 형성된 트렌치 및 비아를 포함하는데, 상기 트렌치 및 비아는 측벽과 바닥을 포함한다. 비아는 대략 2:1 이상의 종횡비(깊이/폭)를 가질 수 있으며, 예를 들어 3:1, 4:1, 5:1, 6:1, 12:1, 15:1, 또는 그 이상의 종횡비를 가질 수 있다. 비아는 대략 200 nm 이하의 폭을 가질 수 있으며, 예를 들어 150 nm, 100 nm, 65 nm, 45 nm, 32 nm, 20 nm, 또는 그 이하의 폭을 가질 수 있다. 그러나, 본 발명의 실시예는 이러한 종횡비 또는 비아 폭에 한정되지는 않으며, 다른 종횡비 또는 비아 폭이 사용될 수도 있다.

도 2a는 본 발명의 실시예에 따른 이중 다마신 상호접속 구조를 개략적으로 보여주는 단면도이다. 이중 다마신 상호접속 구조에는 평탄화된 벌크 Cu 금속(322)이 충전되어 있는데, 이 평탄화된 벌크 Cu 금속은 이중 다마신 상호접속 구조에 벌크 Cu 금속을 충전하고 평탄화 공정, 예컨대 화학 기계 연마(CMP) 공정을 이용하여 잉여 Cu 금속을 제거함으로써 형성될 수 있다. 또한, 도 2a에 개략적으로 도시된 바와 같이, 평탄화 공정에서 배리어층(318)이 필드 표면(314)으로부터 제거된다. 벌크 Cu 금속 증착 공정은 회로 제조 분야의 당업자에게 잘 알려져 있으며, 예를 들어 전기화학적 도금 공정 또는 무전해 도금 공정을 포함한다. 또한, CMP 공정은 당업자에게 잘 알려져 있다.

도 2a에서, 배리어층(318)은, 예를 들어 Ta 함유층(예컨대, Ta, TaC, TaN, 또는 TaCN, 또는 이들의 조합), Ti 함유층(예컨대, Ti, TiN, 또는 이들의 조합), 또는 W 함유층(예컨대, W, WN, 또는 이들의 조합)을 포함할 수 있다. 한 예에서, 배리어층(318)은 터티아리 아밀 이미도-트리스-디메틸아미도 탄탈룸(Ta(NC(CH3)2C2H5)(N(CH3)2)3) 및 H2에 교대로 노출시키는 것을 이용하여 플라스마 강화 원자층 증착(PEALD) 시스템에서 증착된 TaCN을 포함할 수 있다.

도 2a에서, 이중 다마신 상호접속 구조는 유전체층(300)에 제1 금속 배선층(302)(예컨대, Cu 또는 W)을 더 포함한다. 유전체층(300)은, 예컨대 SiO2, 플루오르화 실리콘 글래스(FSG)와 같은 저유전상수 물질, 탄소가 도핑된 산화물, 폴리머, SiCOH 함유 저유전상수 물질, 비다공질 저유전상수 물질, 다공질 저유전상수 물질, CVD 저유전상수 물질, 스핀온 유전체(SOD) 저유전상수 물질, 또는 임의의 다른 적합한 유전체 물질을 포함할 수 있다. 이중 다마신 상호접속 구조는 유전체층(304)에 에칭된 트렌치 및 비아를 포함한다. 유전체층(304)은 이중 다마신 상호접속 구조 주위에 "필드(field)" 표면(314) 영역을 포함한다. 도시되어 있지는 않지만, 상호접속 구조는, 예를 들어 유전체층(300)과 유전체층(304) 사이에 트렌치 에칭 정지층 및 비아 에칭 정지층과, 제1 금속 배선층(302)을 유전체층(300)으로부터 분리시키는 배리어층 등의 추가적인 층들을 포함할 수 있다. 이중 다마신 상호접속 구조는 당업자에게 알려진 표준 리소그래피 및 에칭 방법을 이용하여 형성될 수 있다. 또한, 본 발명의 실시예는 더 간단하거나 더 복잡한 이중 다마신 상호접속 구조 및 금속 배선층을 포함하는 다른 종류의 오목한 피쳐에도 적용될 수 있는 것으로 이해될 것이다.

도 2a는 제1 금속 배선층(302)에 선택적으로 증착된 선택적 금속막(312)(예컨대, Ru 금속막)을 더 보여준다. 본 발명의 일 실시예에 따르면, 벌크 Cu 금속 충전 이전에, Ru막(도시 생략)이 배리어층(318)에 등각적으로 증착될 수 있다.

본 발명자들은, 평탄화되어 있는 패턴화된 기판의 이후의 처리(예컨대, 선택적 금속 증착)에 있어서, 평탄화 공정에 사용된 부식성 공정 환경으로 인하여, 평탄화 공정, 예컨대 CMP 등이 문제를 야기할 수 있다는 것을 알게 되었다. 본 발명의 실시예에 따르면, 이러한 문제는 평탄화되어 있는 패턴화된 기판을 수소(H2), 질소(N2), 또는 암모니아(NH3), 또는 이들의 조합의 존재 하에서 열처리하는 것을 통해 최소화되거나 또는 없어질 수 있다.

본 발명의 일 실시예에 따르면, 도 2a의 이중 다마신 상호접속 구조를 형성한 이후에, 유전체층(304)의 필드 표면(314) 및 평탄화된 벌크 Cu 금속(322)이 H2, N2, 또는 NH3, 또는 이들의 조합의 존재 하에서 열처리된다. 열처리는 기판 온도를 200℃ 미만으로 하여 수행될 수 있고, 아르곤(Ar) 등과 같은 희가스를 더 포함할 수 있다. 별법으로서, 열처리는 기판 온도를 200℃ 내지 400℃로 하여 수행될 수 있다. 한 예에서는, 순수 H2, 순수 N2, 또는 순수 NH3가 사용될 수 있다. 다른 예에서, H2, N2, 또는 NH3, 또는 이들의 조합은 아르곤(Ar) 등과 같은 희가스를 더 포함할 수 있다. 한 예에서는, 10:1의 H2/Ar 혼합물이 사용될 수 있다.

본 발명의 다른 실시예에 따르면, 열처리는 H2의 존재 하에서 기판 온도를 200℃ 미만으로 하여 수행될 수 있다. 한 예에서는, 순수 H2 가 사용될 수 있다. 다른 예에서는, H2와 Ar의 혼합물이 사용될 수 있다.

본 발명의 또 다른 실시예에 따르면, 열처리는 N2 또는 NH3, 또는 이들의 조합의 존재 하에서 기판 온도를200℃ 미만으로 하여 수행될 수 있다. 한 예에서는, 순수 N2 또는 순수 NH3가 사용될 수 있다. 다른 예에서는, N2와 Ar의 혼합물, NH3와 Ar의 혼합물, 또는 N2, NH3 및Ar의 혼합물이 사용될 수 있다.

열처리 이후에는, 도 2b에 도시된 바와 같이, 열처리되어 있는 평탄화된 벌크 Cu 금속(322) 상에 Ru 금속막(324)을 선택적으로 증착한다. Ru 금속막(324)은 기판 온도를 100℃ 내지 300℃로 하여 증착될 수 있다. 본 발명의 일 실시예에 따르면, 열처리 및 Ru 금속막 증착은 모두는 기판 온도를 200℃ 미만으로 하여 수행될 수 있다. Ru 금속막(324)은 Ru3(CO)12 전구체 증기 및 CO 가스를 포함하는 공정 가스를 이용한 TCVD 공정에서 증착될 수 있다. 일 실시예에서, Ru 금속막(324)의 평균 두께는 2 내지 20Å이거나, 5 내지 15Å, 예를 들어 대략 10Å일 수 있다. 일 실시예에서, Ru 금속막(324)의 평균 두께는 10Å미만일 수 있다. 일 실시예에 따르면, 평탄화된 벌크 Cu 금속(322)에의 Ru 금속막(324)의 표면 피복은, 평탄화된 벌크 Cu 금속(322)을 노출시키는 간극으로 인해 불완전하다. 본 발명의 일 실시예에 따르면, 열처리 및 Ru 금속막 증착은 동일한 공정 챔버에서 수행될 수 있다. 별법으로서, 열처리 및 Ru 금속막 증착은 서로 다른 공정 챔버에서 수행될 수 있다.

평탄화된 벌크 Cu 금속(322) 상에 Ru 금속막(324)을 선택적으로 증착한 후에, 도 2b에 도시된 부분적으로 제조된 반도체 디바이스를 더 처리한다. 도 2c는 Ru 금속막(324) 및 유전체층(304) 상에 증착된 등각 캡층(326)을 보여준다. 캡층(326)은 예컨대 질화규소 또는 질화탄소규소를 포함할 수 있다. 다른 예에서, 캡층(326)은 예컨대 CuSiN, WN, TiN, 또는 CoN 등의 질화금속을 포함할 수 있다. 본 발명의 일 실시예에 따르면, 캡층(326)의 증착 이전에, Ru 금속막과 유전체층은 H2, N2, 또는 NH3, 또는 이들의 조합의 존재 하에서 기판 온도를 150℃ 내지 400℃로 하여 열처리될 수 있다.

도 3은 본 발명의 실시예에 따라, Ru3(CO)12 전구체 증기 및 CO 가스로부터 Ru 금속막을 증착하는 열화학 기상 증착(TCVD) 시스템을 개략적으로 보여준다. 증착 시스템(1)은, Ru 금속막이 위에 형성되는 패턴화된 기판(25)을 지지하도록 되어 있는 기판 홀더(20)를 구비한 공정 챔버(10)를 포함한다. 공정 챔버(10)는 증기 전구체 전달 시스템(40)을 통하여 금속 전구체 기화 시스템(50)에 연결된다.

공정 챔버(10)는 또한 덕트(36)를 통해 진공 펌핑 시스템(38)에 연결되고, 진공 펌핑 시스템(38)은, 패턴화된 기판(25) 상에 Ru 금속막을 형성하기에 적합하고 금속 전구체 기화 시스템(50) 내에서 Ru3(CO)12 전구체(52)가 기화하기에 적합한 압력에 이르기까지, 공정 챔버(10), 증기 전구체 전달 시스템(40) 및 금속 전구체 기화 시스템(50)을 배기하도록 되어 있다.

도 3을 계속 참조해 보면, 금속 전구체 기화 시스템(50)은, Ru3(CO)12 전구체(52)를 저장하고, Ru3(CO)12 전구체(52)를 기화시키기에 충분한 온도까지 Ru3(CO)12 전구체(52)를 가열하며, Ru3(CO)12 전구체 증기를 증기 전구체 전달 시스템(40)에 도입시키도록 되어 있다. Ru3(CO)12 전구체(52)는 금속 전구체 기화 시스템(50)의 선택된 가열 조건 하에서 고체이다. 고체 Ru3(CO)12 전구체(52)를 승화시키기 위한 바람직한 온도를 달성하기 위해, 금속 전구체 기화 시스템(50)은 기화 온도를 제어하도록 구성된 기화 온도 제어 시스템(54)에 연결되어 있다.

예를 들어, Ru3(CO)12 전구체(52)의 온도는 대략 40℃ 내지 대략 150℃로 상승될 수 있다. 별법으로서, 기화 온도는 대략 60℃ 내지 대략 90℃로 유지될 수 있다. Ru3(CO)12 전구체(52)가 승화를 일으키도록 가열됨에 따라, Ru3(CO)12 전구체의 증기가 형성되는 경우, 이를 포집하도록 Ru3(CO)12 전구체(52)의 위 또는 사이로 CO 함유 가스가 지나간다. CO 함유 가스는 CO를 포함하고, 선택적으로 N2와 같은 불활성 캐리어 가스, 희가스(즉, He, Ne, Ar, Kr, 또는 Xe), 또는 이들의 조합을 포함한다. CO 가스의 존재 하에서 Ru3(CO)12 전구체를 기화하면, 패턴화된 기판으로의 Ru3(CO)12 전구체 증기의 전달이 제한되는 문제점을 줄일 수 있다. Ru3(CO)12 전구체 증기가 형성되고 있을 때 Ru3(CO)12 전구체의 증기에 CO 가스를 부가하면, 기화 온도를 상승시킬 수 있게 되는 것으로 나타나 있다. 상승된 온도는 Ru3(CO)12 전구체의 증기압을 증가시키며, 그 결과 Ru3(CO)12 전구체의 공정 챔버로의 전달이 증가되고, 이에 따라 패턴화된 기판(25) 상에의 Ru 금속막의 증착율이 증가된다. Ru3(CO)12 전구체를 공정 챔버(10)에 전달하기 이전에, 증기 전구체 전달 시스템(40)에서 Ru3(CO)12 전구체가 조기에 분해되는 것을 줄이도록 CO 가스를 사용하는 것은, Ru 금속막을 증착하기 위한 Ru3(CO)12 전구체의 증기의 공정 챔버로의 효과적인 이동을 촉진하는 것으로 나타나 있는데, 이는 2004년 11월 23일에 출원되고 발명의 명칭이 "금속 카르보닐 전구체로부터의 금속층의 증착율을 증가시키는 방법(Method for Increasing Deposition Rates of Metal Layers from Metal-carbonyl Precursors)"인 미국 특허 출원 제10/996,145에 기술되어 있으며, 이 특허의 전체 내용은 본원에 참조로 인용되어 있다.

한 예에서, 금속 전구체 기화 시스템(50)은 Ru3(CO)12 증기의 효과적인 기화 및 전달을 위해 구성된 멀티 트레이(multi-tray) 기화 시스템일 수 있다. 예시적인 멀티 트레이 기화 시스템이, 2004년 11월 29일에 출원되고 발명의 명칭이 "멀티 트레이 막 전구체 기화 시스템 및 이를 포함하는 박막 증착 시스템(Multi-Tray Film Precursor Evaporation System and Thin Film Deposition System)"인 미국 특허 출원 제10/998,420호에 기술되어 있다.

예를 들어, 가스 공급 시스템(60)이 금속 전구체 기화 시스템(50)에 연결되고, 예컨대 Ru3(CO)12 전구체(52)의 아래에 피드 라인(61)을 통해, 또는 Ru3(CO)12 전구체(52)의 위에 피드 라인(62)을 통해, CO, 캐리어 가스, 또는 이들의 혼합물을 공급하도록 구성되어 있다. 또한, 가스 공급 시스템(60)은 금속 전구체 기화 시스템(50)의 하류에서 증기 전구체 전달 시스템(40)에 연결되어, Ru3(CO)12 전구체(52) 증기가 증기 전구체 전달 시스템(40)에 들어갈 때 또는 그 이후에 피드 라인(63)을 통해 Ru3(CO)12 전구체(52)의 증기에 가스를 공급한다. 또한, 피드 라인(63)은, 패턴화된 기판(25)을 Ru3(CO)12 전구체 증기 및 CO 가스에 노출시키기 전에, 패턴화된 기판(25)의 노출면을 흡착된 CO로 포화시키도록, 패턴화된 기판(25)을 CO 가스를 포함하는 전처리 가스로 전처리하는 데에 이용될 수 있다.

도시되어 있지는 않지만, 가스 공급 시스템(60)은 캐리어 가스 공급원, CO 가스 공급원, 하나 이상의 제어 밸브, 하나 이상이 필터 및 질량 유량 제어기를 포함할 수 있다. 예를 들어, CO 함유 가스의 유량은 약 0.1 sccm 내지 약 1000 sccm일 수 있다. 별법으로서, CO 함유 가스의 유량은 약 10 sccm 내지 약 500 sccm일 수 있다. 또 다른 별법으로서, CO 함유 가스의 유량은 약 50 sccm 내지 약 200 sccm일 수 있다. 본 발명의 실시예에 따르면, CO 함유 가스의 유량은 약 0.1 sccm 내지 약 1000 sccm의 범위일 수 있다. 별법으로서, CO 함유 가스의 유량은 약 1 sccm 내지 약 500 sccm일 수 있다.

금속 전구체 기화 시스템(50)의 하류에서, Ru3(CO)12 전구체 증기 및 CO 가스를 포함하는 공정 가스는, 공정 챔버(10)에 연결된 증기 분배 시스템(30)을 경유해 공정 챔버(10)에 들어갈 때까지, 증기 전구체 전달 시스템(40)을 통해 유동한다. 증기 전구체 전달 시스템(40)은, 증기 라인 온도를 제어하여 Ru3(CO)12 전구체 증기의 분해 및 Ru3(CO)12 전구체 증기의 응결을 방지하기 위해, 증기 라인 온도 제어 시스템(42)에 연결될 수 있다. 증기 전구체 전달 시스템(40)은, 예를 들어 50℃ 내지 100℃의 온도로 유지될 수 있다.

도 3을 계속 참조해 보면, 공정 챔버(10)의 일부분을 형성하며 공정 챔버에 연결되는 증기 분배 시스템(30)은, 증기가 증기 분배판(34)을 통과하여 패턴화된 기판(25) 상의 처리 영역(33)에 진입하기에 앞서, 증기를 분산시키는 증기 분배 플레넘(32)을 포함한다. 또한, 증기 분배판(34)은 증기 분배판(34)의 온도를 제어하도록 구성된 분배판 온도 제어 시스템(35)에 연결될 수 있다.

Ru3(CO)12 전구체 증기 및 CO 가스를 포함하는 공정 가스가 일단 공정 챔버(10)의 처리 영역(33)에 진입하면, Ru3(CO)12 전구체 증기는 패턴화된 기판(25)의 높은 온도로 인해 기판 표면에 흡착되자마자 열 분해되며, 패턴화된 기판(25) 상에는 Ru 금속막이 형성된다. 기판 홀더(20)가 기판 온도 제어 시스템(22)에 연결되어 있기 때문에, 기판 홀더(20)는 패턴화된 기판(25)의 온도를 상승시키도록 구성된다. 예를 들어, 기판 온도 제어 시스템(22)은 패턴화된 기판(25)의 온도를 약 500℃에 이르기까지 상승시키도록 구성될 수 있다. 또한, 공정 챔버(10)는 챔버 벽의 온도를 제어하도록 구성된 챔버 온도 제어 시스템(12)에 연결될 수 있다.

도 3을 계속 참조해 보면, 증착 시스템(1)은 증착 시스템(1)의 동작을 작동 및 제어하도록 구성된 제어 시스템(80)을 더 포함할 수 있다. 제어 시스템(80)은 공정 챔버(10), 기판 홀더(20), 기판 온도 제어 시스템(22), 챔버 온도 제어 시스템(12), 증기 분배 시스템(30), 증기 전구체 전달 시스템(40), 금속 전구체 기화 시스템(50) 및 가스 공급 시스템(60)에 연결되어 있다.

도 4는 본 발명의 실시예에 따라 Ru3(CO)12 전구체 증기 및 CO 가스로부터 Ru 금속막을 증착하는 다른 TCVD 시스템을 개략적으로 보여준다. 증착 시스템(100)은, Ru 금속막이 위에 형성되는 패턴화된 기판(125)을 지지하도록 구성된 기판 홀더(120)를 구비한 공정 챔버(110)를 포함한다. 공정 챔버(110)는, Ru3(CO)12 전구체(152)를 저장 및 기화하도록 구성된 금속 전구체 기화 시스템(150)과, Ru3(CO)12 전구체(152)의 증기를 공정 챔버(110)로 이송하도록 구성된 증기 전구체 전달 시스템(140)을 구비한 전구체 전달 시스템(105)에 연결될 수 있다.

공정 챔버(110)는 상측 챔버 섹션(111), 하측 챔버 섹션(112) 및 배기 챔버(113)를 포함한다. 하측 챔버 섹션(112) 내에는 개구(114)가 형성되며, 이 개구에서 하측 챔버 섹션(112)이 배기 챔버(113)와 연결된다.

도 4를 계속 참조해 보면, 기판 홀더(120)는 처리 대상인 패턴화된 기판(또는 웨이퍼)(125)을 지지하는 수평면을 제공한다. 기판 홀더(120)는 배기 챔버(113)의 하부로부터 상향 연장되는 실린더형 지지 부재(122)에 의해 지지될 수 있다. 또한, 기판 홀더(120)는 기판 홀더 온도 제어 시스템(128)에 연결된 히터(126)를 포함한다. 히터(126)는, 예를 들어 하나 이상의 저항 가열 요소를 포함할 수 있다. 별법으로서, 히터(126)는 예를 들어 텅스텐-할로겐 램프와 같은 방사 가열 시스템을 포함할 수 있다. 기판 홀더 온도 제어 시스템(128)은, 하나 이상의 가열 요소에 전력을 제공하기 위한 전력 공급원과, 기판의 온도 혹은 기판 홀더의 온도, 또는 양자 모두를 측정하기 위한 하나 이상의 온도 센서, 그리고 패턴화된 기판(125) 또는 기판 홀더(120)의 온도의 모니터링, 조정, 또는 제어 중 적어도 하나를 수행하도록 구성된 제어기를 포함할 수 있다.

처리 동안에, 가열된 패턴화된 기판(125)은 Ru3(CO)12 전구체 증기를 열 분해시킬 수 있으며, Ru 금속막의 패턴화된 기판(125) 상에의 증착을 가능하게 한다. 기판 홀더(120)는 소기의 Ru 금속막을 패턴화된 기판(125) 상에 증착하기에 적합한 소정의 온도에 이르기까지 가열된다. 또한, 챔버 온도 제어 시스템(121)에 연결된 히터(도시 생략)는, 챔버 벽을 소정의 온도에 이르기까지 가열하도록 공정 챔버(110)의 벽에 매설될 수 있다. 히터는 공정 챔버(110)의 벽의 온도를 약 40℃ 내지 약 150℃, 또는 약 40℃ 내지 약 80℃로 유지시킬 수 있다. 압력계(도시 생략)는 공정 챔버의 압력을 측정하는 데 사용된다. 본 발명의 실시예에 따르면, 공정 챔버의 압력은 약 1 mTorr 내지 약 500 mTorr일 수 있다. 별법으로서, 공정 챔버의 압력은 약 10 mTorr 내지 약 100 mTorr일 수 있다.

또한 도 4에 도시된 바와 같이, 증기 분배 시스템(130)이 공정 챔버(110)의 상측 챔버 섹션(111)에 연결되어 있다. 증기 분배 시스템(130)은, 전구체 증기를 하나 이상의 오리피스(134)를 통하여 증기 분배 플레넘(132)으로부터 상기 패턴화된 기판(125) 상의 처리 영역(133)으로 도입시키도록 구성된 증기 분배판(131)을 포함한다.

또한, 상측 챔버 섹션(111)에는, Ru3(CO)12 전구체의 증기 및 CO 가스를 포함하는 공정 가스를 증기 전구체 전달 시스템(140)으로부터 증기 분배 플레넘(132)으로 도입시키기 위한 개구(135)가 마련되어 있다. 또한, 냉각 또는 가열된 유체를 유동시키도록 구성된 동심형 유체 채널과 같은 온도 제어 요소(136)가, 증기 분배 시스템(130)의 온도를 제어하기 위해 마련되고, 이에 따라 Ru3(CO)12 전구체 증기가 증기 분배 시스템(130) 내에서 분해 또는 응결되는 것이 방지된다. 예를 들어, 물과 같은 유체가 증기 분배 온도 제어 시스템(138)으로부터 상기 유체 채널에 공급될 수 있다. 증기 분배 온도 제어 시스템(138)은, 유체 공급원과, 열 교환기와, 유체 온도 혹은 증기 분배판의 온도, 또는 양자 모두를 측정하기 위한 하나 이상의 온도 센서, 그리고 증기 분배판(131)의 온도를 약 20℃ 내지 약 150℃로 제어하도록 구성된 제어기를 포함할 수 있다. 전구체가 증기 분배판(131) 상에 응결되는 것을 피하기 위해, Ru3(CO)12 전구체의 경우, 증기 분배판(131)의 온도는 약 65℃ 이상의 온도로 유지될 수 있다.

도 4에 도시된 바와 같이, 금속 전구체 기화 시스템(150)은, Ru3(CO)12 전구체(152)를 수용하고 Ru3(CO)12 전구체(152)의 온도를 상승시켜 Ru3(CO)12 전구체(152)를 기화시키도록 구성되어 있다. 본원에서, 용어 "기화", "승화" 및 "증발"은, 변화가 예를 들어 고체에서 액체를 거쳐 기체로의 변화인가, 고체에서 기체로의 변화인가, 또는 액체에서 기체로의 변화인가에는 상관없이, 고체 또는 액체 전구체로부터 증기(기체)가 일반적으로 형성되는 것을 지칭하는 데 호환적으로 사용될 수 있다. 전구체 히터(154), Ru3(CO)12 전구체(152)의 소기의 증기압을 발생시키는 온도로 Ru3(CO)12 전구체(152)를 유지시키도록 Ru3(CO)12 전구체(152)를 가열시키기 위해 마련된다. 전구체 히터(154)는 Ru3(CO)12 전구체(152)의 온도를 제어하도록 구성된 기화 온도 제어 시스템(156)에 연결되어 있다. 예를 들어, 전구체 히터(154)는 Ru3(CO)12 전구체(152)의 온도를 약 40℃ 내지 약 150℃로, 또는 약 60℃ 내지 약 90℃로 조정하도록 구성될 수 있다.

Ru3(CO)12 전구체(152)가 증발(또는 승화)을 일으키도록 가열됨에 따라, Ru3(CO)12 전구체 증기가 형성되면, 이를 포집하기 위해 CO 함유 가스가 Ru3(CO)12 전구체(152)의 위 또는 사이로 지나갈 수 있다. CO 함유 가스는 CO를 포함하고, 선택적으로 N2와 같은 불활성 캐리어 가스, 또는 희가스(즉, He, Ne, Ar, Kr, Xe)를 포함한다. 예를 들어, 가스 공급 시스템(160)이 금속 전구체 기화 시스템(150)에 연결되어 있고, 예컨대 Ru3(CO)12 전구체(152)의 위 또는 사이로 CO 가스를 유동시키도록 구성되어 있다. 도 4에 도시되어 있지는 않지만, 가스 공급 시스템(160)은 또한, 금속 전구체(152)의 증기가 증기 전구체 전달 시스템(140)에 들어갈 때 또는 그 이후에, CO 가스를 금속 전구체(152)의 증기에 공급하도록 증기 전구체 전달 시스템(140)에 연결될 수 있으며, 이에 따라, 예를 들어 패턴화된 기판(125)을 Ru3(CO)12 전구체 증기 및 CO 가스를 포함하는 공정 가스에 노출시키기에 앞서, CO 가스를 포함하는 전처리 가스로 상기 패턴화된 기판(125)을 전처리하여, 상기 패턴화된 기판(125)의 노출면을 흡착된 CO로 포화시킬 수 있다.

가스 공급 시스템(160)은, 불활성 캐리어 가스, CO 가스, 또는 이들의 혼합물을 포함하는 가스 공급원(161)과, 하나 이상의 제어 밸브(162)와, 하나 이상의 필터(164), 그리고 질량 유량 제어기(165)를 포함할 수 있다. 예를 들어, CO 함유 가스의 질량 유량은 약 0.1 sccm 내지 약 1000 sccm의 범위일 수 있다.

또한, 센서(166)가 금속 전구체 기화 시스템(150)으로부터의 총 가스 유량을 측정하기 위해 마련되어 있다. 센서(166)는, 예를 들어 질량 유량 제어기를 포함할 수 있고, 공정 챔버(110)에 전달되는 Ru3(CO)12 전구체 증기의 양은 센서(166) 및 질량 유량 제어기(165)를 이용하여 결정될 수 있다. 별법으로서, 센서(166)는 공정 챔버(110)로의 가스 흐름에서 Ru3(CO)12 전구체의 농도를 측정하는 흡광 센서를 포함할 수 있다.

바이패스 라인(167)이 센서(166)의 하류에 위치할 수 있고, 이 바이패스 라인은 증기 전구체 전달 시스템(140)을 배기 라인(116)에 접속시킬 수 있다. 바이패스 라인(167)은, 증기 전구체 전달 시스템(140)을 배기시키고, Ru3(CO)12 전구체 증기 및 CO 가스의 공정 챔버(110)로의 공급을 안정화하기 위해 마련되어 있다. 또한, 증기 전구체 전달 시스템(140)의 분기부의 하류에 위치한 바이패스 밸브(168)가 바이패스 라인(167) 상에 마련되어 있다.

도 4를 계속 참조해 보면, 증기 전구체 전달 시스템(140)은 제1 밸브(141) 및 제2 밸브(142)를 각각 구비한 고전도성 증기 라인을 포함한다. 또한, 증기 전구체 전달 시스템(140)은, 히터(도시 생략)를 통해 증기 전구체 전달 시스템(140)을 가열하도록 구성된 증기 라인 온도 제어 시스템(143)을 더 포함할 수 있다. 증기 라인의 온도는, Ru3(CO)12 전구체 증기가 증기 라인에서 응결되는 것을 막도록 제어될 수 있다. 증기 라인의 온도는 약 20℃ 내지 약 100℃ 또는 약 40℃ 내지 약 90℃로 제어될 수 있다.

또한, 가스 공급 시스템(190)으로부터 CO 가스가 공급될 수 있다. 예를 들어, 가스 공급 시스템(190)은 증기 전구체 전달 시스템(140)에 연결되어 있고, 이 가스 공급 시스템은, 예를 들어 증기 전구체 전달 시스템(140)에서, 예컨대 밸브(141)의 하류에서, CO 가스를 포함하는 전처리 가스로 상기 패턴화된 기판(125)을 전처리하도록, 또는 Ru3(CO)12 전구체 증기와 추가 CO 가스를 혼합하도록 구성되어 있다. 가스 공급 시스템(190)은 CO 가스 공급원(191)과, 하나 이상의 제어 밸브(192)와, 하나 이상의 필터(194), 그리고 질량 유량 제어기(195)를 포함할 수 있다. 예를 들어, CO 가스의 질량 유량은 약 0.1 sccm 내지 약 1000 sccm의 범위일 수 있다.

질량 유량 제어기(165 및 195)와 밸브(162, 192, 168, 141 및 142)는 제어기(196)에 의해 제어되고, 이 제어기는 불활성 캐리어 가스, CO 가스 및 Ru3(CO)12 전구체 증기의 공급, 차단 및 유동을 제어한다. 또한, 제어기(196)에는 센서(166)가 연결되어 있고, 센서(166)의 출력에 기초하여, 제어기(196)는 공정 챔버(110)로의 소기의 Ru3(CO)12 전구체 유동을 확보하도록, 질량 유량 제어기(165)를 통과하는 캐리어 가스의 유동을 제어할 수 있다.

도 4에 예시된 바와 같이, 배기 라인(116)은 배기 챔버(113)를 진공 펌핑 시스템(118)에 연결한다. 진공 펌프(119)는, 공정 챔버(110)를 소기의 진공도에 이르기까지 배기하는 데 사용되고, 처리 동안에는 공정 챔버(110)로부터 가스상 종을 제거하는 데 사용된다. 자동 압력 제어기(APC)(115) 및 트랩(117)이 진공 펌프(119)에 직렬로 연결되어 사용될 수 있다. 진공 펌프(119)는 펌핑 속도를 초당 500 리터(또는 그 이상)까지 올릴 수 있는 터보 분자 펌프(TMP)를 포함할 수 있다. 별법으로서, 진공 펌프(119)는 드라이 러핑 펌프(dry roughing pump)를 포함할 수 있다. 처리 동안에, 공정 가스는 공정 챔버(110)에 도입될 수 있고, 챔버 압력은 자동 압력 제어기(115)에 의해 조정될 수 있다. 자동 압력 제어기(115)는 나비형 밸브 또는 게이트 밸브를 포함할 수 있다. 트랩(117)은 미반응 Ru3(CO)12 전구체 물질 및 부산물을 공정 챔버(110)로부터 수집할 수 있다.

공정 챔버(110) 내의 기판 홀더(120)를 다시 살펴보면, 도 4에 도시된 바와 같이, 3개의 기판 리프트 핀(127)(두 개만 도시됨)이 패턴화된 기판(125)을 유지, 상승 및 하강시키기 위해 마련되어 있다. 기판 리프트 핀(127)은 플레이트(123)에 결합되어 있고, 기판 홀더(120)의 상면의 아래로 하강될 수 있다. 예를 들어 에어 실린더를 이용하는 구동 기구(129)가, 플레이트(123)를 상승 및 하강하는 수단을 제공한다. 패턴화된 기판(125)은, 게이트 밸브(200) 및 챔버 피드쓰루 통로(202)를 통해 로봇 이송 시스템(도시 생략)에 의하여 공정 챔버(110)의 안과 밖으로 이송될 수 있으며, 기판 리프트 핀(127)에 수취될 수 있다. 패턴화된 기판(125)을 일단 이송 시스템으로부터 수취하면, 기판 리프트 핀(127)을 하강시킴으로써 상기 패턴화된 기판을 기판 홀더(120)의 상면까지 하강시킬 수 있다.

도 4를 계속 참조해 보면, 증착 시스템 제어기(180)는 마이크로프로세서와, 메모리, 그리고 증착 시스템(100)의 입력을 통신 및 활성화할 뿐만 아니라 증착 시스템(100)의 출력을 모니터하기에 충분한 제어 전압을 발생시킬 수 있는 디지털 I/O 포트를 포함한다. 또한, 증착 시스템 제어기(180)는, 공정 챔버(110); 제어기(196)와, 증기 라인 온도 제어 시스템(143), 그리고 기화 온도 제어 시스템(156)을 포함하는 전구체 전달 시스템(105); 증기 분배 온도 제어 시스템(138); 진공 펌핑 시스템(118); 및 기판 홀더 온도 제어 시스템(128)에 연결되어 있고 정보를 교환한다. 진공 펌핑 시스템(118)에서, 제어기(180)는 공정 챔버(110)의 압력을 제어하기 위해 자동 압력 제어기(115)에 연결되어 있고 정보를 교환한다. 메모리에 저장된 프로그램은, 저장된 공정 레시피에 따라 전술한 증착 시스템(100)의 구성 요소를 제어하는 데 이용된다.

제어기(180)는, 메모리에 담긴 하나 이상의 명령의 하나 이상의 시퀀스를 실행하는 프로세서에 응답하여, 본 발명의 마이크로프로세서 기반 처리 단계의 일부 또는 전체를 수행하는 범용 컴퓨터 시스템으로 구현될 수 있다. 이러한 명령은, 하드 디스크 또는 착탈식 미디어 드라이브와 같은 다른 컴퓨터 판독 가능한 매체로부터 제어기의 메모리에 읽혀 들여질 수 있다. 멀티 프로세싱 장치의 하나 이상의 프로세서도 또한 메인 메모리에 담긴 명령의 시퀀스를 실행하는 제어기의 마이크로프로세서로서 채용될 수 있다. 다른 실시예에서, 하드웨어에 내장된 회로(hard-wired circuitry)가 소프트웨어 명령을 대신해 또는 소프트웨어 명령과 함께 사용될 수 있다. 따라서, 실시예는 하드웨어 회로와 소프트웨어의 임의의 특정한 조합에 한정되지 않는다.

제어기(180)는, 본 발명의 교시에 따라 프로그래밍된 명령을 담고, 데이터 구조, 테이블, 기록, 또는 본 발명을 구현하는 데 필요한 그 밖의 데이터를 담기 위한, 적어도 하나의 컴퓨터 판독 가능한 매체 또는 메모리, 예를 들어 제어기 메모리 등을 포함한다. 컴퓨터 판독 가능한 매체의 예로는 콤팩트 디스크, 하드 디스크, 플로피 디스크, 테이프, 광자기 디스크, PROMs(EPROM, EEPROM, flash EPROM), DRAM, SRAM, SDRAM, 또는 임의의 다른 자기 매체, 콤팩트 디스크 (예컨대, CD-ROM), 또는 임의의 다른 광학 매체, 펀치 카드, 페이퍼 테이프, 또는 구멍의 패턴을 갖는 그 밖의 물리적 매체, 반송파(후술함), 또는 컴퓨터가 판독할 수 있는 임의의 다른 매체가 있다.

본 발명은, 제어기(180)의 제어를 위한, 본 발명을 구현하는 디바이스(들)의 구동을 위한, 및/또는 제어기와 인간 사용자와의 상호작용을 가능하게 하기 위한 소프트웨어를 포함하며, 이 소프트웨어는 어느 하나의 컴퓨터 판독 가능한 매체 또는 컴퓨터 판독 가능한 매체의 조합에 저장된다. 이러한 소프트웨어는 디바이스 드라이버, 운영 시스템, 개발 툴 및 응용 소프트웨어를 포함할 수 있으나, 이에 한정되지는 않는다. 이러한 컴퓨터 판독 가능한 매체는, 본 발명의 구현시에 수행되는 처리의 일부(처리가 나뉘어진 경우) 또는 전체를 행하기 위한 본 발명의 컴퓨터 프로그램 제품을 더 포함할 수 있다.

본 발명의 컴퓨터 코드 디바이스는, 해석 가능하거나 실행 가능한 임의의 코드 메커니즘(스크립트를 포함하지만 이에 한정되지는 않음), 해석 가능한 프로그램, 동적 링크 라이브러리(DLLs), 자바 클래스 및 완전한 실행 프로그램일 수 있다. 또한, 본 발명의 처리의 일부는 더 나은 성능, 신뢰성, 및/또는 비용을 위해 나뉘어질 수 있다.

본원에 사용된 용어 "컴퓨터 판독 가능한 매체"는, 제어기(180)의 프로세서에 실행 명령을 제공하는 데에 참여하는 임의의 매체를 지칭한다. 컴퓨터 판독 가능한 매체는, 비휘발성 매체, 휘발성 매체 및 전송 매체(이에 한정되는 것은 아님)를 비롯한 많은 형식을 취할 수 있다. 비휘발성 매체는, 예를 들어 광학 디스크, 자기 디스크, 또는 하드 디스크나 착탈식 미디어 드라이브와 같은 광자기 디스크를 포함한다. 휘발성 매체는 메인 메모리와 같은 동적 메모리를 포함한다. 또한, 제어기의 프로세서에 하나 이상의 실행 명령의 하나 이상의 시퀀스를 수행시키는 데에, 다양한 형태의 컴퓨터 판독 가능한 매체가 관여할 수 있다. 예를 들어, 명령은 초기에는 원격 컴퓨터의 자기 디스크에 담겨있을 수 있다. 원격 컴퓨터는, 본 발명의 일부 또는 전체를 구현하기 위한 명령을 원격으로 동적 메모리에 로드하고, 상기 명령을 네트워크를 거쳐 제어기(180)에 송신할 수 있다.

제어기(180)는 증착 시스템(100)에 대해 가까이 위치할 수 있고, 또는 증착 시스템(100)에 대해 원거리에 위치할 수 있다. 예를 들어, 제어기(180)는 직접 접속, 인트라넷, 인터넷, 또는 무선 접속 중 적어도 하나를 이용하여 증착 시스템(100)과 데이터를 교환할 수 있다. 제어기(180)는, 예를 들어 고객 사이트(즉, 디바이스 생산 회사 등)에서 인트라넷에 연결될 수 있고, 또는 예를 들어 판매자 사이트(즉, 장비 제조자)에서 인트라넷에 연결될 수 있다. 또한, 제어기(180)는 예를 들어 인터넷에 연결될 수 있다. 또한, 다른 컴퓨터(즉, 제어기, 서버 등)가, 직접 접속, 인트라넷 및 인터넷 중 적어도 하나를 통하여 데이터를 교환하기 위해, 예를 들어 제어기(180)에 액세스할 수 있다. 또한, 당업자라면 이해하듯이, 제어기(180)는 증착 시스템(100)과 무선 접속을 통하여 데이터를 교환할 수 있다.

Cu 금속 배선에서의 전자 이동(EM) 및 응력 이동(SM)을 향상시키도록, 선택적 저온 Ru 증착을 반도체 디바이스의 제조에 통합하는 복수의 실시예가, 여러 실시예에 개시되어 있다. 본 발명의 실시예에 대한 이상의 설명은 예시 및 설명을 목적으로 주어진 것이다. 개시된 특정 형태에 본 발명을 한정하려는 의도는 전혀 없다. 명세서 및 이하의 청구범위는, 단지 설명의 목적으로 사용되고 있고 제한적인 것으로 해석되어서는 안 되는 용어를 포함한다. 예를 들어, 본원에(청구범위 포함) 사용된 용어 "위(상)"는, 패턴화된 기판 "위(상)"의 막이 기판의 바로 위에 있고 바로 접촉하고 있는 것을 요구하지 않으며; 상기 막과 기판 사이에 제2의 막 또는 다른 구조가 존재할 수 있다.

당업자는, 상기의 교시 내용을 고려하여 다양한 수정 및 변형이 실시될 수 있음을 인식할 수 있다. 당업자는, 도면에 도시된 여러 구성 요소에 대하여 다양한 등가의 조합과 대체물을 인식할 것이다. 따라서, 본 발명의 범위는 본 상세한 설명에 의해 한정되지 않고, 오히려 첨부된 청구범위에 의해 한정되도록 되어 있다.

Claims (20)

- 반도체 디바이스 형성 방법으로서,

유전체층에 오목한 피쳐를 갖는 패턴화된 기판으로서, 상기 오목한 피쳐에는 평탄화된 벌크 Cu 금속이 적어도 실질적으로 충전되어 있는 것인 패턴화된 기판을 마련하는 단계;

상기 평탄화된 벌크 Cu 금속 및 상기 유전체층을 H2, N2, 또는 NH3, 또는 이들의 조합의 존재 하에서 열처리하는 단계; 및

열처리된 상기 평탄화된 벌크 Cu 금속 상에 Ru 금속막을 선택적으로 증착하는 단계

를 포함하는 반도체 디바이스 형성 방법. - 제1항에 있어서, 상기 열처리하는 단계와 상기 증착하는 단계는 기판 온도를 200℃ 미만으로 하여 수행되는 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 증착하는 단계는 기판 온도를 100℃ 내지 300℃로 하여 수행되는 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 열처리하는 단계는 기판 온도를 200℃ 미만으로 하여 수행되는 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 열처리하는 단계는 기판 온도를 200℃ 내지 400℃로 하여 수행되는 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 Ru 금속막의 두께는 1Å 내지 30Å인 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 Ru 금속막의 두께는 10Å 미만인 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 평탄화된 벌크 Cu 금속에의 상기 Ru 금속막의 표면 피복은, 상기 평탄화된 벌크 Cu 금속을 노출시키는 간극으로 인해 불완전한 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 Ru 금속막을 선택적으로 증착하는 단계는,

Ru3(CO)12 전구체 증기 및 CO 가스를 포함하는 공정 가스를 형성하는 단계로서, 전구체 기화 시스템에서 고체 Ru3(CO)12 전구체를 약 40℃ 내지 약 150℃의 온도로 가열하고, 상기 고체 Ru3(CO)12 전구체를 상기 온도로 유지하여, 상기 Ru3(CO)12 전구체 증기를 형성하는 것과, 상기 Ru3(CO)12 전구체 증기가 형성되고 있을 때, 상기 Ru3(CO)12 전구체 증기를 상기 CO 가스로 포집하도록, 상기 가열하는 동작 동안에 상기 CO 가스를 상기 전구체 기화 시스템에서 상기 고체 Ru3(CO)12 전구체와 접촉하게 유동시키는 것, 그리고 상기 공정 가스를 상기 전구체 기화 시스템으로부터 상기 패턴화된 기판이 있는 공정 챔버로 이송하는 것을 포함하는 공정 가스 형성 단계; 및

상기 패턴화된 기판을 열화학 기상 증착 공정에서 상기 공정 가스에 노출시키는 단계를 포함하는 것인 반도체 디바이스 형성 방법. - 제1항에 있어서, 상기 오목한 피쳐는 하나 이상의 트렌치 및 하나 이상의 비아를 포함하는 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 패턴화된 기판은, 상기 오목한 피쳐 내에 배리어층을 더 포함하는 것인 반도체 디바이스 형성 방법.

- 제1항에 있어서, 상기 Ru 금속막과 상기 유전체층 상에 등각(conformal) 캡층을 증착하는 단계를 더 포함하는 반도체 디바이스 형성 방법.

- 제12항에 있어서, 상기 등각 캡층을 증착하는 단계 이전에, 상기 Ru 금속막과 상기 유전체층을 H2, N2, 또는 NH3, 또는 이들의 조합의 존재 하에서 기판 온도를 150℃ 내지 400℃로 하여 열처리하는 단계를 더 포함하는 반도체 디바이스 형성 방법.

- 반도체 디바이스 형성 방법으로서,

유전체층에 오목한 피쳐를 갖는 패턴화된 기판으로서, 상기 오목한 피쳐에는 평탄화된 벌크 Cu 금속이 적어도 실질적으로 충전되어 있는 것인 패턴화된 기판을 마련하는 단계;

상기 평탄화된 벌크 Cu 금속 및 상기 유전체층을 H2의 존재 하에서 기판 온도를 200℃ 미만으로 하여 열처리하는 단계; 및

열화학 기상 증착 공정에서 상기 패턴화된 기판을 Ru3(CO)12 전구체 증기 및 CO 가스를 함유하는 공정 가스에 노출시킴으로써, 열처리된 상기 평탄화된 벌크 Cu 금속 상에 Ru 금속막을 선택적으로 증착하는 단계

를 포함하는 반도체 디바이스 형성 방법. - 제14항에 있어서, 상기 Ru 금속막과 상기 유전체층 상에 등각 캡층을 증착하는 단계를 더 포함하는 반도체 디바이스 형성 방법.

- 제15항에 있어서, 상기 등각 캡층을 증착하는 단계 이전에, 상기 Ru 금속막과 상기 유전체층을 H2, N2, 또는 NH3, 또는 이들의 조합의 존재 하에서 기판 온도를 약 150℃ 내지 약 400℃로 하여 열처리하는 단계를 더 포함하는 반도체 디바이스 형성 방법.

- 제14항에 있어서, 상기 Ru 금속막의 두께는 2Å 내지 30Å인 것인 반도체 디바이스 형성 방법.

- 반도체 디바이스 형성 방법으로서,

유전체층에 오목한 피쳐를 갖는 패턴화된 기판으로서, 상기 오목한 피쳐에는 평탄화된 벌크 Cu 금속이 적어도 실질적으로 충전되어 있는 것인 패턴화된 기판을 마련하는 단계;

상기 평탄화된 벌크 Cu 금속 및 상기 유전체층을 N2 또는 NH3, 또는 이들의 조합의 존재 하에서 열처리하는 단계; 및

열화학 기상 증착 공정에서 상기 패턴화된 기판을 Ru3(CO)12 전구체 증기 및 CO 가스를 함유하는 공정 가스에 노출시킴으로써, 열처리된 상기 평탄화된 벌크 Cu 금속 상에 Ru 금속막을 선택적으로 증착하는 단계

를 포함하는 반도체 디바이스 형성 방법. - 제18항에 있어서, 상기 Ru 금속막과 상기 유전체층 상에 등각 캡층을 증착하는 단계를 더 포함하는 반도체 디바이스 형성 방법.

- 제19항에 있어서, 상기 등각 캡층을 증착하는 단계 이전에, 상기 Ru 금속막과 상기 유전체층을 H2, N2, 또는 NH3, 또는 이들의 조합의 존재 하에서 기판 온도를 약 150℃ 내지 약 400℃로 하여 열처리하는 단계를 더 포함하는 반도체 디바이스 형성 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/018,074 | 2008-01-22 | ||

| US12/018,074 US7776740B2 (en) | 2008-01-22 | 2008-01-22 | Method for integrating selective low-temperature ruthenium deposition into copper metallization of a semiconductor device |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20100116631A true KR20100116631A (ko) | 2010-11-01 |

Family

ID=40548644

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020107018622A KR20100116631A (ko) | 2008-01-22 | 2009-01-19 | 선택적 저온 루테늄 증착을 반도체 디바이스의 구리 금속 배선에 통합하는 방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7776740B2 (ko) |

| JP (1) | JP5550566B2 (ko) |

| KR (1) | KR20100116631A (ko) |

| CN (1) | CN101981686B (ko) |

| TW (1) | TWI564964B (ko) |

| WO (1) | WO2009094325A1 (ko) |

Families Citing this family (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7737528B2 (en) * | 2008-06-03 | 2010-06-15 | International Business Machines Corporation | Structure and method of forming electrically blown metal fuses for integrated circuits |

| US8823176B2 (en) * | 2008-10-08 | 2014-09-02 | International Business Machines Corporation | Discontinuous/non-uniform metal cap structure and process for interconnect integration |

| US7977235B2 (en) * | 2009-02-02 | 2011-07-12 | Tokyo Electron Limited | Method for manufacturing a semiconductor device with metal-containing cap layers |

| US8716132B2 (en) * | 2009-02-13 | 2014-05-06 | Tokyo Electron Limited | Radiation-assisted selective deposition of metal-containing cap layers |

| DE102009010844B4 (de) * | 2009-02-27 | 2018-10-11 | Advanced Micro Devices, Inc. | Bereitstellen eines verbesserten Elektromigrationsverhaltens und Verringern der Beeinträchtigung empfindlicher dielektrischer Materialien mit kleinem ε in Metallisierungssystemen von Halbleiterbauelementen |

| US8242019B2 (en) * | 2009-03-31 | 2012-08-14 | Tokyo Electron Limited | Selective deposition of metal-containing cap layers for semiconductor devices |

| US8178439B2 (en) * | 2010-03-30 | 2012-05-15 | Tokyo Electron Limited | Surface cleaning and selective deposition of metal-containing cap layers for semiconductor devices |

| US8232200B1 (en) * | 2011-03-18 | 2012-07-31 | International Business Machines Corporation | Methods of forming integrated circuit devices having damascene interconnects therein with metal diffusion barrier layers and devices formed thereby |

| CN102214612B (zh) * | 2011-05-27 | 2015-10-07 | 上海华虹宏力半导体制造有限公司 | 静态随机存储器的制备方法 |

| WO2013126323A1 (en) * | 2012-02-23 | 2013-08-29 | Applied Materials, Inc. | Method and apparatus for precursor delivery |

| CN107836034B (zh) * | 2015-06-05 | 2022-07-19 | 东京毅力科创株式会社 | 用于互连的钌金属特征部填充 |

| JP2017069313A (ja) * | 2015-09-29 | 2017-04-06 | 株式会社日立国際電気 | 半導体装置の製造方法、基板処理装置、ガス供給システムおよびプログラム |

| JP6559046B2 (ja) * | 2015-11-04 | 2019-08-14 | 東京エレクトロン株式会社 | パターン形成方法 |

| US9768063B1 (en) * | 2016-06-30 | 2017-09-19 | Lam Research Corporation | Dual damascene fill |

| US10224224B2 (en) | 2017-03-10 | 2019-03-05 | Micromaterials, LLC | High pressure wafer processing systems and related methods |

| US10622214B2 (en) | 2017-05-25 | 2020-04-14 | Applied Materials, Inc. | Tungsten defluorination by high pressure treatment |

| US10847360B2 (en) | 2017-05-25 | 2020-11-24 | Applied Materials, Inc. | High pressure treatment of silicon nitride film |

| WO2018222771A1 (en) | 2017-06-02 | 2018-12-06 | Applied Materials, Inc. | Dry stripping of boron carbide hardmask |

| US10269571B2 (en) | 2017-07-12 | 2019-04-23 | Applied Materials, Inc. | Methods for fabricating nanowire for semiconductor applications |

| US10179941B1 (en) | 2017-07-14 | 2019-01-15 | Applied Materials, Inc. | Gas delivery system for high pressure processing chamber |

| US10276411B2 (en) * | 2017-08-18 | 2019-04-30 | Applied Materials, Inc. | High pressure and high temperature anneal chamber |

| KR102405723B1 (ko) | 2017-08-18 | 2022-06-07 | 어플라이드 머티어리얼스, 인코포레이티드 | 고압 및 고온 어닐링 챔버 |

| WO2019055415A1 (en) | 2017-09-12 | 2019-03-21 | Applied Materials, Inc. | APPARATUS AND METHODS FOR MANUFACTURING SEMICONDUCTOR STRUCTURES USING A PROTECTIVE BARRIER LAYER |

| US10643867B2 (en) | 2017-11-03 | 2020-05-05 | Applied Materials, Inc. | Annealing system and method |

| WO2019094481A1 (en) | 2017-11-11 | 2019-05-16 | Micromaterials Llc | Gas delivery system for high pressure processing chamber |

| CN111373519B (zh) | 2017-11-16 | 2021-11-23 | 应用材料公司 | 高压蒸气退火处理设备 |

| CN111432920A (zh) | 2017-11-17 | 2020-07-17 | 应用材料公司 | 用于高压处理系统的冷凝器系统 |

| TWI790320B (zh) * | 2017-12-16 | 2023-01-21 | 美商應用材料股份有限公司 | 釕的選擇性原子層沉積 |

| JP7299898B2 (ja) | 2018-01-24 | 2023-06-28 | アプライド マテリアルズ インコーポレイテッド | 高圧アニールを用いたシーム修復 |

| CN111902929A (zh) | 2018-03-09 | 2020-11-06 | 应用材料公司 | 用于含金属材料的高压退火处理 |

| US10714331B2 (en) | 2018-04-04 | 2020-07-14 | Applied Materials, Inc. | Method to fabricate thermally stable low K-FinFET spacer |

| US10950429B2 (en) | 2018-05-08 | 2021-03-16 | Applied Materials, Inc. | Methods of forming amorphous carbon hard mask layers and hard mask layers formed therefrom |

| US10566188B2 (en) | 2018-05-17 | 2020-02-18 | Applied Materials, Inc. | Method to improve film stability |

| US10704141B2 (en) | 2018-06-01 | 2020-07-07 | Applied Materials, Inc. | In-situ CVD and ALD coating of chamber to control metal contamination |

| US10748783B2 (en) | 2018-07-25 | 2020-08-18 | Applied Materials, Inc. | Gas delivery module |

| US10675581B2 (en) | 2018-08-06 | 2020-06-09 | Applied Materials, Inc. | Gas abatement apparatus |

| WO2020092002A1 (en) | 2018-10-30 | 2020-05-07 | Applied Materials, Inc. | Methods for etching a structure for semiconductor applications |

| CN112996950B (zh) | 2018-11-16 | 2024-04-05 | 应用材料公司 | 使用增强扩散工艺的膜沉积 |

| WO2020117462A1 (en) | 2018-12-07 | 2020-06-11 | Applied Materials, Inc. | Semiconductor processing system |

| WO2020251696A1 (en) | 2019-06-10 | 2020-12-17 | Applied Materials, Inc. | Processing system for forming layers |

| US11901222B2 (en) | 2020-02-17 | 2024-02-13 | Applied Materials, Inc. | Multi-step process for flowable gap-fill film |

Family Cites Families (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4851895A (en) * | 1985-05-06 | 1989-07-25 | American Telephone And Telegraph Company, At&T Bell Laboratories | Metallization for integrated devices |

| US4929468A (en) * | 1988-03-18 | 1990-05-29 | The United States Of America As Represented By The United States Department Of Energy | Formation of amorphous metal alloys by chemical vapor deposition |

| US4938999A (en) * | 1988-07-11 | 1990-07-03 | Jenkin William C | Process for coating a metal substrate by chemical vapor deposition using a metal carbonyl |

| US5171610A (en) * | 1990-08-28 | 1992-12-15 | The Regents Of The University Of Calif. | Low temperature photochemical vapor deposition of alloy and mixed metal oxide films |

| US5314727A (en) * | 1992-07-28 | 1994-05-24 | Minnesota Mining & Mfg. Co./Regents Of The University Of Minnesota | Chemical vapor deposition of iron, ruthenium, and osmium |

| US5359787A (en) | 1993-04-16 | 1994-11-01 | Air Products And Chemicals, Inc. | High purity bulk chemical delivery system |

| CA2206217C (en) | 1997-05-27 | 2003-01-07 | Miroslav Milinkovic | Nickel carbonyl vapour deposition process |

| US6077780A (en) * | 1997-12-03 | 2000-06-20 | Advanced Micro Devices, Inc. | Method for filling high aspect ratio openings of an integrated circuit to minimize electromigration failure |

| ATE255555T1 (de) * | 1998-05-01 | 2003-12-15 | Pfizer Prod Inc | Verfahren zur herstellung von enantiomeren reinem oder optisch angereicherter sertraline-tetralon durch kontinuierliche chromatographie |

| US6287435B1 (en) | 1998-05-06 | 2001-09-11 | Tokyo Electron Limited | Method and apparatus for ionized physical vapor deposition |

| US6063705A (en) * | 1998-08-27 | 2000-05-16 | Micron Technology, Inc. | Precursor chemistries for chemical vapor deposition of ruthenium and ruthenium oxide |

| US6074945A (en) * | 1998-08-27 | 2000-06-13 | Micron Technology, Inc. | Methods for preparing ruthenium metal films |

| CA2307036C (en) | 1998-11-03 | 2003-05-27 | Chemical Vapour Deposition Systems Inc. | Nickel carbonyl vapour deposition apparatus and process |

| US6242349B1 (en) * | 1998-12-09 | 2001-06-05 | Advanced Micro Devices, Inc. | Method of forming copper/copper alloy interconnection with reduced electromigration |

| US6232230B1 (en) * | 1999-01-05 | 2001-05-15 | Advanced Micro Devices, Inc. | Semiconductor interconnect interface processing by high temperature deposition |

| US6319832B1 (en) * | 1999-02-19 | 2001-11-20 | Micron Technology, Inc. | Methods of making semiconductor devices |

| US6342733B1 (en) * | 1999-07-27 | 2002-01-29 | International Business Machines Corporation | Reduced electromigration and stressed induced migration of Cu wires by surface coating |

| US6303809B1 (en) * | 1999-12-10 | 2001-10-16 | Yun Chi | Organometallic ruthenium and osmium source reagents for chemical vapor deposition |

| US7228556B2 (en) * | 1999-12-21 | 2007-06-05 | Tivo Inc. | Distributed, interactive television program guide; system and method |

| AU2001260374A1 (en) * | 2000-05-15 | 2001-11-26 | Asm Microchemistry Oy | Process for producing integrated circuits |

| US6440495B1 (en) * | 2000-08-03 | 2002-08-27 | Applied Materials, Inc. | Chemical vapor deposition of ruthenium films for metal electrode applications |

| US6444263B1 (en) * | 2000-09-15 | 2002-09-03 | Cvc Products, Inc. | Method of chemical-vapor deposition of a material |

| KR100727372B1 (ko) * | 2001-09-12 | 2007-06-12 | 토소가부시키가이샤 | 루테늄착체, 그 제조방법 및 박막의 제조방법 |

| US6420583B1 (en) * | 2001-09-27 | 2002-07-16 | Praxair Technology, Inc | Methods of synthesizing ruthenium and osmium compounds |

| US6713373B1 (en) * | 2002-02-05 | 2004-03-30 | Novellus Systems, Inc. | Method for obtaining adhesion for device manufacture |

| US7264846B2 (en) * | 2002-06-04 | 2007-09-04 | Applied Materials, Inc. | Ruthenium layer formation for copper film deposition |

| JP3992588B2 (ja) | 2002-10-23 | 2007-10-17 | 東京エレクトロン株式会社 | 成膜方法 |

| US6989321B2 (en) * | 2003-09-30 | 2006-01-24 | Tokyo Electron Limited | Low-pressure deposition of metal layers from metal-carbonyl precursors |

| US7078341B2 (en) | 2003-09-30 | 2006-07-18 | Tokyo Electron Limited | Method of depositing metal layers from metal-carbonyl precursors |

| US7107998B2 (en) * | 2003-10-16 | 2006-09-19 | Novellus Systems, Inc. | Method for preventing and cleaning ruthenium-containing deposits in a CVD apparatus |

| US20050110142A1 (en) * | 2003-11-26 | 2005-05-26 | Lane Michael W. | Diffusion barriers formed by low temperature deposition |

| US7285308B2 (en) * | 2004-02-23 | 2007-10-23 | Advanced Technology Materials, Inc. | Chemical vapor deposition of high conductivity, adherent thin films of ruthenium |

| US7211509B1 (en) * | 2004-06-14 | 2007-05-01 | Novellus Systems, Inc, | Method for enhancing the nucleation and morphology of ruthenium films on dielectric substrates using amine containing compounds |

| US7476618B2 (en) * | 2004-10-26 | 2009-01-13 | Asm Japan K.K. | Selective formation of metal layers in an integrated circuit |

| JP2006128288A (ja) | 2004-10-27 | 2006-05-18 | Tokyo Electron Ltd | 成膜方法、半導体装置の製造方法、半導体装置、プログラムおよび記録媒体 |

| US7270848B2 (en) * | 2004-11-23 | 2007-09-18 | Tokyo Electron Limited | Method for increasing deposition rates of metal layers from metal-carbonyl precursors |

| US7279421B2 (en) * | 2004-11-23 | 2007-10-09 | Tokyo Electron Limited | Method and deposition system for increasing deposition rates of metal layers from metal-carbonyl precursors |

| US7638002B2 (en) * | 2004-11-29 | 2009-12-29 | Tokyo Electron Limited | Multi-tray film precursor evaporation system and thin film deposition system incorporating same |

| US20060113675A1 (en) * | 2004-12-01 | 2006-06-01 | Chung-Liang Chang | Barrier material and process for Cu interconnect |

| JP2006179599A (ja) * | 2004-12-21 | 2006-07-06 | Toshiba Corp | 半導体装置およびその製造方法 |

| US7265048B2 (en) * | 2005-03-01 | 2007-09-04 | Applied Materials, Inc. | Reduction of copper dewetting by transition metal deposition |

| US7396766B2 (en) * | 2005-03-31 | 2008-07-08 | Tokyo Electron Limited | Low-temperature chemical vapor deposition of low-resistivity ruthenium layers |

| US7288479B2 (en) * | 2005-03-31 | 2007-10-30 | Tokyo Electron Limited | Method for forming a barrier/seed layer for copper metallization |

| US20070059502A1 (en) * | 2005-05-05 | 2007-03-15 | Applied Materials, Inc. | Integrated process for sputter deposition of a conductive barrier layer, especially an alloy of ruthenium and tantalum, underlying copper or copper alloy seed layer |

| US7402519B2 (en) * | 2005-06-03 | 2008-07-22 | Intel Corporation | Interconnects having sealing structures to enable selective metal capping layers |

| US7713876B2 (en) * | 2005-09-28 | 2010-05-11 | Tokyo Electron Limited | Method for integrating a ruthenium layer with bulk copper in copper metallization |

| US7785658B2 (en) * | 2005-10-07 | 2010-08-31 | Asm Japan K.K. | Method for forming metal wiring structure |

| US20070099422A1 (en) * | 2005-10-28 | 2007-05-03 | Kapila Wijekoon | Process for electroless copper deposition |

| US20070117377A1 (en) * | 2005-11-23 | 2007-05-24 | Chih-Chao Yang | Conductor-dielectric structure and method for fabricating |

| US7439624B2 (en) * | 2006-05-18 | 2008-10-21 | International Business Machines Corporation | Enhanced mechanical strength via contacts |

| US20080081464A1 (en) * | 2006-09-29 | 2008-04-03 | Tokyo Electron Limited | Method of integrated substrated processing using a hot filament hydrogen radical souce |

-

2008

- 2008-01-22 US US12/018,074 patent/US7776740B2/en not_active Expired - Fee Related

-

2009

- 2009-01-19 WO PCT/US2009/031414 patent/WO2009094325A1/en active Application Filing

- 2009-01-19 JP JP2010544381A patent/JP5550566B2/ja not_active Expired - Fee Related

- 2009-01-19 KR KR1020107018622A patent/KR20100116631A/ko not_active Application Discontinuation

- 2009-01-19 CN CN200980110629.9A patent/CN101981686B/zh not_active Expired - Fee Related

- 2009-01-22 TW TW098102510A patent/TWI564964B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| CN101981686B (zh) | 2016-03-02 |

| JP5550566B2 (ja) | 2014-07-16 |

| US7776740B2 (en) | 2010-08-17 |

| JP2011510517A (ja) | 2011-03-31 |

| US20090186481A1 (en) | 2009-07-23 |

| TWI564964B (zh) | 2017-01-01 |

| CN101981686A (zh) | 2011-02-23 |

| WO2009094325A1 (en) | 2009-07-30 |

| TW200947558A (en) | 2009-11-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7776740B2 (en) | Method for integrating selective low-temperature ruthenium deposition into copper metallization of a semiconductor device | |

| US7829454B2 (en) | Method for integrating selective ruthenium deposition into manufacturing of a semiconductior device | |

| JP5674669B2 (ja) | ルテニウム金属キャップ層を形成する方法 | |

| US20120252210A1 (en) | Method for modifying metal cap layers in semiconductor devices | |

| US7473634B2 (en) | Method for integrated substrate processing in copper metallization | |

| US8076241B2 (en) | Methods for multi-step copper plating on a continuous ruthenium film in recessed features | |

| JP5683038B2 (ja) | 成膜方法 | |

| US7432195B2 (en) | Method for integrating a conformal ruthenium layer into copper metallization of high aspect ratio features | |

| US20080081464A1 (en) | Method of integrated substrated processing using a hot filament hydrogen radical souce | |

| US20080078325A1 (en) | Processing system containing a hot filament hydrogen radical source for integrated substrate processing | |

| US9779950B2 (en) | Ruthenium film forming method, film forming apparatus, and semiconductor device manufacturing method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |