KR102199607B1 - 비휘발성 메모리에 멀티비트 데이터를 저장하기 위한 시스템 및 방법 - Google Patents

비휘발성 메모리에 멀티비트 데이터를 저장하기 위한 시스템 및 방법 Download PDFInfo

- Publication number

- KR102199607B1 KR102199607B1 KR1020207010818A KR20207010818A KR102199607B1 KR 102199607 B1 KR102199607 B1 KR 102199607B1 KR 1020207010818 A KR1020207010818 A KR 1020207010818A KR 20207010818 A KR20207010818 A KR 20207010818A KR 102199607 B1 KR102199607 B1 KR 102199607B1

- Authority

- KR

- South Korea

- Prior art keywords

- read current

- voltage

- offset value

- memory cells

- memory cell

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims abstract description 29

- 239000000758 substrate Substances 0.000 claims description 19

- 239000004065 semiconductor Substances 0.000 claims description 14

- 239000000463 material Substances 0.000 description 13

- 230000008878 coupling Effects 0.000 description 5

- 238000010168 coupling process Methods 0.000 description 5

- 238000005859 coupling reaction Methods 0.000 description 5

- 230000006870 function Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 3

- 238000000926 separation method Methods 0.000 description 3

- 230000008569 process Effects 0.000 description 2

- 230000005641 tunneling Effects 0.000 description 2

- 230000005689 Fowler Nordheim tunneling Effects 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

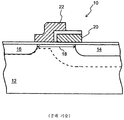

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0425—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a merged floating gate and select transistor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0441—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates

- G11C16/0458—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates comprising two or more independent floating gates which store independent data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0466—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS]

- G11C16/0475—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS] comprising two or more independent storage sites which store independent data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201762581489P | 2017-11-03 | 2017-11-03 | |

| US62/581,489 | 2017-11-03 | ||

| US16/148,304 US10515694B2 (en) | 2017-11-03 | 2018-10-01 | System and method for storing multibit data in non-volatile memory |

| US16/148,304 | 2018-10-01 | ||

| PCT/US2018/053930 WO2019089168A1 (en) | 2017-11-03 | 2018-10-02 | System and method for storing multibit data in non-volatile memory |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20200043501A KR20200043501A (ko) | 2020-04-27 |

| KR102199607B1 true KR102199607B1 (ko) | 2021-01-08 |

Family

ID=66327523

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020207010818A Active KR102199607B1 (ko) | 2017-11-03 | 2018-10-02 | 비휘발성 메모리에 멀티비트 데이터를 저장하기 위한 시스템 및 방법 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US10515694B2 (enExample) |

| EP (1) | EP3704700B1 (enExample) |

| JP (1) | JP6970826B2 (enExample) |

| KR (1) | KR102199607B1 (enExample) |

| CN (1) | CN111344791B (enExample) |

| TW (1) | TWI682393B (enExample) |

| WO (1) | WO2019089168A1 (enExample) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100671698B1 (ko) * | 2004-08-05 | 2007-01-18 | 매그나칩 반도체 유한회사 | 엘디아이 내 디지털 아날로그 변환기의 테스트 장치 |

| KR20230080156A (ko) | 2021-11-29 | 2023-06-07 | 충남대학교산학협력단 | 멀티 레벨 구동이 가능한 메모리 소자 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10991433B2 (en) * | 2019-09-03 | 2021-04-27 | Silicon Storage Technology, Inc. | Method of improving read current stability in analog non-volatile memory by limiting time gap between erase and program |

| US11682459B2 (en) * | 2020-05-13 | 2023-06-20 | Silicon Storage Technology, Inc. | Analog neural memory array in artificial neural network comprising logical cells and improved programming mechanism |

| US12080355B2 (en) | 2021-06-02 | 2024-09-03 | Silicon Storage Technology, Inc. | Method of improving read current stability in analog non-volatile memory by post-program tuning for memory cells exhibiting random telegraph noise |

| US11769558B2 (en) * | 2021-06-08 | 2023-09-26 | Silicon Storage Technology, Inc. | Method of reducing random telegraph noise in non-volatile memory by grouping and screening memory cells |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20150085571A1 (en) | 2013-09-24 | 2015-03-26 | Sandisk Technologies Inc. | Updating read voltages |

| US20160064058A1 (en) | 2014-08-29 | 2016-03-03 | Everspin Technologies, Inc. | Configuration and testing for magnetoresistive memory |

| US20160148701A1 (en) | 2014-11-20 | 2016-05-26 | HGST Netherlands B.V. | Read level grouping algorithms for increased flash performance |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5029130A (en) | 1990-01-22 | 1991-07-02 | Silicon Storage Technology, Inc. | Single transistor non-valatile electrically alterable semiconductor memory device |

| JP2812202B2 (ja) * | 1994-06-27 | 1998-10-22 | ヤマハ株式会社 | 半導体記憶装置 |

| KR100324594B1 (ko) | 1999-06-28 | 2002-02-16 | 박종섭 | 강유전체 메모리 장치 |

| US7082056B2 (en) | 2004-03-12 | 2006-07-25 | Super Talent Electronics, Inc. | Flash memory device and architecture with multi level cells |

| US7324374B2 (en) | 2003-06-20 | 2008-01-29 | Spansion Llc | Memory with a core-based virtual ground and dynamic reference sensing scheme |

| US7315056B2 (en) | 2004-06-07 | 2008-01-01 | Silicon Storage Technology, Inc. | Semiconductor memory array of floating gate memory cells with program/erase and select gates |

| US7554856B2 (en) * | 2006-10-06 | 2009-06-30 | Qimonda Flash Gmbh & Co. Kg | Memory cell |

| US20090039410A1 (en) | 2007-08-06 | 2009-02-12 | Xian Liu | Split Gate Non-Volatile Flash Memory Cell Having A Floating Gate, Control Gate, Select Gate And An Erase Gate With An Overhang Over The Floating Gate, Array And Method Of Manufacturing |

| US8238149B2 (en) | 2009-06-25 | 2012-08-07 | Macronix International Co., Ltd. | Methods and apparatus for reducing defect bits in phase change memory |

| JP2012209004A (ja) | 2011-03-30 | 2012-10-25 | Toshiba Corp | 半導体記憶装置 |

| US9099202B2 (en) * | 2012-11-06 | 2015-08-04 | Sandisk Technologies Inc. | 3D stacked non-volatile storage programming to conductive state |

| KR102043723B1 (ko) | 2013-02-28 | 2019-12-02 | 에스케이하이닉스 주식회사 | 반도체 장치 및 이를 포함하는 프로세서와 시스템 |

| KR101716998B1 (ko) | 2013-03-14 | 2017-03-15 | 실리콘 스토리지 테크놀로지 인크 | 비휘발성 메모리 프로그램 알고리즘 디바이스 및 방법 |

| US9484094B2 (en) | 2015-01-21 | 2016-11-01 | Ememory Technology Inc. | Control method of resistive random-access memory |

-

2018

- 2018-10-01 US US16/148,304 patent/US10515694B2/en active Active

- 2018-10-02 WO PCT/US2018/053930 patent/WO2019089168A1/en not_active Ceased

- 2018-10-02 KR KR1020207010818A patent/KR102199607B1/ko active Active

- 2018-10-02 EP EP18872824.0A patent/EP3704700B1/en active Active

- 2018-10-02 JP JP2020524440A patent/JP6970826B2/ja active Active

- 2018-10-02 CN CN201880068646.XA patent/CN111344791B/zh active Active

- 2018-10-24 TW TW107137607A patent/TWI682393B/zh active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20150085571A1 (en) | 2013-09-24 | 2015-03-26 | Sandisk Technologies Inc. | Updating read voltages |

| US20160064058A1 (en) | 2014-08-29 | 2016-03-03 | Everspin Technologies, Inc. | Configuration and testing for magnetoresistive memory |

| US20160148701A1 (en) | 2014-11-20 | 2016-05-26 | HGST Netherlands B.V. | Read level grouping algorithms for increased flash performance |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100671698B1 (ko) * | 2004-08-05 | 2007-01-18 | 매그나칩 반도체 유한회사 | 엘디아이 내 디지털 아날로그 변환기의 테스트 장치 |

| KR20230080156A (ko) | 2021-11-29 | 2023-06-07 | 충남대학교산학협력단 | 멀티 레벨 구동이 가능한 메모리 소자 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201931370A (zh) | 2019-08-01 |

| JP6970826B2 (ja) | 2021-11-24 |

| US20190139602A1 (en) | 2019-05-09 |

| WO2019089168A1 (en) | 2019-05-09 |

| CN111344791B (zh) | 2021-06-25 |

| TWI682393B (zh) | 2020-01-11 |

| EP3704700B1 (en) | 2022-07-20 |

| JP2021501956A (ja) | 2021-01-21 |

| CN111344791A (zh) | 2020-06-26 |

| EP3704700A4 (en) | 2021-07-21 |

| US10515694B2 (en) | 2019-12-24 |

| KR20200043501A (ko) | 2020-04-27 |

| EP3704700A1 (en) | 2020-09-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102199607B1 (ko) | 비휘발성 메모리에 멀티비트 데이터를 저장하기 위한 시스템 및 방법 | |

| TW201832241A (zh) | 減少在非揮發記憶體單元中的程式干擾的方法 | |

| US10699787B2 (en) | System and method for minimizing floating gate to floating gate coupling effects during programming in flash memory | |

| CN110462582A (zh) | 基于非易失性存储器单元阵列生成随机数的系统和方法 | |

| KR102344013B1 (ko) | 전류 승수들을 사용하여 비휘발성 메모리에서 멀티비트 데이터를 저장 및 검색하기 위한 시스템 및 방법 | |

| KR102282580B1 (ko) | 비휘발성 메모리 어레이에서 피크 전력 요구 및 잡음을 관리하기 위한 시스템 및 방법 | |

| TWI697001B (zh) | 用於藉由最佳化程式化操作來實施推理引擎的系統及方法 | |

| US20250231705A1 (en) | Coarse and fine programming of non-volatile memory cells | |

| WO2025058634A1 (en) | System and method for implementing temperature compensation in a memory device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A302 | Request for accelerated examination | ||

| PA0105 | International application |

Patent event date: 20200414 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PA0201 | Request for examination | ||

| PA0302 | Request for accelerated examination |

Patent event date: 20200414 Patent event code: PA03022R01D Comment text: Request for Accelerated Examination |

|

| PG1501 | Laying open of application | ||

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20200810 Patent event code: PE09021S01D |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

Patent event code: PE07011S01D Comment text: Decision to Grant Registration Patent event date: 20201207 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

Comment text: Registration of Establishment Patent event date: 20201231 Patent event code: PR07011E01D |

|

| PR1002 | Payment of registration fee |

Payment date: 20201231 End annual number: 3 Start annual number: 1 |

|

| PG1601 | Publication of registration | ||

| PR1001 | Payment of annual fee |

Payment date: 20231128 Start annual number: 4 End annual number: 4 |