KR102199607B1 - 비휘발성 메모리에 멀티비트 데이터를 저장하기 위한 시스템 및 방법 - Google Patents

비휘발성 메모리에 멀티비트 데이터를 저장하기 위한 시스템 및 방법 Download PDFInfo

- Publication number

- KR102199607B1 KR102199607B1 KR1020207010818A KR20207010818A KR102199607B1 KR 102199607 B1 KR102199607 B1 KR 102199607B1 KR 1020207010818 A KR1020207010818 A KR 1020207010818A KR 20207010818 A KR20207010818 A KR 20207010818A KR 102199607 B1 KR102199607 B1 KR 102199607B1

- Authority

- KR

- South Korea

- Prior art keywords

- read current

- voltage

- offset value

- memory cells

- memory cell

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 29

- 239000000758 substrate Substances 0.000 claims description 19

- 239000004065 semiconductor Substances 0.000 claims description 14

- 239000000463 material Substances 0.000 description 13

- 230000008878 coupling Effects 0.000 description 5

- 238000010168 coupling process Methods 0.000 description 5

- 238000005859 coupling reaction Methods 0.000 description 5

- 230000006870 function Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 3

- 238000000926 separation method Methods 0.000 description 3

- 230000008569 process Effects 0.000 description 2

- 230000005641 tunneling Effects 0.000 description 2

- 230000005689 Fowler Nordheim tunneling Effects 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0425—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a merged floating gate and select transistor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0441—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates

- G11C16/0458—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing multiple floating gate devices, e.g. separate read-and-write FAMOS transistors with connected floating gates comprising two or more independent floating gates which store independent data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0466—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS]

- G11C16/0475—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells with charge storage in an insulating layer, e.g. metal-nitride-oxide-silicon [MNOS], silicon-oxide-nitride-oxide-silicon [SONOS] comprising two or more independent storage sites which store independent data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하는 것, 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하는 것, 제2 판독 전류에 제1 오프셋 값을 적용하는 것, 및 이어서 제1 판독 전류와 제2 판독 전류를 조합하여 제3 판독 전류를 형성하는 것, 및 이어서 제3 판독 전류를 이용하여 프로그램 상태를 결정하는 것에 의한, 복수의 메모리 셀들을 갖는 메모리 디바이스를 판독하는 방법, 및 이들을 위해 구성된 디바이스. 대안적으로, 제1 전압이 제1 판독 전류로부터 생성되고, 제2 전압이 제2 판독 전류로부터 생성되며, 그에 의해 오프셋 값이 제2 전압에 적용되며, 여기서 제1 전압과 제2 전압이 조합되어 제3 전압을 형성하고, 이어서 프로그램 상태는 제3 전압을 이용하여 결정된다.

Description

관련 출원

본 출원은 2017년 11월 3일자로 출원된 미국 가출원 제62/581,489호 및 2018년 10월 1일자로 출원된 미국 특허 출원 제16/148,304호의 이익을 주장한다.

기술분야

본 발명은 비휘발성 메모리 디바이스에 관한 것이며, 더 구체적으로는 그 안에 저장될 수 있는 비트의 개수를 증가시키는 것에 관한 것이다.

비휘발성 메모리 디바이스들은 본 기술 분야에 잘 알려져 있다. 예를 들어, 분리형 게이트 메모리 셀이 미국 특허 제5,029,130호에 개시되어 있다. 이러한 메모리 셀은 소스 영역과 드레인 영역 사이에 연장되는 기판의 채널 영역 위에 배치되고 그의 전도율을 제어하는 제어 게이트 및 플로팅 게이트를 갖는다. (플로팅 게이트 상에 전자들을 주입함으로써) 메모리 셀을 프로그램하고, (플로팅 게이트로부터 전자들을 제거함으로써) 메모리 셀을 소거하고, (플로팅 게이트의 프로그래밍 상태를 결정하기 위해 채널 영역의 전도율을 측정하거나 검출함으로써) 메모리 셀을 판독하기 위해 전압들의 다양한 조합들이 제어 게이트, 소스 및 드레인에 인가된다.

비휘발성 메모리 셀들 내의 게이트들의 구성 및 개수는 달라질 수 있다. 예를 들어, 미국 특허 제7,315,056호는 소스 영역 위에 프로그램/소거 게이트를 추가로 포함하는 메모리 셀을 개시한다. 미국 특허 제7,868,375호는 소스 영역 위에 소거 게이트를 그리고 플로팅 게이트 위에 커플링 게이트를 추가로 포함하는 메모리 셀을 개시한다.

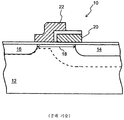

도 1은 이격된 소스 및 드레인 영역들(14/16)이 실리콘 반도체 기판(12)에 형성된 분리형 게이트 메모리 셀(10)을 예시한다. 기판의 채널 영역(18)이 소스/드레인 영역들(14/16) 사이에 정의된다. 플로팅 게이트(20)가 채널 영역(18)의 제1 부분 위에 배치되고 그로부터 절연된다(그리고 부분적으로 소스 영역(14) 위에 있고 그로부터 절연된다). 제어 게이트(워드 라인 게이트 또는 선택 게이트로도 지칭됨)(22)가 채널 영역(18)의 제2 부분 위에 배치되고 그로부터 절연된 하부 부분, 및 위쪽으로 그리고 플로팅 게이트(20) 위로 연장되는 상부 부분을 갖는다(즉, 제어 게이트(22)는 플로팅 게이트(20)의 상부 에지 주위를 감싼다).

메모리 셀(10)은 제어 게이트(22) 상에 고 포지티브 전압을 그리고 소스 및 드레인 영역들(14/16) 상에 기준 전위를 배치함으로써 소거될 수 있다. 플로팅 게이트(20)와 제어 게이트(22) 사이의 고 전압 강하는 잘 알려진 파울러-노드하임(Fowler-Nordheim) 터널링 메커니즘에 의해 플로팅 게이트(20) 상의 전자들이 플로팅 게이트(20)로부터 개재된 절연체를 통해 제어 게이트(22)로 터널링하게 할 것이다(플로팅 게이트(20)를 더 포지티브로 대전된 상태 - 소거된 상태로 둠). 메모리 셀(10)은 드레인 영역(16)에 접지 전위를, 소스 영역(14) 상에 포지티브 전압을, 그리고 제어 게이트(22) 상에 포지티브 전압을 인가함으로써 프로그램될 수 있다. 이어서 전자들이 드레인 영역(16)으로부터 소스 영역(14)을 향해 흐를 것이며, 이때 일부 전자들은 가속화되고 가열되며 이에 의해 그들은 플로팅 게이트(20) 상에 주입된다(플로팅 게이트를 네거티브로 대전된 상태 - 프로그램된 상태로 둠). 메모리 셀(10)은 드레인 영역(16) 상에 접지 전위를, 소스 영역(14) 상에 포지티브 전압을, 그리고 제어 게이트(22) 상에 포지티브 전압을 배치함으로써 판독될 수 있다(제어 게이트(22) 아래의 채널 영역 부분을 턴온함). 플로팅 게이트가 더 포지티브로 대전(소거)되는 경우, 제어 게이트 상의 포지티브 전압은 플로팅 게이트에 적어도 부분적으로 커플링되어 플로팅 게이트 아래의 채널 영역 부분을 턴온할 것이고, 소스 영역(14)으로부터 드레인 영역(16)으로 전류가 흐를 것이다(즉, 메모리 셀(10)은 감지된 전류 흐름에 기초하여 그의 소거된 "1" 상태에 있는 것으로 감지된다). 플로팅 게이트(20)가 네거티브로 대전(프로그램)되는 경우, 제어 게이트(22)로부터의 커플링된 전압은 플로팅 게이트의 네거티브 전하를 극복하지 못할 것이고, 플로팅 게이트 아래의 채널 영역은 약하게 턴온되거나 턴오프되며, 그에 의해 임의의 전류 흐름을 감소시키거나 방지한다(즉, 메모리 셀(10)은 감지된 전류 흐름이 낮거나 없음에 기초하여 그의 프로그램된 "0" 상태에 있는 것으로 감지된다).

도 2는 메모리 셀(10)과 동일한 요소들을 갖지만, 소스 영역(14) 위에 배치되고 그로부터 절연된 프로그램/소거(PE) 게이트(32)를 추가로 갖는 대안적인 분리형 게이트 메모리 셀(30)을 예시한다(즉, 이것은 3-게이트 설계이다). 메모리 셀(30)은 PE 게이트(32) 상에 고 전압을 배치하여 플로팅 게이트(20)로부터 PE 게이트(32)로의 전자들의 터널링을 유도함으로써 소거될 수 있다. 메모리 셀(30)은 채널 영역(18)을 통해 흐르는 전류로부터의 전자들을 플로팅 게이트(20) 상에 주입하기 위해 제어 게이트(22), PE 게이트(32), 및 소스 영역(14) 상에 포지티브 전압들을, 그리고 드레인 영역(16) 상에 전류를 배치함으로써 프로그램될 수 있다. 메모리 셀(40)은 제어 게이트(22) 및 드레인 영역(16) 상에 포지티브 전압들을 배치하고, 전류 흐름을 감지함으로써 판독될 수 있다.

도 3은 메모리 셀(10)과 동일한 요소들을 갖지만, 소스 영역(14) 위에 배치되고 그로부터 절연된 소거 게이트(42), 및 플로팅 게이트(20) 위에 있고 그로부터 절연된 커플링 게이트(44)를 추가로 갖는 대안적인 분리형 게이트 메모리 셀(40)을 예시한다. 메모리 셀(40)은 플로팅 게이트(20)로부터 소거 게이트(42)로의 전자들의 터널링을 유도하기 위해 소거 게이트(42) 상에 고전압을(그리고 선택적으로 커플링 게이트(44) 상에 네거티브 전압을) 배치함으로써 소거될 수 있다. 메모리 셀(40)은 채널 영역(18)을 통해 흐르는 전류로부터의 전자들을 플로팅 게이트(20) 상에 주입하기 위해 제어 게이트(22), 소거 게이트(42), 커플링 게이트(44), 및 소스 영역(14) 상에 포지티브 전압들을, 그리고 드레인 영역(16) 상에 전류를 배치함으로써 프로그램될 수 있다. 메모리 셀(40)은 제어 게이트(22) 및 드레인 영역(16) 상에(그리고 선택적으로 소거 게이트(42) 및/또는 커플링 게이트(44) 상에) 포지티브 전압들을 배치하고, 전류 흐름을 감지함으로써 판독될 수 있다.

위에 언급된 모든 메모리 셀들에 대해, 메모리 셀들을 "0" 상태로 프로그램하고, 메모리 셀들을 "1" 상태로 소거하고, 메모리 셀들이 프로그램된 상태에 있는지 또는 소거된 상태에 있는지를 결정하기 위해 메모리 셀들을 판독하기 위해서 프로그램, 소거 및 판독 동작들 각각에서 전압들이 인가된다. 그러한 메모리 디바이스들에 대한 한 가지 문제점은 각각의 메모리 셀이 단지 1 비트의 데이터만을 저장할 수 있다는 것이다(즉, 셀은 단지 2개의 가능한 상태만을 갖는다). 각각의 메모리 셀에 1 비트 초과의 데이터를 프로그램할 필요가 있다. 메모리 셀이 단지 2개의 이진 값(즉, 단지 1 비트의 정보)보다 많이 저장할 수 있도록 위에 설명된 메모리 셀들을 아날로그 방식으로 동작시키는 것이 또한 알려져 있다. 예를 들어, 메모리 셀들은 그들의 문턱 전압(threshold voltage) 아래에서 동작될 수 있는데, 이는 메모리 셀들을 완전히 프로그램하거나 완전히 소거하는 대신에, 그들이 단지 부분적으로 프로그램되거나 부분적으로 소거되고, 메모리 셀의 문턱 전압 아래에서 아날로그 방식으로 동작될 수 있다는 것을 의미한다. 메모리 셀들을 문턱 전압 위의 다수의 프로그램 상태 중 하나로 프로그램하는 것도 또한 가능하다. 그러나, 이산 프로그래밍 상태들이 요구되는 경우, 다양한 상태들에 대한 판독 전류 값들이 서로 너무 가깝기 때문에 메모리 셀들을 신뢰성 있게 프로그램하고 판독하는 것이 어려울 수 있다.

전술된 문제 및 요구는 복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하는 단계, 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하는 단계, 제2 판독 전류에 제1 오프셋 값을 적용하는 단계, 및 이어서 제1 판독 전류와 제2 판독 전류를 조합하여 제3 판독 전류를 형성하는 단계, 및 이어서 제3 판독 전류를 이용하여 프로그램 상태를 결정하는 단계에 의한, 복수의 메모리 셀들을 갖는 메모리 디바이스를 판독하는 방법에 의해 해결된다.

복수의 메모리 셀들을 갖는 메모리 디바이스를 판독하는 방법은 복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하는 단계, 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하는 단계, 제1 판독 전류로부터 제1 전압을 생성하는 단계, 제2 판독 전류로부터 제2 전압을 생성하는 단계, 제2 전압에 제1 오프셋 값을 적용하는 단계, 및 이어서 제1 전압과 제2 전압을 조합하여 제3 전압을 형성하는 단계, 및 이어서 제3 전압을 이용하여 프로그램 상태를 결정하는 단계를 포함한다.

메모리 디바이스는 반도체 기판, 반도체 기판 상에 형성된 복수의 메모리 셀들, 및 반도체 기판 상에 형성되고, 복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하고, 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하고, 제2 판독 전류에 제1 오프셋 값을 적용하고, 이어서 제1 판독 전류와 제2 판독 전류를 조합하여 제3 판독 전류를 형성하고, 이어서 제3 판독 전류를 이용하여 프로그램 상태를 결정하도록 구성된 회로를 포함한다.

메모리 디바이스는 반도체 기판, 반도체 기판 상에 형성된 복수의 메모리 셀들, 및 반도체 기판 상에 형성되고, 복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하고, 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하고, 제1 판독 전류로부터 제1 전압을 생성하고, 제2 판독 전류로부터 제2 전압을 생성하고, 제2 전압에 제1 오프셋 값을 적용하고, 이어서 제1 전압 및 제2 전압을 조합하여 제3 전압을 형성하고, 이어서 제3 전압을 이용하여 프로그램 상태를 결정하도록 구성된 회로를 포함한다.

본 발명의 다른 목적들 및 특징들이 명세서, 청구범위 및 첨부 도면의 검토에 의해 명백해질 것이다.

도 1은 제1 종래의 분리형 게이트 비휘발성 메모리 셀의 측단면도이다.

도 2는 제2 종래의 분리형 게이트 비휘발성 메모리 셀의 측단면도이다.

도 3은 제3 종래의 분리형 게이트 비휘발성 메모리 셀의 측단면도이다.

도 4는 비휘발성 메모리 셀의 8개의 프로그램 상태에 대한 전류 대 전압 특성을 예시하는 그래프이다.

도 5a 및 도 5b는 2개의 비휘발성 메모리 셀의 8개의 프로그램 상태에 대한 전류 대 전압 특성을 예시하는 그래프들이다.

도 6a 및 도 6b는 제2 셀의 프로그램 상태들이 제1 셀의 프로그램 상태들에 대해 시프트된, 2개의 비휘발성 메모리 셀의 8개의 프로그램 상태에 대한 전류 대 전압 특성을 예시하는 그래프들이다.

도 6c는 2개의 비휘발성 메모리 셀의 8개의 프로그램 상태에 대한 전류 대 전압 특성을 집합적으로 예시하는 그래프이다.

도 7은 메모리 디바이스 아키텍처의 평면도이다.

도 8은 메모리 셀들의 어레이의 레이아웃을 예시하는 개략도이다.

도 2는 제2 종래의 분리형 게이트 비휘발성 메모리 셀의 측단면도이다.

도 3은 제3 종래의 분리형 게이트 비휘발성 메모리 셀의 측단면도이다.

도 4는 비휘발성 메모리 셀의 8개의 프로그램 상태에 대한 전류 대 전압 특성을 예시하는 그래프이다.

도 5a 및 도 5b는 2개의 비휘발성 메모리 셀의 8개의 프로그램 상태에 대한 전류 대 전압 특성을 예시하는 그래프들이다.

도 6a 및 도 6b는 제2 셀의 프로그램 상태들이 제1 셀의 프로그램 상태들에 대해 시프트된, 2개의 비휘발성 메모리 셀의 8개의 프로그램 상태에 대한 전류 대 전압 특성을 예시하는 그래프들이다.

도 6c는 2개의 비휘발성 메모리 셀의 8개의 프로그램 상태에 대한 전류 대 전압 특성을 집합적으로 예시하는 그래프이다.

도 7은 메모리 디바이스 아키텍처의 평면도이다.

도 8은 메모리 셀들의 어레이의 레이아웃을 예시하는 개략도이다.

본 발명은 각각의 메모리 셀에 1 비트 초과의 정보를 저장할 수 있는 비휘발성 메모리 디바이스들에 관한 것이다. 이는 메모리 셀들을 그의 문턱 전압 위 및/또는 아래에서 동작시킴으로써 행해질 수 있다. 예를 들어, 메모리 셀들을 완전히 프로그램하거나 완전히 소거하는 대신에, 그들은 단지 부분적으로 프로그램되거나 부분적으로 소거되고, 아날로그 방식으로 동작될 수 있다. 다음의 설명은 메모리 셀의 문턱 전압 아래에서 동작하는 메모리 셀들에 초점을 맞춘다. 그러나, 그것은 메모리 셀의 문턱 전압 위에서 동작되는 메모리 셀들에도 동등하게 적용된다.

본 발명을 가장 잘 예시하기 위해, 제어 게이트 전압의 함수로서의 채널 전류 사이의 문턱 아래(sub-threshold) 관계가 설명된다. 메모리 셀의 임의의 주어진 프로그램된 상태에 대해, 제어 게이트 전압이 점진적으로 증가함에 따라, 채널 전류는 점진적으로 상승한다. 채널 전류의 로그의 함수로서 플로팅될 때, 이 관계는 선형이다. 더욱이, 메모리 셀 프로그래밍 상태가 변경됨에 따라(예를 들어, 플로팅 게이트 상에 프로그램된 전자들의 개수가 변화함에 따라), 제어 게이트 전압의 함수로서의 전류의 선형 로그 관계가 위아래로 시프트된다.

이 관계가 도 4에 예시되어 있다. 제어 게이트 전압의 함수로서의 (채널 영역을 통한) 전류의 선형 로그 관계가 다수의 상이한 프로그램 상태에 대해 나타내어져 있다. 프로그램 상태 n=0은 메모리 셀의 가장 높은 프로그램 상태(즉, 판독 전류를 여전히 허용하는 플로팅 게이트 상의 가장 많은 전자들 - 이 지점을 넘어서의 프로그래밍은 본질적으로 메모리 셀들을 판독하는 데 사용되는 모든 제어 게이트 전압에 대해 메모리 셀 전류를 턴오프함)를 나타내고, 프로그램 상태 n=7은 메모리 셀의 가장 낮은 프로그램 상태(즉, 가장 높은 소거 상태에 대응하는, 플로팅 게이트 상의 가장 적은 전자들)를 나타낸다. 도 4에 의해 나타내어진 메모리 셀은, 그것이 8개의 상이한 상태로 프로그램될 수 있기 때문에, 이론적으로 다수 비트의 정보를 저장할 수 있다. 판독 전압 VR과 같은 하나 이상의 특정 제어 게이트 전압에서 전류를 측정함으로써, 프로그램 상태 n이 결정될 수 있다.

도 4에 나타내어진 바와 같이 n개의 프로그램 상태를 저장하도록 구성된 메모리 셀에 관한 한 가지 문제점은 상태의 개수 n이 단지 몇 개를 초과할 경우 2개의 인접한 프로그램 상태에 대한 판독 전류의 차이가 신뢰성 있는 동작에 대해 너무 작을 수 있다는 것(즉, 프로그램 상태들이 서로 너무 가까이 있음)이다. 서로 너무 가까이 있는 프로그램 상태들은 메모리 셀들의 프로그램 및/또는 판독 시에 노이즈에 취약하다. 예를 들어, 메모리 셀이 얼마나 신뢰성 있게 임의의 주어진 프로그램 상태로 프로그램될 수 있는지의 면에서 작은 변동 범위가 있을 것이다. 유사하게, 판독 전류를 측정함으로써 셀의 상태가 얼마나 신뢰성 있게 판독될 수 있는지의 면에서 작은 변동 범위가 있을 것이다. 따라서, n개의 상태들은 서로 너무 가까이 위치될 수 없고, 그렇지 않으면 그들은 서로 신뢰성 있게 구별될 수 없다. 이것은 단일 메모리 셀 내에 프로그램될 수 있는 상태의 개수 n에 실제적인 한계를 두며, 이는 메모리 디바이스에 저장될 수 있는 상태의 개수 n에 실제적인 한계가 있음을 의미한다.

도 5a 및 도 5b는 위에 설명된 문제에 대한 해결책을 예시한다. 구체적으로, 상이한 상태들 n이 다수의 메모리 셀에 걸쳐 저장될 수 있다. 예를 들어, 도 4의 단일 메모리 셀에 저장된 8개의 프로그램 상태는 2개의 상이한 셀에 저장될 수 있는데, 즉 처음 4개의 상태(n=0 내지 n=3)는 제1 셀(도 5a, 셀 1)에 저장될 수 있고, 마지막 4개의 상태(n=4 내지 n=7)는 제2 셀(도 5b, 셀 2)에 저장될 수 있다. 2개의 셀을 이용하여, 동일한 수의 총 상태가 저장될 수 있지만, 더 나은 신뢰성을 위해 인접한 프로그램 상태들 사이의 분리는 2배이다. 또는, 바꿔 말하면, 단지 하나의 셀만을 이용하는 것에 비해 2개의 메모리 셀을 이용하여 인접한 프로그램 상태들 사이에 주어진 분리를 갖고서 2배 많은 상태가 저장될 수 있다.

위에 설명된 바와 같이 2개의(또는 더 많은) 셀에 걸쳐 프로그램 상태들을 분할하는 것은 프로그램 상태 분리 문제를 해결하지만, 다른 문제를 야기한다. 이상적으로는, 설계 구성 및 동작을 단순화하기 위해, 양쪽 셀들의 판독 전류들이 함께 가산될 것이고, 조합된 판독 전류가 8개의 가능한 비트 중 어느 것(8개의 가능한 프로그램 상태 중 하나에 대응)이 메모리 셀들의 쌍 내에 프로그래밍되는지를 결정하는 데 사용된다. 그러나, 도 5a 내지 도 5b로부터 명백한 바와 같이, 상이한 셀들에서의 상이한 상태들은 동일한 전류/전압 특성을 갖는다. 예를 들어, 셀 1에서의 상태 n=0은 셀 2에서의 상태 n=4와 동일한 판독 전류 출력을 생성한다. 다른 상태들에 대해서도 그러하다(n=1과 n=5가 동일한 판독 전류를 생성하는, 등등). 따라서, 판독 전압 VR이 인가될 때 하나의 셀이 오프되도록 완전히 프로그램되더라도, 판독 전류가 어느 상태에 적용되는지를 결정할 방법이 없다. 예를 들어, 비트 값이 프로그램 상태 n=6에 대응하고, 셀 2가 n=6으로 프로그램되고 셀 1이 오프되도록 프로그램되는 경우, 나중에 그 2개의 셀로부터의 조합된 판독 전류를 다시 판독할 때, 조합된 판독 전류가 프로그램 상태 6과 대응하는지 또는 프로그램 상태 2와 대응하는지가 결정될 수 없다.

이러한 문제를 극복하기 위해, 셀 2로부터의 판독 전류에 오프셋 X가 적용되어, 셀 2로부터의 판독 전류 판독값들이 셀 1로부터의 가능한 전류 판독값들 중 임의의 것 위로 효과적으로 시프트되게 한다. 예를 들어, 셀 1에서의 상태 3에 대한 전류 레벨들이 셀 2의 판독 전류에 가산될 수 있다. 따라서, 셀 1에서의 4개의 상태에 대한 모든 가능한 판독 전류들은 셀 2에서의 4개의 상태에 대한 가능한 판독 전류들 중 어떤 것과도 겹치지 않을 것이다. 이것이 도 6a 및 도 6b에 나타내어져 있다. 따라서, 셀 1의 n=3의 프로그래밍 상태가 양쪽 셀들에 대한 최대 프로그램 상태라고 가정하면(즉, 프로그램 상태 n=3에 대해 도시된 판독 전류가 각각의 메모리 셀에 대한 최대 판독 전류임), 셀 2의 모든 가능한 프로그램 상태에 대해 셀 2에 의해 프로그래밍 상태 n=3의 판독 전류를 초과하는 겹치지 않는 판독 전류들이 제공될 수 있다. 모든 가능한 프로그램 상태(셀 1에 대해 n=0 내지 3 및 셀 2에 대해 n=4 내지 7)에 대한 양쪽 셀들에 대한 판독 전류가 도 6c에 집합적으로 도시되어 있다. 이는 2개의 셀 전류가 함께 가산된 후에 제어 게이트들 상의 단일 판독 전압 VR을 이용하여 양쪽 셀들의 프로그램 상태들이 고유하게 결정될 수 있으면서도, 프로그램 상태들이 충분히 분리된다는 것을 의미하는데, 그 이유는 셀 2에 대한 판독 전류가 그 셀에 의해 그렇지 않으면 생성될 수 있는 최대 판독 전류를 초과하도록 허용되기 때문이다. 예를 들어, 셀들의 쌍에 저장되고 있는 비트가 프로그램 상태 n=6에 대응한다면, 셀 2는 상태 n=6으로 프로그램되고, 셀 1은 오프되도록 프로그램된다. 그 후에 판독 동작 동안, n=6 상태는 다른 상태들 중 임의의 것으로부터 고유하게 판독될 수 있다. 유사하게, 셀들의 쌍에 저장되고 있는 비트가 프로그램 상태 n=1에 대응한다면, 셀 1은 상태 n=1로 프로그램되고, 셀 2는 오프되도록 프로그램된다. 그 후에 판독 동작 동안, n=1 상태는 다른 상태들 중 임의의 것으로부터 고유하게 판독될 수 있다.

셀 2에 대한 오프셋 X의 구현은 셀 2로부터의 판독 전류가 셀 1로부터의 셀 전류에 가산되기 전에 셀 2로부터의 판독 전류에 전류 오프셋 X를 가산하는 가산 회로를 이용하여 수행될 수 있다(예를 들어, 가산 회로는 셀들을 통해 전류들을 검출하는 데 사용되는 감지 증폭기의 일부임). 또는, 가산 회로는 셀 2를 통해 검출되고 있는 전류를 반영하기 위해 감지 증폭기에 의해 생성되는 전압 신호에 전압 오프셋 X를 가산할 수 있다. 이 경우에, 그것은 메모리 셀들의 쌍으로부터 어느 프로그램 상태가 판독되었는지를 조합된 전압 신호로부터 결정하기 전에 함께 가산되는 전압 신호들(검출된 전류 레벨들에 대응)일 것이다. 또는, 셀 1에 대한 전류/전압 신호에 가산되기 전에 셀 2에 대한 전류 또는 전압 신호를 곱하기 위해 승산기 회로가 감지 증폭기의 일부로서 있거나 그의 다운스트림에 있을 수 있다. 오프셋 X는, 그것이 전압 오프셋이든지 또는 전류 오프셋이든지 간에, 기준 셀(즉, 이 목적을 위해 전용되는 메모리 셀 어레이 내의 메모리 셀)에 저장될 수 있으며, 따라서 적절한 양의 오프셋이 그 주어진 다이에 대한 셀 2에 대한 전압 또는 전류 신호에 신뢰성 있게 적용된다.

예시적인 메모리 디바이스의 아키텍처가 도 7에 예시되어 있다. 메모리 디바이스는 2개의 별개의 평면(평면 A(52a) 및 평면 B(52b))으로 분리될 수 있는, 비휘발성 메모리 셀들의 어레이(50)를 포함한다. 메모리 셀들은 도 1 내지 도 3에 도시된 타입의 것이고, 단일 칩 상에 형성되고, 반도체 기판(12)에서 복수의 로우(row)들 및 컬럼(column)들로 배열될 수 있다. 비휘발성 메모리 셀들의 어레이에 어드레스 디코더들(예컨대, XDEC(54)(로우 디코더), SLDRV(56), YMUX(58)(컬럼 디코더), HVDEC(60)) 및 비트 라인 컨트롤러(BLINHCTL)(62)가 인접해 있는데, 이들은 선택된 메모리 셀들에 대한 판독, 프로그램, 및 소거 동작들 동안에 어드레스들을 디코딩하고 다양한 전압들을 다양한 메모리 셀 게이트들 및 영역들에 공급하는 데 사용된다. 컬럼 디코더(58)는 판독 동작 동안 비트 라인들 상의 전압들 또는 전류들을 측정하기 위한 감지 증폭기들을 포함한다. 컨트롤러(66)(제어 회로를 포함함)가 타깃 메모리 셀들 상에서 각각의 동작(프로그램, 소거, 판독)을 구현하도록 다양한 디바이스 요소들을 제어한다. 전하 펌프 CHRGPMP(64)가 컨트롤러(66)의 제어 하에 메모리 셀들을 판독, 프로그램 및 소거하는 데 사용되는 다양한 전압들을 제공한다. 오프셋 X 및 신호 가산은, 예를 들어, 컨트롤러(66) 내의 회로를 이용하여 구현될 수 있다. 대안적으로 또는 추가적으로, 오프셋 X 및 신호 가산은 컬럼 디코더 YMUX(58)의 감지 증폭기 부분 내의 회로를 이용하여 구현될 수 있다.

위에 설명된 실시예는 2개의 메모리 셀 및 8개의 상태 n의 맥락에서 예시되었지만, 셀들, 총 상태들 n, 및 메모리 셀당 상태들 n의 상이한 개수는 달라질 수 있다. 총 비트들, 및 그에 따라 상태들의 개수는 단순히 n개의 상태를 저장하는 데 사용되고 있는 셀의 개수를 증가시킴으로써 임의의 원하는 개수로 확대될 수 있다. 예를 들어, 3개의 셀이 사용되는 경우, 제1 오프셋이 제2 셀의 판독 전류 또는 전압에 적용되고, 제2 (상이한) 오프셋이 제3 셀의 판독 전류 또는 전압에 적용되고, 따라서 3개의 셀 모두에 대한 프로그램 상태 판독 전류들/전압들이 겹치지 않는다.

도 8은 도 1의 2-게이트 메모리 셀들에 대한 어레이 구성을 도시하며, 여기서 메모리 셀들은 로우들 및 컬럼들로 배열된다. 이러한 어레이 구성은 도 2 및 도 3의 메모리 셀들에 동등하게 적용되며, 이에 의해 추가 게이트들에 대해 추가 라인들이 추가될 것이다. 워드 라인들 WL은 각각 메모리 셀들의 하나의 로우에 대한 제어 게이트들에 연결된다. 비트 라인들 BL은 각각 메모리 셀들의 하나의 컬럼에 대한 드레인 영역들에 연결된다. 소스 라인들 SL은 각각 메모리 셀들의 쌍의 하나의 로우에 대한 소스 영역들에 연결된다. 바람직하게는, 그의 판독 전류들 또는 전압들이 함께 가산된 셀들 각각은 상이한 컬럼들에 배치되고 따라서 판독 프로세스가 더 빠르다. 따라서, 2개의 메모리 셀이 사용되는 위의 예에 대해, 셀 1은 비트 라인 BL0에 연결된 컬럼 1에 있을 것이고, 셀 2는 비트 라인 BL1에 연결된 컬럼 2에 있을 것이다. 판독 동작 동안, 셀 1에 대한 판독 전류는 비트 라인 BL0 상에서 검출되고 셀 2에 대한 판독 전류는 비트 라인 BL1 상에서 검출된다. 감지 증폭기들 내에 있는 또는 그로부터 다운스트림에 있는 회로가 비트 라인 BL1 상의 판독 전류(또는 그에 대응하는 전압)에 오프셋 X를 가산하고 이어서 양쪽 셀들로부터의 판독 전류들(또는 전압들)을 서로 가산하고 이어서 조합된 판독 전류/전압으로부터 메모리 셀들의 쌍에 어느 프로그램 상태가 프로그램되는지를 결정할 것이다.

본 발명은 본 명세서에 예시되고 전술된 실시예(들)로 제한되지 않는다는 것이 이해되어야 한다. 예를 들어, 본 명세서에서 본 발명에 대한 언급은 임의의 청구항 또는 청구항 용어의 범위를 제한하는 것이 아니라, 대신에 단지 하나 이상의 청구항에 의해 커버될 수 있는 하나 이상의 특징들에 대해 언급하는 것으로 의도된다. 본 발명은 메모리 셀들의 문턱 아래 동작에 관하여 설명되지만, 그것은 문턱 위에서 동작되는 메모리 셀들에서 구현될 수 있다(그 경우에 전류와 전압 사이의 로그 관계는 더 이상 적용되지 않을 수 있다). 셀을 도면들에 도시된 그의 가장 높은 프로그램 상태로 프로그래밍하는 것은 실제로 가장 높은 프로그램 상태가 완전히 소거된 메모리 셀인 소거 동작을 수반한다는 점에 유의해야 한다. 오프셋 X를 적용하는 것은 위에서 양 X만큼 전류 또는 전압의 값에 가산하는 것(그 값을 증가시키는 것)에 의해 개시되어 있다. 그러나, 오프셋 X를 적용하는 것은 네거티브 오프셋을 포함할 수 있으며, 이는 양 X만큼 전류 또는 전압의 값으로부터 감산하는 것(그 값을 감소시키는 것)에 의해 달성될 수 있다. 전술된 재료들, 프로세스들, 및 수치 예들은 단지 예시적인 것일 뿐이며, 청구항들을 제한하는 것으로 간주되어서는 안된다. 또한, 청구항들 및 명세서로부터 명백한 바와 같이, 모든 방법 단계들이 예시된 정확한 순서로 수행될 필요는 없다. 마지막으로, 재료의 단일 층들이 그러한 또는 유사한 재료들의 다수의 층들로서 형성될 수 있고, 그 반대도 마찬가지이다.

본 명세서에 사용된 바와 같이, 용어들 "~ 위에" 및 "~ 상에" 둘 모두는 "직접적으로 ~ 상에"(어떠한 중간 재료들, 요소들 또는 공간도 사이에 배치되지 않음)와 "간접적으로~ 상에"(중간 재료들, 요소들 또는 공간이 사이에 배치됨)를 포괄적으로 포함한다는 것에 유의하여야 한다. 마찬가지로, 용어 "인접한"은 "직접적으로 인접한"(어떠한 중간 재료들, 요소들 또는 공간도 사이에 배치되지 않음)과 "간접적으로 인접한"(중간 재료들, 요소들 또는 공간이 사이에 배치됨)을 포함하고, "~에 실장되는"은 "직접적으로 ~에 실장되는"(어떠한 중간 재료들, 요소들 또는 공간도 사이에 배치되지 않음)과 "간접적으로 ~에 실장되는"(중간 재료들, 요소들 또는 공간이 사이에 배치됨)을 포함하고, "전기적으로 커플링되는"은 "직접적으로 ~에 전기적으로 커플링되는"(요소들을 함께 전기적으로 접속시키는 어떠한 중간 재료들 또는 요소들도 사이에 없음)과 "간접적으로 ~에 전기적으로 커플링되는"(요소들을 함께 전기적으로 접속시키는 중간 재료들 또는 요소들이 사이에 있음)을 포함한다. 예를 들어, "기판 위에" 요소를 형성하는 것은 어떠한 중간 재료들/요소들도 사이에 갖지 않고서 직접적으로 기판 상에 요소를 형성하는 것뿐만 아니라, 하나 이상의 중간 재료들/요소들을 사이에 갖고서 간접적으로 기판 상에 요소를 형성하는 것을 포함할 수 있다.

Claims (24)

- 복수의 메모리 셀들을 갖는 메모리 디바이스를 판독하는 방법으로서,

상기 복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하는 단계;

상기 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하는 단계;

상기 제2 판독 전류에 제1 오프셋 값을 적용하는 단계; 이어서

상기 제1 판독 전류와 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 조합하여 제3 판독 전류를 형성하는 단계; 및 이어서

상기 제3 판독 전류를 이용하여 제1 및 제 2 메모리 셀의 프로그램 상태를 결정하는 단계를 포함하는, 방법. - 제1항에 있어서, 제3 판독 전류를 형성하기 위해 상기 제1 판독 전류와 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 조합하는 단계는 상기 제1 판독 전류 및 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 함께 가산하는 단계를 포함하는, 방법.

- 제1항에 있어서,

상기 복수의 메모리 셀들 중 제3 메모리 셀을 판독하여 제4 판독 전류를 생성하는 단계;

상기 제4 판독 전류에 제2 오프셋 값을 적용하는 단계를 추가로 포함하며,

상기 제3 판독 전류를 형성하기 위해 상기 제1 판독 전류와 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 조합하는 단계는 상기 제1 판독 전류, 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류, 및 상기 제2 오프셋 값을 갖는 상기 제4 판독 전류를 조합하여 상기 제3 판독 전류를 형성하는 단계를 포함하는, 방법. - 제3항에 있어서, 상기 제2 오프셋 값은 상기 제1 오프셋 값과는 상이한, 방법.

- 제3항에 있어서, 상기 제3 판독 전류를 형성하기 위해 상기 제1 판독 전류와 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 조합하는 단계는 상기 제1 판독 전류, 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류, 및 상기 제2 오프셋 값을 갖는 상기 제4 판독 전류를 함께 가산하는 단계를 포함하는, 방법.

- 제1항에 있어서, 상기 복수의 메모리 셀들은 상기 메모리 셀들의 로우(row)들 및 컬럼(column)들의 어레이로 배열되고, 상기 컬럼들 각각은 상기 컬럼들 각각 내의 상기 메모리 셀들에 연결된 비트 라인을 포함하고, 상기 제1 메모리 셀은 상기 컬럼들 중 제1 컬럼에 배치되고, 상기 제2 메모리 셀은 상기 컬럼들 중 상기 제1 컬럼과는 상이한 상기 컬럼들 중 제2 컬럼에 배치되는, 방법.

- 복수의 메모리 셀들을 갖는 메모리 디바이스를 판독하는 방법으로서,

상기 복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하는 단계;

상기 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하는 단계;

상기 제1 판독 전류로부터 제1 전압을 생성하는 단계;

상기 제2 판독 전류로부터 제2 전압을 생성하는 단계;

상기 제2 전압에 제1 오프셋 값을 적용하는 단계; 이어서

상기 제1 전압과 상기 제1 오프셋 값을 갖는 상기 제2 전압을 조합하여 제3 전압을 형성하는 단계; 및 이어서

상기 제3 전압을 이용하여 제1 및 제 2 메모리 셀의 프로그램 상태를 결정하는 단계를 포함하는, 방법. - 제7항에 있어서, 상기 제1 전압과 상기 제1 오프셋 값을 갖는 상기 제2 전압을 조합하는 단계는 상기 제1 전압 및 상기 제1 오프셋 값을 갖는 상기 제2 전압을 함께 가산하는 단계를 포함하는, 방법.

- 제7항에 있어서,

상기 복수의 메모리 셀들 중 제3 메모리 셀을 판독하여 제3 판독 전류를 생성하는 단계;

상기 제3 판독 전류로부터 제4 전압을 생성하는 단계;

상기 제4 전압에 제2 오프셋 값을 적용하는 단계를 추가로 포함하며,

제3 전압을 형성하기 위해 상기 제1 전압과 상기 제1 오프셋 값을 갖는 상기 제2 전압을 조합하는 단계는 상기 제1 전압, 상기 제1 오프셋 값을 갖는 상기 제2 전압, 및 상기 제2 오프셋 값을 갖는 상기 제4 전압을 조합하여 상기 제3 전압을 형성하는 단계를 포함하는, 방법. - 제9항에 있어서, 상기 제2 오프셋 값은 상기 제1 오프셋 값과는 상이한, 방법.

- 제9항에 있어서, 제3 전압을 형성하기 위해 상기 제1 전압과 상기 제1 오프셋 값을 갖는 상기 제2 전압을 조합하는 단계는 상기 제1 전압, 상기 제1 오프셋 값을 갖는 상기 제2 전압, 및 상기 제2 오프셋 값을 갖는 상기 제4 전압을 함께 가산하는 단계를 포함하는, 방법.

- 제7항에 있어서, 상기 복수의 메모리 셀들은 상기 메모리 셀들의 로우들 및 컬럼들의 어레이로 배열되고, 상기 컬럼들 각각은 상기 컬럼들 각각 내의 상기 메모리 셀들에 연결된 비트 라인을 포함하고, 상기 제1 메모리 셀은 상기 컬럼들 중 제1 컬럼에 배치되고, 상기 제2 메모리 셀은 상기 컬럼들 중 상기 제1 컬럼과는 상이한 상기 컬럼들 중 제2 컬럼에 배치되는, 방법.

- 메모리 디바이스로서,

반도체 기판;

상기 반도체 기판 상에 형성된 복수의 메모리 셀들; 및

상기 반도체 기판 상에 형성되고,

상기 복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하고,

상기 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하고,

상기 제2 판독 전류에 제1 오프셋 값을 적용하고, 이어서

상기 제1 판독 전류와 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 조합하여 제3 판독 전류를 형성하고, 이어서

상기 제3 판독 전류를 이용하여 제1 및 제 2 메모리 셀의 프로그램 상태를 결정하도록

구성된 회로를 포함하는, 디바이스. - 제13항에 있어서, 상기 제3 판독 전류를 형성하기 위해 상기 제1 판독 전류와 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 조합하는 것은 상기 제1 판독 전류 및 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 함께 가산하는 것을 포함하는, 디바이스.

- 제13항에 있어서, 상기 회로는,

상기 복수의 메모리 셀들 중 제3 메모리 셀을 판독하여 제4 판독 전류를 생성하고,

상기 제4 판독 전류에 제2 오프셋 값을 적용하도록 추가로 구성되고,

상기 제3 판독 전류를 형성하기 위해 상기 제1 판독 전류와 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 조합하는 것은 상기 제1 판독 전류, 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류, 및 상기 제2 오프셋 값을 갖는 상기 제4 판독 전류를 조합하여 상기 제3 판독 전류를 형성하는 것을 포함하는, 디바이스. - 제15항에 있어서, 상기 제2 오프셋 값은 상기 제1 오프셋 값과는 상이한, 디바이스.

- 제15항에 있어서, 상기 제3 판독 전류를 형성하기 위해 상기 제1 판독 전류와 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류를 조합하는 것은 상기 제1 판독 전류, 상기 제1 오프셋 값을 갖는 상기 제2 판독 전류, 및 상기 제2 오프셋 값을 갖는 상기 제4 판독 전류를 함께 가산하는 것을 포함하는, 디바이스.

- 제13항에 있어서,

상기 복수의 메모리 셀들은 상기 메모리 셀들의 로우들 및 컬럼들의 어레이로 배열되고,

상기 컬럼들 각각은 상기 컬럼들 각각 내의 상기 메모리 셀들에 연결된 비트 라인을 포함하고,

상기 제1 메모리 셀은 상기 컬럼들 중 제1 컬럼에 배치되고,

상기 제2 메모리 셀은 상기 컬럼들 중 상기 제1 컬럼과는 상이한 상기 컬럼들 중 제2 컬럼에 배치되는, 디바이스. - 메모리 디바이스로서,

반도체 기판;

상기 반도체 기판 상에 형성된 복수의 메모리 셀들; 및

상기 반도체 기판 상에 형성되고,

상기 복수의 메모리 셀들 중 제1 메모리 셀을 판독하여 제1 판독 전류를 생성하고,

상기 복수의 메모리 셀들 중 제2 메모리 셀을 판독하여 제2 판독 전류를 생성하고,

상기 제1 판독 전류로부터 제1 전압을 생성하고,

상기 제2 판독 전류로부터 제2 전압을 생성하고,

상기 제2 전압에 제1 오프셋 값을 적용하고, 이어서

상기 제1 전압과 상기 제1 오프셋 값을 갖는 상기 제2 전압을 조합하여 제3 전압을 형성하고, 이어서

상기 제3 전압을 이용하여 제1 및 제 2 메모리 셀의 프로그램 상태를 결정하도록

구성된 회로를 포함하는, 디바이스. - 제19항에 있어서, 제3 전압을 형성하기 위해 상기 제1 전압과 상기 제1 오프셋 값을 갖는 상기 제2 전압을 조합하는 것은 상기 제1 전압 및 상기 제1 오프셋 값을 갖는 상기 제2 전압을 함께 가산하는 것을 포함하는, 디바이스.

- 제19항에 있어서, 상기 회로는,

상기 복수의 메모리 셀들 중 제3 메모리 셀을 판독하여 제3 판독 전류를 생성하고,

상기 제3 판독 전류로부터 제4 전압을 생성하고,

상기 제4 전압에 제2 오프셋 값을 적용하도록 추가로 구성되고,

제3 전압을 형성하기 위해 상기 제1 전압과 상기 제1 오프셋 값을 갖는 상기 제2 전압을 조합하는 것은 상기 제1 전압, 상기 제1 오프셋 값을 갖는 상기 제2 전압, 및 상기 제2 오프셋 값을 갖는 상기 제4 전압을 조합하여 상기 제3 전압을 형성하는 것을 포함하는, 디바이스. - 제21항에 있어서, 상기 제2 오프셋 값은 상기 제1 오프셋 값과는 상이한, 디바이스.

- 제21항에 있어서, 제3 전압을 형성하기 위해 상기 제1 전압과 상기 제1 오프셋 값을 갖는 상기 제2 전압을 조합하는 것은 상기 제1 전압, 상기 제1 오프셋 값을 갖는 상기 제2 전압, 및 상기 제2 오프셋 값을 갖는 상기 제4 전압을 함께 가산하는 것을 포함하는, 디바이스.

- 제19항에 있어서,

상기 복수의 메모리 셀들은 상기 메모리 셀들의 로우들 및 컬럼들의 어레이로 배열되고,

상기 컬럼들 각각은 상기 컬럼들 각각 내의 상기 메모리 셀들에 연결된 비트 라인을 포함하고,

상기 제1 메모리 셀은 상기 컬럼들 중 제1 컬럼에 배치되고,

상기 제2 메모리 셀은 상기 컬럼들 중 상기 제1 컬럼과는 상이한 상기 컬럼들 중 제2 컬럼에 배치되는, 디바이스.

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201762581489P | 2017-11-03 | 2017-11-03 | |

| US62/581,489 | 2017-11-03 | ||

| US16/148,304 US10515694B2 (en) | 2017-11-03 | 2018-10-01 | System and method for storing multibit data in non-volatile memory |

| US16/148,304 | 2018-10-01 | ||

| PCT/US2018/053930 WO2019089168A1 (en) | 2017-11-03 | 2018-10-02 | System and method for storing multibit data in non-volatile memory |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20200043501A KR20200043501A (ko) | 2020-04-27 |

| KR102199607B1 true KR102199607B1 (ko) | 2021-01-08 |

Family

ID=66327523

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020207010818A KR102199607B1 (ko) | 2017-11-03 | 2018-10-02 | 비휘발성 메모리에 멀티비트 데이터를 저장하기 위한 시스템 및 방법 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US10515694B2 (ko) |

| EP (1) | EP3704700B1 (ko) |

| JP (1) | JP6970826B2 (ko) |

| KR (1) | KR102199607B1 (ko) |

| CN (1) | CN111344791B (ko) |

| TW (1) | TWI682393B (ko) |

| WO (1) | WO2019089168A1 (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100671698B1 (ko) * | 2004-08-05 | 2007-01-18 | 매그나칩 반도체 유한회사 | 엘디아이 내 디지털 아날로그 변환기의 테스트 장치 |

| KR20230080156A (ko) | 2021-11-29 | 2023-06-07 | 충남대학교산학협력단 | 멀티 레벨 구동이 가능한 메모리 소자 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10991433B2 (en) * | 2019-09-03 | 2021-04-27 | Silicon Storage Technology, Inc. | Method of improving read current stability in analog non-volatile memory by limiting time gap between erase and program |

| US11682459B2 (en) | 2020-05-13 | 2023-06-20 | Silicon Storage Technology, Inc. | Analog neural memory array in artificial neural network comprising logical cells and improved programming mechanism |

| US12080355B2 (en) | 2021-06-02 | 2024-09-03 | Silicon Storage Technology, Inc. | Method of improving read current stability in analog non-volatile memory by post-program tuning for memory cells exhibiting random telegraph noise |

| US11769558B2 (en) | 2021-06-08 | 2023-09-26 | Silicon Storage Technology, Inc. | Method of reducing random telegraph noise in non-volatile memory by grouping and screening memory cells |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20150085571A1 (en) | 2013-09-24 | 2015-03-26 | Sandisk Technologies Inc. | Updating read voltages |

| US20160064058A1 (en) | 2014-08-29 | 2016-03-03 | Everspin Technologies, Inc. | Configuration and testing for magnetoresistive memory |

| US20160148701A1 (en) | 2014-11-20 | 2016-05-26 | HGST Netherlands B.V. | Read level grouping algorithms for increased flash performance |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5029130A (en) | 1990-01-22 | 1991-07-02 | Silicon Storage Technology, Inc. | Single transistor non-valatile electrically alterable semiconductor memory device |

| JP2812202B2 (ja) * | 1994-06-27 | 1998-10-22 | ヤマハ株式会社 | 半導体記憶装置 |

| KR100324594B1 (ko) | 1999-06-28 | 2002-02-16 | 박종섭 | 강유전체 메모리 장치 |

| US7082056B2 (en) | 2004-03-12 | 2006-07-25 | Super Talent Electronics, Inc. | Flash memory device and architecture with multi level cells |

| US7324374B2 (en) | 2003-06-20 | 2008-01-29 | Spansion Llc | Memory with a core-based virtual ground and dynamic reference sensing scheme |

| US7315056B2 (en) | 2004-06-07 | 2008-01-01 | Silicon Storage Technology, Inc. | Semiconductor memory array of floating gate memory cells with program/erase and select gates |

| US7554856B2 (en) * | 2006-10-06 | 2009-06-30 | Qimonda Flash Gmbh & Co. Kg | Memory cell |

| US20090039410A1 (en) | 2007-08-06 | 2009-02-12 | Xian Liu | Split Gate Non-Volatile Flash Memory Cell Having A Floating Gate, Control Gate, Select Gate And An Erase Gate With An Overhang Over The Floating Gate, Array And Method Of Manufacturing |

| US8238149B2 (en) | 2009-06-25 | 2012-08-07 | Macronix International Co., Ltd. | Methods and apparatus for reducing defect bits in phase change memory |

| JP2012209004A (ja) | 2011-03-30 | 2012-10-25 | Toshiba Corp | 半導体記憶装置 |

| US9099202B2 (en) * | 2012-11-06 | 2015-08-04 | Sandisk Technologies Inc. | 3D stacked non-volatile storage programming to conductive state |

| KR102043723B1 (ko) | 2013-02-28 | 2019-12-02 | 에스케이하이닉스 주식회사 | 반도체 장치 및 이를 포함하는 프로세서와 시스템 |

| CN105027216B (zh) | 2013-03-14 | 2017-09-22 | 硅存储技术公司 | 非易失性存储器编程算法装置和方法 |

| US9484094B2 (en) | 2015-01-21 | 2016-11-01 | Ememory Technology Inc. | Control method of resistive random-access memory |

-

2018

- 2018-10-01 US US16/148,304 patent/US10515694B2/en active Active

- 2018-10-02 EP EP18872824.0A patent/EP3704700B1/en active Active

- 2018-10-02 KR KR1020207010818A patent/KR102199607B1/ko active IP Right Grant

- 2018-10-02 WO PCT/US2018/053930 patent/WO2019089168A1/en unknown

- 2018-10-02 CN CN201880068646.XA patent/CN111344791B/zh active Active

- 2018-10-02 JP JP2020524440A patent/JP6970826B2/ja active Active

- 2018-10-24 TW TW107137607A patent/TWI682393B/zh active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20150085571A1 (en) | 2013-09-24 | 2015-03-26 | Sandisk Technologies Inc. | Updating read voltages |

| US20160064058A1 (en) | 2014-08-29 | 2016-03-03 | Everspin Technologies, Inc. | Configuration and testing for magnetoresistive memory |

| US20160148701A1 (en) | 2014-11-20 | 2016-05-26 | HGST Netherlands B.V. | Read level grouping algorithms for increased flash performance |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100671698B1 (ko) * | 2004-08-05 | 2007-01-18 | 매그나칩 반도체 유한회사 | 엘디아이 내 디지털 아날로그 변환기의 테스트 장치 |

| KR20230080156A (ko) | 2021-11-29 | 2023-06-07 | 충남대학교산학협력단 | 멀티 레벨 구동이 가능한 메모리 소자 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2019089168A1 (en) | 2019-05-09 |

| CN111344791A (zh) | 2020-06-26 |

| TW201931370A (zh) | 2019-08-01 |

| JP6970826B2 (ja) | 2021-11-24 |

| EP3704700B1 (en) | 2022-07-20 |

| KR20200043501A (ko) | 2020-04-27 |

| CN111344791B (zh) | 2021-06-25 |

| JP2021501956A (ja) | 2021-01-21 |

| EP3704700A4 (en) | 2021-07-21 |

| EP3704700A1 (en) | 2020-09-09 |

| TWI682393B (zh) | 2020-01-11 |

| US20190139602A1 (en) | 2019-05-09 |

| US10515694B2 (en) | 2019-12-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102199607B1 (ko) | 비휘발성 메모리에 멀티비트 데이터를 저장하기 위한 시스템 및 방법 | |

| TW201832241A (zh) | 減少在非揮發記憶體單元中的程式干擾的方法 | |

| US10699787B2 (en) | System and method for minimizing floating gate to floating gate coupling effects during programming in flash memory | |

| US10878897B2 (en) | System and method for storing and retrieving multibit data in non-volatile memory using current multipliers | |

| CN111095410B (zh) | 通过优化编程操作来执行推理引擎的系统和方法 | |

| KR102282580B1 (ko) | 비휘발성 메모리 어레이에서 피크 전력 요구 및 잡음을 관리하기 위한 시스템 및 방법 | |

| KR20230163580A (ko) | 메모리 셀들을 그룹화하고 스크리닝함으로써 비휘발성 메모리에서 랜덤 텔레그래프 잡음을 감소시키는 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A302 | Request for accelerated examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |