KR101341912B1 - 표시장치용 구동회로 - Google Patents

표시장치용 구동회로 Download PDFInfo

- Publication number

- KR101341912B1 KR101341912B1 KR1020090091234A KR20090091234A KR101341912B1 KR 101341912 B1 KR101341912 B1 KR 101341912B1 KR 1020090091234 A KR1020090091234 A KR 1020090091234A KR 20090091234 A KR20090091234 A KR 20090091234A KR 101341912 B1 KR101341912 B1 KR 101341912B1

- Authority

- KR

- South Korea

- Prior art keywords

- transmission line

- logic power

- driving

- data

- input pin

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2085—Special arrangements for addressing the individual elements of the matrix, other than by driving respective rows and columns in combination

- G09G3/2088—Special arrangements for addressing the individual elements of the matrix, other than by driving respective rows and columns in combination with use of a plurality of processors, each processor controlling a number of individual elements of the matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0232—Special driving of display border areas

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

- G09G2330/023—Power management, e.g. power saving using energy recovery or conservation

- G09G2330/024—Power management, e.g. power saving using energy recovery or conservation with inductors, other than in the electrode driving circuitry of plasma displays

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2092—Details of a display terminals using a flat panel, the details relating to the control arrangement of the display terminal and to the interfaces thereto

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal (AREA)

- Liquid Crystal Display Device Control (AREA)

- Control Of El Displays (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Abstract

본 발명은 블록 딤(block dim) 및 노이즈 현상을 방지하여 화질을 향상시킬 수 있는 표시장치의 구동회로에 관한 것으로, 패널의 표시부에 화상을 표시하는데 필요한 각종 신호들을 생성하는 구동 집적회로; 상기 구동 집적회로가 실장되는 실장영역 및 상기 구동 집적회로의 입력핀들을 외부 시스템에 접속시키기 위한 다수의 입력패턴들 및 상기 구동 집적회로의 출력핀들을 패널에 접속시키기 위한 다수의 출력패턴들이 형성된 표면 실장형 패키지; 상기 입력패턴들 중 외부 시스템으로부터의 논리 전원을 전송하는 적어도 하나의 논리전원입력패턴; 상기 입력핀들 중 상기 논리전원입력패턴에 접속된 적어도 하나의 논리전원입력핀; 상기 논리전원입력핀에 접속되며, 상기 구동 집적회로의 내부에 형성되어 상기 논리 전원을 전송하는 논리전원전송라인; 상기 논리전원전송라인에 병렬로 접속되며, 상기 구동 집적회로의 내부에 형성되어 상기 논리전원전송라인으로부터의 논리 전원에 의해 동작하는 다수의 데이터 구동부들; 상기 실장영역에 형성되며, 일측이 상기 논리전원입력패턴에 접속된 적어도 하나의 외부 보조전송라인; 상기 구동 집적회로의 내부에 형성되며, 일측이 적어도 하나의 데이터 구동부에 접속된 적어도 하나의 내부 보조전송라인; 및, 상기 내부 보조전송라인의 타측과 상기 외부 보조전송라인의 타측간을 연결하며, 상기 구동집적 회로에 설치된 적어도 하나의 보조입력핀을 포함함을 특징으로 한다.

표시장치, 블록 딤, 데이터 구동부, 구동 집적회로, 논리 전원

Description

본 발명은 표시장치용 구동회로에 관한 것으로, 특히 구동 집적회로의 가장자리에 위치한 데이터 구동부에 추가적으로 전원을 공급함으로써 화면의 가장자리에 블록 딤(block dim) 및 노이즈 현상을 방지하여 화질을 향상시킬 수 있는 표시장치의 구동회로에 대한 것이다.

구동 집적회로내에는 패널내의 데이터 라인들에 화상 데이터들을 공급하기 위한 다수의 데이터 구동부들이 구성된다. 이들 데이터 구동부들은 논리 전원을 공급받아 구동되는데, 이들 데이터 구동부들 중 논리 전원이 공급되는 입력핀으로부터 가장 멀리 위치한 데이터 구동부에 공급되는 논리 전원은 나머지 데이터 구동부들에 비하여 큰 왜곡을 갖는다. 따라서 구동 집적회로의 가장자리에 위치한 데이터 구동부로부터 출력되는 화상 데이터들 역시 왜곡된 형태를 나타내며, 이러한 왜곡된 화상 데이터들이 공급되는 화면의 가장자리가 다른 화면 부분에 비하여 화상이 두드러져 보임에 따라 화면이 분할되어 보이는 블록 딤(block dim) 및 화면 노이즈 현상이 발생하게 된다. 즉, 종래에는 이러한 블록 딤 및 화면 노이즈가 발생되어 화질이 저하되는 문제점이 있었다.

본 발명은 상기와 같은 문제점을 해결하기 위하여 안출한 것으로, 구동 집적회로의 양측 가장자리에 위치한 2개의 데이터 구동부에 외부 보조전송라인, 보조 입력핀 및 내부 보조전송라인을 경유하여 전송되는 논리 전원을 추가적으로 공급함으로써 양측 가장자리에 위치한 데이터 구동부에 최종적으로 공급되는 논리 전원의 왜곡의 크기의 감소를 방지할 수 있는 표시장치용 구동회로를 제공하는데 그 목적이 있다.

상기와 같은 목적을 달성하기 위한 본 발명에 따른 표시장치용 구동회로는, 패널의 표시부에 화상을 표시하는데 필요한 각종 신호들을 생성하는 구동 집적회로; 상기 구동 집적회로가 실장되는 실장영역 및 상기 구동 집적회로의 입력핀들을 외부 시스템에 접속시키기 위한 다수의 입력패턴들 및 상기 구동 집적회로의 출력핀들을 패널에 접속시키기 위한 다수의 출력패턴들이 형성된 표면 실장형 패키지; 상기 입력패턴들 중 외부 시스템으로부터의 논리 전원을 전송하는 적어도 하나의 논리전원입력패턴; 상기 입력핀들 중 상기 논리전원입력패턴에 접속된 적어도 하나의 논리전원입력핀; 상기 논리전원입력핀에 접속되며, 상기 구동 집적회로의 내부에 형성되어 상기 논리 전원을 전송하는 논리전원전송라인; 상기 논리전원전송라인에 병렬로 접속되며, 상기 구동 집적회로의 내부에 형성되어 상기 논리전원전송라인으로부터의 논리 전원에 의해 동작하는 다수의 데이터 구동부들; 상기 실장영역 에 형성되며, 일측이 상기 논리전원입력패턴에 접속된 적어도 하나의 외부 보조전송라인; 상기 구동 집적회로의 내부에 형성되며, 일측이 적어도 하나의 데이터 구동부에 접속된 적어도 하나의 내부 보조전송라인; 및, 상기 내부 보조전송라인의 타측과 상기 외부 보조전송라인의 타측간을 연결하며, 상기 구동집적 회로에 설치된 적어도 하나의 보조입력핀을 포함함을 특징으로 한다.

상기 구동 집적회로는 상기 다수의 데이터 구동부들의 동작을 제어하기 위한 구동 제어부를 더 포함하며; 상기 구동 제어부는 상기 논리전원전송라인에 접속되며; n개(n은 6이상의 짝수)의 데이터 구동부들은 상기 구동 제어부를 중심으로 하여 이 구동 제어부의 양측에 n/2개씩 나누어 배열되며; 상기 외부 보조전송라인이 제 1 및 제 2 외부 보조전송라인을 포함하며; 상기 내부 보조전송라인이 제 1 및 제 2 내부 보조전송라인을 포함하며; 상기 보조입력핀이 제 1 및 제 2 보조 입력핀을 포함하며; 상기 제 1 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 1 보조 입력핀에 접속되며; 상기 제 1 내부 보조전송라인의 일측이 구동 제어부의 일측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 가장 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 1 보조 입력핀에 접속되며; 상기 제 2 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 2 보조 입력핀에 접속되며; 상기 제 2 내부 보조전송라인의 일측이 구동 제어부의 타측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 가장 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 2 보조 입력핀에 접속됨을 특징으로 한다.

상기 구동 집적회로는 각 데이터 구동부 사이에 위치한 신호지연/완충부를 더 포함하며; 상기 구동 제어부로부터 출력된 소스아웃풋인에이블신호는 상기 신호지연/완충부를 통해 상기 구동 제어부의 일측에 위치한 n/2개의 데이터 구동부들에 순차적으로 공급됨과 아울러, 상기 구동 제어부의 타측에 위치한 n/2개의 데이터 구동부들에 순차적으로 공급되며; 각 데이터 구동부는 상기 소스아웃풋인에이블신호에 응답하여 샘플링된 화상 데이터들을 동시에 출력하는 것을 특징으로 한다.

상기 구동 제어부는, 외부 시스템으로부터의 화상 데이터들을 재정렬하여 출력하는 데이터 정렬부; 상기 데이터 정렬부로부터의 화상 데이터들을 순차적으로 샘플링 및 홀딩하는 샘플/홀딩부; 및, 외부 시스템으로부터 제어신호를 공급받아 상기 소스아웃풋인에이블신호를 포함한 각종 타이밍 제어신호를 출력하는 제어신호생성부를 포함함을 특징으로 한다.

각 데이터 구동부는, 상기 샘플/홀딩부로부터의 m개(m=k*n; k는 4이상의 자연수)의 샘플링된 화상 데이터들 중 m/n개의 샘플링된 화상 데이터들을 동시에 공급받고, 상기 소스아웃풋인에이블신호에 응답하여 m/n개의 샘플링된 화상 데이터들을 동시에 출력하는 래치부; 상기 래치부로부터의 m/n개의 샘플링된 화상 데이터들을 아날로그 신호로 변환하는 디지털-아날로그 변환부; 및, 상기 디지털-아날로그 변환부로부터의 샘플링된 화상 데이터들을 버퍼링하여 출력하는 신호완충부를 포함함을 특징으로 한다.

상기 구동 집적회로는 상기 다수의 데이터 구동부들의 동작을 제어하기 위한 구동 제어부를 더 포함하며; 상기 구동 제어부는 상기 논리전원전송라인에 접속되 며; n개(n은 4이상의 자연수)의 데이터 구동부들은 상기 구동 제어부를 중심으로 하여 이 구동 제어부의 양측에 n/2개씩 나누어 배열되며; 상기 외부 보조전송라인이 제 1 내지 제 4 외부 보조전송라인으로 구성되며; 상기 내부 보조전송라인이 제 1 내지 제 4 내부 보조전송라인으로 구성되며; 상기 보조입력핀이 제 1 내지 제 4 보조 입력핀으로 구성되며; 상기 제 1 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 1 보조 입력핀에 접속되며; 상기 제 1 내부 보조전송라인의 일측이 구동 제어부의 일측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 가장 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 1 보조 입력핀에 접속되며; 상기 제 2 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 2 보조 입력핀에 접속되며; 상기 제 2 내부 보조전송라인의 일측이 구동 제어부의 타측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 가장 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 2 보조 입력핀에 접속되며; 상기 제 3 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 3 보조 입력핀에 접속되며; 상기 제 3 내부 보조전송라인의 일측이 구동 제어부의 일측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 두 번째로 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 3 보조 입력핀에 접속되며; 상기 제 4 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 4 보조 입력핀에 접속되며; 상기 제 4 내부 보조전송라인의 일측이 구동 제어부의 타측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 두 번째로 멀리 위치한 데이터 구동부 에 접속되고, 타측이 상기 제 4 보조 입력핀에 접속됨을 특징으로 한다.

본 발명에 따른 표시장치용 구동회로는 다음과 같은 효과를 갖는다.

본 발명에서는 구동 집적회로의 양측 가장자리에 위치한 2개의 데이터 구동부에 외부 보조전송라인, 보조 입력핀 및 내부 보조전송라인을 경유하여 전송되는 논리 전원을 추가적으로 공급함으로써 양측 가장자리에 위치한 데이터 구동부에 최종적으로 공급되는 논리 전원의 왜곡의 크기의 감소시킬 수 있다.

따라서 종래의 블록 딤 및 화면 노이즈 현상에 의한 화질 저하를 방지할 수 있다.

도 1은 본 발명의 실시예에 따른 표시장치용 구동회로(DRC)를 나타낸 도면이다.

도 1에 도시된 표시장치는 크게 화상을 표시하기 위한 화상을 표시하기 위한 표시부(D) 및 이 표시부(D) 둘레의 비표시부(ND)를 포함하는 패널(PN)과, 상기 패널(PN)의 표시부(D)에 화상을 표시하는데 필요한 각종 신호들을 생성하는 구동 집적회로(D-IC) 및 구동 집적회로(D-IC)가 실장된 표면 실장형 패키지(TCP)를 포함하는 구동회로(DRC)를 갖는다.

표면 실장형 패키지(TCP)는 테입 캐리어 패키지(Tape Carrier Package)가 사용될 수 있다.

구동회로(DRC)의 일측은 인쇄회로기판(PCB)에 접속되며, 이 구동회로(DRC)의 타측은 패널(PN)의 비표시부(ND)에 접속된다. 이 패널(PN)은 액정을 포함하는 패널 또는 유기발광다이오드를 포함하는 패널 등이 될 수 있다.

인쇄회로기판(PCB)은 도시하지 않은 외부 시스템과 접속되는 바, 이 외부 시스템으로부터의 화상 데이터 및 각종 제어신호들은 이 인쇄회로기판(PCB)을 통하여 구동회로(DRC)에 공급된다.

패널(PN)의 표시부(D)에는 서로 교차하는 다수의 게이트 라인(GL)들 및 데이터 라인(DL)들과, 그리고 이 게이트 라인(GL)들로부터의 게이트 신호 및 데이터 라인(DL)들로부터의 화상 데이터에 따라 화상을 표시하는 화소들이 형성된다.

이 패널(PN)의 비표시부(ND)에는 구동회로(DRC)부터의 화상 데이터들을 데이터 라인(DL)들로 전송하기 위한 다수의 데이터 링크라인들 및 이 구동회로(DRC)로부터의 게이트 신호들을 게이트 라인(GL)들로 전송하기 위한 다수의 데이터 링크라인들이 형성된다.

여기서 도 1에서의 구동회로(DRC)를 좀 더 구체적으로 설명하면 다음과 같다.

도 2는 도 1에서의 구동 집적회로의 상세 도면이며, 도 3은 제 1 실시예에 따른 표면 실장형 패키지(TCP)를 나타낸 도면으로서, 이 도 3은 도 1에서의 구동회로(DRC)에서 표면 실장형 패키지(TCP)만을 따로 나타낸 도면이다.

도 2 및 도 3에 도시된 바와 같이, 표면 실장형 패키지(TCP)는 구동 집적회로(D-IC)가 실장되는 실장영역(MD)과, 이 구동 집적회로(D-IC)의 입력핀(IP)들을 외부 시스템에 접속시키기 위한 다수의 입력패턴(IU)들과, 그리고 이 구동 집적회 로(D-IC)의 출력핀(OP)들을 패널(PN)에 접속시키기 위한 다수의 출력패턴(OU)들을 포함한다. 도 2 및 도 3에서의 입력패턴(IU)들과 출력패턴(OU)들간의 구분을 위해 입력패턴(IU)들에 포함된 입력라인들(IL)들을 출력패턴들(OU)에 포함된 출력라인들(OL)보다 더 두껍게 나타내었다. 이는 단지 구분상의 편의를 위해 두께의 차이를 나타낸 것이며, 실제 입력패턴(IU)들의 입력라인(IL)들과 출력패턴(OU)의 출력라인(OL)들의 두께는 동일하게 설정될 수 있다.

입력패턴(IU)들은 구동 집적회로(D-IC)의 입력핀(IP)들을 외부 시스템에 연결시키기 위한 것으로, 각 입력패턴(IU)은 상기 표면 실장형 패키지(TCP)의 일측 끝단에 위치한 입력패드부(201)에 형성된 입력패드(IPD)와, 상기 입력패드(IPD)와 상기 입력핀(IP)간을 연결하는 입력라인(IL)을 포함한다. 이 다수의 입력패턴(IU)들 중 적어도 하나의 입력패턴(IU)은 외부 시스템으로부터의 논리 전원을 전송하는 입력패턴(IU)으로서, 이 논리 전원을 전송하는 입력패턴(IU)을 다른 입력패턴(IU)들과 구분하기 위해 논리전원입력패턴(IU_NP)으로 부르기로 한다. 이 논리전원입력패턴(IU_NP) 역시 입력패드(IPD)와 입력라인(IL)으로 구성된다.

출력패턴(OU)들은 구동 집적회로(D-IC)의 출력핀(OP)들을 패널(PN), 즉 패널(PN)의 데이터 라인(DL)들에 연결시키기 위한 것으로, 각 출력패턴(OU)은 상기 표면 실장형 패키지(TCP)의 타측 끝단에 위치한 출력패드부(202)에 형성된 출력패드(OPD)와, 상기 출력패드(OPD)와 상기 출력핀(OP)간을 연결하는 출력라인(OL)을 포함한다.

표면 실장형 패키지(TCP)의 좌측 가장자리에는 다수의 LOG(Line On Glass)형 전송패턴(LOGL)이 형성되는 바, 이 LOG형 전송패턴(LOGL)은 구동 집적회로(D-IC)를 통과하지 않고 패널(PN)의 비표시부(ND)에 형성된 LOG형 신호전송라인들에 바로 접속된다. 이 LOG형 전송패턴(LOGL)은 인쇄회로기판(PCB)을 통해 외부 시스템으로부터 공급되는 구동전압 및 그라운드 전압 등을 패널(PN)에 공급하는 역할을 한다. 이 LOG형 전송패턴(LOGL)은 입력패드부(201)에 형성된 입력패드(IPD)와, 출력패드부(202)에 형성된 출력패드(OPD)와, 그리고 이 입력패드(IPD)와 출력패드(OPD)간을 연결하는 전송라인(IL)을 포함한다.

표면 실장형 패키지(TCP)의 실장영역(MD)은 구동 집적회로(D-IC)가 COF(Chip On Film) 방식으로 실장되는 영역으로서 이 영역은 구동 집적회로(D-IC)가 실장되기 전에는 어떠한 전기적 라인도 형성되지 않는 빈 영역으로서, 본 발명에 따르면 이 구동 집적회로(D-IC)가 실장되기 이전의 이 빈 영역인 실장영역(MD)에 외부 보조전송라인(1OAL, 2OAL)이 형성된다. 이 외부 보조전송라인(1OAL, 2OAL)은 다수 형성될 수 있는 바, 도 3에는 하나의 실시예로서 2개의 외부 보조전송라인(1OAL, 2OAL)이 나타나 있다.

도 3에 도시된 바와 같이, 외부 보조전송라인(1OAL, 2OAL)의 일측은 논리전원입력패턴(IU_NP)의 입력라인(IL)에 접속된다. 외부 보조전송라인(1OAL, 2OAL)의 수가 다수일 경우, 도 3에 도시된 바와 같이 각 외부 보조전송라인(1OAL, 2OAL)은 개별적으로 각 논리전원입력패턴(IU_NP)에 연결될 수 있다. 또 다른 방법으로서, 외부 보조전송라인의 수가 다수일 경우, 모든 외부 보조전송라인(1OAL, 2OAL)의 일측이 하나의 논리전원입력패턴(IU_NP)에 함께 연결될 수 있다.

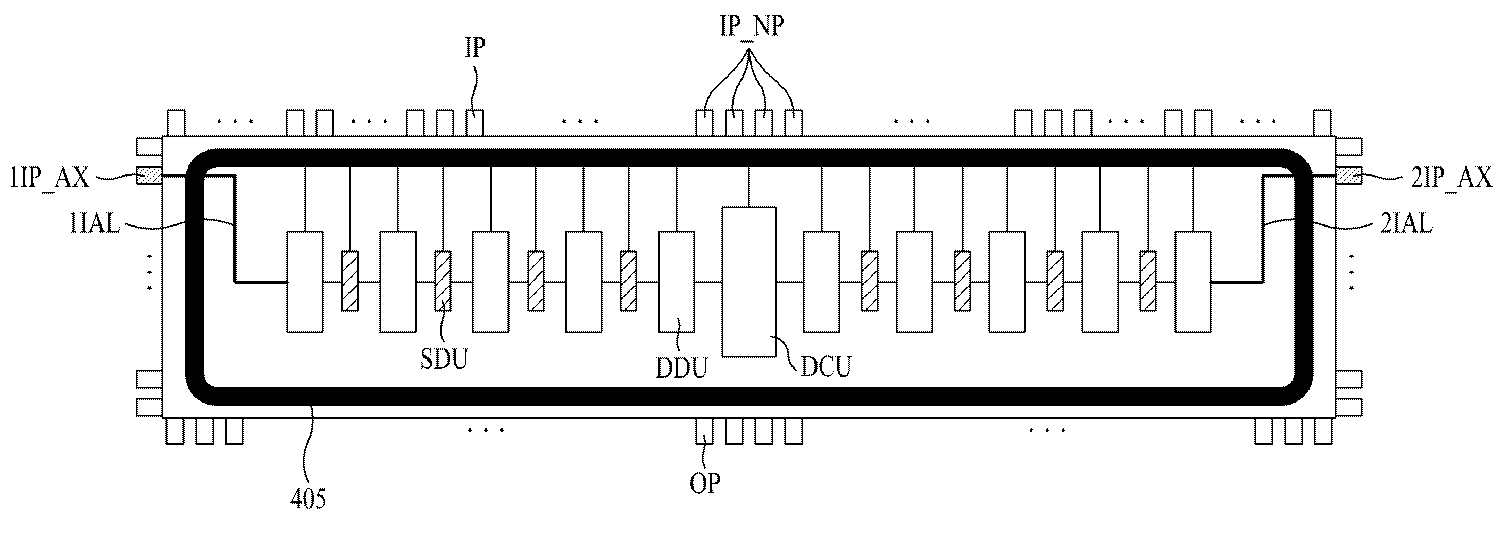

도 4는 본 발명의 제 1 실시예에 따른 구동 집적회로(D-IC)를 나타낸 도면으로서. 이 도 4는 도 1에서의 구동회로(DRC)에서 구동 집적회로(D-IC)만을 따로 나타낸 도면이다.

구동 집적회로(D-IC)는 다수의 입력핀(IP)들, 다수의 출력핀(OP)들, 적어도 하나의 보조 입력핀(I1P_AX, 2IP_AX), 적어도 하나의 내부 보조전송라인(1IAL, 2IAL), 논리전원전송라인(405), 구동 제어부(DCU), 다수의 데이터 구동부(DDU)들 및 다수의 신호지연/완충부(SDU)들을 포함한다.

다수의 입력핀(IP)들 중 적어도 하나의 입력핀(IP)은 논리전원입력패턴(IU_NP)의 입력라인(IL)에 접속되는 바, 이 논리전원입력패턴(IU_NP)에 접속된 입력핀(IP)을 다른 입력핀(IP)들과 구분하기 위해 논리전원입력핀(IP_NP)으로 부르기로 한다.

다수의 입력핀(IP)들, 다수의 출력핀(OP)들 및 적어도 하나의 보조 입력핀(IP)은 구동 집적회로(D-IC)의 외부 가장자리에 형성되어, 이 구동 집적회로(D-IC)의 내부에 형성된 각종 회로들과 외부의 입력패턴(IU)들 및 출력패턴(OU)들간을 전기적으로 연결하는 역할을 한다.

적어도 하나의 내부 보조전송라인, 논리전원전송라인(405), 다수의 데이터 구동부(DDU)들 및 다수의 신호지연/완충부(SDU)들은 구동 집적회로(D-IC)의 내부에 형성된다.

논리전원전송라인(405)은 논리전원입력핀(IP_NP)에 접속된다. 논리전원입력 핀(IP_NP)이 다수일 경우 이들 모두는 논리전원전송라인(405)에 함께 연결된다. 도 4에는 하나의 예로서 4개의 논리전원입력핀(IP_NP)이 도시되어 있는 바, 이들 4개의 논리전원입력핀(IP_NP)들은 모두 논리전원전송라인(405)에 공통으로 접속된다.

다수의 데이터 구동부(DDU)들은 구동 집적회로(D-IC)의 내부에 형성되는 바, 이 다수의 데이터 구동부(DDU)들은 논리전원전송라인(405)에 병렬로 접속되어 이 논리전원전송라인(405)으로부터의 논리 전원에 의해 동작한다.

내부 보조전송라인은 구동 집적회로(D-IC)의 내부에 형성되는 바, 이 내부 보조전송라인의 일측은 적어도 하나의 데이터 구동부(DDU)에 접속된다. 이 내부 보조전송라인은 다수 구비될 수 있다. 이와 같이 내부 보조전송라인이 다수일 경우, 도 4에 도시된 바와 같이 각각의 내부 보조전송라인은 개별적으로 각 보조 입력핀(IP)에 독립적으로 접속될 수 있다. 다른 방법으로, 이 내부 보조전송라인이 다수일 경우, 모든 내부 보조전송라인들이 하나의 보조 입력핀(IP)에 공통으로 접속될 수 있다.

보조입력핀(IP)은 내부 보조전송라인의 타측과 상기 외부 보조전송라인의 타측간을 서로 연결한다.

이러한 구조에 의해 외부 시스템으로부터의 논리 전원은 논리전원입력패턴(IU_NP), 논리전원입력핀(IP_NP), 논리전원전송라인(405)을 경유하여 각 데이터 구동부(DDU) 및 각 신호지연/완충부(SDU)에 공급되는 바, 특히 적어도 어느 하나의 데이터 구동부(DDU)는 상술된 경로 외에도 다음과 같은 추가된 경로를 통해 논리 전원을 더 공급받는다. 즉, 적어도 하나의 데이터 구동부(DDU)는 외부 보조전송라 인, 보조 입력핀(IP) 및 내부 보조전송라인을 통해 공급되는 논리 전원을 더 공급받는다. 이를 좀 더 구체적으로 설명하면 다음과 같다.

도 4에 도시된 바와 같이, 구동 제어부(DCU), 다수의 데이터 구동부(DDU)들 및 다수의 신호지연/완충부(SDU)들이 논리전원전송라인(405)에 접속되어 있는데, 이때 n개(n은 6이상의 짝수)의 데이터 구동부(DDU)들은 상기 구동 제어부(DCU)를 중심으로 하여 이 구동 제어부(DCU)의 양측에 n/2개씩 나누어 배열된다. 예를 들어, 도 4에 도시된 바와 같이 하나의 구동 제어부(DCU)와 10개의 데이터 구동부(DDU)들이 구비되어 있는 바, 이들 10개의 데이터 구동부(DDU)들 중 5개의 데이터 구동부(DDU)들은 이 구동 제어부(DCU)의 좌측에 일렬로 배열되어 있으며, 나머지 5개의 데이터 구동부(DDU)들은 이 구동 제어부(DCU)의 우측에 일렬로 배열되어 있다.

여기서 구동 제어부(DCU)는 논리전원입력핀(IP_NP)들에 가장 근접하여 위치하고 있으며, 데이터 구동부(DDU)들은 이 논리전원입력핀(IP_NP)들로부터 순차적으로 멀어지도록 배열되어 있다. 이에 따라 논리전원입력핀(IP_NP)으로부터 가장 멀리 떨어져 위치한, 즉 구동 제어부(DCU)로부터 가장 멀리 떨어져 위치한 데이터 구동부(DDU)에는 다른 데이터 구동부(DDU)에 비하여 왜곡되고 약한 논리 전원이 공급된다. 따라서, 구동 집적회로(D-IC)의 양측 가장자리에 위치한 2개의 데이터 구동부(DDU)에 외부 보조전송라인(1OAL, 2OAL), 보조 입력핀(1IP_AX, 2IP_AX) 및 내부 보조전송라인(1IAL, 2IAL)을 경유하여 전송되는 논리 전원을 추가적으로 공급함으로써 양측 가장자리에 위치한 데이터 구동부(DDU)에 최종적으로 공급되는 논리 전 원의 왜곡의 크기의 감소를 방지할 수 있다.

예를 들어, 도 4에 도시된 바와 같이 구동 제어부(DCU)의 좌측에 위치한 데이터 구동부(DDU)들 중 상기 구동 제어부(DCU)로부터 가장 멀리 위치한 데이터 구동부(DDU)는 제 1 외부 보조전송라인(1OAL), 제 1 보조 입력핀(1IP_AX) 및 제 1 내부 보조전송라인(1IAL)을 통해 전송되는 논리 전원을 추가적으로 공급받으며, 그리고 이 구동 제어부(DCU)의 우측에 위치한 데이터 구동부(DDU)들 중 상기 구동 제어부(DCU)로부터 가장 멀리 위치한 데이터 구동부(DDU)는 제 2 외부 보조전송라인(2OAL), 제 2 보조 입력핀(2IP_AX) 및 제 2 내부 보조전송라인(2IAL)을 통해 전송되는 논리 전원을 추가적으로 공급받는다.

도 5는 본 발명의 제 2 실시예에 따른 표면 실장형 패키지(TCP)를 나타낸 도면이고, 도 6은 본 발명의 제 2 실시예에 따른 구동 집적회로(D-IC)를 나타낸 도면으로서, 이 도 5는 도 1에서의 구동회로(DRC)에서 표면 실장형 패키지(TCP)만을 따로 나타낸 도면이며, 도 6은 도 1에서의 구동회로(DRC)에서 구동 집적회로(D-IC)만을 따라 나타낸 도면이다.

여기서 도 5에서의 입력패턴(IU)들과 출력패턴(OU)들간의 구분을 위해 입력패턴(IU)들에 포함된 입력라인들(IL)들을 출력패턴들(OU)에 포함된 출력라인들(OL)보다 더 두껍게 나타내었다. 이는 단지 구분상의 편의를 위해 두께의 차이를 나타낸 것이며, 실제 입력패턴(IU)들의 입력라인(IL)들과 출력패턴(OU)의 출력라인(OL)들의 두께는 동일하게 설정될 수 있다.

도 5에 도시된 구조는 상술된 도 3의 구조에 2개의 외부 보조전송라인 들(3OAl, 4OAL)이 더 추가된 구조로서, 도 5에 도시된 바와 같이 제 1 내지 제 4 외부 보조전송라인(1OAL 내지 4OAL)들이 실장영역(MD)에 형성되어 있다.

도 6에 도시된 구조는 상술된 도 4의 구조에 2개의 보조 입력핀(3IP_AX, 4IP_AX)들이 더 추가된 구조로서, 도 6에 도시된 바와 같이 제 1 내지 제 4 보조 입력핀(1IP_AX 내지 4IP_AX)들이 구동 집적회로(D-IC)의 외부에 설치되어 있다.

제 1 및 제 2 외부 보조전송라인(1OAL, 2OAL), 그리고 제 1 및 제 2 보조 입력핀(1IP_AX, 2IP_AX)들의 접속관계는 상술된 도 3 및 도 4에서의 설명을 참조하기로 한다.

도 6에 도시된 바와 같이 구동 제어부(DCU)의 좌측에 위치한 데이터 구동부(DDU)들 중 상기 구동 제어부(DCU)로부터 두 번째로 멀리 위치한 데이터 구동부(DDU)는 제 3 외부 보조전송라인(3OAL), 제 3 보조 입력핀(3IP_AX) 및 제 3 내부 보조전송라인(3IAL)을 통해 전송되는 논리 전원을 추가적으로 공급받으며, 그리고 이 구동 제어부(DCU)의 우측에 위치한 데이터 구동부(DDU)들 중 상기 구동 제어부(DCU)로부터 두 번째로 멀리 위치한 데이터 구동부(DDU)는 제 4 외부 보조전송라인(4OAL), 제 4 보조 입력핀(4IP_AX) 및 제 4 내부 보조전송라인(4IAL)을 통해 전송되는 논리 전원을 추가적으로 공급받는다.

여기서, 구동 제어부(DCU), 데이터 구동부(DDU) 및 신호지연/완충부(SDU)의 구성을 좀 더 구체적으로 설명하면 다음과 같다.

도 7은 구동 제어부(DCU), 데이터 구동부(DDU) 및 신호지연/완충부(SDU)에 대한 상세 구성도이다.

구동 제어부(DCU)는 데이터 정렬부(DA), 샘플/홀딩부(SH) 및 제어신호생성부(CSG)를 포함한다.

데이터 정렬부(DA)는 외부 시스템으로부터의 화상 데이터(ID)들을 재정렬하여 출력한다.

샘플/홀딩부(SH)는 데이터 정렬부(DA)로부터의 화상 데이터(ID)들을 순차적으로 샘플링 및 홀딩한다.

제어신호생성부(CSG)는 외부 시스템으로부터 제어신호를 공급받아 상기 소스아웃풋인에이블신호(SOE)를 포함한 각종 타이밍 제어신호를 출력한다.

각 데이터 구동부(DDU)는 래치부(LT), 디지털-아날로그 변환부(DAC) 및 신호완충부(BF)를 포함한다.

래치부(LT)는 샘플/홀딩부(SH)로부터의 m개(m=k*n; k는 4이상의 자연수)의 샘플링된 화상 데이터(ID)들 중 m/n개의 샘플링된 화상 데이터(ID)들을 동시에 공급받고, 소스아웃풋인에이블신호(SOE)에 응답하여 m/n개의 샘플링된 화상 데이터(ID)들을 동시에 출력한다. 즉, 샘플/홀딩부(SH)에 저장된 n개의 샘플링 화상 데이터(ID)들은 각 데이터 구동부(DDU)의 래치부(LT)에 동일하게 나뉘어져 공급되며, 각 래치부(LT)는 제어신호생성부(CSG)로부터의 소스아웃풋인에이블신호(SOE)에 응답하여 자신에게 공급된 샘플링된 화상 데이터(ID)들을 동시에 출력한다. 이때, 구동 제어부(DCU)의 바로 양측에 위치한 2개의 데이터 구동부(DDU)들은 제어신호생성부(CSG)로부터 바로 소스아웃풋인에이블신호(SOE)를 공급받으며, 나머지 데이터 구동부(DDU)들은 신호지연/완충부(SDU)에 의해서 순차적으로 지연된 소스아웃풋인에 이블신호(SOE)를 공급받는다. 따라서 구동 제어부(DCU)에 더 근접하게 위치한 데이터 구동부(DDU)일수록 더 먼저 소스아웃풋인에이블신호(SOE)를 공급받으므로, 구동 제어부(DCU)에 더 근접하게 위치한 데이터 구동부(DDU)일수록 샘플링된 화상 데이터(ID)들을 더 먼저 출력한다.

디지털-아날로그 변환부(DAC)는 래치부(LT)로부터의 m/n개의 샘플링된 화상 데이터(ID)들을 아날로그 신호로 변환한다.

신호완충부(BF)는 디지털-아날로그 변환부(DAC)로부터의 샘플링된 화상 데이터(ID)들을 버퍼링하여 출력한다.

도 8은 구동 제어부(DCU), 데이터 구동부(DDU) 및 신호지연/완충부(SDU)에 논리 전원이 공급되는 과정을 설명하기 위한 도면이다.

논리전원전송라인(405)으로부터의 논리 전원(NP)은 구동 제어부(DCU)내의 데이터 정렬부(DA), 샘플/홀딩부(SH) 및 제어신호생성부(CSG)에 각각 공급됨과 아울러, 각 데이터 구동부(DDU)내의 래치부(LT), 디지털-아날로그 변환부(DAC) 및 신호완충부(BF)에 각각 공급된다. 특히, 구동 제어부(DCU)의 좌측에 위치한 데이터 구동부(DDU)들 중 상기 구동 제어부(DCU)로부터 가장 멀리 위치한 데이터 구동부(DDU)내의 래치부(LT), 디지털-아날로그 변환부(DAC) 및 신호완충부(BF) 각각은 제 1 외부 보조전송라인(1OAL), 제 1 보조 입력핀(1IP_AX) 및 제 1 내부 보조전송라인(1IAL)을 통해 전송되는 논리 전원(NP)을 추가적으로 더 공급받으며, 그리고 이 구동 제어부(DCU)의 우측에 위치한 데이터 구동부(DDU)들 중 상기 구동 제어부(DCU)로부터 가장 멀리 위치한 데이터 구동부(DDU)내의 래치부(LT), 디지털-아날 로그 변환부(DAC) 및 신호완충부(BF)는 제 2 외부 보조전송라인(2OAL), 제 2 보조 입력핀(2IP_AX) 및 제 2 내부 보조전송라인(2IAL)을 통해 전송되는 논리 전원(NP)을 추가적으로 더 공급받는다.

논리 전원(NP)은 상술된 데이터 정렬부(DA), 샘플/홀딩부(SH), 제어신호생성부(CSG), 래치부(LT), 디지털-아날로그 변환부(DAC) 및 신호완충부(BF) 각각이 상술된 기능을 수행할 수 있도록 하는데 필요한 전원이다.

이상에서 설명한 본 발명은 상술한 실시예 및 첨부된 도면에 한정되는 것이 아니고, 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 여러 가지 치환, 변형 및 변경이 가능하다는 것이 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 있어 명백할 것이다.

도 1은 본 발명의 실시예에 따른 표시장치용 구동회로를 나타낸 도면

도 2는 도 1에서의 구동 집적회로의 상세 도면

도 3은 제 1 실시예에 따른 표면 실장형 패키지를 나타낸 도면

도 4는 본 발명의 제 1 실시예에 따른 구동 집적회로를 나타낸 도면

도 5는 본 발명의 제 2 실시예에 따른 표면 실장형 패키지를 나타낸 도면

도 6은 본 발명의 제 2 실시예에 따른 구동 집적회로를 나타낸 도면

도 7은 구동 제어부, 데이터 구동부 및 신호지연/완충부에 대한 상세 구성도

도 8은 구동 제어부, 데이터 구동부 및 신호지연/완충부에 논리 전원이 공급되는 과정을 설명하기 위한 도면

* 도면의 주요부에 대한 설명

1IP_AX: 제 1 보조 입력핀 2IP_AX: 제 2 보조 입력핀

1IAL: 제 1 내부 전송라인 2IAL: 제 2 내부 전송라인

405: 논리전원전송라인 DCU: 구동 제어부

DDU: 데이터 구동부 SDU: 신호지연/완충부

IP_NP: 논리전원입력핀

Claims (6)

- 패널의 표시부에 화상을 표시하는데 필요한 각종 신호들을 생성하는 구동 집적회로;상기 구동 집적회로가 실장되는 실장영역 및 상기 구동 집적회로의 입력핀들을 외부 시스템에 접속시키기 위한 다수의 입력패턴들 및 상기 구동 집적회로의 출력핀들을 패널에 접속시키기 위한 다수의 출력패턴들이 형성된 표면 실장형 패키지;상기 입력패턴들 중 외부 시스템으로부터의 논리 전원을 전송하는 적어도 하나의 논리전원입력패턴;상기 입력핀들 중 상기 논리전원입력패턴에 접속된 적어도 하나의 논리전원입력핀;상기 논리전원입력핀에 접속되며, 상기 구동 집적회로의 내부에 형성되어 상기 논리 전원을 전송하는 논리전원전송라인;상기 논리전원전송라인에 병렬로 접속되며, 상기 구동 집적회로의 내부에 형성되어 상기 논리전원전송라인으로부터의 논리 전원에 의해 동작하는 다수의 데이터 구동부들;상기 실장영역에 형성되며, 일측이 상기 논리전원입력패턴에 접속된 적어도 하나의 외부 보조전송라인;상기 구동 집적회로의 내부에 형성되며, 상기 데이터 구동부들 중 상기 논리전원입력핀으로부터 가장 멀리 위치한 적어도 하나의 데이터 구동부에 일측이 접속된 적어도 하나의 내부 보조전송라인; 및,상기 내부 보조전송라인의 타측과 상기 외부 보조전송라인의 타측간을 연결하며, 상기 구동집적 회로에 설치된 적어도 하나의 보조입력핀을 포함함을 특징으로 하는 표시장치용 구동회로.

- 제 1 항에 있어서,상기 구동 집적회로는 상기 다수의 데이터 구동부들의 동작을 제어하기 위한 구동 제어부를 더 포함하며;상기 구동 제어부가 상기 다수의 데이터 구동부들에 접속되며;상기 구동 제어부 및 다수의 데이터 구동부들이 상기 논리전원전송라인에 의해 둘러싸여 있으며;상기 논리전원입력이 상기 논리전원전송라인의 외측에 위치하며;상기 논리전원입력핀이 상기 논리전원전송라인에 접속되며;상기 구동 제어부 및 다수의 데이터 구동부들이 상기 논리전원전송라인에 접속되며;상기 구동 제어부 및 다수의 데이터 구동부들 중 상기 구동 제어부가 상기 논리전원입력핀에 가장 근접하여 위치하고 있으며;n개(n은 6이상의 짝수)의 데이터 구동부들은 상기 구동 제어부를 중심으로 하여 이 구동 제어부의 양측에 n/2개씩 나누어 배열되며;상기 외부 보조전송라인이 제 1 및 제 2 외부 보조전송라인을 포함하며;상기 내부 보조전송라인이 제 1 및 제 2 내부 보조전송라인을 포함하며;상기 보조입력핀이 제 1 및 제 2 보조 입력핀을 포함하며;상기 제 1 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 1 보조 입력핀에 접속되며;상기 제 1 내부 보조전송라인의 일측이 구동 제어부의 일측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 가장 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 1 보조 입력핀에 접속되며;상기 제 2 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 2 보조 입력핀에 접속되며;상기 제 2 내부 보조전송라인의 일측이 구동 제어부의 타측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 가장 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 2 보조 입력핀에 접속됨을 특징으로 하는 표시장치용 구동회로.

- 제 2 항에 있어서,상기 구동 집적회로는 각 데이터 구동부 사이에 위치한 신호지연/완충부를 더 포함하며;상기 구동 제어부로부터 출력된 소스아웃풋인에이블신호는 상기 신호지연/완충부를 통해 상기 구동 제어부의 일측에 위치한 n/2개의 데이터 구동부들에 순차적으로 공급됨과 아울러, 상기 구동 제어부의 타측에 위치한 n/2개의 데이터 구동부들에 순차적으로 공급되며;상기 구동 제어부로부터 출력된 소스아웃풋인에이블신호는 상기 구동 제어부에 가장 근접한 데이터 구동부부터 순차적으로 공급되며;각 데이터 구동부는 상기 소스아웃풋인에이블신호에 응답하여 샘플링된 화상 데이터들을 동시에 출력하는 것을 특징으로 하는 표시장치용 구동회로.

- 제 3 항에 있어서,상기 구동 제어부는,외부 시스템으로부터의 화상 데이터들을 재정렬하여 출력하는 데이터 정렬부;상기 데이터 정렬부로부터의 화상 데이터들을 순차적으로 샘플링 및 홀딩하는 샘플/홀딩부; 및,외부 시스템으로부터 제어신호를 공급받아 상기 소스아웃풋인에이블신호를 포함한 각종 타이밍 제어신호를 출력하는 제어신호생성부를 포함함을 특징으로 하는 표시장치용 구동회로.

- 제 4 항에 있어서,각 데이터 구동부는,상기 샘플/홀딩부로부터의 m개(m=k*n; k는 4이상의 자연수)의 샘플링된 화상 데이터들 중 m/n개의 샘플링된 화상 데이터들을 동시에 공급받고, 상기 소스아웃풋인에이블신호에 응답하여 m/n개의 샘플링된 화상 데이터들을 동시에 출력하는 래치부;상기 래치부로부터의 m/n개의 샘플링된 화상 데이터들을 아날로그 신호로 변환하는 디지털-아날로그 변환부; 및,상기 디지털-아날로그 변환부로부터의 샘플링된 화상 데이터들을 버퍼링하여 출력하는 신호완충부를 포함함을 특징으로 하는 표시장치용 구동회로.

- 제 1 항에 있어서,상기 구동 집적회로는 상기 다수의 데이터 구동부들의 동작을 제어하기 위한 구동 제어부를 더 포함하며;상기 구동 제어부가 상기 다수의 데이터 구동부들에 접속되며;상기 구동 제어부 및 다수의 데이터 구동부들이 상기 논리전원전송라인에 의해 둘러싸여 있으며;상기 논리전원입력이 상기 논리전원전송라인의 외측에 위치하며;상기 논리전원입력핀이 상기 논리전원전송라인에 접속되며;상기 구동 제어부 및 다수의 데이터 구동부들이 상기 논리전원전송라인에 접속되며;상기 구동 제어부 및 다수의 데이터 구동부들 중 상기 구동 제어부가 상기 논리전원입력핀에 가장 근접하여 위치하고 있으며;n개(n은 4이상의 자연수)의 데이터 구동부들은 상기 구동 제어부를 중심으로 하여 이 구동 제어부의 양측에 n/2개씩 나누어 배열되며;상기 외부 보조전송라인이 제 1 내지 제 4 외부 보조전송라인으로 구성되며;상기 내부 보조전송라인이 제 1 내지 제 4 내부 보조전송라인으로 구성되며;상기 보조입력핀이 제 1 내지 제 4 보조 입력핀으로 구성되며;상기 제 1 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 1 보조 입력핀에 접속되며;상기 제 1 내부 보조전송라인의 일측이 구동 제어부의 일측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 가장 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 1 보조 입력핀에 접속되며;상기 제 2 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 2 보조 입력핀에 접속되며;상기 제 2 내부 보조전송라인의 일측이 구동 제어부의 타측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 가장 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 2 보조 입력핀에 접속되며;상기 제 3 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 3 보조 입력핀에 접속되며;상기 제 3 내부 보조전송라인의 일측이 구동 제어부의 일측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 두 번째로 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 3 보조 입력핀에 접속되며;상기 제 4 외부 보조전송라인의 일측이 상기 논리전원입력패턴에 접속되고, 타측이 상기 제 4 보조 입력핀에 접속되며;상기 제 4 내부 보조전송라인의 일측이 구동 제어부의 타측에 위치한 n/2개의 데이터 구동부들 중 상기 구동 제어부로부터 두 번째로 멀리 위치한 데이터 구동부에 접속되고, 타측이 상기 제 4 보조 입력핀에 접속됨을 특징으로 하는 표시장치용 구동회로.

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090091234A KR101341912B1 (ko) | 2009-09-25 | 2009-09-25 | 표시장치용 구동회로 |

| JP2010209230A JP5134665B2 (ja) | 2009-09-25 | 2010-09-17 | 表示装置用駆動回路 |

| CN2010102935354A CN102034415B (zh) | 2009-09-25 | 2010-09-21 | 用于显示装置的驱动电路 |

| US12/890,568 US9240136B2 (en) | 2009-09-25 | 2010-09-24 | Driving circuit for display device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090091234A KR101341912B1 (ko) | 2009-09-25 | 2009-09-25 | 표시장치용 구동회로 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110033660A KR20110033660A (ko) | 2011-03-31 |

| KR101341912B1 true KR101341912B1 (ko) | 2013-12-13 |

Family

ID=43779799

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020090091234A KR101341912B1 (ko) | 2009-09-25 | 2009-09-25 | 표시장치용 구동회로 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9240136B2 (ko) |

| JP (1) | JP5134665B2 (ko) |

| KR (1) | KR101341912B1 (ko) |

| CN (1) | CN102034415B (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9406273B2 (en) | 2013-08-30 | 2016-08-02 | Silicon Works Co., Ltd. | Flat panel display apparatus and source driver IC |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102360171B1 (ko) * | 2015-04-24 | 2022-02-07 | 주식회사 엘엑스세미콘 | 구동 드라이버 |

| KR102034072B1 (ko) * | 2017-08-14 | 2019-10-18 | 엘지디스플레이 주식회사 | 표시장치, 구동회로 장치 및 표시장치의 구동방법 |

| KR102434845B1 (ko) * | 2018-01-29 | 2022-08-24 | 삼성디스플레이 주식회사 | 터치 패널 및 이를 포함하는 표시 장치 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0713509A (ja) * | 1993-06-21 | 1995-01-17 | Toshiba Corp | 表示データ駆動用集積回路 |

| JP2008129029A (ja) | 2006-11-16 | 2008-06-05 | Seiko Epson Corp | ソースドライバ、電気光学装置及び電子機器 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3235612B2 (ja) * | 1990-04-24 | 2001-12-04 | セイコーエプソン株式会社 | 半導体装置 |

| JP3319459B2 (ja) * | 1990-04-24 | 2002-09-03 | セイコーエプソン株式会社 | 半導体装置 |

| JP3884111B2 (ja) * | 1995-10-18 | 2007-02-21 | 東芝電子エンジニアリング株式会社 | 映像制御装置およびこの映像制御装置を備える平面ディスプレイ装置 |

| US6525718B1 (en) * | 1997-02-05 | 2003-02-25 | Sharp Kabushiki Kaisha | Flexible circuit board and liquid crystal display device incorporating the same |

| JP3647666B2 (ja) * | 1999-02-24 | 2005-05-18 | シャープ株式会社 | 表示素子用駆動装置及びそれを用いた表示モジュール |

| JP3595754B2 (ja) * | 1999-06-10 | 2004-12-02 | シャープ株式会社 | 液晶表示装置 |

| JP4783890B2 (ja) * | 2000-02-18 | 2011-09-28 | 株式会社 日立ディスプレイズ | 液晶表示装置 |

| US6856373B2 (en) * | 2000-08-29 | 2005-02-15 | Fujitsu Display Technologies Corporation | Liquid crystal display apparatus and reduction of electromagnetic interference |

| KR100831301B1 (ko) * | 2001-12-22 | 2008-05-22 | 엘지디스플레이 주식회사 | 라인 온 글래스형 액정표시장치 |

| JP2003233358A (ja) * | 2002-02-12 | 2003-08-22 | Hitachi Ltd | 液晶ドライバ及び液晶ディスプレイ装置 |

| JP4390451B2 (ja) * | 2002-12-26 | 2009-12-24 | Necエレクトロニクス株式会社 | 表示装置およびデータ側駆動回路 |

| KR100686334B1 (ko) * | 2003-11-14 | 2007-02-22 | 삼성에스디아이 주식회사 | 표시장치 및 그의 구동방법 |

| KR100589381B1 (ko) * | 2003-11-27 | 2006-06-14 | 삼성에스디아이 주식회사 | 역다중화기를 이용한 표시 장치 및 그 구동 방법 |

| KR101032947B1 (ko) * | 2004-03-18 | 2011-05-09 | 삼성전자주식회사 | 표시 장치 및 그 구동 장치 |

| JP4749687B2 (ja) * | 2004-07-30 | 2011-08-17 | シャープ株式会社 | 表示装置 |

| JP2007272180A (ja) * | 2006-03-30 | 2007-10-18 | Lg Phillips Lcd Co Ltd | 液晶表示装置及びその駆動方法 |

| US7576713B2 (en) * | 2006-04-25 | 2009-08-18 | Lg Electronics Inc. | Plasma display apparatus |

| JP2008014996A (ja) * | 2006-07-03 | 2008-01-24 | Seiko Epson Corp | 電気光学装置および電子機器 |

| KR20080087525A (ko) * | 2007-03-27 | 2008-10-01 | 삼성전자주식회사 | 액정표시장치와 액정표시장치의 구동방법 |

| US20100052558A1 (en) * | 2008-08-29 | 2010-03-04 | Samsung Electronics Co., Ltd. | Backlight assembly, driving method thereof and display apparatus |

| JP5203993B2 (ja) * | 2009-02-02 | 2013-06-05 | ルネサスエレクトロニクス株式会社 | ドライバ、表示装置及びアンプ回路駆動方法 |

| JP4768039B2 (ja) * | 2009-03-02 | 2011-09-07 | パナソニック株式会社 | 表示駆動装置および表示装置 |

| KR20100108677A (ko) * | 2009-03-30 | 2010-10-08 | 엘지디스플레이 주식회사 | 액정표시장치 |

| KR101341910B1 (ko) * | 2009-09-25 | 2013-12-13 | 엘지디스플레이 주식회사 | 표시장치용 구동회로 및 이의 구동방법 |

| KR101341907B1 (ko) * | 2009-09-29 | 2013-12-13 | 엘지디스플레이 주식회사 | 표시장치용 구동회로 및 이의 구동방법 |

-

2009

- 2009-09-25 KR KR1020090091234A patent/KR101341912B1/ko active IP Right Grant

-

2010

- 2010-09-17 JP JP2010209230A patent/JP5134665B2/ja active Active

- 2010-09-21 CN CN2010102935354A patent/CN102034415B/zh active Active

- 2010-09-24 US US12/890,568 patent/US9240136B2/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0713509A (ja) * | 1993-06-21 | 1995-01-17 | Toshiba Corp | 表示データ駆動用集積回路 |

| JP2008129029A (ja) | 2006-11-16 | 2008-06-05 | Seiko Epson Corp | ソースドライバ、電気光学装置及び電子機器 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9406273B2 (en) | 2013-08-30 | 2016-08-02 | Silicon Works Co., Ltd. | Flat panel display apparatus and source driver IC |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102034415B (zh) | 2013-06-05 |

| JP5134665B2 (ja) | 2013-01-30 |

| CN102034415A (zh) | 2011-04-27 |

| US20110074760A1 (en) | 2011-03-31 |

| KR20110033660A (ko) | 2011-03-31 |

| JP2011070189A (ja) | 2011-04-07 |

| US9240136B2 (en) | 2016-01-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5134666B2 (ja) | 表示装置用駆動回路及びその駆動方法 | |

| US20060164587A1 (en) | Display panel assembly and display apparatus having the same | |

| JP5265634B2 (ja) | 表示装置用駆動回路及びその駆動方法 | |

| KR101603228B1 (ko) | 표시장치 | |

| US7701432B2 (en) | Routing signals to drivers of display device with minimized wiring | |

| US20080204434A1 (en) | Display Device | |

| KR102594393B1 (ko) | 유기발광표시패널, 유기발광표시장치 | |

| US10726787B2 (en) | Chip on film and display device including the same | |

| US20100220094A1 (en) | Scan signal line driver circuit and display device | |

| KR20090103190A (ko) | 표시장치 | |

| KR101341912B1 (ko) | 표시장치용 구동회로 | |

| CN110556078A (zh) | 显示装置 | |

| KR20200113984A (ko) | 표시 장치 | |

| WO2015087460A1 (ja) | 画像表示装置に用いられるゲート駆動用集積回路、画像表示装置、および、有機elディスプレイ | |

| KR20150077778A (ko) | 디스플레이 장치의 검사 방법 | |

| US20090147030A1 (en) | LCD Driver IC and Method for Operating the Same | |

| KR20110014359A (ko) | 액정표시장치 | |

| CN111243500B (zh) | 显示面板 | |

| JP2006023589A (ja) | 液晶表示装置 | |

| KR20090093180A (ko) | 액정표시장치 | |

| KR20210054980A (ko) | 드라이버 ic 및 이를 포함하는 디스플레이장치 | |

| CN115440152A (zh) | 包括多芯片膜封装件的显示设备 | |

| CN117012127A (zh) | 显示驱动装置及其数据传输方法 | |

| KR20060104710A (ko) | 액정표시장치 | |

| KR20090110484A (ko) | 액정 표시 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20161118 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20171116 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20181114 Year of fee payment: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20191113 Year of fee payment: 7 |