KR101085139B1 - 박막 트랜지스터 어레이 기판 및 그 제조 방법 - Google Patents

박막 트랜지스터 어레이 기판 및 그 제조 방법 Download PDFInfo

- Publication number

- KR101085139B1 KR101085139B1 KR1020040101447A KR20040101447A KR101085139B1 KR 101085139 B1 KR101085139 B1 KR 101085139B1 KR 1020040101447 A KR1020040101447 A KR 1020040101447A KR 20040101447 A KR20040101447 A KR 20040101447A KR 101085139 B1 KR101085139 B1 KR 101085139B1

- Authority

- KR

- South Korea

- Prior art keywords

- storage capacitor

- thin film

- film transistor

- line

- pixel electrode

- Prior art date

Links

- 239000010409 thin film Substances 0.000 title claims abstract description 76

- 239000000758 substrate Substances 0.000 title claims abstract description 71

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 19

- 239000010410 layer Substances 0.000 claims abstract description 103

- 238000003860 storage Methods 0.000 claims abstract description 85

- 239000003990 capacitor Substances 0.000 claims abstract description 84

- 238000002161 passivation Methods 0.000 claims abstract description 45

- 239000004973 liquid crystal related substance Substances 0.000 claims abstract description 23

- 210000002858 crystal cell Anatomy 0.000 claims abstract description 11

- 239000011241 protective layer Substances 0.000 claims abstract description 5

- 238000000034 method Methods 0.000 claims description 40

- 239000010408 film Substances 0.000 claims description 38

- 229920002120 photoresistant polymer Polymers 0.000 claims description 27

- 230000001681 protective effect Effects 0.000 claims description 25

- 238000005530 etching Methods 0.000 claims description 14

- 238000004380 ashing Methods 0.000 claims description 5

- 238000000059 patterning Methods 0.000 claims description 3

- 230000015572 biosynthetic process Effects 0.000 claims description 2

- 206010047571 Visual impairment Diseases 0.000 abstract description 10

- 229910052751 metal Inorganic materials 0.000 description 13

- 239000002184 metal Substances 0.000 description 13

- 238000000151 deposition Methods 0.000 description 7

- 238000000206 photolithography Methods 0.000 description 7

- 229910021417 amorphous silicon Inorganic materials 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- 239000007772 electrode material Substances 0.000 description 5

- 210000004027 cell Anatomy 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 239000011810 insulating material Substances 0.000 description 3

- 230000000149 penetrating effect Effects 0.000 description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 3

- 241000270730 Alligator mississippiensis Species 0.000 description 2

- 229910001182 Mo alloy Inorganic materials 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- -1 acryl Chemical group 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 150000002894 organic compounds Chemical class 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136227—Through-hole connection of the pixel electrode to the active element through an insulation layer

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F2201/00—Constructional arrangements not provided for in groups G02F1/00 - G02F7/00

- G02F2201/48—Flattening arrangements

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Nonlinear Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Chemical & Material Sciences (AREA)

- Mathematical Physics (AREA)

- Optics & Photonics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Computer Hardware Design (AREA)

- Liquid Crystal (AREA)

Abstract

본 발명은 잔상을 최소화시켜 화질을 향상시킬 수 있는 박막트랜지스터 어레이 기판 및 그 제조방법에 관한 것이다.

본 발명에 따른 박막 트랜지스터 어레이 기판은 게이트 절연막을 사이에 두고 서로 교차되게 형성된 게이트 라인 및 데이터 라인과; 상기 게이트 라인과 데이터 라인의 교차영역에 형성된 박막 트랜지스터와; 상기 데이터 라인 및 박막 트랜지스터를 보호함과 아울러 상기 박막 트랜지스터의 드레인 전극을 노출시키는 접촉홀을 가지는 보호막과; 상기 접촉홀을 통해 상기 박막 트랜지스터의 드레인 전극과 접속된 화소전극과; 상기 게이트 라인과 상기 게이트 라인과 분리된 공통라인 중 어느 하나와, 상기 화소 전극에 의해 형성되며, 액정셀의 전압을 유지하는 스토리지 캐패시터를 구비하고, 상기 스토리지 캐패시터는 상기 스토리지 캐패시터 내에서 상기 보호막이 제거되어 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 상기 게이트 절연막을 사이에 두고 중첩되어 형성되거나, 상기 스토리지 캐패시터를 제외한 영역에서의 높이보다 상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막과 상기 게이트 절연막을 사이에 두고 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 중첩되어 형성되는 것을 특징으로 한다.

Description

도 1은 통상적인 박막 트랜지스터 어레이 기판의 일부를 도시한 평면도이다.

도 2은 도 1에 도시된 박막 트랜지스터 어레이 기판을 Ⅰ-Ⅰ'선을 따라 절단하여 도시한 단면도이다.

도 3a 내지 도 3d는 도 2에 도시된 박막 트랜지스터 어레이 기판의 제조방법을 단계적으로 도시한 단면도이다.

도 4는 액정표시패널에 공급되는 전압을 나타내는 파형도이다.

도 5는 본 발명의 제1 실시예에 따른 박막 트랜지스터 어레이 기판의 일부를 도시한 단면도이다.

도 6a 내지 도 7b는 본 발명의 제1 실시예에 따른 박막 트랜지스터 어레이 기판의 제조방법을 단계적으로 도시한 단면도이다.

도 8은 본 발명의 제2 실시예에 따른 박막 트랜지스터 어레이 기판의 일부를 도시한 단면도이다.

도 9a 내지 도 9c는 본 발명의 제2 실시예에 따른 박막 트랜지스터 어레이 기판의 제조방법을 단계적으로 도시한 단면도이다.

도 10은 본 발명의 제3 실시예에 따른 박막 트랜지스터 어레이 기판을 나타내는 평면도이다.

< 도면의 주요 부분에 대한 부호의 설명 >

2, 102 : 게이트 라인 4, 104 : 데이터 라인

6, 106 : 박막 트랜지스터 8, 108 : 게이트 전극

10, 110 : 소스 전극 12, 112 : 드레인 전극

14, 114 : 활성층 16,116 : 접촉홀

18, 118 : 화소전극 20,120 : 스토리지 캐패시터

44,144 : 게이트 절연막 50,150 : 보호막

본 발명은 박막 트랜지스터 어레이 기판에 관한 것으로, 특히 잔상을 최소화시켜 화질을 향상시킬 수 있는 박막트랜지스터 어레이 기판 및 그 제조방법에 관한 것이다.

통상의 액정표시장치는 전계를 이용하여 액정의 광투과율을 조절함으로써 화상을 표시하게 된다. 이를 위하여 액정표시장치는 액정셀들이 매트릭스 형태로 배열되어진 액정패널과, 액정패널을 구동하기 위한 구동회로를 구비한다.

액정패널은 서로 대향하는 박막 트랜지스터 어레이 기판 및 칼러필터 어레이 기판과, 두 기판 사이에 일정한 셀갭 유지를 위해 위치하는 스페이서와, 그 셀갭에 채워진 액정을 구비한다.

박막 트랜지스터 어레이 기판은 게이트 라인들 및 데이터 라인들과, 그 게이트 라인들과 데이터 라인들의 교차부마다 스위치소자로 형성된 박막 트랜지스터와, 액정셀 단위로 형성되어 박막 트랜지스터에 접속된 화소 전극 등과, 그들 위에 도포된 배향막으로 구성된다. 게이트 라인들과 데이터 라인들은 각각의 패드부를 통해 구동회로들로부터 신호를 공급받는다. 박막 트랜지스터는 게이트 라인에 공급되는 스캔신호에 응답하여 데이터 라인에 공급되는 화소전압신호를 화소 전극에 공급한다.

칼라필터 어레이 기판은 액정셀 단위로 형성된 칼라필터들과, 칼러필터들간의 구분 및 외부광 반사를 위한 블랙 매트릭스와, 액정셀들에 공통적으로 기준전압을 공급하는 공통 전극 등과, 그들 위에 도포되는 배향막으로 구성된다.

액정패널은 박막 트랜지스터 어레이 기판과 칼라필터 어레이 기판을 별도로 제작하여 합착한 다음 액정을 주입하고 봉입함으로써 완성하게 된다.

도 1은 종래의 박막 트랜지스터 어레이 기판을 도시한 평면도이고, 도 2는 도 1에 도시된 박막 트랜지스터 어레이 기판을 Ⅰ-Ⅰ'선을 따라 절단하여 도시한 단면도이다.

도 1 및 도 2에 도시된 박막 트랜지스터 어레이 기판은 하부기판(42) 위에 게이트 절연막(44)을 사이에 두고 교차하게 형성된 게이트 라인(2) 및 데이터 라인 (4)과, 그 교차부마다 형성된 박막 트랜지스터(Thin Film Transistor ; 이하 "TFT"라 함)(6)와, 그 교차구조로 마련된 셀영역에 형성된 화소 전극(18)을 구비한다. 그리고, TFT 어레이 기판은 화소전극(18)과 이전단 게이트 라인(2)의 중첩부에 형성된 스토리지 캐패시터(20)를 구비한다.

TFT(6)는 게이트 라인(2)에 접속된 게이트 전극(8)과, 데이터 라인(4)에 접속된 소스 전극(10)과, 화소 전극(18)에 접속된 드레인 전극(12)과, 게이트 전극(8)과 중첩되고 소스 전극(10)과 드레인 전극(12) 사이에 채널을 형성하는 활성층(14)을 구비한다. 활성층(14)은 데이터 라인(4), 소스 전극(10) 및 드레인 전극(12)과 중첩되게 형성되고 소스 전극(10)과 드레인 전극(12) 사이의 채널부를 더 포함한다. 활성층(14) 위에는 데이터 라인(4), 소스 전극(10) 및 드레인 전극(12)과 오믹접촉을 위한 오믹접촉층(48)이 더 형성된다.

이러한 TFT(6)는 게이트 라인(2)에 공급되는 게이트 신호에 응답하여 데이터 라인(4)에 공급되는 화소전압 신호가 화소 전극(18)에 충전되어 유지되게 한다.

화소전극(18)은 보호막(50)을 관통하는 접촉홀(16)을 통해 TFT(6)의 드레인 전극(12)과 접속된다. 화소 전극(18)은 충전된 화소전압에 의해 도시하지 않은 상부 기판에 형성되는 공통 전극과 전위차를 발생시키게 된다. 이 전위차에 의해 TFT 어레이 기판과 컬러필터 어레이 기판 사이에 위치하는 액정이 유전 이방성에 의해 회전하게 되며 도시하지 않은 광원으로부터 화소전극(18)을 경유하여 입사되는 광을 상부 기판 쪽으로 투과시키게 된다.

스토리지 캐패시터(20)는 전단 게이트라인(2)과 화소전극(18)의해 형성된다. 게이트라인(2)과 화소전극(18) 사이에는 게이트 절연막(44) 및 보호막(50)이 위치하게 된다. 이러한 스토리지 캐패시터(20)는 화소 전극(18)에 충전된 화소전압이 다음 화소전압이 충전될 때까지 유지되도록 도움을 주게 된다.

이하, 도 3a 내지 도 3d를 참조하여 TFT 어레이 기판의 제조방법을 설명하면 다음과 같다.

먼저, 하부기판(42) 상에 스퍼터링 방법 등의 증착방법을 통해 게이트 금속층이 형성된 후 포토리쏘그래피 공정과 식각공정으로 게이트 금속층이 패터닝됨으로써 도 3a에 도시된 바와 같이, 게이트라인(2), 게이트전극(8)을 포함하는 게이트 패턴들이 형성된다.

게이트 패턴들이 형성된 하부기판(42) 상에 PECVD, 스퍼터링 등의 증착방법을 통해 게이트 절연막(44)이 형성된다. 게이트 절연막(44)이 형성된 하부기판(42) 상에 비정질 실리콘층, n+ 비정질 실리콘층, 그리고 소스/드레인 금속층이 순차적으로 형성된다.

소스/드레인 금속층 위에 회절 마스크를 이용한 포토리쏘그래피 공정 및 식각공정 등을 이용하여 데이터 라인(4), 소스 전극(10), 드레인 전극(12)을 포함하는 소스/드레인 패턴과, 소스 드레인 패턴 하부에 오믹접촉층(48)과 활성층(14)을 포함하는 반도체 패턴(45)이 형성된다.

한편, 반도체 패턴(45)은 별도의 마스크 공정을 이용하여 소스/드레인 패턴과는 별개로 형성될 수 도 있다.

소스/드레인 패턴들이 형성된 게이트 절연막(44) 상에 PECVD 등의 증착방법 으로 보호막(50)이 전면 형성된 후 포토리쏘그래피 공정과 식각공정으로 패터닝됨으로써 도 3c에 도시된 바와 같이 접촉홀(16)이 형성된다. 접촉홀(16)은 보호막(50)을 관통하여 드레인 전극(12)이 노출되게 형성된다.

보호막(50) 상에 스퍼터링 등의 증착방법으로 투명전극 물질이 전면 증착된 후 포토리쏘그래피 공정과 식각공정을 통해 투명전극 물질이 패터닝됨으로써 도 3d에 도시된 바와 같이 화소전극(18)이 형성된다. 화소전극(18)은 접촉홀(16)을 통해 드레인 전극(12)과 전기적으로 접속된다. 또한, 화소전극(18)는 게이트 절연막(44) 및 보호막(50)을 사이에 두고 전단 게이트 라인(2)과 중첩되게 형성됨으로써 스토리지 캐패시터(20)를 구성한다.

이러한, TFT 어레이 기판은 TFT(6)의 게이트 전극(8)에 도 4에 도시된 바와 같이 게이트 전압(Vg)이 공급되며, 소스전극(10)에는 데이터 전압(Vd)이 공급된다. TFT(6)의 게이트 전극(8)에 TFT(6)의 문턱전압 이상의 게이트 전압(Vg)이 인가되면 소스전극(10)과 드레인 전극(12) 사이에 채널이 형성되면서 데이터 전압(Vd)이 TFT의 소스전극(10)과 드레인 전극(12)을 경유하여 액정셀(Clc)과 스토리지 캐패시터(20)(Cst)에 충전된다.

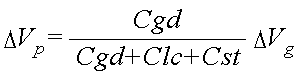

여기서, 데이터전압(Vd)과 액정셀(Clc)에 충전되는 전압(Vlc)의 차인 피드 쓰로우 전압(Feed Through Voltage ; △Vp)은 아래의 수학식 1로 정의된다.

여기서, Cgd는 TFT의 게이트단자와 드레인단자사이에 형성되는 기생캐패시터이고, △Vg는 Vgh 전압과 Vgl 전압의 차전압이다.

이러한, 피드 쓰로우 전압(△Vp)은 플리커 등의 잔상을 나타나게 하는 등 화질 저하의 요인이 되고 있다. 이에 따라, 수학식 1에 의해 피드 쓰로우 전압(△Vp)을 최소화 하기 위해 스토리지 캐패시터(120) 용량(Cst)을 최대화 함으로써 화질저하를 감소시키기 위한 연구가 진행 중에 있다. 그러나, 스토리지 캐패시터의 용량(Cst)을 크게 하면 할수록 그 만큼 스토리지 캐패시터(120)가 차지하는 면적이 커지게 됨으로써 개구율이 작아지는 문제가 발생된다. 또한, 보호막(50) 및 게이트 절연막(44)의 두께를 작게하는 경우 게이트 절연막(44) 및 보호막(50)이 충분히 절연역할을 할 수 없는 문제가 발생된다.

따라서, 본 발명의 목적은 잔상을 최소화시켜 화질을 향상시킬 수 있는 박막트랜지스터 어레이 기판 및 그 제조방법을 제공하는 것이다.

상기 목적을 달성하기 위하여, 본 발명에 따른 박막 트랜지스터 어레이 기판은 게이트 절연막을 사이에 두고 서로 교차되게 형성된 게이트 라인 및 데이터 라인과; 상기 게이트 라인과 데이터 라인의 교차영역에 형성된 박막 트랜지스터와; 상기 데이터 라인 및 박막 트랜지스터를 보호함과 아울러 상기 박막 트랜지스터의 드레인 전극을 노출시키는 접촉홀을 가지는 보호막과; 상기 접촉홀을 통해 상기 박막 트랜지스터의 드레인 전극과 접속된 화소전극과; 상기 게이트 라인과 상기 게이트 라인과 분리된 공통라인 중 어느 하나와, 상기 화소 전극에 의해 형성되며, 액정셀의 전압을 유지하는 스토리지 캐패시터를 구비하고, 상기 스토리지 캐패시터는 상기 스토리지 캐패시터 내에서 상기 보호막이 제거되어 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 상기 게이트 절연막을 사이에 두고 중첩되어 형성되거나, 상기 스토리지 캐패시터를 제외한 영역에서의 높이보다 상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막과 상기 게이트 절연막을 사이에 두고 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 중첩되어 형성되는 것을 특징으로 한다.

삭제

상기 공통라인은 상기 화소전극을 가로질러 형성된 것을 특징으로 한다.

본 발명에 따른 박막 트랜지스터 어레이 기판의 제조방법은 게이트 라인과 상기 게이트라인과 분리된 공통라인을 형성하는 단계와; 상기 게이트 라인과 게이트 절연막을 사이에 두고 교차되는 데이터 라인과, 상기 게이트 라인과 데이터 라인의 교차영역에 박막 트랜지스터를 형성하는 단계와; 상기 박막 트랜지스터를 덮도록 형성됨과 아울러 박막 트랜지스터의 드레인 전극을 노출시키는 접촉홀을 가지는 보호막을 형성하는 단계와; 상기 접촉홀을 통해 상기 박막 트랜지스터의 드레인 전극과 접속되는 화소전극과, 상기 공통라인 및 게이트 라인 중 어느 하나와 상기 화소전극을 포함하며 액정셀의 전압을 유지하는 스토리지 캐패시터를 형성하는 단계를 포함하고, 상기 스토리지 캐패시터는 상기 스토리지 캐패시터 내에서 상기 보호막이 제거되어 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 상기 게이트 절연막을 사이에 두고 중첩되어 형성되거나, 상기 스토리지 캐패시터를 제외한 영역에서의 높이보다 상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막과 상기 게이트 절연막을 사이에 두고 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 중첩되어 형성되는 것을 특징으로 한다.

삭제

상기 보호막을 형성하는 단계는 상기 보호막 상에 회절 마스크를 정렬시키는 단계와; 상기 회절 마스크를 이용하여 상기 스토리지 캐패시터를 제외한 영역에서보다 상기 스토리지 캐패시터의 형성 영역에서 낮은 높이를 가지는 포토레지스트 패턴을 형성하는 단계와; 상기 포토레지스트 패턴을 마스크로 상기 보호막을 패터닝하여 상기 접촉홀을 형성하는 단계와; 상기 포토레지스트 패턴을 애싱하여 상기 스토리지 캐패시터에 포함될 보호막을 노출시키는 단계와; 상기 애싱된 포토레지스트 패턴을 마스크로 이용한 식각 공정을 통해 상기 스토리지 캐패시터를 제외한 영역에서의 높이보다 상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막을 형성하는 단계와; 상기 애싱된 포토레지스트 패턴을 제거하는 단계를 포함하는 것을 특징으로 한다.

상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막은 식각 시간에 의해 상기 보호막의 높이가 조절되는 것을 특징으로 한다.

상기 공통라인은 상기 화소전극을 가로지르도록 형성되는 것을 특징으로 한다.

상기 목적 외에 본 발명의 다른 목적 및 이점들은 첨부 도면을 참조한 본 발명의 바람직한 실시 예에 대한 설명을 통하여 명백하게 드러나게 될 것이다.

이하, 본 발명의 바람직한 실시 예를 도 5 내지 도 10를 참조하여 상세하게 설명하기로 한다.

도 5는 본 발명의 제1 실시예에 따른 박막 트랜지스터 어레이 기판을 도시한 단면도이다.

도 5에 도시된 박막 트랜지스터 어레이 기판은 하부기판(142) 위에 게이트 절연막(144)을 사이에 두고 교차하게 형성된 게이트 라인(102) 및 데이터 라인(104)과, 그 교차부마다 형성된 박막 트랜지스터(Thin Film Transistor ; 이하 "TFT"라 함)(106)와, 그 교차구조로 마련된 셀영역에 형성된 화소 전극(118)을 구비한다. 그리고, TFT 어레이 기판은 화소전극(118)과 이전단 게이트 라인(102)의 중첩부에 형성된 스토리지 캐패시터(120)를 구비한다.

TFT(106)는 게이트 라인(102)에 접속된 게이트 전극(108)과, 데이터 라인(104)에 접속된 소스 전극(110)과, 화소 전극(118)에 접속된 드레인 전극(112)과, 게이트 전극(108)과 중첩되고 소스 전극(110)과 드레인 전극(112) 사이에 채널을 형성하는 활성층(114)을 구비한다. 활성층(114)은 데이터 라인(104), 소스 전극(110) 및 드레인 전극(112)과 중첩되게 형성되고 소스 전극(110)과 드레인 전극(112) 사이의 채널부를 더 포함한다. 활성층(114) 위에는 데이터 라인(104), 소스 전극(110) 및 드레인 전극(112)과 오믹접촉을 위한 오믹접촉층(148)이 더 형성된다.

이러한 TFT(106)는 게이트 라인(102)에 공급되는 게이트 신호에 응답하여 데이터 라인(104)에 공급되는 화소전압 신호가 화소 전극(118)에 충전되어 유지되게 한다.

화소전극(118)은 보호막(150)을 관통하는 접촉홀(116)을 통해 TFT(106)의 드레인 전극(112)과 접속된다. 화소 전극(118)은 충전된 화소전압에 의해 도시하지 않은 상부 기판에 형성되는 공통 전극과 전위차를 발생시키게 된다. 이 전위차에 의해 TFT 어레이 기판과 컬러필터 어레이 기판 사이에 위치하는 액정이 유전 이방 성에 의해 회전하게 되며 도시하지 않은 광원으로부터 화소전극(118)을 경유하여 입사되는 광을 상부 기판 쪽으로 투과시키게 된다.

스토리지 캐패시터(120)는 전단 게이트라인(102)과 화소전극(118)에 의해 형성된다. 게이트라인(102)과 화소전극(118) 사이에는 게이트 절연막(44)이 위치하게 된다.

보호막(150)은 스토리지 캐패시터(120) 내에는 위치하지 않게 된다. 이에 따라, 피드 쓰로우 전압(△Vp)이 최소화됨으로써 플리커 등의 잔상이 최소화됨으로써 화질이 향상된다.

이를 좀더 구체적으로 설명하면 다음과 같다.

일반적으로 수학식 2와 같이 캐패시터의 용량은 전극의 단면적에 비례하게 되고, 전극 사이의 거리에 반비례하게 된다.

즉, 본 발명의 제1 실시예에서는 보호막(150)이 스토리지 캐패시터(120) 내의 게이트 절연막(144) 상에서 제거되게 형성된다. 이에 따라, 화소전극(118)과 게이터 전극(102) 사이의 거리가 작아지게 됨으로써 스토리지 캐패시터(120)의 용량(Cst)이 커지게 된다. 이러한, 스토리지 캐패시터(120)의 용량(Cst)은 수학식 3 에 나타난 바와 같이 피드 쓰로우 전압(△Vp)을 감소시키는 역할을 한다.

그 결과, 피드 쓰로우 전압(△Vp)이 최소화 됨으로써 플리커 등의 잔상 문제가 방지되어 화질이 향상된다.

이하, 도 6a 내지 도 6d를 참조하여 TFT 어레이 기판의 제조방법을 설명하면 다음과 같다.

먼저, 하부기판(142) 상에 스퍼터링 방법 등의 증착방법을 통해 게이트 금속층이 형성된다. 이어서, 마스크를 이용한 포토리쏘그래피 공정과 식각공정으로 게이트 금속층이 패터닝됨으로써 도 6a에 도시된 바와 같이, 게이트라인(102), 게이트전극(108)을 포함하는 게이트 패턴들이 형성된다. 게이트 금속으로는 크롬(Cr), 몰리브덴(Mo), 알루미늄계 금속 등이 단일층 또는 이중층 구조로 이용된다.

게이트 패턴들이 형성된 하부기판(142) 상에 PECVD, 스퍼터링 등의 증착방법을 통해 게이트 절연막(144)이 형성된다. 게이트 절연막(144)의 재료로는 산화 실리콘(SiOx) 또는 질화 실리콘(SiNx) 등의 무기 절연물질이 이용된다.

게이트 절연막(144)이 형성된 하부기판(142) 상에 비정질 실리콘층, n+ 비정질 실리콘층, 그리고 소스/드레인 금속층이 순차적으로 형성된다.

소스/드레인 금속층 위에 마스크를 이용한 포토리쏘그래피 공정으로 포토레지스트 패턴을 형성하게 된다. 이 경우 마스크로는 TFT(106)의 채널부에 회절 노광부를 갖는 회절 노광 마스크를 이용함으로써 채널부의 포토레지스트 패턴이 다른 소스/드레인 패턴부 보다 낮은 높이를 갖게 한다.

이어서, 포토레지스트 패턴을 이용한 습식 식각공정으로 소스/드레인 금속층이 패터닝됨으로써 데이터 라인(104), 소스 전극(110), 그 소스 전극(110)과 일체화된 드레인 전극(112)을 포함하는 소스/드레인 패턴들이 형성된다.

그 다음, 동일한 포토레지스트 패턴을 이용한 건식 식각공정으로 n+ 비정질 실리콘층과 비정질 실리콘층이 동시에 패터닝됨으로써 오믹접촉층(148)과 활성층(114)을 포함하는 반도체 패턴(145)이 형성된다.

그리고, 채널부에서 상대적으로 낮은 높이를 갖는 포토레지스트 패턴이 애싱(Ashing) 공정으로 제거된 후 건식 식각공정으로 채널부의 소스/드레인 패턴 및 오믹접촉층(148)이 식각된다. 이에 따라, 도 6b에 도시된 바와 같이 채널부의 활성층(114)이 노출됨과 아울러 소스 전극(110)과 드레인 전극(112)이 전기적으로 분리된다.

이어서, 스트립 공정으로 소스/드레인 패턴부 위에 남아 있는 포토레지스트 패턴이 제거된다. 소스/드레인 금속으로는 몰리브덴(Mo), 티타늄, 탄탈륨, 몰리브덴 합금(Mo alloy), 구리(Cu), 알루미늄계 금속 등이 이용된다.

한편, 반도체 패턴(145)은 별도의 마스크 공정을 이용하여 소스/드레인 패턴과는 별개로 형성될 수 도 있다.

소스/드레인 패턴들이 형성된 게이트 절연막(144) 상에 PECVD 등의 증착방법으로 보호막(150)이 전면 형성된다. 보호막(150)은 마스크를 이용한 포토리쏘그래피 공정과 식각공정으로 패터닝됨으로써 도 6c에 도시된 바와 같이 보호막(50)을 관통하여 드레인 전극(112)을 노출시키는 접촉홀(116)이 형성됨과 아울러 스토리지 캐패시터가 마련되는 영역에서 게이트 절연막(144)이 노출된다.

이러한, 보호막(150)의 형성방법을 도 7a 및 도 7b를 참조하여 구체적으로 설명하면 다음과 같다.

도 7a를 참조하면, 하부기판(142) 상에 보호막(150)이 전면 형성된 후 포토레지스트(190a)가 전면 도포된다. 이후, 투과영역(180a) 및 차단영역(180b)를 포함하는 마스크(180)가 정렬된 후 노광공정이 실시된다.

이후, 현상공정이 실시됨으로써 도 7b에 도시된 바와 같이 포토레지스트 패턴(190b)이 형성된 후 포토레지스트 패턴(190b)을 마스크로 이용하여 보호막(150)이 패터닝된다. 이에 따라, 도 6c에 도시된 바와 같이 박막 트랜지스터(106)의 드레인 전극(112)을 노출시키는 접촉홀(116)이 형성됨과 아울러 스토리지 캐패시터(120)가 위치할 영역에서 제거되어 게이트 절연막(144)을 노출시키는 보호막(150)이 형성된다.

보호막(150)의 재료로는 게이트 절연막(44)과 같은 무기 절연물질이나 유전상수가 작은 아크릴(acryl)계 유기화합물, BCB 또는 PFCB 등과 같은 유기 절연물질이 이용된다.

보호막(150) 상에 스퍼터링 등의 증착방법으로 투명전극 물질이 전면 증착된다. 이어서 마스크를 이용한 포토리쏘그래피 공정과 식각공정을 통해 투명전극 물질이 패텅님됨으로써 도 6d에 도시된 바와 같이 화소전극(118)을 포함하는 투명전극 패턴들이 형성된다. 화소 전극(118)은 컨택홀(116)을 통해 드레인 전극(12)과 전기적으로 접속된다. 또한, 화소전극(118)는 게이트 절연막(44)을 사이에 두고 전단 게이트 라인(102)과 중첩되게 형성됨으로써 스토리지 캐패시터(120)를 구성한다. 투명전극 물질로는 인듐주석산화물(Indium Tin Oxide : ITO)이나 주석산화물(Tin Oxide : TO) 또는 인듐아연산화물(Indium Zinc Oxide : IZO)이 이용된다.

이와 같이, 본 발명의 제1 실시예에 따른 박막 트랜지스터 어레이 기판 및 그 제조방법은 보호막(150)이 스토리지 캐패시터(120)에서 제거되게 형성됨으로써 스토리지 캐패시터(120)의 용량이 커질 수 있게 된다. 이에 따라, 피드 쓰로우 전압(△Vp)이 최소화 됨으로써 플리커 등의 잔상 문제가 방지되어 화질이 향상된다.

도 8은 본 발명의 제2 실시예에 따른 박막 트랜지스터 어레이 기판을 나타내는 단면도이다.

도 8에 도시된 박막 트랜지스터 어레이 기판은 도 5에 도시된 박막 트랜지스터 어레이 기판과 대비하여 스토리지 캐패시터(120) 내에 보호막(150)이 부분적으로 제거되어 작은 높이를 갖도록 형성되는 것을 제외하고는 동일한 구성요소들을 가지게 되므로 도 5와 동일한 구성요소들에 대해서는 동일번호를 부여하고 상세한 설명은 생략하기로 한다.

보호막(150)은 박막 트랜지스터(106)의 드레인 전극(112)을 노출시키는 접촉홀(116)을 포함하며 스토리지 캐패시터(120)내에서 종래보다 작은 높이를 가지는 보호막(150)이 형성된다. 이에 따라, 화소전극(118)과 게이터 전극(102) 사이의 거리가 작아지게 됨으로써 스토리지 캐패시터(120)의 용량(Cst)이 커지게 된다. 그 결과, 피드 쓰로우 전압(△Vp)이 최소화됨으로써 플리커 등의 잔상 문제가 방지되 어 화질이 향상된다.

또한, 본 발명의 제2 실시예에서는 회절마스크를 이용하여 보호막(150)을 형성함으로써 스토리지 캐패시터(120) 내의 보호막(150)의 높이를 조절할 수 있게 된다. 따라서, 스토리지 캐패시터(120)의 용량(Cst)을 증가시킬 수 있을 뿐만 아니라 설계자가 원하는 용량을 갖는 스토리지 캐패시터(120)를 형성할 수 있다. 여기서, 스토리지 캐패시터(120)에서의 보호막(150)의 높이는 식각시간으로 조절하게 된다.

도 9a 내지 도 9c는 본 발명의 제2 실시예에 따른 박막 트랜지스터 어레이 기판 및 그 제조방법을 설명하기 위한 도면이다.

본 발명의 제2 실시예에 따른 박막 트랜지스터 어레이 기판의 제조방법은 회절마스크를 이용하여 보호막(150)을 형성함으로써 박막 트랜지스터(106)의 드레인 전극(112)를 노출시키는 접촉홀(116)이 형성됨과 아울러 스토리지 캐패시터(120) 내에 부분적으로 제거된 보호막(150)이 위치하는 것을 제외하고는 도 6a 내지 도 6d에 도시된 본 발명의 제1 실시예에 따른 박막 트랜지스터 어레이 기판의 제조방법과 동일하므로 동일번호를 부여하고 상세한 설명은 생략하기로 한다.

도 9a를 참조하면, 박막 트랜지스터(106) 등이 형성된 하부기판(142) 상에 순차적으로 보호막(150) 및 포토레지스트가 형성된다. 이후, 투과부(182a), 차단부(182b) 및 반투과부(182c)를 포함하는 회절마스크(182)가 정렬된 후 노광공정 및 현상공정이 실시됨으로써 포토레지스트 패턴(192a)이 형성된다. 여기서, 포토레지스트 패턴(192a)은 접촉홀(116)이 형성될 영역의 보호막(150)을 노출시킴과 아울러 스토리지 캐패시터(120)의 낮은 두께를 가지는 보호막(150)이 위치할 영역에서는 상대적으로 낮은 높이(도면의 A영역)를 갖게 형성된다.

이어서, 포토레지스트 패턴(192a)을 마스크로 이용하여 보호막(150)이 패터닝됨으로써 박막 트랜지스터(106)의 드레인 전극(112)을 노출시키는 접촉홀(116)이 형성된다. 이후, 에싱공정이 실시됨으로써 도 9b에 도시된 바와 같이 잔류되는 포토레지스트 패턴(192b)에 의해 스토리지 캐패시터(120)에 포함될 보호막(150)이 노출된다. 이후, 잔류된 포토레지스트 패턴(192b)을 마스크로 이용하여 노출된 보호막(150)이 식각(드라인 에칭)됨으로써 도 9c에 도시된 바와 같이 스토리지 캐패시터(129)를 제외한 영역에서의 보호막(150)의 높이보다 작은 높이를 가지는 가지는 보호막(150)이 잔류되게 된다. 여기서, 잔류된 보호막(150)의 두께는 식각 시간에 의해 조절된다. 이후, 스트립 공정에 의해 잔류된 포토레지스트 패턴(192b)이 제거됨으로써 부분적으로 제거된 보호막(150)이 형성된다.

도 10은 본 발명의 제3 실시예에 따른 박막 트랜지스터 어레이 기판을 나타내는 평면도이다.

도 10에 도시된 박막 트랜지스터 어레이 기판은 화소전극(118)을 가로질러 스토리지 캐패시터(120)가 형성되는 스토리지 온 커먼(storage on common)형의 박막 트랜지스터 어레이 기판을 나타낸다.

이러한, 스토리지 온 커먼(storage on common)형의 박막 트랜지스터 어레이 기판은 도 5에 도시된 박막 트랜지스터 어레이 기판과 대비하여 화소전극(118)을 가로지르며 게이트 라인(102)과 나란하게 형성됨과 아울러 액정 구동시 기준전압이 공급되는 공통라인(125)을 구비하고, 상기 공통라인(125)과 화소전극(118)에 의해 스토리지 캐패시터(120)가 형성되는 것을 제외하고는 동일한 구성요소들을 가지게 되므로 도 5와 동일한 구성요소들에 대해서는 동일번호를 부여하고 상세한 설명은 생략하기로 한다.

본 발명의 제3 실시예에 따른 박막 트랜지스터 어레이 기판은 스토리지 캐패시터(120)가 화소영역 즉, 화소전극이 위치하는 영역을 가로지르도록 형성된다. 이러한, 스토리지 온 커먼(storage on common)형의 박막 트랜지스터 어레이 기판에서는 본 발명의 제1 및 제2 실시예와 동일한 기술적 특징인 보호막(150)이 스토리지 캐패시터(120) 내에서 제거되거나 부분적으로 제거되어 낮은 높이를 가지게 된다. 다만, 제3 실시예에서는 스토리지 캐패시터(120)는 게이트 라인(102)이 아닌 공통라인(125)과 화소전극(118)에 의해 형성된다.

이와 같이, 본 발명의 제3 실시예에 따른 박막 트랜지스터 어레이 기판은 스토리지 온 커먼 방식에서 스토리지 캐패시터내에 보호막이 제거되거나 부분적으로 제거되게 형성된다. 이에 따라, 화소전극(118)과 공통라인(125) 사이의 거리가 작아지게 됨으로써 스토리지 캐패시터(120)의 용량(Cst)이 커지게 된다. 그 결과, 피드 쓰로우 전압(△Vp)이 최소화 됨으로써 플리커 등의 잔상 문제가 방지되어 화질이 향상된다.

여기서, 보호막(150)이 스토리지 캐패시터(120) 내에서 부분적으로 제거되는 경우에도 회절마스크(182)가 이용된다. 따라서, 스토리지 캐패시터(120)의 용량(Cst)을 증가시킬 수 있을 뿐만 아니라 설계자가 원하는 용량을 갖는 스토리지 캐 패시터(120)를 형성할 수 있다.

본 발명의 제3 실시예에 따른 박막 트랜지스터 어레이 기판의 제조방법은 게이트 라인(102) 등의 게이트 패턴을 형성함과 동시에 공통라인(125)를 형성된다. 스토리지 캐패시터(120)에서 보호막을 제거하는 경우는 도 7a 내지 도 7b와 동일한 방식이 이용되고 보호막(150)을 부분적으로 제거하는 경우는 도 9a 내지 도 9c에 도시된 회절마스크(182)를 이용한 포토공정, 애싱공정, 식각공정등을 이용한 패터닝공정과 동일한 방식에 의해 형성된다. 이에 따라, 상세한 설명은 생략하기로 한다.

상술한 바와 같이, 본 발명에 따른 박막 트랜지스터 어레이 기판 및 그 제조 방법은 스토리지 캐패시터 내의 보호막이 제거되거나 또는 부분적으로 제거됨으로써 스토리지 캐패시터의 용량이 커지게 된다. 이에 따라, 피드 쓰로우 전압(△Vp)이 최소화 됨으로써 플리커 등의 잔상 문제가 방지되어 화질이 향상된다.

이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

Claims (8)

- 게이트 절연막을 사이에 두고 서로 교차되게 형성된 게이트 라인 및 데이터 라인과;상기 게이트 라인과 데이터 라인의 교차영역에 형성된 박막 트랜지스터와;상기 데이터 라인 및 박막 트랜지스터를 보호함과 아울러 상기 박막 트랜지스터의 드레인 전극을 노출시키는 접촉홀을 가지는 보호막과;상기 접촉홀을 통해 상기 박막 트랜지스터의 드레인 전극과 접속된 화소전극과;상기 게이트 라인과 상기 게이트 라인과 분리된 공통라인 중 어느 하나와, 상기 화소 전극에 의해 형성되며, 액정셀의 전압을 유지하는 스토리지 캐패시터를 구비하고,상기 스토리지 캐패시터는 상기 스토리지 캐패시터 내에서 상기 보호막이 제거되어 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 상기 게이트 절연막을 사이에 두고 중첩되어 형성되거나,상기 스토리지 캐패시터를 제외한 영역에서의 높이보다 상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막과 상기 게이트 절연막을 사이에 두고 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 중첩되어 형성되는 것을 특징으로 하는 박막 트랜지스터 어레이 기판.

- 삭제

- 제 1 항에 있어서,상기 공통라인은 상기 화소전극을 가로질러 형성된 것을 특징으로 하는 박막 트랜지스터 어레이 기판.

- 게이트 라인과 상기 게이트라인과 분리된 공통라인을 형성하는 단계와;상기 게이트 라인과 게이트 절연막을 사이에 두고 교차되는 데이터 라인과, 상기 게이트 라인과 데이터 라인의 교차영역에 박막 트랜지스터를 형성하는 단계와;상기 박막 트랜지스터를 덮도록 형성됨과 아울러 박막 트랜지스터의 드레인 전극을 노출시키는 접촉홀을 가지는 보호막을 형성하는 단계와;상기 접촉홀을 통해 상기 박막 트랜지스터의 드레인 전극과 접속되는 화소전극과, 상기 공통라인 및 게이트 라인 중 어느 하나와 상기 화소전극을 포함하며 액정셀의 전압을 유지하는 스토리지 캐패시터를 형성하는 단계를 포함하고,상기 스토리지 캐패시터는 상기 스토리지 캐패시터 내에서 상기 보호막이 제거되어 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 상기 게이트 절연막을 사이에 두고 중첩되어 형성되거나,상기 스토리지 캐패시터를 제외한 영역에서의 높이보다 상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막과 상기 게이트 절연막을 사이에 두고 상기 게이트 라인 및 공통 라인 중 어느 하나와 상기 화소 전극이 중첩되어 형성되는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

- 삭제

- 제 4 항에 있어서,상기 보호막을 형성하는 단계는상기 보호막 상에 회절 마스크를 정렬시키는 단계와;상기 회절 마스크를 이용하여 상기 스토리지 캐패시터를 제외한 영역에서보다 상기 스토리지 캐패시터의 형성 영역에서 낮은 높이를 가지는 포토레지스트 패턴을 형성하는 단계와;상기 포토레지스트 패턴을 마스크로 상기 보호막을 패터닝하여 상기 접촉홀을 형성하는 단계와;상기 포토레지스트 패턴을 애싱하여 상기 스토리지 캐패시터에 포함될 보호막을 노출시키는 단계와;상기 애싱된 포토레지스트 패턴을 마스크로 이용한 식각 공정을 통해 상기 스토리지 캐패시터를 제외한 영역에서의 높이보다 상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막을 형성하는 단계와;상기 애싱된 포토레지스트 패턴을 제거하는 단계를 포함하는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

- 제 6 항에 있어서,상기 스토리지 캐패시터 내에서 낮은 높이를 가지는 보호막은 식각 시간에 의해 상기 보호막의 높이가 조절되는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

- 제 4 항에 있어서,상기 공통라인은 상기 화소전극을 가로지르도록 형성되는 것을 특징으로 하는 박막 트랜지스터 어레이 기판의 제조방법.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020040101447A KR101085139B1 (ko) | 2004-12-03 | 2004-12-03 | 박막 트랜지스터 어레이 기판 및 그 제조 방법 |

| US11/293,888 US20060132411A1 (en) | 2004-12-03 | 2005-12-02 | Thin film transistor array substrate and fabricating method thereof |

| US12/019,063 US8278161B2 (en) | 2004-12-03 | 2008-01-24 | Method for fabricating a thin film transistor array substrate with a thinned protective film over a storage capacitor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020040101447A KR101085139B1 (ko) | 2004-12-03 | 2004-12-03 | 박막 트랜지스터 어레이 기판 및 그 제조 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20060062573A KR20060062573A (ko) | 2006-06-12 |

| KR101085139B1 true KR101085139B1 (ko) | 2011-11-21 |

Family

ID=36595033

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020040101447A KR101085139B1 (ko) | 2004-12-03 | 2004-12-03 | 박막 트랜지스터 어레이 기판 및 그 제조 방법 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US20060132411A1 (ko) |

| KR (1) | KR101085139B1 (ko) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101034744B1 (ko) * | 2004-06-25 | 2011-05-17 | 엘지디스플레이 주식회사 | 액정표시장치의 박막트랜지스터 구조 |

| KR101217157B1 (ko) * | 2005-10-20 | 2012-12-31 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이 기판 및 그 제조 방법 |

| KR20080007813A (ko) | 2006-07-18 | 2008-01-23 | 삼성전자주식회사 | 박막 트랜지스터 어레이 기판 |

| KR101288426B1 (ko) * | 2006-10-10 | 2013-07-23 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| JP6019329B2 (ja) * | 2011-03-31 | 2016-11-02 | 株式会社Joled | 表示装置および電子機器 |

| KR101924079B1 (ko) | 2012-07-06 | 2018-12-03 | 삼성디스플레이 주식회사 | 액정 표시 장치 및 그 제조 방법 |

| CN103698955A (zh) * | 2013-12-13 | 2014-04-02 | 京东方科技集团股份有限公司 | 像素单元、阵列基板及其制造方法和显示装置 |

| KR101556160B1 (ko) * | 2015-01-07 | 2015-10-02 | 삼성디스플레이 주식회사 | 박막 트랜지스터 어레이 기판 |

| CN106200177B (zh) * | 2016-08-25 | 2019-11-26 | 武汉华星光电技术有限公司 | 显示器及其显示面板 |

| CN109860207B (zh) * | 2019-02-27 | 2022-07-19 | 合肥鑫晟光电科技有限公司 | 一种阵列基板、其制作方法、显示面板及显示装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100303134B1 (ko) * | 1995-05-09 | 2002-11-23 | 엘지.필립스 엘시디 주식회사 | 액정표시소자및그제조방법. |

| KR970011972A (ko) * | 1995-08-11 | 1997-03-29 | 쯔지 하루오 | 투과형 액정 표시 장치 및 그 제조 방법 |

| CN1148600C (zh) * | 1996-11-26 | 2004-05-05 | 三星电子株式会社 | 薄膜晶体管基片及其制造方法 |

| TW413844B (en) * | 1998-11-26 | 2000-12-01 | Samsung Electronics Co Ltd | Manufacturing methods of thin film transistor array panels for liquid crystal displays and photolithography method of thin films |

| TW518442B (en) * | 2000-06-29 | 2003-01-21 | Au Optronics Corp | Thin film transistor liquid crystal display and its manufacture method |

| JP4619508B2 (ja) * | 2000-09-27 | 2011-01-26 | シャープ株式会社 | パターン形成方法、薄膜トランジスタマトリクス基板の製造方法および露光マスク |

| KR100456137B1 (ko) * | 2001-07-07 | 2004-11-08 | 엘지.필립스 엘시디 주식회사 | 액정표시장치의 어레이 기판 및 그의 제조방법 |

| KR100878280B1 (ko) * | 2002-11-20 | 2009-01-13 | 삼성전자주식회사 | 4색 구동 액정 표시 장치 및 이에 사용하는 표시판 |

| JP4615197B2 (ja) * | 2002-08-30 | 2011-01-19 | シャープ株式会社 | Tftアレイ基板の製造方法および液晶表示装置の製造方法 |

| KR100886241B1 (ko) * | 2002-09-10 | 2009-02-27 | 엘지디스플레이 주식회사 | 액정표시소자의 제조방법 |

| TWI242671B (en) * | 2003-03-29 | 2005-11-01 | Lg Philips Lcd Co Ltd | Liquid crystal display of horizontal electronic field applying type and fabricating method thereof |

| KR101157978B1 (ko) * | 2005-06-30 | 2012-06-25 | 엘지디스플레이 주식회사 | 액정표시패널의 제조방법 |

-

2004

- 2004-12-03 KR KR1020040101447A patent/KR101085139B1/ko active IP Right Grant

-

2005

- 2005-12-02 US US11/293,888 patent/US20060132411A1/en not_active Abandoned

-

2008

- 2008-01-24 US US12/019,063 patent/US8278161B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR20060062573A (ko) | 2006-06-12 |

| US20060132411A1 (en) | 2006-06-22 |

| US8278161B2 (en) | 2012-10-02 |

| US20080113475A1 (en) | 2008-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7411217B2 (en) | Thin film transistor array substrate and manufacturing method of the same | |

| KR100556702B1 (ko) | 표시 소자용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR101121620B1 (ko) | 표시 소자용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR100499371B1 (ko) | 박막 트랜지스터 어레이 기판 및 그 제조 방법 | |

| US7316944B2 (en) | Fabricating method of a liquid crystal display device | |

| KR100456137B1 (ko) | 액정표시장치의 어레이 기판 및 그의 제조방법 | |

| KR100682358B1 (ko) | 액정 표시 패널 및 제조 방법 | |

| KR101126396B1 (ko) | 박막트랜지스터 어레이 기판 및 그 제조방법 | |

| US8278161B2 (en) | Method for fabricating a thin film transistor array substrate with a thinned protective film over a storage capacitor | |

| KR100556701B1 (ko) | 표시 소자용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR20070063734A (ko) | 박막 트랜지스터 어레이 기판 및 그 제조 방법 | |

| KR100870522B1 (ko) | 액정표시소자 및 그 제조방법 | |

| KR20050001936A (ko) | 박막 트랜지스터 및 그 제조 방법과 이를 이용한 박막트랜지스터 어레이 기판 및 그 제조 방법 | |

| KR20040016489A (ko) | 액정표시소자 및 그 제조방법 | |

| KR100968341B1 (ko) | 박막 트랜지스터 어레이 기판 및 그 제조 방법 | |

| KR20080110124A (ko) | 액정표시패널 및 그 제조방법 | |

| KR100583314B1 (ko) | 표시 소자용 박막 트랜지스터 기판 및 그 제조 방법 | |

| KR20060067281A (ko) | 박막 트랜지스터 기판 및 그 제조방법 | |

| KR100619624B1 (ko) | 박막 트랜지스터 어레이 기판 및 그 제조 방법 | |

| KR100682362B1 (ko) | 액정 표시 패널 및 제조 방법 | |

| KR20040016963A (ko) | 박막트랜지스터 어레이 기판의 제조방법용 마스크 | |

| KR20050050241A (ko) | 박막 트랜지스터 어레이 기판 및 그 제조 방법 | |

| KR101142981B1 (ko) | 박막 트랜지스터 어레이 기판 및 그 제조 방법 | |

| KR100558711B1 (ko) | 박막 트랜지스터 어레이 기판 및 그 제조 방법 | |

| KR20080001990A (ko) | 액정표시패널 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20141021 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20151028 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20161012 Year of fee payment: 6 |

|

| FPAY | Annual fee payment |

Payment date: 20171016 Year of fee payment: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20181015 Year of fee payment: 8 |