JP7686817B1 - アイソレータ - Google Patents

アイソレータ Download PDFInfo

- Publication number

- JP7686817B1 JP7686817B1 JP2024020877A JP2024020877A JP7686817B1 JP 7686817 B1 JP7686817 B1 JP 7686817B1 JP 2024020877 A JP2024020877 A JP 2024020877A JP 2024020877 A JP2024020877 A JP 2024020877A JP 7686817 B1 JP7686817 B1 JP 7686817B1

- Authority

- JP

- Japan

- Prior art keywords

- coil

- substrate

- semiconductor chip

- flexible printed

- wiring board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F27/00—Details of transformers or inductances, in general

- H01F27/28—Coils; Windings; Conductive connections

- H01F27/2804—Printed windings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/20—Inductors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W44/00—Electrical arrangements for controlling or matching impedance

- H10W44/501—Inductive arrangements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/611—Insulating or insulated package substrates; Interposers; Redistribution layers for connecting multiple chips together

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/401—Package configurations characterised by multiple insulating or insulated package substrates, interposers or RDLs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/111—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Coils Or Transformers For Communication (AREA)

- Combinations Of Printed Boards (AREA)

- Networks Using Active Elements (AREA)

- Near-Field Transmission Systems (AREA)

Abstract

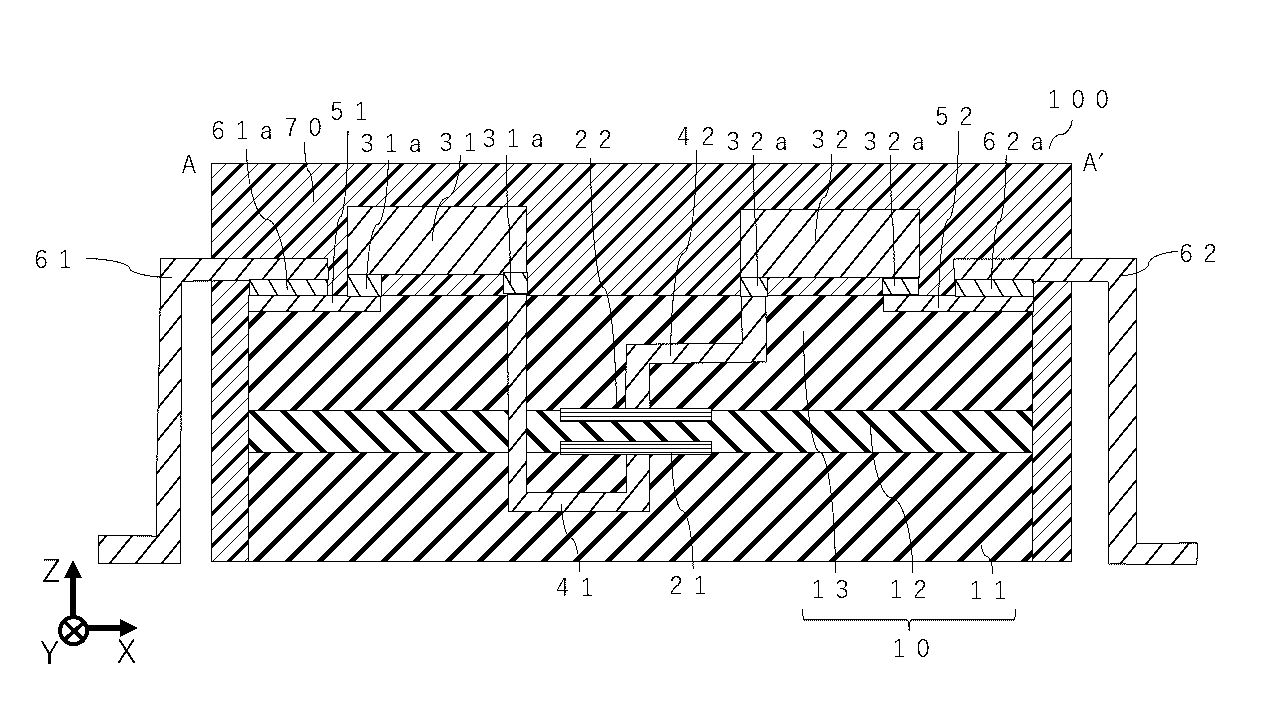

【解決手段】実施形態のアイソレータは、リジッド基板である第1リジッド基板と、前記第1リジッド基板に第1方向に積層されたフレキシブルプリント配線板である第1フレキシブルプリント配線板と、を有する基板と、前記第1フレキシブルプリント配線板に設けられた第1コイルと、前記第1フレキシブルプリント配線板に設けられ、前記第1方向において前記第1コイルと離間し対向する第2コイルと、前記基板の上に設けられた第1半導体チップと、前記基板の上に設けられた第2半導体チップと、前記基板の中に設けられ、前記第1半導体チップと前記第1コイルを接続する第1配線と、前記基板の中に設けられ、前記第2半導体チップと前記第2コイルを接続する第2配線と、を有する。

【選択図】 図3

Description

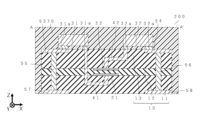

図1は、本実施形態に係るアイソレータ100を例示する模式的平面図である。

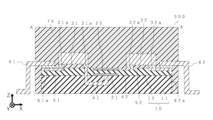

図5は、第1実施形態の第1変形例に係るアイソレータ101の断面構造を示している。第1実施形態に係るアイソレータ100と共通する部分については一部説明を省略する。

図6は、第2実施形態に係るアイソレータ200の断面構造を表している。第1実施形態に係るアイソレータ100と共通する部分については一部説明を省略する。

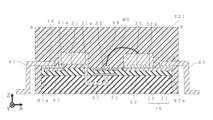

図7は、第3実施形態に係るアイソレータ300の断面構造を表している。第1実施形態に係るアイソレータ100と共通する部分については一部説明を省略する。

第3実施形態の第1変形例に係るアイソレータ301について、図8を参照しつつ説明する。図7に示すアイソレータ300と共通する部分は一部説明を省略する。

図9は、第4実施形態に係るアイソレータ400の断面構造を表している。第1実施形態に係るアイソレータ100と共通する部分については一部説明を省略する。

11・・・第1リジッド基板

12・・・第1フレキシブルプリント配線板

13・・・第2リジッド基板

21・・・第1コイル

22・・・第2コイル

31・・・第1半導体チップ

32・・・第2半導体チップ

31a、32a・・・接着層

41・・・第1配線

42・・・第2配線

41a・・・第1部分

42a・・・第1部分

43・・・第3配線

51、52、53、54・・・導電層

55、56・・・貫通導電領域

57、58・・・裏面電極

61、62・・・リードフレーム

61a、62a・・・接着層

70・・・樹脂部

81・・・第1ダイパッド

82・・・第2ダイパッド

83・・・第3ダイパッド

84、85・・・外部端子

W0、W1、W2、W3、W4・・・ワイヤ

Claims (9)

- リジッド基板である第1リジッド基板と、前記第1リジッド基板に第1方向に積層されたフレキシブルプリント配線板である第1フレキシブルプリント配線板と、を有する基板と、

前記第1フレキシブルプリント配線板に設けられた第1コイルと、

前記第1フレキシブルプリント配線板に設けられ、前記第1方向において前記第1コイルと離間し対向する第2コイルと、

前記基板の上に設けられた第1半導体チップと、

前記基板の上に設けられた第2半導体チップと、

前記基板の中に設けられ、前記第1半導体チップと前記第1コイルを接続する第1配線と、

前記基板の中に設けられ、前記第2半導体チップと前記第2コイルを接続する第2配線と、

を有するアイソレータ。 - 前記第1フレキシブルプリント配線板は、前記第1リジッド基板の上に設けられ、

前記基板は、前記第1フレキシブルプリント配線板の上に設けられた第2リジッド基板をさらに有する、

請求項1に記載のアイソレータ。 - 前記第1配線は、前記第2リジッド基板の上面から前記第1フレキシブルプリント配線板の下面まで前記第1方向に伸びる、

請求項2に記載のアイソレータ。 - 前記第1配線は、前記第1フレキシブルプリント配線板に形成され、前記第1フレキシブルプリント配線板の下面に沿って伸び、前記第1コイルと接続される第1部分を有する、

請求項3に記載のアイソレータ。 - 前記第1半導体チップ及び前記第2半導体チップを封止する樹脂部と、

前記第1半導体チップ又は前記第2半導体チップとそれぞれ電気的に接続される複数のリードフレームと、

をさらに有する、

請求項3に記載のアイソレータ。 - 前記第1半導体チップ及び前記第2半導体チップを封止する樹脂部と、

前記第1リジッド基板に設けられ、前記樹脂部から露出する複数の裏面電極と、

前記基板の中を前記第1方向に延伸して設けられた貫通導電領域と、

前記貫通導電領域と、前記第1半導体チップ又は前記第2半導体チップを接続する導電層と、

をさらに有する、請求項3に記載のアイソレータ。 - 第1ダイパッドと、

前記第1ダイパッドの上に設けられた第1半導体チップと、

前記第1ダイパッドと離間して設けられた第2ダイパッドと、

前記第2ダイパッドの上に設けられ、リジッド基板である第1リジッド基板と、前記第1リジッド基板に第1方向に積層されたフレキシブルプリント配線板である第1フレキシブルプリント配線板と、を有する基板と、

前記第1フレキシブルプリント配線板に設けられた第1コイルと、

前記第1フレキシブルプリント配線板に設けられ、前記第1方向において前記第1コイルと離間し対向する第2コイルと、

前記基板の上に設けられ、前記基板の中に設けられた第3配線によって前記第2コイルと接続された電極パッドと、

前記第1ダイパッド及び前記第2ダイパッドと離間して設けられた第3ダイパッドと、

前記第3ダイパッドの上に設けられた第2半導体チップと、

前記第1半導体チップと、前記第2ダイパッドとを接続する第1ワイヤと、

前記電極パッドと、前記第2半導体チップとを接続する第2ワイヤと、

を有するアイソレータ。 - 前記第1フレキシブルプリント配線板は、

前記第1コイルが下面に設けられ、前記第2コイルが上面に設けられる基材と、

前記基材を前記第1方向に挟むように、上面と下面のそれぞれに前記第1コイル又は前記第2コイルの前記第1方向の厚さと同等以上の厚さで設けられた絶縁体と、を有する、

請求項1乃至7のいずれか1項に記載のアイソレータ。 - 前記基材は、ポリイミドを含むフィルム状の絶縁材料からなり、

前記絶縁体は、熱硬化性樹脂を含む、

請求項8に記載のアイソレータ。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2024020877A JP7686817B1 (ja) | 2024-02-15 | 2024-02-15 | アイソレータ |

| CN202411003168.8A CN120497253A (zh) | 2024-02-15 | 2024-07-25 | 隔离器 |

| US18/815,554 US20250266409A1 (en) | 2024-02-15 | 2024-08-26 | Isolator |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2024020877A JP7686817B1 (ja) | 2024-02-15 | 2024-02-15 | アイソレータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP7686817B1 true JP7686817B1 (ja) | 2025-06-02 |

| JP2025125043A JP2025125043A (ja) | 2025-08-27 |

Family

ID=95895103

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2024020877A Active JP7686817B1 (ja) | 2024-02-15 | 2024-02-15 | アイソレータ |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20250266409A1 (ja) |

| JP (1) | JP7686817B1 (ja) |

| CN (1) | CN120497253A (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7170685B2 (ja) * | 2020-03-19 | 2022-11-14 | 株式会社東芝 | アイソレータ |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007240404A (ja) | 2006-03-10 | 2007-09-20 | Nippon Soken Inc | 運動検出装置 |

| JP2012182740A (ja) | 2011-03-02 | 2012-09-20 | Nitto Denko Corp | アイソレータ用回路基板、アイソレータおよびそれらの製造方法 |

| WO2016148113A1 (ja) | 2015-03-18 | 2016-09-22 | タツタ電線株式会社 | ストレッチャブルケーブルおよびストレッチャブル回路基板 |

| JP2022543053A (ja) | 2019-08-20 | 2022-10-07 | ステムコ カンパニー リミテッド | コイル装置 |

| JP2023141929A (ja) | 2022-03-24 | 2023-10-05 | 株式会社東芝 | アイソレータ |

| JP2023143993A (ja) | 2020-03-19 | 2023-10-06 | 株式会社東芝 | アイソレータ |

-

2024

- 2024-02-15 JP JP2024020877A patent/JP7686817B1/ja active Active

- 2024-07-25 CN CN202411003168.8A patent/CN120497253A/zh active Pending

- 2024-08-26 US US18/815,554 patent/US20250266409A1/en active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007240404A (ja) | 2006-03-10 | 2007-09-20 | Nippon Soken Inc | 運動検出装置 |

| JP2012182740A (ja) | 2011-03-02 | 2012-09-20 | Nitto Denko Corp | アイソレータ用回路基板、アイソレータおよびそれらの製造方法 |

| WO2016148113A1 (ja) | 2015-03-18 | 2016-09-22 | タツタ電線株式会社 | ストレッチャブルケーブルおよびストレッチャブル回路基板 |

| JP2022543053A (ja) | 2019-08-20 | 2022-10-07 | ステムコ カンパニー リミテッド | コイル装置 |

| JP2023143993A (ja) | 2020-03-19 | 2023-10-06 | 株式会社東芝 | アイソレータ |

| JP2023141929A (ja) | 2022-03-24 | 2023-10-05 | 株式会社東芝 | アイソレータ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN120497253A (zh) | 2025-08-15 |

| JP2025125043A (ja) | 2025-08-27 |

| US20250266409A1 (en) | 2025-08-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7372131B2 (en) | Routing element for use in semiconductor device assemblies | |

| KR20010086344A (ko) | 적층형 반도체 장치 | |

| US8981579B2 (en) | Impedance controlled packages with metal sheet or 2-layer rdl | |

| KR100606295B1 (ko) | 회로 모듈 | |

| JPWO2007086481A1 (ja) | 電子デバイスパッケージ、モジュール、および電子機器 | |

| CN100505242C (zh) | 多层构成半导体微型组件 | |

| US12101884B2 (en) | Isolator | |

| WO2018235715A1 (ja) | モジュールおよびその製造方法 | |

| JP7686817B1 (ja) | アイソレータ | |

| KR101139084B1 (ko) | 다층 프린트 기판 및 그 제조 방법 | |

| JP4071782B2 (ja) | 半導体装置 | |

| KR102345061B1 (ko) | 반도체 패키지 | |

| JPH02343A (ja) | 電子部品搭載用基板 | |

| US20240321850A1 (en) | Isolator | |

| JP7788972B2 (ja) | アイソレータ | |

| US20260082954A1 (en) | Isolator | |

| JPWO2012086107A1 (ja) | 電子部品実装構造中間体、電子部品実装構造体および電子部品実装構造体の製造方法 | |

| JP2009231480A (ja) | 半導体装置 | |

| JP2009218390A (ja) | 半導体装置およびその製造方法 | |

| CN118693061A (zh) | 隔离器 | |

| JPH11176975A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20240520 |

|

| RD07 | Notification of extinguishment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7427 Effective date: 20250321 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20250422 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20250521 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7686817 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |