JP7635155B2 - 光電子構造素子、画素、ディスプレイ配置構造体およびそれに関する方法 - Google Patents

光電子構造素子、画素、ディスプレイ配置構造体およびそれに関する方法 Download PDFInfo

- Publication number

- JP7635155B2 JP7635155B2 JP2021568189A JP2021568189A JP7635155B2 JP 7635155 B2 JP7635155 B2 JP 7635155B2 JP 2021568189 A JP2021568189 A JP 2021568189A JP 2021568189 A JP2021568189 A JP 2021568189A JP 7635155 B2 JP7635155 B2 JP 7635155B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- pixel

- semiconductor

- optoelectronic component

- semiconductor element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2074—Display of intermediate tones using sub-pixels

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/075—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H10H20/00

- H01L25/0753—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H10H20/00 the devices being arranged next to each other

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/819—Bodies characterised by their shape, e.g. curved or truncated substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/84—Coatings, e.g. passivation layers or antireflective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/84—Coatings, e.g. passivation layers or antireflective coatings

- H10H20/841—Reflective coatings, e.g. dielectric Bragg reflectors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/85—Packages

- H10H20/851—Wavelength conversion means

- H10H20/8515—Wavelength conversion means not being in contact with the bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/85—Packages

- H10H20/855—Optical field-shaping means, e.g. lenses

- H10H20/856—Reflecting means

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/85—Packages

- H10H20/857—Interconnections, e.g. lead-frames, bond wires or solder balls

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H29/00—Integrated devices, or assemblies of multiple devices, comprising at least one light-emitting semiconductor element covered by group H10H20/00

- H10H29/10—Integrated devices comprising at least one light-emitting semiconductor component covered by group H10H20/00

- H10H29/14—Integrated devices comprising at least one light-emitting semiconductor component covered by group H10H20/00 comprising multiple light-emitting semiconductor components

- H10H29/142—Two-dimensional arrangements, e.g. asymmetric LED layout

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N69/00—Integrated devices, or assemblies of multiple devices, comprising at least one superconducting element covered by group H10N60/00

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/034—Manufacture or treatment of coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/036—Manufacture or treatment of packages

- H10H20/0363—Manufacture or treatment of packages of optical field-shaping means

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/813—Bodies having a plurality of light-emitting regions, e.g. multi-junction LEDs or light-emitting devices having photoluminescent regions within the bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/81—Bodies

- H10H20/822—Materials of the light-emitting regions

- H10H20/824—Materials of the light-emitting regions comprising only Group III-V materials, e.g. GaP

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Theoretical Computer Science (AREA)

- Led Devices (AREA)

- Led Device Packages (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Electroluminescent Light Sources (AREA)

Description

ディスプレイなどの多くの用途では、光電子構造素子はモノリシックに組み立てられている。したがって、個々の構造素子はボードまたはバックプレーンに配置されるのではなく、光電子構造素子を基板に統合し、これらの素子を個別に駆動制御できるようにしたものである。これによって、小型化が可能になるだけでなく、転写プロセスおよびはんだ付け工程が少なくて済むという利点もある。さらに、このようなモノリシックモジュールは、個々の構造素子のサイズとモジュールのサイズとの両方について容易にスケーリングすることができる。構造素子は、自由に定義可能なマトリクス状に配置することができる。このようなスケーリング効果は、特に大量生産の際に非常に有効である。

一態様では、反射面を追加した誘電体フィルターを取り付けたLEDの放射パターンの改善が関係している。本開示の第1の態様による光電子構造素子、特にLEDは、少なくとも1つの半導体素子と、1つの誘電体フィルターと、1つの反射材料とを含む。

以下の構成は、主に表示デバイスおよびディスプレイ、ひいてはモノリシックに統合された光電子構造素子を有するベースユニットおよびモジュールに関するものである。しかしながら、本発明は、この用途または図示のモノリシックな構成要素に限定されるものではない。むしろ、提示された原理および構成は、スケーリングが必要な広範囲の電子用途およびアプリケーションに適しているように一般化することができる。特に、指向性を持った放射に関する態様は、図18の画素の冗長性および観点に関する態様と組み合わせることができる。同じことが、図18~図21の構成にも当てはまり、それらの原理は、例えば、図5と図6あるいは図8~図16の構成との組み合わせに適している。ここで示した例は、図1あるいは図2Bのようにミラーと組み合わせることもできる。これは、構成だけでなく、主に特許請求の範囲に記載されているこれらの態様の特徴にも当てはまる。

更なる光電子構造素子、ディスプレイ配置構造体、光電子デバイス、画素、アレイ、および種々の方法を、以下に対象として述べる。

[対象1]

光電子構造素子であって、

光を発生させるように形成された活性ゾーンを有する、少なくとも1つの半導体素子と、

前記少なくとも1つの半導体素子の第1の主表面の上に配置されており、所定の方向にのみ光を透過するように形成された誘電体フィルターと、

前記少なくとも1つの半導体素子の少なくとも一方の側面および前記誘電体フィルターの少なくとも一方の側面に配置された反射材料と

を有する、光電子構造素子。

[対象2]

前記少なくとも1つの半導体素子の少なくとも1つの側面が、前記活性ゾーンの高さで傾斜して延びている、対象1記載の光電子構造素子。

[対象3]

前記少なくとも1つの半導体素子が、第1の端子と第2の端子とを有しており、

前記反射材料が、導電性であり、前記少なくとも1つの半導体素子の第1の端子に結合されている、対象1または2記載の光電子構造素子。

[対象4]

前記反射材料が、電流供給用の前記第1の端子に接触するように、光源の対向する2つの側面でのみ導電性に形成されている、対象3記載の光電子構造素子。

[対象5]

前記反射材料が、電流供給用の前記端子から絶縁されるように、他の2つの側では非導電性に形成されている、対象4記載の光電子構造素子。

[対象6]

前記誘電体フィルターが、放射方向に隣り合う前記半導体素子の層に少なくとも部分的に形成されている、対象1から5までのいずれか1つ記載の光電子構造素子。

[対象7]

前記誘電体フィルターが、異なる屈折率を有する第1の領域および第2の領域を有しており、変換材料が前記第1の領域を形成している、対象1から6までのいずれか1つ記載の光電子構造素子。

[対象8]

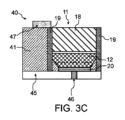

前記少なくとも1つの半導体素子が、前記第1の主表面に対向する第2の主表面を有しており、

前記少なくとも1つの半導体素子の第2の主表面の下には、反射層が配置されている、対象1から7までのいずれか1つ記載の光電子構造素子。

[対象9]

前記反射層が、少なくとも部分的に導電性であり、前記少なくとも1つの半導体素子の第2の端子に結合されている、対象1から8までのいずれか1つ記載の光電子構造素子。

[対象10]

前記反射層が電気的に絶縁されており、1つ以上の導電層が前記反射層の上および/または下に配置されている、対象8記載の光電子構造素子。

[対象11]

電気絶縁性の第1の材料が、前記反射材料と前記反射層との間に配置されており、特に前記電気絶縁性の第1の材料は、前記少なくとも1つの半導体素子よりも低い屈折率を有している、対象1から10までのいずれか1つ記載の光電子構造素子。

[対象12]

前記少なくとも1つの半導体素子と前記誘電体フィルターとの間に、表面が粗面化された層が配置されている、対象1から11までのいずれか1つ記載の光電子構造素子。

[対象13]

前記光電子構造素子が、

光出射面にあり、無機色素または量子ドットを有している変換材料;または

前記誘電体フィルターと前記半導体材料との間にあり、無機色素または量子ドットを有している変換材料

をさらに含む、対象1から12までのいずれか1つ記載の光電子構造素子。

[対象14]

前記少なくとも1つの半導体素子の第1の主表面が、粗面化された表面を有している、対象1から13までのいずれか1つ記載の光電子構造素子。

[対象15]

前記少なくとも1つの半導体素子が、少なくとも140μmの横方向の広がりおよび/または少なくとも5μmの高さを有している、対象1から14までのいずれか1つ記載の光電子構造素子。

[対象16]

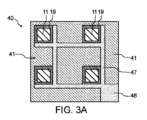

前記少なくとも1つの半導体素子が、アレイ状に配置された複数の半導体素子を含んでおり、隣り合う半導体素子は、反射材料によって互いに分離されている、対象1から15までのいずれか1つ記載の光電子構造素子。

[対象17]

前記反射材料が導電性であり、前記半導体素子の前記第1の端子が前記反射材料を介して共通の外部端子に接続されている、対象11記載の光電子構造素子。

[対象18]

前記少なくとも1つの半導体素子が、並置された複数の半導体素子を含んでおり、隣り合う半導体素子の間には、電気絶縁性の第2の材料が配置されている、対象1から17までのいずれか1つ記載の光電子構造素子。

[対象19]

前記反射材料が導電性であり、前記電気絶縁性の第2の材料の上および/または下および/または内部には、前記半導体素子の前記第1の端子を共通の外部端子に接続する導体トラックが延在している、対象1から18までのいずれか1つ記載の光電子構造素子。

[対象20]

前記半導体素子の前記第2の端子が、個別に駆動制御可能である、対象1から19までのいずれか1つ記載の光電子構造素子。

[対象21]

前記光電子構造素子が、前記誘電体フィルターの上に配置されたレンズをさらに含む、対象1から20までのいずれか1つ記載の光電子構造素子。

[対象22]

光電子構造素子を製造する方法であって、

光を発生させるように形成された活性ゾーンを有する、前述または後述の対象のうちいずれか1つ記載の少なくとも1つの半導体素子を提供するステップと、

前記少なくとも1つの半導体素子の第1の主表面の上に誘電体フィルターを配置するステップであって、前記誘電体フィルターは、所定の方向にのみ光を透過するように形成されている、ステップと、

前記少なくとも1つの半導体素子の少なくとも1つの側面および前記誘電体フィルターの少なくとも1つの側面に、反射材料を配置するステップと

を含む、方法。

[対象23]

ディスプレイのピクセルを生成するための光電子構造素子を備えた画素であって、

前記画素は、少なくとも2つのサブ画素、特に同色発光の2つのサブ画素から形成されており、特に各サブ画素は光電子構造素子によって形成されており、

同一の画素素子の隣り合う2つのサブ画素の間にはサブ画素分離素子が設けられており、

前記サブ画素分離素子は、それぞれのサブ画素の電気駆動制御に関して分離を行うように構成されており、それぞれ前記サブ画素が発する光に関して光学的に結合を行うように構成されている、画素。

[対象24]

前記サブ画素が共通のエピタキシャル層を有しており、前記サブ画素分離素子が、主発光方向のエピタキシャル層平面に対して横方向に前記エピタキシャル層内でトレンチ状に延在している、対象23記載の画素。

[対象25]

前記画素のサブ画素が、互いに独立して電気的に接触接続可能であるかつ/または駆動制御可能である、対象23または24記載の画素。

[対象26]

少なくとも2つの前記サブ画素が、前記サブ画素分離素子によって分離された共通の活性層を有している、対象23から25までのいずれか1つ記載の画素。

[対象27]

前記サブ画素分離素子が、前記画素の活性層まで延在しているか、または少なくとも部分的に当該画素を貫通するように延在している、対象23から26までのいずれか1つ記載の画素。

[対象28]

前記サブ画素分離素子が、特に前記活性層の領域において、拡散されたドーパントによって生じた量子井戸インターミキシングによって形成されている、対象23から27までのいずれか1つ記載の画素。

[対象29]

前記画素が、前記画素の表面にわたって延在しているレンズをさらに含む、対象23から28までのいずれか1つ記載の画素。

[対象30]

透明な導電層が表面に形成されている、対象23から29までのいずれか1つ記載の画素。

[対象31]

少なくとも1つのサブ画素を接触させるための少なくとも1つのコンタクト面が、前記光出射面と反対側の面に設けられている、対象23から30までのいずれか1つ記載の画素。

[対象32]

対象23から31までのいずれか1つ記載の複数の画素を有するディスプレイ配置構造体であって、

隣り合う2つの画素の間に画素素子分離層が設けられており、前記画素素子分離層は、それぞれの画素の駆動制御に関して前記隣り合う画素を電気的に分離し、かつ前記画素が発する光に関して前記隣り合う画素を光学的に分離するように構成されている、ディスプレイ配置構造体。

[対象33]

前記画素と関連する前記サブ画素とが共通のエピタキシャル層を有しており、前記画素素子分離層が、主発光方向の前記エピタキシャル層平面に対して横方向に前記エピタキシャル層内にトレンチ状に延在している、対象32記載のディスプレイ配置構造体。

[対象34]

前記画素素子分離層のトレンチ深さd1は、前記サブ画素分離素子のトレンチ深さよりも大きい、対象32または33記載のディスプレイ配置構造体。

[対象35]

前記隣り合う画素またはサブ画素が、画素素子分離層および/またはサブ画素分離素子によって分離された活性層を含んでいる、対象32から34までのいずれか1つ記載のディスプレイ配置構造体。

[対象36]

前記ディスプレイ配置構造体が、前記画素のコンタクト領域に対応するコンタクト領域を有するキャリア層をさらに含み、前記キャリア層には、次の素子、すなわち

前記画素の電流供給のための導電線、

電流ドライバ回路または供給回路、および

輝度を調整するための制御回路

のうちの少なくとも1つが設けられている、対象32から35までのいずれか1つ記載のディスプレイ配置構造体。

[対象37]

画素を較正する方法であって、次のステップ、すなわち

対象23から31までのいずれか1つ記載の画素のサブ画素を駆動制御するステップと、

サブ画素の欠陥情報を検出するステップと、

前記欠陥情報を前記制御ユニットの記憶ユニットに記憶するステップと

を含む、方法。

[対象38]

画素のすべての個々のサブ画素について、駆動制御、検出および記憶が順次実行される、対象37記載の方法。

[対象39]

少なくとも2つの光電子構造素子を有し、n型ドープ層とp型ドープ層との間にあるそれぞれの構造素子が発光に適した活性ゾーンを形成しているアレイにおいて、

隣接して形成された2つの光電子構造素子の間で、n型ドープ側およびp型ドープ側からクラッド層までもしくはクラッド層内まで、または活性ゾーンまでもしくは少なくとも部分的に活性ゾーン内まで、最大厚さd c の材料遷移部が形成されるように、層シーケンスの材料が中断または除去されており、これにより前記材料遷移部における電気的および/または光学的な伝導性が低下する

ことを特徴とする、アレイ。

[対象40]

前記材料遷移部が、前記活性ゾーンと、前記活性ゾーンの少なくとも片側にある厚さの小さい残留層とを有している、対象39記載のアレイ。

[対象41]

除去された材料が、充填材料で少なくとも部分的に置き換えられている、対象39または40記載のアレイ。

[対象42]

除去された材料が、相対的に小さなバンドギャップを有し、ひいては前記活性ゾーンの光を吸収する材料で少なくとも部分的に置き換えられている、対象39から41までのいずれか1つ記載のアレイ。

[対象43]

除去された材料が、高い屈折率、特にドープされた材料または充填材料の屈折率よりも高い屈折率を有する材料で少なくとも部分的に置き換えられている、対象39から42までのいずれか1つ記載のアレイ。

[対象44]

前記光を吸収する材料および/または前記高い屈折率を有する材料が、それぞれの材料遷移部に施与されている、対象39から43までのいずれか1つ記載のアレイ。

[対象45]

前記高い屈折率を有する材料が、屈折率を高める材料を前記充填材料に、特にそれぞれのクラッド層までの拡散または注入によって、形成されている、対象39から44までのいずれか1つ記載のアレイ。

[対象46]

光吸収を高める材料および/または電気抵抗を高める材料が、それぞれの材料遷移部の前記活性ゾーンに拡散または注入されている、対象39から45までのいずれか1つ記載のアレイ。

[対象47]

少なくとも1つの光学構造体、特にフォトニック結晶および/またはブラッグミラーが、前記材料遷移部に沿って、前記材料遷移部の上に、または前記材料遷移部内に作製されている、対象39から46までのいずれか1つ記載のアレイ。

[対象48]

2つの互いに対向する電気的コンタクトによって前記材料遷移部の2つの主表面に電気バイアスが印加され、それぞれの材料遷移部を通して電界が発生する、対象39から47までのいずれか1つ記載のアレイ。

[対象49]

前記材料遷移部の前記2つの主表面の少なくとも一方の面に施与されたまたは成長させたn型ドープ材料および/またはp型ドープ材料によって、それぞれの材料遷移部を通して電界が発生する、対象39から48までのいずれか1つ記載のアレイ。

[対象50]

前記材料遷移部の露出した主表面および/または前記光電子構造素子の露出した表面領域が、特に二酸化ケイ素を有するそれぞれのパッシベーション層によって、電気的に絶縁され、パッシベーションされている、対象39から49までのいずれか1つ記載のアレイ。

[対象51]

前記光電子構造素子の前記主表面が、コンタクト層によって電気的に接触接続されている、対象39から50までのいずれか1つ記載のアレイ。

[対象52]

光電子構造素子とそれに隣り合う光電子構造素子との間の前記材料および/または前記材料遷移部が、特に方向に応じて互いに異なるように形成されている、対象39から51までのいずれか1つ記載のアレイ。

[対象53]

前記アレイが、主放射方向に面している表面に施与された変換材料をさらに含む、対象39から52までのいずれか1つ記載のアレイ。

[対象54]

光電子画素のアレイを製造する方法であって、次のステップ、すなわち

n型ドープ層およびp型ドープ層の全体的に平面な層シーケンスをアレイに沿って提供するステップであって、これらの間に発光に適した活性ゾーンを形成する、ステップと、

-形成される隣り合う画素間の材料をn型ドープ側およびp型ドープ側から少なくとも部分的に除去するステップであって、それにより前記活性ゾーンを含む最大厚さd c の材料遷移部を残し、隣り合う画素間の電気的および/または光学的な伝導性を低下させるステップと

を含む、方法。

[対象55]

前記材料を除去するステップが、前記n型ドープ側およびp型ドープ側から非ドープのクラッド層までもしくは非ドープのクラッド層内まで、または活性ゾーンまでもしくは少なくとも部分的に活性ゾーン内まで層シーケンスを除去することを含む、対象54記載の方法。

[対象56]

前記n型ドープ側および/またはp型ドープ側から除去された材料が、充填材料で少なくとも部分的に置き換えられる、対象54記載の方法。

[対象57]

前記n型ドープ側および/またはp型ドープ側から除去された材料が、相対的に小さなバンドギャップを有し、ひいては前記活性ゾーンの光を吸収する材料で少なくとも部分的に置き換えられる、対象54から56までのいずれか1つ記載の方法。

[対象58]

前記n型ドープ側および/またはp型ドープ側から除去された材料が、高い屈折率、特にドープされた材料または充填材料の屈折率よりも高い屈折率を有する材料で置き換えられる、対象54から57までのいずれか1つ記載の方法。

[対象59]

前記光を吸収する材料および/または前記高い屈折率を有する材料が、それぞれの材料遷移部に施与される、対象54から58までのいずれか1つ記載の方法。

[対象60]

前記高い屈折率を有する材料が、前記充填材料に、特にそれぞれのクラッド層までの拡散または注入によって形成される、対象54から59までのいずれか1つ記載の方法。

[対象61]

前記n型ドープ側および/またはp型ドープ側から光吸収を高める材料および/または電気抵抗を高める材料が前記活性ゾーンに拡散または注入される、対象54から60までのいずれか1つ記載の方法。

[対象62]

前記n型ドープ側および/またはp型ドープ側から前記材料遷移部に沿って、前記材料遷移部の上にまたは前記材料遷移部内に、少なくとも1つの光学構造体、特にフォトニック結晶および/またはブラッグミラーが作製される、対象54から61までのいずれか1つ記載の方法。

[対象63]

前記n型ドープ側およびp型ドープ側から2つの互いに対向する電気的コンタクトが形成されて、前記材料遷移部の2つの主表面に電気バイアスが印加され、それぞれの材料遷移部を通して電界が発生する、対象54から62までのいずれか1つ記載の方法。

[対象64]

前記材料遷移部の前記2つの主表面のうちの少なくとも一方の面に施与されたまたは成長させたn型ドープ材料および/またはp型ドープ材料によって、それぞれの材料遷移部を通して電界が導入される、対象54から63までのいずれか1つ記載の方法。

[対象65]

前記方法が、前記材料遷移部の露出した主表面および/または前記画素の露出した表面領域を、特に二酸化ケイ素を有するそれぞれのパッシベーション層によって、電気的に絶縁し、パッシベーションすることを含む、対象54から64までのいずれか1つ記載の方法。

[対象66]

前記方法が、前記画素の主表面をコンタクト層によって電気的に接触接続することを含む、対象54から65までのいずれか1つ記載の方法。

[対象67]

前記画素とその隣り合う画素との間の材料および/または材料遷移部が、特に方向に応じて互いに異なるように形成される、対象54から66までのいずれか1つ記載の方法。

[対象68]

前記ステップが、最初は前記アレイの一方の主表面に対して実行され、その後、基板交換後に前記アレイの他方の主表面に対して実行される、対象54から67までのいずれか1つ記載の方法。

[対象69]

ディスプレイ配置構造体であって、

モノリシック集積回路とマトリクス状に配置されたIC基板コンタクトとを備えたIC基板部品と、

第1のドーピングを有する第1の半導体層と第2のドーピングを有する第2の半導体層とを有する半導体層シーケンスを含むモノリシック画素化オプトチップであって、前記第1の半導体層の電荷キャリアの極性は、前記第2の半導体層の電荷キャリアの極性とは異なり、前記半導体層シーケンスは積層方向を規定している、モノリシック画素化オプトチップと

を含み、

前記モノリシック画素化オプトチップ内には、マトリクス状に配置された光電子構造素子が存在し、

各光電子構造素子は、前記IC基板部品に面している背面と、第1の光源コンタクトとを有しており、前記第1の光源コンタクトは、前記第1の半導体層に接触する形で隣接し、前記IC基板コンタクトのそれぞれ1つに電気的に接続されている、ディスプレイ配置構造体において、

前記第1の光源コンタクトの前記背面への投影面積が、最大でも前記背面の面積の半分に相当し、

前記第1の光源コンタクトが、積層方向に対して垂直方向を指し示す横方向において背面側アブソーバで取り囲まれている

ことを特徴とする、ディスプレイ配置構造体。

[対象70]

前記第1の半導体層および前記第2の半導体層が、10 4 Sm -1 未満、好ましくは3・10 3 Sm -1 未満、さらに好ましくは10 3 Sm -1 未満のp型またはn型の伝導性を有している、対象69記載のディスプレイ配置構造体。

[対象71]

積層方向における前記第1の半導体層の層厚が、横方向における前記第1の光源コンタクトの最大対角線の最大10倍、好ましくは最大5倍である、対象69または70記載のディスプレイ配置構造体。

[対象72]

前記光電子構造素子の画素サイズが100μm超、特に120μm超、特に200μm~1000μmの範囲である、対象69から71までのいずれか1つ記載のディスプレイ配置構造体。

[対象73]

前記第1の光源コンタクトの前記背面への投影面積が、前記背面の面積の最大25%、好ましくは最大10%に相当している、対象69から72までのいずれか1つ記載のディスプレイ配置構造体。

[対象74]

前記背面側アブソーバが、積層方向に前記半導体シーケンス内へ延在している、対象69から73までのいずれか1つ記載のディスプレイ配置構造体。

[対象75]

各光電子構造素子の前記第2の半導体層の上で積層方向に、透明な材料からなる第2の光源コンタクトが配置されており、前記光源コンタクトは、モノリシック画素化オプトチップの正面側の透明なコンタクト層に電気的に接続されている、対象69から74までのいずれか1つ記載のディスプレイ配置構造体。

[対象76]

前記第2の光源コンタクトが、透明なコンタクト層自体によって形成されている、対象75記載のディスプレイ配置構造体。

[対象77]

前記第2の光源コンタクトが透明なコンタクト層に隣接しており、隣接して配置された前記光電子構造素子の前記第2の光源コンタクトは、積層方向に対して垂直方向を指し示す横方向において正面側アブソーバで互いに分離されている、対象69から76までのいずれか1つ記載のディスプレイ配置構造体。

[対象78]

前記正面側アブソーバは、積層方向とは逆向きに第2の半導体層まで、好ましくは第2の半導体層内まで延在している、対象69から77までのいずれか1つ記載のディスプレイ配置構造体。

[対象79]

積層方向を基準として、前記第1の光源コンタクトの下には、前記第1の光源コンタクトよりも横断面積が大きいオプトチップコンタクト素子が隣接している、対象69から78までのいずれか1つ記載のディスプレイ配置構造体。

[対象80]

前記ディスプレイ配置構造体が、前記モノリシック画素化オプトチップの表面に光変換素子をさらに含んでいる、対象69から79までのいずれか1つ記載のディスプレイ配置構造体。

[対象81]

ディスプレイ配置構造体を製造する方法であって、

モノリシック集積回路とマトリクス状に配置されたIC基板コンタクトとを備えたIC基板部品と、モノリシック画素化オプトチップとが電気的に接続されており、

前記モノリシック画素化オプトチップ内では、第1のドーピングを有する第1の半導体層と第2のドーピングを有する第2の半導体層とを有する半導体層シーケンスが成長され、前記第1の半導体層の電荷キャリアの極性は、前記第2の半導体層の電荷キャリアの極性とは異なり、前記半導体層シーケンスは積層方向を規定し、

前記モノリシック画素化オプトチップ内には、マトリクス状に配置された光電子構造素子が設置され、各光電子構造素子は、前記IC基板部品に面している背面と、第1の光源コンタクトとを有しており、前記第1の光源コンタクトは、前記第1の半導体層に接触する形で隣接し、前記IC基板コンタクトのそれぞれ1つに電気的に接続されている、方法において、

前記第1の光源コンタクトを、積層方向に対して垂直な投影面積が、前記背面の面積の最大でも半分を占めるような大きさで設置し、

前記第1の光源コンタクトを、積層方向に対して垂直方向を指し示す横方向において背面側アブソーバで取り囲む

ことを特徴とする、方法。

Claims (22)

- 光電子構造素子であって、

第1の主表面から光を発生させるように形成された活性ゾーンを有する、少なくとも1つの半導体素子と、

前記少なくとも1つの半導体素子の前記第1の主表面の上に配置されており、所定の方向にのみ光を透過するように形成された誘電体フィルターと、

前記少なくとも1つの半導体素子の少なくとも一方の側面および前記誘電体フィルターの少なくとも一方の側面に配置された反射材料と

を有する、光電子構造素子。 - 前記少なくとも1つの半導体素子の少なくとも1つの側面が、前記活性ゾーンの高さで傾斜して延びている、請求項1記載の光電子構造素子。

- 前記少なくとも1つの半導体素子が、第1の端子と第2の端子とを有しており、

前記反射材料が、導電性であり、前記少なくとも1つの半導体素子の第1の端子に結合されている、請求項1または2記載の光電子構造素子。 - 前記反射材料が、電流供給用の前記第1の端子に接触するように、光源の対向する2つの側面でのみ導電性に形成されている、請求項3記載の光電子構造素子。

- 前記反射材料が、電流供給用の前記端子から絶縁されるように、他の2つの側では非導電性に形成されている、請求項4記載の光電子構造素子。

- 前記誘電体フィルターが、放射方向に隣り合う前記半導体素子の層に少なくとも部分的に形成されている、請求項1から5までのいずれか1項記載の光電子構造素子。

- 前記誘電体フィルターが、異なる屈折率を有する第1の領域および第2の領域を有しており、変換材料が前記第1の領域を形成している、請求項1から6までのいずれか1項記載の光電子構造素子。

- 前記少なくとも1つの半導体素子が、前記第1の主表面に対向する第2の主表面を有しており、

前記少なくとも1つの半導体素子の第2の主表面の下には、反射層が配置されている、請求項3記載の光電子構造素子。 - 前記反射層が、少なくとも部分的に導電性であり、前記少なくとも1つの半導体素子の第2の端子に結合されている、請求項8記載の光電子構造素子。

- 前記反射層が電気的に絶縁されており、1つ以上の導電層が前記反射層の上および/または下に配置されている、請求項8記載の光電子構造素子。

- 電気絶縁性の第1の材料が、前記反射材料と前記反射層との間に配置されており、特に前記電気絶縁性の第1の材料は、前記少なくとも1つの半導体素子よりも低い屈折率を有している、請求項8から10までのいずれか1項記載の光電子構造素子。

- 前記少なくとも1つの半導体素子と前記誘電体フィルターとの間に、表面が粗面化された層が配置されている、請求項1から11までのいずれか1項記載の光電子構造素子。

- 前記光電子構造素子が、

光出射面にあり、無機色素または量子ドットを有している変換材料;または

前記誘電体フィルターと前記半導体素子との間にあり、無機色素または量子ドットを有している変換材料

をさらに含む、請求項1から12までのいずれか1項記載の光電子構造素子。 - 前記少なくとも1つの半導体素子の第1の主表面が、粗面化された表面を有している、請求項1から13までのいずれか1項記載の光電子構造素子。

- 前記少なくとも1つの半導体素子が、少なくとも140μmの横方向の広がりおよび/または少なくとも5μmの高さを有している、請求項1から14までのいずれか1項記載の光電子構造素子。

- 前記少なくとも1つの半導体素子が、アレイ状に配置された複数の半導体素子を含んでおり、隣り合う半導体素子は、前記反射材料によって互いに分離されている、請求項1から15までのいずれか1項記載の光電子構造素子。

- 前記反射材料が導電性であり、前記半導体素子の前記第1の端子が前記反射材料を介して共通の外部端子に接続されている、請求項3記載の光電子構造素子。

- 前記少なくとも1つの半導体素子が、並置された複数の半導体素子を含んでおり、隣り合う半導体素子の間には、電気絶縁性の第2の材料が配置されている、請求項3記載の光電子構造素子。

- 前記反射材料が導電性であり、前記電気絶縁性の第2の材料の上および/または下および/または内部には、前記半導体素子の前記第1の端子を共通の外部端子に接続する導体トラックが延在している、請求項18記載の光電子構造素子。

- 前記半導体素子の前記第2の端子が、個別に駆動制御可能である、請求項9記載の光電子構造素子。

- 前記光電子構造素子が、前記誘電体フィルターの上に配置されたレンズをさらに含む、請求項1から20までのいずれか1項記載の光電子構造素子。

- 光電子構造素子を製造する方法であって、

光を発生させるように形成された活性ゾーンを有する、請求項1から21までのいずれか1項記載の少なくとも1つの半導体素子を提供するステップと、

前記少なくとも1つの半導体素子の第1の主表面の上に誘電体フィルターを配置するステップであって、前記誘電体フィルターは、所定の方向にのみ光を透過するように形成されている、ステップと、

前記少なくとも1つの半導体素子の少なくとも1つの側面および前記誘電体フィルターの少なくとも1つの側面に、反射材料を配置するステップと

を含む、方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2025021121A JP2025081418A (ja) | 2019-05-14 | 2025-02-12 | 光電子構造素子、画素、ディスプレイ配置構造体およびそれに関する方法 |

Applications Claiming Priority (11)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102019112604 | 2019-05-14 | ||

| DE102019112604.5 | 2019-05-14 | ||

| DE102019113792 | 2019-05-23 | ||

| DE102019113792.6 | 2019-05-23 | ||

| DE102019129209.3 | 2019-10-29 | ||

| DE102019129209 | 2019-10-29 | ||

| DE102019131506 | 2019-11-21 | ||

| DE102019131506.9 | 2019-11-21 | ||

| PCT/EP2020/052191 WO2020157149A1 (de) | 2019-01-29 | 2020-01-29 | µ-LED, µ-LED ANORDNUNG, DISPLAY UND VERFAHREN ZU SELBEN |

| EPPCT/EP2020/052191 | 2020-01-29 | ||

| PCT/EP2020/058997 WO2020229043A2 (de) | 2019-05-14 | 2020-03-30 | Optoelektronisches bauelement, pixel, displayanordnung und verfahren |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2025021121A Division JP2025081418A (ja) | 2019-05-14 | 2025-02-12 | 光電子構造素子、画素、ディスプレイ配置構造体およびそれに関する方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022532641A JP2022532641A (ja) | 2022-07-15 |

| JP7635155B2 true JP7635155B2 (ja) | 2025-02-25 |

Family

ID=69941401

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021568189A Active JP7635155B2 (ja) | 2019-05-14 | 2020-03-30 | 光電子構造素子、画素、ディスプレイ配置構造体およびそれに関する方法 |

| JP2025021121A Pending JP2025081418A (ja) | 2019-05-14 | 2025-02-12 | 光電子構造素子、画素、ディスプレイ配置構造体およびそれに関する方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2025021121A Pending JP2025081418A (ja) | 2019-05-14 | 2025-02-12 | 光電子構造素子、画素、ディスプレイ配置構造体およびそれに関する方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20220223771A1 (ja) |

| JP (2) | JP7635155B2 (ja) |

| KR (1) | KR20220007069A (ja) |

| CN (1) | CN114127964A (ja) |

| DE (1) | DE112020002375A5 (ja) |

| WO (1) | WO2020229043A2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12310150B2 (en) * | 2019-08-06 | 2025-05-20 | Osram Opto Semiconductors Gmbh | Optoelectronic device having a photonic crystal structure |

| TW202512546A (zh) * | 2020-12-28 | 2025-03-16 | 大陸商上海顯耀顯示科技有限公司 | 微發光二極體結構及包括該結構之微發光二極體晶片 |

| CN113036008B (zh) * | 2021-03-12 | 2023-11-03 | 錼创显示科技股份有限公司 | 发光元件及显示面板 |

| TWI762234B (zh) | 2021-03-12 | 2022-04-21 | 錼創顯示科技股份有限公司 | 發光元件及顯示面板 |

| US11682752B2 (en) * | 2021-03-31 | 2023-06-20 | Lumileds Llc | Light-emitting device with nano-structured light extraction layer |

| DE102021129118A1 (de) * | 2021-11-09 | 2023-05-11 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Bauelement und optoelektronische vorrichtung mit strukturen zur reduzierung vom optischen übersprechen |

| US11869923B2 (en) * | 2021-12-14 | 2024-01-09 | Lumileds Llc | Light-emitting array with dielectric light collection structures |

| CN114122217A (zh) * | 2022-01-25 | 2022-03-01 | 北京芯海视界三维科技有限公司 | 发光器件和显示装置 |

| CN114122216A (zh) * | 2022-01-25 | 2022-03-01 | 北京芯海视界三维科技有限公司 | 发光器件和显示装置 |

| US11841508B2 (en) * | 2022-04-13 | 2023-12-12 | Meta Platforms Technologies, Llc | Micro-LED light extraction efficiency enhancement |

| JP7764832B2 (ja) * | 2022-10-19 | 2025-11-06 | 豊田合成株式会社 | 発光装置 |

| CN116404028B (zh) * | 2023-05-10 | 2024-04-05 | 诺视科技(苏州)有限公司 | 像素单元及其制作方法、微显示屏、像素级分立器件 |

| WO2025051681A1 (en) * | 2023-09-06 | 2025-03-13 | Ams-Osram International Gmbh | µLED COMPRISING A MULTILAYER THIN-FILM LIGHT OUTCOUPLING STRUCTURE |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002246647A (ja) | 2001-02-16 | 2002-08-30 | Stanley Electric Co Ltd | 波長変換型半導体素子 |

| JP2010539715A (ja) | 2007-09-21 | 2010-12-16 | オスラム オプト セミコンダクターズ ゲゼルシャフト ミット ベシュレンクテル ハフツング | 放射放出コンポーネント |

| JP2012510716A (ja) | 2008-12-02 | 2012-05-10 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | Led組立体 |

| JP2014110333A (ja) | 2012-12-03 | 2014-06-12 | Citizen Holdings Co Ltd | Led装置及びその製造方法 |

| JP2016174179A (ja) | 2010-06-07 | 2016-09-29 | コーニンクレッカ フィリップス エヌ ヴェKoninklijke Philips N.V. | 半導体発光デバイスのパッシベーション |

| JP2018050082A (ja) | 2017-12-28 | 2018-03-29 | 日亜化学工業株式会社 | 発光装置及び発光装置の製造方法 |

| JP2018527748A (ja) | 2015-08-03 | 2018-09-20 | ルミレッズ ホールディング ベーフェー | 反射性側面コーティングを伴う半導体発光デバイス |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0738153A (ja) * | 1993-07-20 | 1995-02-07 | Sharp Corp | 半導体発光素子並びに光ファイバモジュール装置および半導体発光素子ディスプレイ装置 |

| JPH11145519A (ja) * | 1997-09-02 | 1999-05-28 | Toshiba Corp | 半導体発光素子、半導体発光装置および画像表示装置 |

| DE19911717A1 (de) * | 1999-03-16 | 2000-09-28 | Osram Opto Semiconductors Gmbh | Monolithisches elektrolumineszierendes Bauelement und Verfahren zu dessen Herstellung |

| US7279718B2 (en) * | 2002-01-28 | 2007-10-09 | Philips Lumileds Lighting Company, Llc | LED including photonic crystal structure |

| AU2003252359A1 (en) * | 2002-08-01 | 2004-02-23 | Nichia Corporation | Semiconductor light-emitting device, method for manufacturing same and light-emitting apparatus using same |

| EP1887634A3 (de) * | 2006-08-11 | 2011-09-07 | OSRAM Opto Semiconductors GmbH | Strahlungsemittierendes Halbleiterbauelement |

| WO2010028146A2 (en) * | 2008-09-08 | 2010-03-11 | 3M Innovative Properties Company | Electrically pixelated luminescent device |

| WO2010056596A2 (en) * | 2008-11-13 | 2010-05-20 | 3M Innovative Properties Company | Electrically pixelated luminescent device incorporating optical elements |

| WO2010149027A1 (en) * | 2009-06-22 | 2010-12-29 | Industrial Technology Research Institute | Light-emitting unit array, method for fabricating the same and projection apparatus |

| JP5523354B2 (ja) * | 2010-03-31 | 2014-06-18 | パナソニック株式会社 | 表示パネル装置及び表示パネル装置の製造方法 |

| KR101178912B1 (ko) * | 2010-06-01 | 2012-09-03 | 삼성디스플레이 주식회사 | 유기 전계발광 표시장치 |

| WO2013124924A1 (ja) * | 2012-02-23 | 2013-08-29 | パナソニック株式会社 | 窒化物半導体発光チップ、窒化物半導体発光装置及び窒化物半導体チップの製造方法 |

| JP6149487B2 (ja) * | 2012-11-09 | 2017-06-21 | 日亜化学工業株式会社 | 発光装置の製造方法および発光装置 |

| DE102012112302A1 (de) * | 2012-12-14 | 2014-06-18 | Osram Opto Semiconductors Gmbh | Anzeigevorrichtung und Verfahren zur Herstellung einer Anzeigevorrichtung |

| US9153171B2 (en) * | 2012-12-17 | 2015-10-06 | LuxVue Technology Corporation | Smart pixel lighting and display microcontroller |

| KR102489836B1 (ko) * | 2015-06-30 | 2023-01-18 | 엘지디스플레이 주식회사 | 유기전계발광표시장치 |

| JP6612565B2 (ja) * | 2015-09-11 | 2019-11-27 | アルパッド株式会社 | ディスプレイパネル、表示装置およびディスプレイパネルの製造方法 |

| KR102472353B1 (ko) * | 2016-04-01 | 2022-11-30 | 쑤저우 레킨 세미컨덕터 컴퍼니 리미티드 | 발광소자, 어레이 기판, 패널, 및 이를 포함하는 표시장치 |

| DE112017006432T5 (de) * | 2016-12-21 | 2019-09-05 | Seoul Viosys Co., Ltd | Hochzuverlässige lumineszenzdiode |

| US20200251460A1 (en) * | 2017-08-25 | 2020-08-06 | Sharp Kabushiki Kaisha | Micro-led element, image display element, and production method |

| TWI643328B (zh) * | 2017-10-13 | 2018-12-01 | 英屬開曼群島商錼創科技股份有限公司 | 顯示裝置 |

| US11538852B2 (en) * | 2019-04-23 | 2022-12-27 | Osram Opto Semiconductors Gmbh | μ-LED, μ-LED device, display and method for the same |

-

2020

- 2020-03-30 US US17/595,298 patent/US20220223771A1/en active Pending

- 2020-03-30 DE DE112020002375.3T patent/DE112020002375A5/de active Pending

- 2020-03-30 JP JP2021568189A patent/JP7635155B2/ja active Active

- 2020-03-30 KR KR1020217037590A patent/KR20220007069A/ko not_active Ceased

- 2020-03-30 CN CN202080051214.5A patent/CN114127964A/zh active Pending

- 2020-03-30 WO PCT/EP2020/058997 patent/WO2020229043A2/de not_active Ceased

-

2025

- 2025-02-12 JP JP2025021121A patent/JP2025081418A/ja active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002246647A (ja) | 2001-02-16 | 2002-08-30 | Stanley Electric Co Ltd | 波長変換型半導体素子 |

| JP2010539715A (ja) | 2007-09-21 | 2010-12-16 | オスラム オプト セミコンダクターズ ゲゼルシャフト ミット ベシュレンクテル ハフツング | 放射放出コンポーネント |

| JP2012510716A (ja) | 2008-12-02 | 2012-05-10 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | Led組立体 |

| JP2016174179A (ja) | 2010-06-07 | 2016-09-29 | コーニンクレッカ フィリップス エヌ ヴェKoninklijke Philips N.V. | 半導体発光デバイスのパッシベーション |

| JP2014110333A (ja) | 2012-12-03 | 2014-06-12 | Citizen Holdings Co Ltd | Led装置及びその製造方法 |

| JP2018527748A (ja) | 2015-08-03 | 2018-09-20 | ルミレッズ ホールディング ベーフェー | 反射性側面コーティングを伴う半導体発光デバイス |

| JP2018050082A (ja) | 2017-12-28 | 2018-03-29 | 日亜化学工業株式会社 | 発光装置及び発光装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20220007069A (ko) | 2022-01-18 |

| WO2020229043A2 (de) | 2020-11-19 |

| DE112020002375A5 (de) | 2022-01-27 |

| CN114127964A (zh) | 2022-03-01 |

| US20220223771A1 (en) | 2022-07-14 |

| JP2022532641A (ja) | 2022-07-15 |

| WO2020229043A3 (de) | 2021-04-15 |

| JP2025081418A (ja) | 2025-05-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7635155B2 (ja) | 光電子構造素子、画素、ディスプレイ配置構造体およびそれに関する方法 | |

| US11908847B2 (en) | Image display element and method for manufacturing image display element | |

| US11289634B2 (en) | Image display element | |

| CN112242468B (zh) | 微型发光元件及图像显示元件 | |

| US10403608B2 (en) | Light-emitting diode (LED) device for realizing multi-colors | |

| KR102650950B1 (ko) | 발광 소자 및 그것을 갖는 표시 장치 | |

| US11133434B2 (en) | Image display device | |

| US11587973B2 (en) | Micro light-emitting diode display panel | |

| JP7105612B2 (ja) | 画像表示素子およびその形成方法 | |

| KR20190071274A (ko) | 발광소자 패키지 및 이를 이용한 디스플레이 장치 | |

| KR20190071152A (ko) | 발광소자 패키지 및 이를 이용한 디스플레이 장치 | |

| KR102658970B1 (ko) | 다이오드 어레이를 구비하는 광전자 장치 | |

| KR102256893B1 (ko) | 발광 모듈 및 상기 발광 모듈을 포함하는 디스플레이 장치 | |

| KR20080075368A (ko) | 질화물 반도체 발광소자 및 제조방법 | |

| US20240355965A1 (en) | Light emitting device and image display apparatus | |

| KR20230056050A (ko) | 모놀리식 나노컬럼 구조 | |

| KR101640360B1 (ko) | 광전 소자 및 그 제조 방법 | |

| US10998694B2 (en) | Laser diode | |

| JP7613127B2 (ja) | 発光装置、プロジェクター | |

| JP7460789B2 (ja) | 共振する空洞を有する発光ダイオード構造およびその製造方法 | |

| WO2023099709A1 (en) | Epitaxially grown converter layer, optoelectronic arrangement and method for producing the same | |

| CN120051072B (en) | LED display device and manufacturing method thereof | |

| KR102878763B1 (ko) | 표시 장치 및 이의 제조 방법 | |

| US20240030681A1 (en) | Light-emitting device, projector, display, and head-mounted display | |

| WO2025204186A1 (ja) | 発光装置および画像表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220113 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230330 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20240214 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240402 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20240702 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240828 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240924 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20241220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20250114 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20250212 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7635155 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |