JP7588937B2 - 電力増幅器 - Google Patents

電力増幅器 Download PDFInfo

- Publication number

- JP7588937B2 JP7588937B2 JP2020209599A JP2020209599A JP7588937B2 JP 7588937 B2 JP7588937 B2 JP 7588937B2 JP 2020209599 A JP2020209599 A JP 2020209599A JP 2020209599 A JP2020209599 A JP 2020209599A JP 7588937 B2 JP7588937 B2 JP 7588937B2

- Authority

- JP

- Japan

- Prior art keywords

- phase

- positive

- negative

- signal

- overcurrent detection

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000001514 detection method Methods 0.000 claims description 199

- 230000005236 sound signal Effects 0.000 claims description 4

- 238000010586 diagram Methods 0.000 description 18

- 101100433746 Arabidopsis thaliana ABCG29 gene Proteins 0.000 description 4

- 101100433754 Arabidopsis thaliana ABCG30 gene Proteins 0.000 description 4

- 102000012677 DET1 Human genes 0.000 description 4

- 101150113651 DET1 gene Proteins 0.000 description 4

- 101100054289 Oryza sativa subsp. japonica ABCG34 gene Proteins 0.000 description 4

- 101100054291 Oryza sativa subsp. japonica ABCG35 gene Proteins 0.000 description 4

- 101100107595 Oryza sativa subsp. japonica ABCG41 gene Proteins 0.000 description 4

- 101100107601 Oryza sativa subsp. japonica ABCG45 gene Proteins 0.000 description 4

- 101150088582 PDR1 gene Proteins 0.000 description 4

- 101150024488 PDR2 gene Proteins 0.000 description 4

- 101100321174 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) YRR1 gene Proteins 0.000 description 4

- 101100400877 Trichophyton rubrum (strain ATCC MYA-4607 / CBS 118892) MDR1 gene Proteins 0.000 description 4

- 238000002844 melting Methods 0.000 description 4

- 230000008018 melting Effects 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 230000001360 synchronised effect Effects 0.000 description 2

- 101100484492 Arabidopsis thaliana VHA-C gene Proteins 0.000 description 1

- 101150066284 DET2 gene Proteins 0.000 description 1

- 101000746134 Homo sapiens DNA endonuclease RBBP8 Proteins 0.000 description 1

- 101000969031 Homo sapiens Nuclear protein 1 Proteins 0.000 description 1

- 102100021133 Nuclear protein 1 Human genes 0.000 description 1

- 101100206695 Rattus norvegicus Thoc6 gene Proteins 0.000 description 1

- 102100029469 WD repeat and HMG-box DNA-binding protein 1 Human genes 0.000 description 1

- 101710097421 WD repeat and HMG-box DNA-binding protein 1 Proteins 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000010355 oscillation Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

Images

Landscapes

- Amplifiers (AREA)

Description

係る過電流検出回路は、例えば、特許文献1に開示されたようにパワートランジスタの電流をモニターする方法等が知られており、さらに、過電流検出回路の検出精度向上や電力損失の低減を図った構成が特許文献2等において開示されている。

この電力増幅器は、正相入力信号INPと逆相入力信号INNとが、それぞれ基本的に同一構成の増幅回路により増幅されて、BTL接続された負荷RLを駆動可能に構成されてなるものである。

すなわち、正相入力信号INPは、第1のドライブ回路PDR1を介してプッシュプル接続された2つのパワートランジスタQ1,Q2により増幅され、その正相増幅出力OUTPは負荷RLの一端に印加される構成となっている。

また、逆相入力信号INNは、第2のドライブ回路PDR2を介してプッシュプル接続された2つのパワートランジスタQ3,Q4により増幅され、その逆相増幅出力OUTNは負荷RLの他端に印加される構成となっている。

同様に、パワートランジスタQ3,Q4に流れる電流は、検出用トランジスタQd3,Qd4によりモニターされ、所定の第1の電流値を超えた場合に第3及び第4の検出回路DET3,DET4から過電流の検出信号が出力されるようになっている。

例えば、負荷抵抗値RL=4Ω、最大出力電力Poutmax=8Wの電力増幅器の場合、アプリケーションの最大電流は2Aと算出される。したがって、この場合、第1の電流値は2Aを超える適宜な値、例えば、2.5Aなどに設定される。

上述のようにして第1の電流値が決定された後、この電流値においてボンディングワイヤの溶断が生じないようにボンディングワイヤの本数が決定されることとなる。

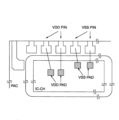

例えば、図7に模式的に示されたように、上述のような過電流に対処するために、半導体ICパッケージPACに搭載されたICチップIC-CHにおいては、電源電圧用ボンディングパッドVDD PADやグランド用ボンディングパッドVSS PADを増設して、半導体ICパッケージPACの外周近傍に設けられた電源電圧用接続ピンVDD PINやグランド用接続ピンVSS PINと、対応するボンディングパッドとを接続するボンディングワイヤを増設することで、ボンディングワイヤ一本あたりに流れる電流を減らす対策が採られる。

そのため、ボンディングワイヤの本数増加とボンディングパッド数の増加による製品原価の高騰を招くという問題がある。

正相入力信号を増幅する正相信号増幅部と、逆相入力信号を増幅する逆相信号増幅部とを有し、前記正相信号増幅部の出力と前記逆相信号増幅部の出力がBTL接続で負荷に供給可能に構成されると共に、前記正相信号増幅部における第1の電流値を超える過電流の発生と、前記逆相信号増幅部における第1の電流値を超える過電流の発生とを、それぞれ検出可能に構成された過電流検出部とを有してなる電力増幅器であって、

前記過電流検出部は、前記正相信号増幅部と前記逆相信号増幅部における同時天絡の発生、又は、前記正相信号増幅部と前記逆相信号増幅部における同時地絡の発生により、前記正相信号増幅部と前記逆相信号増幅部のそれぞれにおける第2の電流値を超える過電流の発生を検出可能に構成されると共に、前記第1の電流値を超える過電流、又は、前記第2の電流値を超える過電流のいずれかが検出された場合に、前記正相信号増幅部及び前記逆相信号増幅部に対して統合過電流検出信号を出力し、

前記正相信号増幅部及び前記逆相信号増幅部は、前記統合過電流検出信号が出力された際に、それぞれ動作停止可能に構成されてなり、

前記正相信号増幅部は、正相パワートランジスタドライブ回路と、正相第1及び第2のパワートランジスタと、正相第1及び第2のモニタトランジスタとを有し、PチャンネルMOSFETの前記正相第1のパワートランジスタと、NチャンネルMOSFETの前記正相第2のパワートランジスタは、ドレインが相互に接続され、前記正相第1のパワートランジスタのソースには電源電圧が印可可能とされ、前記正相第2のパワートランジスタのソースはグランドに接続され、

前記正相第1及び第2のパワートランジスタは、外部から正相入力信号が入力される前記正相パワートランジスタドライブ回路のドライブ信号が、前記正相第1及び第2のパワートランジスタの各々のゲートに入力されることで駆動可能とされ、

PチャンネルMOSFETの前記正相第1のモニタトランジスタとNチャンネルMOSFETの前記正相第2のモニタトランジスタは、ドレインが相互に接続されると共に、前記正相第1及び第2のパワートランジスタのドレイン相互の接続点及び前記負荷の一端が接続される正相出力端子に接続され、

前記正相第1のモニタトランジスタのソースは、正相第1の検出抵抗器を介して前記電源電圧が印加可能とされ、

前記正相第2のモニタトランジスタのソースは、正相第2の検出抵抗器を介してグランドに接続され、

前記逆相信号増幅部は、逆相パワートランジスタドライブ回路と、逆相第1及び第2のパワートランジスタと、逆相第1及び第2のモニタトランジスタとを有し、PチャンネルMOSFETの前記逆相第1のパワートランジスタと、NチャンネルMOSFETの前記逆相第2のパワートランジスタは、ドレインが相互に接続され、前記逆相第1のパワートランジスタのソースには前記電源電圧が印可可能とされ、前記逆相第2のパワートランジスタのソースはグランドに接続され、

前記逆相第1及び第2のパワートランジスタは、外部から逆相入力信号が入力される前記逆相パワートランジスタドライブ回路のドライブ信号が、前記逆相第1及び第2のパワートランジスタの各々のゲートに入力されることで駆動可能とされ、

PチャンネルMOSFETの前記逆相第1のモニタトランジスタとNチャンネルMOSFETの前記逆相第2のモニタトランジスタは、ドレインが相互に接続されると共に、前記逆相第1及び第2のパワートランジスタのドレイン相互の接続点及び前記負荷の他端が接続される逆相出力端子に接続され、

前記正相出力端子と前記逆相出力端子の間には、前記負荷が接続され、

前記逆相第1のモニタトランジスタのソースは、逆相第1の検出抵抗器を介して前記電源電圧が印加可能とされ、

前記逆相第2のモニタトランジスタのソースは、逆相第2の検出抵抗器を介してグランドに接続され、

前記過電流検出部は、正相第1基準第1及び第2の過電流検出回路と、逆相第1基準第1及び第2の過電流検出回路と、正相第2基準第1及び第2の過電流検出回路と、逆相第2基準第1及び第2の過電流検出回路とを有し、

前記正相第1のモニタトランジスタのソースと前記正相第1の検出抵抗器との接続点は、前記正相第1基準第1の過電流検出回路及び前記正相第2基準第1の過電流検出回路の入力段に接続され、

前記正相第2のモニタトランジスタのソースと前記正相第2の検出抵抗器との接続点は、前記正相第1基準第2の過電流検出回路及び前記正相第2基準第2の過電流検出回路の入力段に接続され、

前記逆相第1のモニタトランジスタのソースと前記逆相第1の検出抵抗器との接続点は、前記逆相第1基準第1の過電流検出回路及び前記逆相第2基準第1の過電流検出回路の入力段に接続され、

前記逆相第2のモニタトランジスタのソースと前記逆相第2の検出抵抗器との接続点は、前記逆相第1基準第2の過電流検出回路及び前記逆相第2基準第2の過電流検出回路の入力段に接続され、

前記正相出力端子と逆相出力端子における同時地絡の発生により、前記正相第1のモニタトランジスタにより検出された前記正相第1のパワートランジスタの電流が、前記正相第2基準第1の過電流検出回路によって前記第2の電流値を超える過電流と判定され、前記逆相第1のモニタトランジスタにより検出された前記逆相第1のパワートランジスタの電流が、前記逆相第2基準第1の過電流検出回路によって前記第2の電流値を超える過電流と判定された場合に、前記過電流検出部による前記正相信号増幅部及び前記逆相信号増幅部に対する前記統合過電流検出信号が出力され、

前記正相出力端子と逆相出力端子における同時天絡の発生により、前記正相第2のモニタトランジスタにより検出された前記正相第2のパワートランジスタの電流が、前記正相第2基準第2の過電流検出回路によって前記第2の電流値を超える過電流と判定され、前記逆相第2のモニタトランジスタにより検出された前記逆相第2のパワートランジスタの電流が、前記逆相第2基準第2の過電流検出回路によって前記第2の電流値を超える過電流と判定された場合に、前記過電流検出部による前記正相信号増幅部及び前記逆相信号増幅部に対する前記統合過電流検出信号が出力されるよう構成されてなるものである。

なお、以下に説明する部材、配置等は本発明を限定するものではなく、本発明の趣旨の範囲内で種々改変することができるものである。

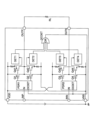

最初に、本発明の実施の形態における電力増幅器の第1の回路構成例について、図1を参照しつつ説明する。

この電力増幅器は、正相信号増幅部101と、逆相信号増幅部102と、過電流検出部103とに大別されて構成されたものとなっている。

正相信号増幅部101と逆相信号増幅部102の各々の増幅出力信号は、BTL接続により負荷(図1においては「RL」と表記)37に供給される構成となっている。

また、逆相信号増幅部102は、被増幅信号が逆相入力信号という点では、正相信号増幅部と異なるが、基本的な構成は正相信号増幅部101と同様である。

この正相第1及び第2のパワートランジスタ1,2は、電源端子95とグランド端子96との間にプッシュプル接続されて設けられている。

すなわち、正相第1及び第2のパワートランジスタ1,2は、ドレインが相互に接続されて、正相第1のパワートランジスタ1のソースは電源端子95に、正相第2のパワートランジスタ2のソースは、グランド端子96に、それぞれ接続されている。

なお、電源端子95とグランド端子96の間には、直流電源40が接続されている。

また、正相パワートランジスタドライブ回路51は、後述するように、過電流検出部103の統合過電流検出信号OCDETが論理値Highに相当するレベルとなると動作停止し、正相第1及び第2のパワートランジスタ1,2の動作を遮断できるようになっている。

正相第1及び第2のモニタトランジスタ5,6は、ドレインが相互に接続されると共に、正相第1及び第2のパワートランジスタ1,2のドレイン相互の接続点と正相出力端子93に接続されている。

この逆相第1及び第2のパワートランジスタ3,4は、電源端子95とグランド端子96との間にプッシュプル接続されて設けられている。

逆相パワートランジスタドライブ回路52は、逆相入力端子92を介して逆相入力信号が入力され、そのドライブ信号を逆相第1及び第2のパワートランジスタ3,4のゲートへ出力することで逆相第1及び第2のパワートランジスタ3,4を駆動されるようになっている。

本発明の実施の形態において、逆相第1のモニタトランジスタ7には、PチャンネルMOSFETが、逆相第2のモニタトランジスタ8には、NチャンネルMOSFETが、それぞれ用いられている。

また、逆相第1のモニタトランジスタ7のソースは、逆相第1の検出抵抗器(図1においては「R1HN」と表記)23を介して電源端子95に印加される電源電圧VDDが印加されるようになっている。また、逆相第1のモニタトランジスタ7のソースと逆相第1の検出抵抗器23との接続点は、逆相第1基準第1の過電流検出回路71及び逆相第2基準第1の過電流検出回路73の入力段に接続されている。

また、正相第2基準第1の過電流検出回路63の出力と、逆相第2基準第1の過電流検出回路73の出力は、第1のAND回路11に入力されて、その論理積出力が6入力論理和回路13に入力されるようになっている。

6入力論理和回路13は、6つの入力のいずれかが論理値Highとなった場合に、それを統合過電流検出信号OCDETとして出力する。

6入力論理和回路13の出力端子は、正相パワートランジスタドライブ回路51と逆相パワートランジスタドライブ回路52のそれぞれの統合過電流検出信号入力端子OCDETに接続されている。

まず、正相入力端子91に外部から入力された正相信号INPは、正相パワートランジスタドライブ回路51、正相第1及び第2のパワートランジスタ1,2により電力増幅され、正相出力端子93から正相出力信号OUTPとして出力される。

また、逆相入力端子92に外部から入力された逆相信号INNは、逆相パワートランジスタドライブ回路52、逆相第1及び第2のパワートランジスタ3,4により電力増幅され、逆相出力端子94から逆相出力信号OUTNとして出力され、正相出力端子93と逆相出力端子94の間に接続された負荷37はBTL駆動されることとなる。

また、正相第2基準第2の過電流検出回路64と逆相第2基準第2の過電流検出回路74の双方において第2の電流値を超える過電流が検出された場合、第2のAND回路12から論理値Highに相当するレベルの検出信号(以下説明の便宜上、「同時天絡過電流検出信号」と称する)が出力される。

なお、第2の電流値の具体的な値は、電力増幅器の具体的な仕様や、使用形態等を考慮して、個々に適切な値を選定することとなる。

図3には、3値パルス幅変調信号の生成に適する3値パルス幅変調回路の回路構成例が、図4には、3値パルス幅変調回路の動作を説明する波形図が、それぞれ示されており、以下、これらの図を参照しつつ3値パルス幅変調信号について説明する。

この3値パルス幅変調回路は、第1及び第2のコンパレータ(図3においては、それぞれ「COM1」、「COM2」と表記)41,42と、三角波発振器(図3においては「OSC」と表記)43を有して構成されている。

第1及び第2のコンパレータ41,42の各々の反転入力端子は、相互に接続されて三角波発振器43の出力段に接続されている。

三角波発振器43には、後述するようなクロック信号CLKが入力され、このクロック信号CLKに同期した三角波信号TWが生成、出力され、第1及び第2のコンパレータ41,42へ入力されるようになっている。

三角波発振器43から出力される三角波信号TW(図4(A)二点鎖線参照)は、アナログオーディオ信号である正相入力信号、逆相入力信号に比して繰り返し周波数が十分高く設定されたものとなっている(図4(B)参照)。すなわち、三角波発振器43に入力されるクロック信号CLK(図4(B)参照)の繰り返し周波数は、アナログオーディオ信号に対して高い周波数に設定されている。

正相アナログ入力信号INPと逆相アナログ入力信号INNが無信号時には、第1のパルス幅変調信号PWMPと第2のパルス幅変調信号PWMNの差分はゼロとなる。その結果、負荷37には、図4(E)に示されたようにハイレベル、ゼロ、マイナスハイレベルの3値パルス幅変調信号が与えられることとなる。

その一方で、3値パルス幅変調信号は、同時にハイレベル、同時にローレベルとなる場合があるため、同時天絡、同時地絡の発生を考慮する必要があるが、本発明の実施の形態における電力増幅器は、係る同時天絡、同時地絡による過電流に起因する回路素子の焼損等を確実に抑圧、防止可能であり、3値パルス幅変調信号を用いる場合に好適である。

無入力時における第1のパルス幅変調信号PWMP及び第2のパルス幅変調信号PWMNは、先に説明したようにデューティ50%であるため、電源電圧VDDの半分の電圧値をバイアスポイントとして動作することとなる。したがって、動作開始時に、出力LCフィルタにVDD/2のインパルスが入力し、LC共振による電流の減衰振動が発生する。

図2には、出力LCフィルタを設けることにより生ずる上述のような問題の解決に適する第2の回路構成例が示されており、以下、同図を参照しつつ、第2の回路構成例について説明する。

なお、図1に示された構成要素と同一の構成要素については、同一の符号を付して、その詳細な説明を省略し、以下、異なる点を中心に説明する。

この第2の回路構成例は、図1に示された第1の回路構成例に、インパルス信号起因の電流が第2の電流値を超えた場合に過電流検出信号の出力を回避するための論理回路(詳細は後述)を付加した構成を有するものである。

第1のAND回路11の出力端子は、第1のDフリップフロップ15のD入力端子に、第2のAND回路12の出力端子は、第2のDフリップフロップ16のD入力端子に、それぞれ接続されている。

第1及び第2のDフリップフロップ15,16のそれぞれの出力Qは、2入力論理和回路17に、それぞれ入力され、2入力論理和回路17の出力は、カウンタ回路18へ被計数信号RSTXとして入力されるようになっている。

さらに、第1のフィルタコイル33(第2のフィルタコイル34)と負荷37との接続点とグランドとの間には、第1のフィルタコンデンサ35(第2のフィルタコンデンサ36)が接続されている。

第1のパルス信号幅変調信号が正相入力端子91から入力されると、第1のパルス信号幅変調信号は、正相パワートランジスタドライブ回路51、正相第1及び第2のパワートランジスタ1,2により電力増幅され正相出力端子93に正相出力信号OUTPとして出力される(図5(A)参照)。

第2のパルス信号幅変調信号が逆相入力端子92から入力されると、第2パルス信号幅変調信号は、逆相パワートランジスタドライブ回路52、逆相第1及び第2のパワートランジスタ3,4により電力増幅され逆相出力端子94に逆相出力信号OUTNとして出力される(図5(B)参照)。

回路起動時(図5において時刻t1)には、正相出力信号OUTP、逆相出力信号OUTNの立ち上がりにより第1及び第2の出力LCフィルタ81,82に起因する突入電流の発生により共振状態となるが、回路の動作状態は時間の経過に伴い徐々に定常状態となってゆく。

その結果、第1のAND回路11により論理値Highに相当する信号が出力されると第1のDフリップフロップ15により、また、第2のAND回路12により論理値Highに相当する信号が出力されると第2のDフリップフロップ16により、それぞれ第1のパルス幅変調信号及び第2のパルス幅変調信号(図4(C)及び図4(D)参照)の1周期の間、論理値Highが保持される。

したがって、正相パワートランジスタドライブ回路51、逆相パワートランジスタドライブ回路52が、統合過電流検出信号OCDETによって動作停止されることはなく、回路起動後の回路動作を維持することができる。

正相出力電流IOUTPと逆相出力電流IOUTNは、第1、第2のパルス幅変調信号PWMP、PWMNに、それぞれ同期するような出力状態となる(図5(C)及び図5(D)時刻tn以降参照)。

そして、第1及び第2のDフリップフロップ15,16のいずれかの論理値Highに相当する信号は、カウンタ回路18において第1のカウント周期の間、計数されることでカウンタ回路18からは、第1のカウント周期終了時に論理値Highに相当する同時過電流検出信号が出力される。この同時過電流検出信号に対応して5入力論理和回路19から論理値Highに相当する過電流検出信号OCDETが出力されることとなる(図5(E)参照)。

また、回路が定常状態にある場合には、LCフィルタ起因のリプル電流が流れるため、第2の電流値は想定されるリプル電流よりも大きめに設定すると好適である。

2…正相第2のパワートランジスタ

3…逆相第1のパワートランジスタ

4…逆相第2のパワートランジスタ

5…正相第1のモニタトランジスタ

6…正相第2のモニタトランジスタ

7…逆相第1のモニタトランジスタ

8…逆相第2のモニタトランジスタ

51…正相パワートランジスタドライブ回路

52…逆相パワートランジスタドライブ回路

61…正相第1基準第1の過電流検出回路

62…正相第1基準第2の過電流検出回路

63…正相第2基準第1の過電流検出回路

62…正相第2基準第2の過電流検出回路

71…逆相第1基準第1の過電流検出回路

72…逆相第1基準第2の過電流検出回路

73…逆相第2基準第1の過電流検出回路

72…逆相第2基準第2の過電流検出回路

Claims (5)

- 正相入力信号を増幅する正相信号増幅部と、逆相入力信号を増幅する逆相信号増幅部とを有し、前記正相信号増幅部の出力と前記逆相信号増幅部の出力がBTL接続で負荷に供給可能に構成されると共に、前記正相信号増幅部における第1の電流値を超える過電流の発生と、前記逆相信号増幅部における第1の電流値を超える過電流の発生とを、それぞれ検出可能に構成された過電流検出部とを有してなる電力増幅器であって、

前記過電流検出部は、前記正相信号増幅部と前記逆相信号増幅部における同時天絡の発生、又は、前記正相信号増幅部と前記逆相信号増幅部における同時地絡の発生により、前記正相信号増幅部と前記逆相信号増幅部のそれぞれにおける第2の電流値を超える過電流の発生を検出可能に構成されると共に、前記第1の電流値を超える過電流、又は、前記第2の電流値を超える過電流のいずれかが検出された場合に、前記正相信号増幅部及び前記逆相信号増幅部に対して統合過電流検出信号を出力し、

前記正相信号増幅部及び前記逆相信号増幅部は、前記統合過電流検出信号が出力された際に、それぞれ動作停止可能に構成されてなり、

前記正相信号増幅部は、正相パワートランジスタドライブ回路と、正相第1及び第2のパワートランジスタと、正相第1及び第2のモニタトランジスタとを有し、PチャンネルMOSFETの前記正相第1のパワートランジスタと、NチャンネルMOSFETの前記正相第2のパワートランジスタは、ドレインが相互に接続され、前記正相第1のパワートランジスタのソースには電源電圧が印可可能とされ、前記正相第2のパワートランジスタのソースはグランドに接続され、

前記正相第1及び第2のパワートランジスタは、外部から正相入力信号が入力される前記正相パワートランジスタドライブ回路のドライブ信号が、前記正相第1及び第2のパワートランジスタの各々のゲートに入力されることで駆動可能とされ、

PチャンネルMOSFETの前記正相第1のモニタトランジスタとNチャンネルMOSFETの前記正相第2のモニタトランジスタは、ドレインが相互に接続されると共に、前記正相第1及び第2のパワートランジスタのドレイン相互の接続点及び前記負荷の一端が接続される正相出力端子に接続され、

前記正相第1のモニタトランジスタのソースは、正相第1の検出抵抗器を介して前記電源電圧が印加可能とされ、

前記正相第2のモニタトランジスタのソースは、正相第2の検出抵抗器を介してグランドに接続され、

前記逆相信号増幅部は、逆相パワートランジスタドライブ回路と、逆相第1及び第2のパワートランジスタと、逆相第1及び第2のモニタトランジスタとを有し、PチャンネルMOSFETの前記逆相第1のパワートランジスタと、NチャンネルMOSFETの前記逆相第2のパワートランジスタは、ドレインが相互に接続され、前記逆相第1のパワートランジスタのソースには前記電源電圧が印可可能とされ、前記逆相第2のパワートランジスタのソースはグランドに接続され、

前記逆相第1及び第2のパワートランジスタは、外部から逆相入力信号が入力される前記逆相パワートランジスタドライブ回路のドライブ信号が、前記逆相第1及び第2のパワートランジスタの各々のゲートに入力されることで駆動可能とされ、

PチャンネルMOSFETの前記逆相第1のモニタトランジスタとNチャンネルMOSFETの前記逆相第2のモニタトランジスタは、ドレインが相互に接続されると共に、前記逆相第1及び第2のパワートランジスタのドレイン相互の接続点及び前記負荷の他端が接続される逆相出力端子に接続され、

前記正相出力端子と前記逆相出力端子の間には、前記負荷が接続され、

前記逆相第1のモニタトランジスタのソースは、逆相第1の検出抵抗器を介して前記電源電圧が印加可能とされ、

前記逆相第2のモニタトランジスタのソースは、逆相第2の検出抵抗器を介してグランドに接続され、

前記過電流検出部は、正相第1基準第1及び第2の過電流検出回路と、逆相第1基準第1及び第2の過電流検出回路と、正相第2基準第1及び第2の過電流検出回路と、逆相第2基準第1及び第2の過電流検出回路とを有し、

前記正相第1のモニタトランジスタのソースと前記正相第1の検出抵抗器との接続点は、前記正相第1基準第1の過電流検出回路及び前記正相第2基準第1の過電流検出回路の入力段に接続され、

前記正相第2のモニタトランジスタのソースと前記正相第2の検出抵抗器との接続点は、前記正相第1基準第2の過電流検出回路及び前記正相第2基準第2の過電流検出回路の入力段に接続され、

前記逆相第1のモニタトランジスタのソースと前記逆相第1の検出抵抗器との接続点は、前記逆相第1基準第1の過電流検出回路及び前記逆相第2基準第1の過電流検出回路の入力段に接続され、

前記逆相第2のモニタトランジスタのソースと前記逆相第2の検出抵抗器との接続点は、前記逆相第1基準第2の過電流検出回路及び前記逆相第2基準第2の過電流検出回路の入力段に接続され、

前記正相出力端子と逆相出力端子における同時地絡の発生により、前記正相第1のモニタトランジスタにより検出された前記正相第1のパワートランジスタの電流が、前記正相第2基準第1の過電流検出回路によって前記第2の電流値を超える過電流と判定され、前記逆相第1のモニタトランジスタにより検出された前記逆相第1のパワートランジスタの電流が、前記逆相第2基準第1の過電流検出回路によって前記第2の電流値を超える過電流と判定された場合に、前記過電流検出部による前記正相信号増幅部及び前記逆相信号増幅部に対する前記統合過電流検出信号が出力され、

前記正相出力端子と逆相出力端子における同時天絡の発生により、前記正相第2のモニタトランジスタにより検出された前記正相第2のパワートランジスタの電流が、前記正相第2基準第2の過電流検出回路によって前記第2の電流値を超える過電流と判定され、前記逆相第2のモニタトランジスタにより検出された前記逆相第2のパワートランジスタの電流が、前記逆相第2基準第2の過電流検出回路によって前記第2の電流値を超える過電流と判定された場合に、前記過電流検出部による前記正相信号増幅部及び前記逆相信号増幅部に対する前記統合過電流検出信号が出力されるよう構成されてなることを特徴とする電力増幅器。 - 前記第2の電流値は、前記第1の電流値よりも小さいことを特徴とする請求項1記載の電力増幅器。

- 前記正相入力信号及び前記逆相入力信号がアナログオーディオ信号である場合に、それぞれ、パルス幅変調を施して前記アナログオーディオ信号の信号レベルに応じてハイレベルとローレベルのパルス信号に変換し、前記パルス幅変調が施された前記正相入力信号を第1のパルス幅変調信号として前記正相信号増幅部へ入力すると共に、前記パルス幅変調が施された前記逆相入力信号を第2のパルス幅変調信号として、前記逆相信号増幅部へ入力し、前記負荷において前記第1のパルス幅変調信号と前記第2のパルス幅変調信号の差分に応じたハイレベル、ゼロ、マイナスハイレベルの3値パルス幅変調信号の生成を可能とたことを特徴とする請求項2記載の電力増幅器。

- 前記正相信号増幅部と前記負荷との間に第1のLCフィルタが、前記逆相信号増幅部と前記負荷との間に第2のLCフィルタが、それぞれ設けられ、

前記過電流検出部は、前記正相信号増幅部と前記逆相信号増幅部における同時天絡の発生により第2の電流値を超える過電流の発生が検出された際に、論理値Highに相当する同時天絡過電流検出信号を生成すると共に、当該同時天絡過電流検出信号を前記第1のパルス幅変調信号及び第2のパルス幅変調信号の1周期分保持する第1のDフリップフロップが設けられる一方、

前記正相信号増幅部と前記逆相信号増幅部における同時地絡の発生により第2の電流値を超える過電流の発生が検出された際に、論理値Highに相当する同時地絡過電流検出信号を生成すると共に、当該同時地絡過電流検出信号を前記パルス幅変調信号の1周期分保持する第2のDフリップフロップが設けられ、

前記第1又は第2のDフリップフロップからの論理値Highに相当する出力信号を第1のカウント周期の間、計数後に論理値Highに相当する同時過電流検出信号として出力するカウンタ回路が設けられ、前記カウンタ回路が前記同時過電流検出信号を出力した場合に、前記統合過電流検出信号を出力可能に構成されてなることを特徴とする請求項3記載の電力増幅器。 - 前記第1のカウント周期は、前記LCフィルタの共振周期よりも大であることを特徴とする請求項4記載の電力増幅器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2020209599A JP7588937B2 (ja) | 2020-12-17 | 2020-12-17 | 電力増幅器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2020209599A JP7588937B2 (ja) | 2020-12-17 | 2020-12-17 | 電力増幅器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022096475A JP2022096475A (ja) | 2022-06-29 |

| JP7588937B2 true JP7588937B2 (ja) | 2024-11-25 |

Family

ID=82163694

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020209599A Active JP7588937B2 (ja) | 2020-12-17 | 2020-12-17 | 電力増幅器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7588937B2 (ja) |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002171140A (ja) | 2000-12-01 | 2002-06-14 | Mitsubishi Electric Corp | オーディオ信号増幅出力回路 |

| JP2007325236A (ja) | 2006-06-05 | 2007-12-13 | Yamaha Corp | D級増幅器およびその過電流保護方法 |

| JP2012235403A (ja) | 2011-05-09 | 2012-11-29 | New Japan Radio Co Ltd | 容量性スピーカ駆動回路 |

| JP2020065120A (ja) | 2018-10-15 | 2020-04-23 | 新日本無線株式会社 | D級増幅回路 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2565818B2 (ja) * | 1992-02-19 | 1996-12-18 | ローム株式会社 | Btl増幅装置の保護回路およびオーディオ装置 |

-

2020

- 2020-12-17 JP JP2020209599A patent/JP7588937B2/ja active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002171140A (ja) | 2000-12-01 | 2002-06-14 | Mitsubishi Electric Corp | オーディオ信号増幅出力回路 |

| JP2007325236A (ja) | 2006-06-05 | 2007-12-13 | Yamaha Corp | D級増幅器およびその過電流保護方法 |

| JP2012235403A (ja) | 2011-05-09 | 2012-11-29 | New Japan Radio Co Ltd | 容量性スピーカ駆動回路 |

| JP2020065120A (ja) | 2018-10-15 | 2020-04-23 | 新日本無線株式会社 | D級増幅回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2022096475A (ja) | 2022-06-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8284953B2 (en) | Circuit and method of reducing pop-up noise in a digital amplifier | |

| KR100924734B1 (ko) | 동기 정류형 스위칭 레귤레이터 | |

| US8134400B2 (en) | Semiconductor circuit | |

| US10367459B2 (en) | Class-D amplifier circuit | |

| US7940138B2 (en) | Electrostatic discharge protection oscillation circuit in LSI | |

| US9160290B2 (en) | Class D amplifier and control method | |

| JP5160320B2 (ja) | スイッチング駆動回路 | |

| JPWO2004010575A1 (ja) | パワーアンプ装置 | |

| CN117394844A (zh) | 电平移位电路、驱动电路和半桥电路 | |

| JP2007082036A (ja) | 半導体集積回路装置、電源装置、電気機器 | |

| US7982522B2 (en) | Semiconductor integrated circuit for realizing an amplifier having ringing reduction circuitry | |

| JP7588937B2 (ja) | 電力増幅器 | |

| US7564275B2 (en) | Switching circuit and a method of driving a load | |

| JP5094431B2 (ja) | 電力増幅回路 | |

| WO2025148379A1 (zh) | 一种断线保护电路及传感器 | |

| US8525559B2 (en) | Non-overlap circuit | |

| JP4835665B2 (ja) | リンギング低減回路および該リンギング低減回路を備えた半導体集積回路 | |

| JP2004056254A (ja) | パワーアンプ装置 | |

| JP7718823B2 (ja) | D級増幅回路 | |

| JP4222389B2 (ja) | リンギング低減回路および該リンギング低減回路を備えた半導体集積回路 | |

| CN222147149U (zh) | 一种逆变输出保护电路 | |

| US7388431B2 (en) | Switching amplifier and control method thereof | |

| JP2024118719A (ja) | D級増幅回路 | |

| JP3951917B2 (ja) | パルス幅変調増幅器 | |

| CN113302570B (zh) | 一种接口电路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20231110 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20240725 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240730 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20240925 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20241017 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20241112 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20241112 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7588937 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |