JP7555829B2 - 平坦化装置、平坦化方法及び物品の製造方法 - Google Patents

平坦化装置、平坦化方法及び物品の製造方法 Download PDFInfo

- Publication number

- JP7555829B2 JP7555829B2 JP2021001035A JP2021001035A JP7555829B2 JP 7555829 B2 JP7555829 B2 JP 7555829B2 JP 2021001035 A JP2021001035 A JP 2021001035A JP 2021001035 A JP2021001035 A JP 2021001035A JP 7555829 B2 JP7555829 B2 JP 7555829B2

- Authority

- JP

- Japan

- Prior art keywords

- superstrate

- substrate

- chuck

- peripheral portion

- edge

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67092—Apparatus for mechanical treatment

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/0002—Lithographic processes using patterning methods other than those involving the exposure to radiation, e.g. by stamping

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/7684—Smoothing; Planarisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28123—Lithography-related aspects, e.g. sub-lithography lengths; Isolation-related aspects, e.g. to solve problems arising at the crossing with the side of the device isolation; Planarisation aspects

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/31058—After-treatment of organic layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/32115—Planarisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67242—Apparatus for monitoring, sorting or marking

- H01L21/67253—Process monitoring, e.g. flow or thickness monitoring

Landscapes

- Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

- Container, Conveyance, Adherence, Positioning, Of Wafer (AREA)

- Two-Way Televisions, Distribution Of Moving Picture Or The Like (AREA)

- Micromachines (AREA)

- Shaping Of Tube Ends By Bending Or Straightening (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Mechanical Treatment Of Semiconductor (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US16/779,205 | 2020-01-31 | ||

| US16/779,205 US11562924B2 (en) | 2020-01-31 | 2020-01-31 | Planarization apparatus, planarization process, and method of manufacturing an article |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2021125680A JP2021125680A (ja) | 2021-08-30 |

| JP2021125680A5 JP2021125680A5 (enExample) | 2023-09-25 |

| JP7555829B2 true JP7555829B2 (ja) | 2024-09-25 |

Family

ID=77062134

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021001035A Active JP7555829B2 (ja) | 2020-01-31 | 2021-01-06 | 平坦化装置、平坦化方法及び物品の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US11562924B2 (enExample) |

| JP (1) | JP7555829B2 (enExample) |

| KR (1) | KR102831923B1 (enExample) |

| TW (1) | TWI817064B (enExample) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12065573B2 (en) * | 2020-07-31 | 2024-08-20 | Canon Kabushiki Kaisha | Photocurable composition |

| US11908711B2 (en) * | 2020-09-30 | 2024-02-20 | Canon Kabushiki Kaisha | Planarization process, planarization system and method of manufacturing an article |

| US12282251B2 (en) | 2021-09-24 | 2025-04-22 | Canon Kabushiki Kaisha | Method of shaping a surface, shaping system, and method of manufacturing an article |

| US12195382B2 (en) * | 2021-12-01 | 2025-01-14 | Canon Kabushiki Kaisha | Superstrate and a method of using the same |

| US20250269438A1 (en) * | 2024-02-27 | 2025-08-28 | Canon Kabushiki Kaisha | Chuck assembly, planarization process, apparatus and method of manufacturing an article |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020009994A (ja) | 2018-07-12 | 2020-01-16 | キヤノン株式会社 | 平坦化装置、平坦化方法及び物品の製造方法 |

Family Cites Families (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5989103A (en) * | 1997-09-19 | 1999-11-23 | Applied Materials, Inc. | Magnetic carrier head for chemical mechanical polishing |

| US6873087B1 (en) * | 1999-10-29 | 2005-03-29 | Board Of Regents, The University Of Texas System | High precision orientation alignment and gap control stages for imprint lithography processes |

| US6964793B2 (en) * | 2002-05-16 | 2005-11-15 | Board Of Regents, The University Of Texas System | Method for fabricating nanoscale patterns in light curable compositions using an electric field |

| US20040206621A1 (en) * | 2002-06-11 | 2004-10-21 | Hongwen Li | Integrated equipment set for forming a low K dielectric interconnect on a substrate |

| US7077992B2 (en) * | 2002-07-11 | 2006-07-18 | Molecular Imprints, Inc. | Step and repeat imprint lithography processes |

| US6900881B2 (en) * | 2002-07-11 | 2005-05-31 | Molecular Imprints, Inc. | Step and repeat imprint lithography systems |

| US7019819B2 (en) * | 2002-11-13 | 2006-03-28 | Molecular Imprints, Inc. | Chucking system for modulating shapes of substrates |

| US6908861B2 (en) * | 2002-07-11 | 2005-06-21 | Molecular Imprints, Inc. | Method for imprint lithography using an electric field |

| US20050098534A1 (en) * | 2003-11-12 | 2005-05-12 | Molecular Imprints, Inc. | Formation of conductive templates employing indium tin oxide |

| ATE477515T1 (de) * | 2004-06-03 | 2010-08-15 | Molecular Imprints Inc | Fluidausgabe und tropfenausgabe nach bedarf für die herstellung im nanobereich |

| US8167393B2 (en) * | 2005-01-14 | 2012-05-01 | Cabot Corporation | Printable electronic features on non-uniform substrate and processes for making same |

| US7878791B2 (en) * | 2005-11-04 | 2011-02-01 | Asml Netherlands B.V. | Imprint lithography |

| US7622935B2 (en) * | 2005-12-02 | 2009-11-24 | Formfactor, Inc. | Probe card assembly with a mechanically decoupled wiring substrate |

| US8850980B2 (en) * | 2006-04-03 | 2014-10-07 | Canon Nanotechnologies, Inc. | Tessellated patterns in imprint lithography |

| US8012395B2 (en) * | 2006-04-18 | 2011-09-06 | Molecular Imprints, Inc. | Template having alignment marks formed of contrast material |

| US7718545B1 (en) * | 2006-10-30 | 2010-05-18 | Hewlett-Packard Development Company, L.P. | Fabrication process |

| JP5182470B2 (ja) | 2007-07-17 | 2013-04-17 | 大日本印刷株式会社 | インプリントモールド |

| US8187515B2 (en) * | 2008-04-01 | 2012-05-29 | Molecular Imprints, Inc. | Large area roll-to-roll imprint lithography |

| US8394282B2 (en) * | 2008-06-09 | 2013-03-12 | Board Of Regents, The University Of Texas System | Adaptive nanotopography sculpting |

| JP5759195B2 (ja) * | 2011-02-07 | 2015-08-05 | キヤノン株式会社 | 型、インプリント方法及び物品製造方法 |

| US20140028686A1 (en) * | 2012-07-27 | 2014-01-30 | Qualcomm Mems Technologies, Inc. | Display system with thin film encapsulated inverted imod |

| JP2014049658A (ja) * | 2012-08-31 | 2014-03-17 | Toshiba Corp | パターン形成方法及びテンプレート |

| JP5823937B2 (ja) | 2012-09-07 | 2015-11-25 | 株式会社東芝 | モールド、モールド用ブランク基板及びモールドの製造方法 |

| JP5851442B2 (ja) * | 2013-03-25 | 2016-02-03 | 株式会社東芝 | モールド及びその製造方法 |

| US9718096B2 (en) * | 2013-08-19 | 2017-08-01 | Board Of Regents, The University Of Texas System | Programmable deposition of thin films of a user-defined profile with nanometer scale accuracy |

| KR102431971B1 (ko) * | 2014-04-18 | 2022-08-16 | 가부시키가이샤 에바라 세이사꾸쇼 | 기판 처리 장치 및 기판 처리 방법 |

| US10409156B2 (en) * | 2015-02-13 | 2019-09-10 | Canon Kabushiki Kaisha | Mold, imprint apparatus, and method of manufacturing article |

| JP2016157785A (ja) * | 2015-02-24 | 2016-09-01 | 株式会社東芝 | テンプレート形成方法、テンプレートおよびテンプレート基材 |

| US9987653B2 (en) * | 2015-10-15 | 2018-06-05 | Board Of Regents, The University Of Texas System | Versatile process for precision nanoscale manufacturing |

| JP6597186B2 (ja) | 2015-10-30 | 2019-10-30 | 大日本印刷株式会社 | インプリント用のモールド、モールド製造用の基板およびインプリント方法 |

| JP7374584B2 (ja) * | 2016-05-20 | 2023-11-07 | ボード オブ リージェンツ,ザ ユニバーシティ オブ テキサス システム | インクジェット座標系に対する基板座標系の精密アライメント |

| US11131922B2 (en) * | 2016-06-06 | 2021-09-28 | Canon Kabushiki Kaisha | Imprint lithography template, system, and method of imprinting |

| US11762284B2 (en) * | 2016-08-03 | 2023-09-19 | Board Of Regents, The University Of Texas System | Wafer-scale programmable films for semiconductor planarization and for imprint lithography |

| US10580659B2 (en) * | 2017-09-14 | 2020-03-03 | Canon Kabushiki Kaisha | Planarization process and apparatus |

| US10606171B2 (en) * | 2018-02-14 | 2020-03-31 | Canon Kabushiki Kaisha | Superstrate and a method of using the same |

| US11198235B2 (en) * | 2018-08-09 | 2021-12-14 | Canon Kabushiki Kaisha | Flexible mask modulation for controlling atmosphere between mask and substrate and methods of using the same |

| JP2020043160A (ja) * | 2018-09-07 | 2020-03-19 | キオクシア株式会社 | インプリント装置、インプリント方法、及び半導体装置の製造方法 |

| US11018018B2 (en) * | 2018-12-05 | 2021-05-25 | Canon Kabushiki Kaisha | Superstrate and methods of using the same |

| US10754078B2 (en) * | 2018-12-20 | 2020-08-25 | Canon Kabushiki Kaisha | Light source, a shaping system using the light source and an article manufacturing method |

| US10892167B2 (en) * | 2019-03-05 | 2021-01-12 | Canon Kabushiki Kaisha | Gas permeable superstrate and methods of using the same |

| US11664220B2 (en) * | 2019-10-08 | 2023-05-30 | Canon Kabushiki Kaisha | Edge exclusion apparatus and methods of using the same |

| US11776840B2 (en) * | 2019-10-29 | 2023-10-03 | Canon Kabushiki Kaisha | Superstrate chuck, method of use, and method of manufacturing an article |

| US11215921B2 (en) * | 2019-10-31 | 2022-01-04 | Canon Kabushiki Kaisha | Residual layer thickness compensation in nano-fabrication by modified drop pattern |

| US11550216B2 (en) * | 2019-11-25 | 2023-01-10 | Canon Kabushiki Kaisha | Systems and methods for curing a shaped film |

| US11107678B2 (en) * | 2019-11-26 | 2021-08-31 | Canon Kabushiki Kaisha | Wafer process, apparatus and method of manufacturing an article |

| JP7346268B2 (ja) * | 2019-12-05 | 2023-09-19 | キヤノン株式会社 | インプリント用のテンプレート、テンプレートを用いたインプリント方法 |

| US11567401B2 (en) * | 2019-12-20 | 2023-01-31 | Canon Kabushiki Kaisha | Nanofabrication method with correction of distortion within an imprint system |

| US11656546B2 (en) * | 2020-02-27 | 2023-05-23 | Canon Kabushiki Kaisha | Exposure apparatus for uniform light intensity and methods of using the same |

| JP2021144985A (ja) * | 2020-03-10 | 2021-09-24 | キオクシア株式会社 | テンプレート、テンプレートの製造方法および半導体装置の製造方法 |

| US12136564B2 (en) * | 2020-03-30 | 2024-11-05 | Canon Kabushiki Kaisha | Superstrate and method of making it |

| US11443940B2 (en) * | 2020-06-24 | 2022-09-13 | Canon Kabushiki Kaisha | Apparatus for uniform light intensity and methods of using the same |

-

2020

- 2020-01-31 US US16/779,205 patent/US11562924B2/en active Active

- 2020-11-30 TW TW109141980A patent/TWI817064B/zh active

-

2021

- 2021-01-06 JP JP2021001035A patent/JP7555829B2/ja active Active

- 2021-01-19 KR KR1020210007179A patent/KR102831923B1/ko active Active

-

2022

- 2022-11-10 US US18/054,487 patent/US12283522B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2020009994A (ja) | 2018-07-12 | 2020-01-16 | キヤノン株式会社 | 平坦化装置、平坦化方法及び物品の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW202143330A (zh) | 2021-11-16 |

| TWI817064B (zh) | 2023-10-01 |

| KR20210098334A (ko) | 2021-08-10 |

| US20230061361A1 (en) | 2023-03-02 |

| US12283522B2 (en) | 2025-04-22 |

| KR102831923B1 (ko) | 2025-07-10 |

| US11562924B2 (en) | 2023-01-24 |

| US20210242073A1 (en) | 2021-08-05 |

| JP2021125680A (ja) | 2021-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7555829B2 (ja) | 平坦化装置、平坦化方法及び物品の製造方法 | |

| US11776840B2 (en) | Superstrate chuck, method of use, and method of manufacturing an article | |

| JP7495949B2 (ja) | 平坦化方法、物品を製造する装置および方法 | |

| JP7481937B2 (ja) | 平坦化方法、平坦化装置及び物品製造方法 | |

| US11590687B2 (en) | Systems and methods for reducing pressure while shaping a film | |

| JP7713064B2 (ja) | 方法、平坦化システム、および物品の製造方法 | |

| JP7598359B2 (ja) | ウェハプロセス、物品を製造する装置および方法 | |

| US11443940B2 (en) | Apparatus for uniform light intensity and methods of using the same | |

| JP7071484B2 (ja) | インプリントシステム内のディストーションの補正を伴うナノ製作方法 | |

| US11550216B2 (en) | Systems and methods for curing a shaped film | |

| JP2023048109A (ja) | テンプレートの製造方法 | |

| US11664220B2 (en) | Edge exclusion apparatus and methods of using the same | |

| JP6951483B2 (ja) | 質量速度変動フィーチャを有するテンプレート、テンプレートを使用するナノインプリントリソグラフィ装置、およびテンプレートを使用する方法 | |

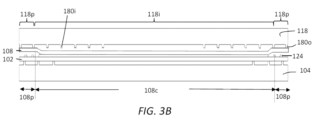

| US11587795B2 (en) | Planarization apparatus including superstrate chuck with bendable periphery | |

| US20210187795A1 (en) | Template apparatus and methods of using the same | |

| TWI885280B (zh) | 使表面成形的方法、成形系統、及製造物品的方法 | |

| US12085852B2 (en) | Template, method of forming a template, apparatus and method of manufacturing an article | |

| US11972976B2 (en) | Planarization system, planarization process, and method of manufacturing an article | |

| US20250180985A1 (en) | Method of Using and Fabricating a Nanoimprint Template with a Mesa Sidewall Coating |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230914 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230914 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20240515 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240520 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240719 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240813 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240911 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7555829 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |