JP7320552B2 - 半導体デバイス及び半導体デバイスの製造方法 - Google Patents

半導体デバイス及び半導体デバイスの製造方法 Download PDFInfo

- Publication number

- JP7320552B2 JP7320552B2 JP2021068262A JP2021068262A JP7320552B2 JP 7320552 B2 JP7320552 B2 JP 7320552B2 JP 2021068262 A JP2021068262 A JP 2021068262A JP 2021068262 A JP2021068262 A JP 2021068262A JP 7320552 B2 JP7320552 B2 JP 7320552B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- insulating layer

- semiconductor device

- gate insulating

- source region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 200

- 238000004519 manufacturing process Methods 0.000 title claims description 43

- 238000000034 method Methods 0.000 title claims description 42

- 239000000758 substrate Substances 0.000 claims description 122

- 230000005669 field effect Effects 0.000 claims description 45

- 238000005468 ion implantation Methods 0.000 description 83

- 239000002019 doping agent Substances 0.000 description 79

- 150000002500 ions Chemical class 0.000 description 32

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 20

- 229910052796 boron Inorganic materials 0.000 description 20

- 238000002513 implantation Methods 0.000 description 19

- 230000008569 process Effects 0.000 description 16

- 108091006146 Channels Proteins 0.000 description 14

- 238000000137 annealing Methods 0.000 description 14

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 13

- 229910052698 phosphorus Inorganic materials 0.000 description 13

- 239000011574 phosphorus Substances 0.000 description 13

- 229910052785 arsenic Inorganic materials 0.000 description 12

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 12

- 238000010586 diagram Methods 0.000 description 12

- 238000010438 heat treatment Methods 0.000 description 12

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 238000001994 activation Methods 0.000 description 9

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 9

- OKZIUSOJQLYFSE-UHFFFAOYSA-N difluoroboron Chemical compound F[B]F OKZIUSOJQLYFSE-UHFFFAOYSA-N 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- 229910052760 oxygen Inorganic materials 0.000 description 9

- 230000005684 electric field Effects 0.000 description 8

- 239000007789 gas Substances 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 230000008859 change Effects 0.000 description 7

- 238000002955 isolation Methods 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 238000004088 simulation Methods 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- 229910044991 metal oxide Inorganic materials 0.000 description 6

- 150000004706 metal oxides Chemical class 0.000 description 6

- 230000003647 oxidation Effects 0.000 description 6

- 238000007254 oxidation reaction Methods 0.000 description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 6

- 238000005530 etching Methods 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 229920005591 polysilicon Polymers 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 4

- 239000012212 insulator Substances 0.000 description 4

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 108010075750 P-Type Calcium Channels Proteins 0.000 description 3

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229920002120 photoresistant polymer Polymers 0.000 description 3

- 108090000699 N-Type Calcium Channels Proteins 0.000 description 2

- 102000004129 N-Type Calcium Channels Human genes 0.000 description 2

- INQLNSVYIFCUML-QZTLEVGFSA-N [[(2r,3s,4r,5r)-5-(6-aminopurin-9-yl)-3,4-dihydroxyoxolan-2-yl]methoxy-hydroxyphosphoryl] [(2r,3s,4r,5r)-5-(4-carbamoyl-1,3-thiazol-2-yl)-3,4-dihydroxyoxolan-2-yl]methyl hydrogen phosphate Chemical compound NC(=O)C1=CSC([C@H]2[C@@H]([C@H](O)[C@@H](COP(O)(=O)OP(O)(=O)OC[C@@H]3[C@H]([C@@H](O)[C@@H](O3)N3C4=NC=NC(N)=C4N=C3)O)O2)O)=N1 INQLNSVYIFCUML-QZTLEVGFSA-N 0.000 description 2

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 229910020286 SiOxNy Inorganic materials 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 229910052681 coesite Inorganic materials 0.000 description 1

- 229910052906 cristobalite Inorganic materials 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000001259 photo etching Methods 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 229910052682 stishovite Inorganic materials 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052905 tridymite Inorganic materials 0.000 description 1

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

図1は、本発明の実施の形態における半導体デバイス100に含まれる非対称高耐圧電界効果トランジスタ(HVMOS:High Voltage MOS)の基本構成の断面模式図を示す。図2は、HVMOSの基本構成の平面模式図を示す。HVMOSは、例えば、動作電圧が25V以上40V以下であることが好適である。HVMOSは、例えば、ディスプレイドライバに用いられる。図3は、HVMOSの各部の寸法を示す。

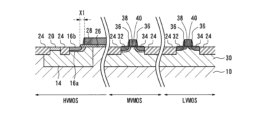

図5及び図6は、半導体デバイス100の製造方法を示す。図5及び図6は半導体デバイス100の製造方法を示す断面模式図であり、半導体デバイス100を構成する各部を強調して示しており、各部の平面方向の寸法及び厚さ方向の寸法は実際の比を示していない場合がある。

図7は、半導体デバイス100の変形例における半導体デバイス102の構成の断面模式図を示す。半導体デバイス102も、非対称構造のHVMOS、対象構造のMVMOS及びLVMOSを含んで構成される。

図8及び図9は、半導体デバイス102の製造方法を示す。図8及び図9は半導体デバイス102の製造方法を示す断面模式図であり、半導体デバイス102を構成する各部を強調して示しており、各部の平面方向の寸法及び厚さ方向の寸法は実際の比を示していない場合がある。

図10及び図11は、従来の非対称HVMOSの構造及び本実施の形態における半導体デバイス100の構造とした場合のソース領域近傍のドーパントの2次元濃度プロファイルをTCADシミュレーションした結果を示す。当該シミュレーションは、LVMOSのゲート長が100nm以下となり、LVMOSのソース領域32及びドレイン領域34のイオン注入エネルギーが小さくされた場合について想定したものである。図10(a)は、従来の非対称HVMOSの構造においてゲート絶縁層26の厚さを77nmとした場合のドーパントの2次元濃度プロファイルを示す。また、図10(b)は、本実施の形態における半導体デバイス100の構造においてゲート絶縁層26の厚さを77nmとした場合の2次元濃度プロファイルを示す。図11(a)は、従来の非対称HVMOSの構造においてゲート絶縁層26の厚さを87nmとした場合のドーパントの2次元濃度プロファイルを示す。また、図11(b)は、本実施の形態における半導体デバイス100の構造においてゲート絶縁層26の厚さを87nmとした場合の2次元濃度プロファイルを示す。

Claims (15)

- 半導体デバイスであって、

第1導電型の半導体の基板と、

前記基板内において前記第1導電型と反対の第2導電型であるソース領域及びドレイン領域と、

前記基板上に形成され、厚さが60nm以上であるゲート絶縁層と、

前記ゲート絶縁層上に形成されたゲート電極と、

前記ゲート絶縁層下に設けられたチャネル領域と、

前記ドレイン領域と前記チャネル領域との間に絶縁領域と、

を備え、

前記ドレイン領域は前記ソース領域より前記ゲート電極から離れた位置に配置され、前記ゲート電極に対して前記ソース領域と前記ドレイン領域が非対称とされている非対称電界効果トランジスタであり、

前記ゲート絶縁層は、前記ソース領域側において前記ゲート電極よりもマージン距離だけ拡げられた拡張絶縁領域を有し、

前記ソース領域から前記ゲート電極の間には前記拡張絶縁領域以外の絶縁領域を有さず、

前記ソース領域から前記ゲート絶縁層の前記拡張絶縁領域下を介して前記ゲート電極下の前記基板内の領域まで延設された前記第2導電型の拡張ソース領域を有し、

前記ソース領域は、前記拡張ソース領域内に形成されていることを特徴とする半導体デバイス。 - 請求項1に記載の半導体デバイスであって、

前記基板内において前記第2導電型であるドリフト領域が形成され、

前記ドレイン領域は、前記ドリフト領域内に配置され、

前記拡張ソース領域は、前記基板の表面から前記ドリフト領域よりも浅いことを特徴とする半導体デバイス。 - 請求項1又は2に記載の半導体デバイスであって、

前記ゲート絶縁層と前記ゲート電極が重なり合った領域から前記ドレイン領域の前記ゲート電極側の端部又はその近傍に亘って前記基板内に形成された絶縁領域を有することを特徴とする半導体デバイス。 - 請求項1~3のいずれか1項に記載の半導体デバイスであって、

前記ゲート絶縁層の厚さは、100nm以下であることを特徴とする半導体デバイス。 - 請求項1~4のいずれか1項に記載の半導体デバイスであって、

前記拡張ソース領域は、前記基板内に形成された前記第1導電型のウェル領域内に形成されていることを特徴とする半導体デバイス。 - 請求項1~5のいずれか1項に記載の半導体デバイスであって、

前記非対称電界効果トランジスタの動作電圧は25V以上40V以下であることを特徴とする半導体デバイス。 - 請求項1~6のいずれか1項に記載の半導体デバイスであって、

前記基板を共通として、前記非対称電界効果トランジスタの前記ゲート絶縁層の厚さより薄い第2のゲート絶縁層を有する電界効果トランジスタであって、当該電界効果トランジスタを構成する前記第2のゲート絶縁層に対して第2のソース領域及び第2のドレイン領域が対称となるように配置された対称電界効果トランジスタを含むことを特徴とする半導体デバイス。 - 請求項7に記載の半導体デバイスであって、

前記対称電界効果トランジスタは、ゲート長が100nm以下であることを特徴とする半導体デバイス。 - 請求項7に記載の半導体デバイスであって、

前記対称電界効果トランジスタは、ゲート絶縁層の厚さが10nm以上20nm以下であることを特徴とする半導体デバイス。 - 請求項7に記載の半導体デバイスであって、

前記対称電界効果トランジスタとして、

ゲート長が100nm以下である第1の電界効果トランジスタと、

ゲート絶縁層の厚さが10nm以上20nm以下である第2の電界効果トランジスタと、

を含むことを特徴とする半導体デバイス。 - 半導体デバイスの製造方法であって、

第1導電型の半導体の基板と、

前記基板内において前記第1導電型と反対の第2導電型である第1ソース領域及び第1ドレイン領域と、

前記基板上に形成され、厚さが60nm以上である第1ゲート絶縁層と、

前記第1ゲート絶縁層上に形成された第1ゲート電極と、

前記第1ゲート絶縁層下に設けられたチャネル領域と、

前記第1ドレイン領域と前記チャネル領域との間に絶縁領域と、

を備え、

前記第1ドレイン領域は前記第1ソース領域より前記第1ゲート電極から離れた位置に配置され、前記第1ゲート電極に対して前記第1ソース領域と前記第1ドレイン領域が非対称とされており、

前記第1ゲート絶縁層は、前記第1ソース領域側において前記第1ゲート電極よりもマージン距離だけ拡げられた拡張絶縁領域を有し、

前記第1ソース領域から前記第1ゲート電極の間には前記拡張絶縁領域以外の絶縁領域を有さず、

前記第1ソース領域から前記第1ゲート絶縁層の前記拡張絶縁領域下を介して前記第1ゲート電極下の前記基板内の領域まで延設された前記第2導電型の拡張ソース領域を有し、

前記第1ソース領域は、前記拡張ソース領域内に形成されている第1電界効果トランジスタと、

前記基板内において第2ソース領域及び第2ドレイン領域と、

前記基板上に形成された第2ゲート絶縁層と、

前記第2ゲート絶縁層上に形成された第2ゲート電極と、

を備え、

前記第2ゲート絶縁層は前記第1電界効果トランジスタの前記第1ゲート絶縁層の厚さより薄く、前記第1電界効果トランジスタよりも低い動作電圧を有する第2電界効果トランジスタと、

を含む半導体デバイスの製造方法であり、

前記拡張ソース領域と前記第2ソース領域の少なくとも一部を同一の製造工程にて形成することを特徴とする半導体デバイスの製造方法。 - 半導体デバイスの製造方法であって、

第1導電型の半導体の基板と、

前記基板内において前記第1導電型と反対の第2導電型である第1ソース領域及び第1ドレイン領域と、

前記基板上に形成され、厚さが60nm以上である第1ゲート絶縁層と、

前記第1ゲート絶縁層上に形成された第1ゲート電極と、

前記第1ゲート絶縁層下に設けられたチャネル領域と、

前記第1ドレイン領域と前記チャネル領域との間に絶縁領域と、

を備え、

前記第1ドレイン領域は前記第1ソース領域より前記第1ゲート電極から離れた位置に配置され、前記第1ゲート電極に対して前記第1ソース領域と前記第1ドレイン領域が非対称とされており、

前記第1ゲート絶縁層は、前記第1ソース領域側において前記第1ゲート電極よりもマージン距離だけ拡げられた拡張絶縁領域を有し、

前記第1ソース領域から前記第1ゲート電極の間には前記拡張絶縁領域以外の絶縁領域を有さず、

前記第1ソース領域から前記第1ゲート絶縁層の前記拡張絶縁領域下を介して前記第1ゲート電極下の前記基板内の領域まで延設された前記第2導電型の拡張ソース領域を有し、

前記第1ソース領域は、前記拡張ソース領域内に形成されている第1電界効果トランジスタと、

前記基板内において前記第2導電型であるウェル領域と、

前記ウェル領域内において前記第1導電型の第2ソース領域及び第2ドレイン領域と、

前記基板上に形成された第2ゲート絶縁層と、

前記第2ゲート絶縁層上に形成された第2ゲート電極と、

を備え、

前記第2ゲート絶縁層は前記第1電界効果トランジスタの前記第1ゲート絶縁層の厚さより薄く、前記第1電界効果トランジスタよりも低い動作電圧を有する第2電界効果トランジスタと、

を含む半導体デバイスの製造方法であり、

前記拡張ソース領域と前記ウェル領域を同一の製造工程にて形成することを特徴とする半導体デバイスの製造方法。 - 請求項11又は12に記載の半導体デバイスの製造方法であって、

前記半導体デバイスは、さらに、

前記基板内において第3ソース領域及び第3ドレイン領域と、

前記基板上に形成された第3ゲート絶縁層と、

前記第3ゲート絶縁層上に形成された第3ゲート電極と、

を備え、前記第2電界効果トランジスタの前記第2ゲート絶縁層の厚さより薄い前記第3ゲート絶縁層を有し、前記第2電界効果トランジスタよりも低い動作電圧を有する第3電界効果トランジスタを含み、

前記第1ソース領域の少なくとも一部と前記第3ソース領域の少なくとも一部を同一の製造工程にて形成することを特徴とする半導体デバイスの製造方法。 - 請求項13に記載の半導体デバイスの製造方法であって、

前記第3電界効果トランジスタのゲート長は100nm以下であることを特徴とする半導体デバイスの製造方法。 - 請求項11~14のいずれか1項に記載の半導体デバイスの製造方法であって、

前記第1ゲート絶縁層の厚さは、60nm以上100nm以下であり、

前記第2ゲート絶縁層の厚さは、10nm以上20nm以下であることを特徴とする半導体デバイスの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021068262A JP7320552B2 (ja) | 2021-04-14 | 2021-04-14 | 半導体デバイス及び半導体デバイスの製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021068262A JP7320552B2 (ja) | 2021-04-14 | 2021-04-14 | 半導体デバイス及び半導体デバイスの製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022163385A JP2022163385A (ja) | 2022-10-26 |

| JP7320552B2 true JP7320552B2 (ja) | 2023-08-03 |

Family

ID=83742230

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021068262A Active JP7320552B2 (ja) | 2021-04-14 | 2021-04-14 | 半導体デバイス及び半導体デバイスの製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7320552B2 (ja) |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002026140A (ja) | 2000-07-10 | 2002-01-25 | Nec Corp | 半導体装置及びその製造方法 |

| JP2005123644A (ja) | 1995-07-14 | 2005-05-12 | Seiko Instruments Inc | 半導体装置とその製造方法 |

| JP2007287798A (ja) | 2006-04-13 | 2007-11-01 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP2009290140A (ja) | 2008-05-30 | 2009-12-10 | Sanyo Electric Co Ltd | パワー半導体装置およびパワー半導体装置の製造方法 |

| JP2010118622A (ja) | 2008-11-14 | 2010-05-27 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP2012099541A (ja) | 2010-10-29 | 2012-05-24 | Fujitsu Semiconductor Ltd | 半導体装置及びその製造方法 |

| JP2019046874A (ja) | 2017-08-30 | 2019-03-22 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

-

2021

- 2021-04-14 JP JP2021068262A patent/JP7320552B2/ja active Active

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005123644A (ja) | 1995-07-14 | 2005-05-12 | Seiko Instruments Inc | 半導体装置とその製造方法 |

| JP2002026140A (ja) | 2000-07-10 | 2002-01-25 | Nec Corp | 半導体装置及びその製造方法 |

| JP2007287798A (ja) | 2006-04-13 | 2007-11-01 | Sanyo Electric Co Ltd | 半導体装置及びその製造方法 |

| JP2009290140A (ja) | 2008-05-30 | 2009-12-10 | Sanyo Electric Co Ltd | パワー半導体装置およびパワー半導体装置の製造方法 |

| JP2010118622A (ja) | 2008-11-14 | 2010-05-27 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP2012099541A (ja) | 2010-10-29 | 2012-05-24 | Fujitsu Semiconductor Ltd | 半導体装置及びその製造方法 |

| JP2019046874A (ja) | 2017-08-30 | 2019-03-22 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2022163385A (ja) | 2022-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6399468B2 (en) | Semiconductor device and method of manufacturing the same | |

| CN103189987B (zh) | 混合型有源-场间隙延伸漏极mos晶体管 | |

| US9768074B2 (en) | Transistor structure and fabrication methods with an epitaxial layer over multiple halo implants | |

| US8183626B2 (en) | High-voltage MOS devices having gates extending into recesses of substrates | |

| US8847332B2 (en) | Laterally diffused metal oxide semiconductor device having halo or pocket implant region | |

| US9660020B2 (en) | Integrated circuits with laterally diffused metal oxide semiconductor structures and methods for fabricating the same | |

| JP5191893B2 (ja) | 半導体素子及び形成方法 | |

| US7408234B2 (en) | Semiconductor device and method for manufacturing the same | |

| JP4686829B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| TWI455318B (zh) | 高壓半導體裝置及其製造方法 | |

| JP2010177292A (ja) | 半導体装置及び半導体装置の製造方法 | |

| US6084269A (en) | Semiconductor device and method of making | |

| CN113540252B (zh) | 半导体器件及制造方法 | |

| JP7320552B2 (ja) | 半導体デバイス及び半導体デバイスの製造方法 | |

| CN112802902B (zh) | 半导体器件及其制造方法 | |

| US11488871B2 (en) | Transistor structure with multiple halo implants having epitaxial layer over semiconductor-on-insulator substrate | |

| JP7253523B2 (ja) | 半導体デバイス及び半導体デバイスの製造方法 | |

| CN110957349A (zh) | 半导体装置及其制造方法 | |

| US20170263770A1 (en) | Semiconductor device and manufacturing method of the same | |

| JP7429211B2 (ja) | 半導体デバイス及び半導体デバイスの製造方法 | |

| US7335549B2 (en) | Semiconductor device and method for fabricating the same | |

| JPH02196434A (ja) | Mosトランジスタの製造方法 | |

| KR20020054109A (ko) | 트렌치 드레인 필드판을 갖는 전력소자 | |

| US8138565B2 (en) | Lateral double diffused metal oxide semiconductor device and method of making the same | |

| JP2024048439A (ja) | 半導体デバイス及び半導体デバイスの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210414 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220628 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220921 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230117 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230324 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230718 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230724 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7320552 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |