JP6883482B2 - センサ回路 - Google Patents

センサ回路 Download PDFInfo

- Publication number

- JP6883482B2 JP6883482B2 JP2017132422A JP2017132422A JP6883482B2 JP 6883482 B2 JP6883482 B2 JP 6883482B2 JP 2017132422 A JP2017132422 A JP 2017132422A JP 2017132422 A JP2017132422 A JP 2017132422A JP 6883482 B2 JP6883482 B2 JP 6883482B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- circuit

- control circuit

- physical quantity

- clock control

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3187—Built-in tests

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/282—Testing of electronic circuits specially adapted for particular applications not provided for elsewhere

- G01R31/2829—Testing of circuits in sensor or actuator systems

Description

<第1の実施形態>

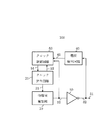

図1は、第1の実施形態のセンサ回路100のブロック図である。

第1の実施形態のセンサ回路100は、物理量検出部10と、クロック発生回路20と、出力ドライバ30と、電位検出回路40と、クロック制御回路50とで構成されている。

出力ドライバ30は、入力が物理量検出部10の出力に接続され、出力が出力端子31に接続される。出力ドライバ30は、物理量検出部10の物理量検出信号12を反転して、出力端子31にセンサ回路100の出力論理信号32を出力する。

クロック発生回路20は、物理量検出部10に検出動作を制御するための制御信号21を出力し、休止期間においてクロック制御回路50にサンプリング信号22を出力する。

クロック制御回路50は、電位検出信号41とサンプリング信号22と物理量検出信号12が入力され、クロック発生回路20にモード切替信号51を出力する。

物理量検出部10は、制御信号21がHレベルのときに動作期間になり、ホール素子の出力電圧を基準電圧と比較し、制御信号21がLレベルのときに休止期間になり、印加された磁束密度が所定の値より小さいとLレベル、所定の値より大きいとHレベルの物理量検出信号12を出力する。

図2は、第1の実施形態のセンサ回路100の動作を示すタイミング図である。

図2において、センサ回路100に印加される磁束密度をBin、物理量検出信号12の電圧をV12、出力端子31の電圧をV31、電位検出信号41の電圧をV41、制御信号21の電圧をV21、サンプリング信号22の電圧をV22、動作周期制御信号51の電圧をV51、とする。また、物理量検出部10が物理量を検出する閾値をBOP、検出を解除する閾値をBRP、とする。

ここで、時刻t4から時刻t7において、出力端子31に外部から強制的にHレベルを入力されると、クロック制御回路50は、時刻t5、t6において、サンプリング信号22によって電位検出信号41のHレベルを読み込み、更に、時刻t8において、サンプリング信号22によって電位検出信号41のLレベルを読み込む。

また、信号パターンをLHHLやHLLHとして説明したが、これに限らず、更に複雑な信号パターンや短い信号パターンであっても良い。

図3は、第2の実施形態のセンサ回路200のブロック図である。第2の実施形態のセンサ回路200は、図1のセンサ回路100に追加してタイムアウト時間を計数するカウンタ60を備えた。また、クロック制御回路50は、カウンタ60が出力するタイムアウト信号61を受ける構成とした。その他の構成については、図1のセンサ回路100と同一であるため、同一の構成要素には同一の符号を付し、説明は省略する。

図4は、第2の実施形態のセンサ回路200の動作を示すタイミング図である。

図4において、タイムアウト信号61の電圧をV61とする。また、図2のタイミング図と同一の動作については、その説明を省略する。

時刻t2において、外部からのノイズが出力端子31に重畳すると、図に示すように電圧V31が変動し、Hレベルの電位検出信号41が出力される。従って、クロック制御回路50は、サンプリング信号22によって電位検出信号41のHレベルを読み込む。

以上説明したように、第2の実施形態のセンサ装置では、タイムアウト信号61を出力するカウンタ60を備えたので、誤ってテストモードに切替えられるという誤動作をより確実に防止できる。

図5は、第3の実施形態のセンサ回路300のブロック図である。第3の実施形態のセンサ回路300は、図1のセンサ回路100に追加して制御信号21を受けてデッドタイム信号71を出力するデッドタイム制御回路70を備えた。また、クロック制御回路50は、デッドタイム制御回路70が出力するデッドタイム信号71を受ける構成とした。その他の構成については、図1のセンサ回路100と同一であるため、同一の構成要素には同一の符号を付し、説明は省略する。

図6は、第3の実施形態のセンサ回路300の動作を示すタイミング図である。

図6において、デッドタイム信号71の電圧をV71とする。また、図2のタイミング図と同一の動作については、その説明を省略する。

また、デッドタイム信号71は、制御信号21がHレベルになったことを受けてHレベルを出力すると説明したが、発明の趣旨に合えばどのような信号を起点にしても良い。

図7は、第4の実施形態のセンサ回路400のブロック図である。第4の実施形態のセンサ回路400は、図1のセンサ回路100に追加してリセット信号81を出力するリセット回路80を備えた。また、クロック制御回路50は、リセット回路80が出力するリセット信号81を受ける構成とした。その他の構成については、図1のセンサ回路100と同一であるため、同一の構成要素には同一の符号を付し、説明は省略する。

図8は、第4の実施形態のセンサ回路400の動作を示すタイミング図である。

図8において、リセット信号81の電圧をV81とする。また、図2のタイミング図と同一の動作については、その説明を省略する。

時刻t2において、外部からのノイズが出力端子31に重畳すると、図に示すように電圧V31が変動し、Hレベルの電位検出信号41が出力される。従って、クロック制御回路50は、サンプリング信号22によって電位検出信号41のHレベルを読み込む。

従って、時刻t4において、外部からのノイズが出力端子31に重畳したとしても、クロック制御回路50は、電位検出信号41を誤ってHLLHと認識することがなくなる。

なお、リセット信号81は、図8では、制御信号21がHレベルになったことを受けてLレベルになっているが、例えばワンショットパルスにしても良い。

20 クロック発生回路

30 出力ドライバ

31 出力端子

40 電位検出回路

50 クロック制御回路

60 カウンタ

70 デッドタイム制御回路

80 リセット回路

100、200、300、400 センサ回路

Claims (5)

- 動作期間と休止期間を備えた間欠動作をするセンサ回路であって、

印加される物理量に応じて2つの異なる電位レベルの物理量検出信号を出力する物理量検出部と、

前記物理量検出信号を受けて論理信号を出力端子へ出力する出力ドライバと、

前記物理量検出部へ前記間欠動作を制御するための制御信号を出力し、前記休止期間にサンプリング信号を出力するクロック発生回路と、

前記出力端子の電位を検出し、検出信号を出力する電位検出回路と、

前記サンプリング信号と前記検出信号が入力され、前記クロック発生回路へモード切替信号を出力するクロック制御回路と、を備え、

前記クロック制御回路は、前記検出信号を前記サンプリング信号に基づきサンプリングしたデータに所定の信号パターンを検出すると、前記クロック発生回路をテストモードに切替えるモード切替信号を出力する

ことを特徴とするセンサ回路。 - 前記クロック制御回路は、更に、前記物理量検出部の出力する前記物理量検出信号が入力され、

前記テストモードにおいて前記物理量検出信号が変化すると、通常モードに切替えるモード切替信号を出力する

ことを特徴とする請求項1に記載のセンサ回路。 - 更に、カウンタを備え、

前記カウンタは、前記検出信号の変動を受けて計数を開始し、タイムアウト時間に達すると前記クロック制御回路にタイムアウト信号を出力し、

前記クロック制御回路は、前記タイムアウト信号によって前記サンプリング信号をマスクする

ことを特徴とする請求項1または2に記載のセンサ回路。 - 更に、デッドタイム制御回路を備え、

前記デッドタイム制御回路は、前記休止期間への遷移後の所定期間に前記クロック制御回路にデッドタイム信号を出力し、

前記クロック制御回路は、前記デッドタイム信号によって前記サンプリング信号をマスクする

ことを特徴とする請求項1または2に記載のセンサ回路。 - 更に、リセット回路を備え、

前記リセット回路は、前記検出信号の幅が小さいことを検出すると前記クロック制御回路にリセット信号を出力し、

前記クロック制御回路は、前記リセット信号によって前記サンプリング信号をマスクする

ことを特徴とする請求項1または2に記載のセンサ回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW106127049A TWI701444B (zh) | 2016-08-26 | 2017-08-10 | 感測電路 |

| KR1020170107292A KR102303877B1 (ko) | 2016-08-26 | 2017-08-24 | 센서 회로 |

| US15/685,473 US10191124B2 (en) | 2016-08-26 | 2017-08-24 | Sensor circuit |

| CN201710741669.XA CN107783065B (zh) | 2016-08-26 | 2017-08-25 | 传感器电路 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016165827 | 2016-08-26 | ||

| JP2016165827 | 2016-08-26 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018036252A JP2018036252A (ja) | 2018-03-08 |

| JP2018036252A5 JP2018036252A5 (ja) | 2020-07-30 |

| JP6883482B2 true JP6883482B2 (ja) | 2021-06-09 |

Family

ID=61567306

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017132422A Active JP6883482B2 (ja) | 2016-08-26 | 2017-07-06 | センサ回路 |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP6883482B2 (ja) |

| KR (1) | KR102303877B1 (ja) |

| TW (1) | TWI701444B (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7465173B2 (ja) | 2020-08-03 | 2024-04-10 | エイブリック株式会社 | 磁気センサ回路 |

| JP2022153693A (ja) | 2021-03-30 | 2022-10-13 | エイブリック株式会社 | センサ装置 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6337270A (ja) * | 1986-07-31 | 1988-02-17 | Fujitsu Ltd | 半導体装置 |

| JPH1116395A (ja) * | 1997-06-25 | 1999-01-22 | Mitsubishi Electric Corp | 半導体記憶装置 |

| TW419592B (en) * | 1998-03-31 | 2001-01-21 | Hitachi Maxell | Current accumulating value detecting apparatus, current detecting apparatus and the battery set used |

| JP3672082B2 (ja) | 2000-09-14 | 2005-07-13 | 理研計器株式会社 | 熱線式ガスセンサーを用いたガス検知警報装置 |

| TW559970B (en) * | 2001-04-05 | 2003-11-01 | Kawasaki Microelectronics Inc | Test circuit, semiconductor product wafer having the test circuit, and method of monitoring manufacturing process using the test circuit |

| JP2006153699A (ja) * | 2004-11-30 | 2006-06-15 | Matsushita Electric Ind Co Ltd | 磁界検出装置 |

| US7295051B2 (en) * | 2005-06-15 | 2007-11-13 | Cypress Semiconductor Corp. | System and method for monitoring a power supply level |

| DE102006050832B4 (de) * | 2006-10-27 | 2012-07-26 | Infineon Technologies Ag | In-Betrieb-Test eines Signalpfades mittels wenigstens zweier Testsignale |

| JP4756701B2 (ja) | 2006-12-13 | 2011-08-24 | 三洋電機株式会社 | 電源電圧検出回路 |

| KR20100034030A (ko) * | 2007-06-27 | 2010-03-31 | 가부시키가이샤 어드밴티스트 | 검출 장치 및 시험 장치 |

| JP4786608B2 (ja) * | 2007-07-30 | 2011-10-05 | パナソニック株式会社 | 磁界検出装置 |

| JP2007322442A (ja) | 2007-09-07 | 2007-12-13 | Matsushita Electric Ind Co Ltd | 流量計測装置 |

| US8120354B2 (en) * | 2008-05-01 | 2012-02-21 | Broadband Discovery Systems, Inc. | Self-calibrating magnetic field monitor |

| JP5206487B2 (ja) | 2009-02-25 | 2013-06-12 | 富士通セミコンダクター株式会社 | 半導体集積回路の制御方法および半導体集積回路 |

| TWI408390B (zh) * | 2010-06-25 | 2013-09-11 | Princeton Technology Corp | 用於類比量測模組之控制電路與相關控制模組 |

| KR101254263B1 (ko) * | 2010-11-23 | 2013-04-12 | 삼성디스플레이 주식회사 | 전원 변환기, 직류-직류 변환기를 포함하는 표시 장치, 표시 장치를 포함하는 시스템 및 표시 장치의 구동 방법 |

| US8760217B2 (en) * | 2011-02-25 | 2014-06-24 | Qualcomm Incorporated | Semiconductor device having on-chip voltage regulator |

| KR101204205B1 (ko) * | 2011-05-13 | 2012-11-26 | 삼성전기주식회사 | 관성 센서 구동 장치 및 방법 |

| JP5957242B2 (ja) | 2012-03-01 | 2016-07-27 | アズビル株式会社 | 超音波流量計簡易診断装置 |

| US8943377B2 (en) | 2012-08-15 | 2015-01-27 | International Business Machines Corporation | On-chip detection of types of operations tested by an LBIST |

-

2017

- 2017-07-06 JP JP2017132422A patent/JP6883482B2/ja active Active

- 2017-08-10 TW TW106127049A patent/TWI701444B/zh active

- 2017-08-24 KR KR1020170107292A patent/KR102303877B1/ko active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018036252A (ja) | 2018-03-08 |

| TW201807417A (zh) | 2018-03-01 |

| KR20180023852A (ko) | 2018-03-07 |

| TWI701444B (zh) | 2020-08-11 |

| KR102303877B1 (ko) | 2021-09-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4965387B2 (ja) | 磁気センサ回路 | |

| US7746131B2 (en) | Reset signal filter | |

| CN107783065B (zh) | 传感器电路 | |

| JP6883482B2 (ja) | センサ回路 | |

| KR20100083729A (ko) | 검출 회로 및 센서 장치 | |

| JP4719190B2 (ja) | 2値化回路 | |

| KR100309233B1 (ko) | 싱글-엔드-제로 수신기 회로 | |

| KR101015785B1 (ko) | 접촉 감지 센서 및 감지 방법 | |

| CN110398622B (zh) | 过零检测电路和传感器装置 | |

| JP2007282182A (ja) | 2値化回路 | |

| US9608603B2 (en) | Sampling circuit | |

| JP4942195B2 (ja) | データ通信装置、データ通信システム及びデータ通信方法 | |

| JP6585977B2 (ja) | 半導体装置および発振回路の制御方法 | |

| KR100917999B1 (ko) | 가변 환경을 고려한 접촉 감지 센서 및 감지 방법 | |

| JP4955725B2 (ja) | 2値化回路 | |

| JP2014062825A (ja) | 電圧検出回路及び電圧検出方法 | |

| JP5059801B2 (ja) | 2値化回路 | |

| US9111644B2 (en) | Readout circuit and semiconductor device | |

| JP2022153693A5 (ja) | ||

| JP2009171206A (ja) | ばらつき調整回路 | |

| JP2007027885A (ja) | スイッチ動作検出回路 | |

| JP2005223837A (ja) | 信号判定装置 | |

| JP2008311998A (ja) | クロック数カウント回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200609 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200609 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210409 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210506 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210510 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6883482 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |