JP6690708B2 - 等化回路,受信回路および集積回路装置 - Google Patents

等化回路,受信回路および集積回路装置 Download PDFInfo

- Publication number

- JP6690708B2 JP6690708B2 JP2018523272A JP2018523272A JP6690708B2 JP 6690708 B2 JP6690708 B2 JP 6690708B2 JP 2018523272 A JP2018523272 A JP 2018523272A JP 2018523272 A JP2018523272 A JP 2018523272A JP 6690708 B2 JP6690708 B2 JP 6690708B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- equalization

- data

- signal

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000006243 chemical reaction Methods 0.000 claims description 65

- 230000005540 biological transmission Effects 0.000 claims description 40

- 238000013481 data capture Methods 0.000 claims description 14

- 238000012545 processing Methods 0.000 claims description 9

- 238000010586 diagram Methods 0.000 description 18

- 230000008054 signal transmission Effects 0.000 description 12

- 238000000034 method Methods 0.000 description 4

- 238000004891 communication Methods 0.000 description 3

- 230000001934 delay Effects 0.000 description 3

- 230000008030 elimination Effects 0.000 description 3

- 238000003379 elimination reaction Methods 0.000 description 3

- 238000011084 recovery Methods 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 230000003321 amplification Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/08—Modifications for reducing interference; Modifications for reducing effects due to line faults ; Receiver end arrangements for detecting or overcoming line faults

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04B—TRANSMISSION

- H04B3/00—Line transmission systems

- H04B3/02—Details

- H04B3/04—Control of transmission; Equalising

- H04B3/06—Control of transmission; Equalising by the transmitted signal

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03006—Arrangements for removing intersymbol interference

- H04L25/03012—Arrangements for removing intersymbol interference operating in the time domain

- H04L25/03019—Arrangements for removing intersymbol interference operating in the time domain adaptive, i.e. capable of adjustment during data reception

- H04L25/03057—Arrangements for removing intersymbol interference operating in the time domain adaptive, i.e. capable of adjustment during data reception with a recursive structure

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03878—Line equalisers; line build-out devices

- H04L25/03885—Line equalisers; line build-out devices adaptive

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03891—Spatial equalizers

- H04L25/03949—Spatial equalizers equalizer selection or adaptation based on feedback

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03006—Arrangements for removing intersymbol interference

- H04L2025/03433—Arrangements for removing intersymbol interference characterised by equaliser structure

- H04L2025/03439—Fixed structures

- H04L2025/03445—Time domain

- H04L2025/03471—Tapped delay lines

- H04L2025/03484—Tapped delay lines time-recursive

- H04L2025/0349—Tapped delay lines time-recursive as a feedback filter

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L25/00—Baseband systems

- H04L25/02—Details ; arrangements for supplying electrical power along data transmission lines

- H04L25/03—Shaping networks in transmitter or receiver, e.g. adaptive shaping networks

- H04L25/03006—Arrangements for removing intersymbol interference

- H04L2025/03592—Adaptation methods

- H04L2025/03598—Algorithms

- H04L2025/03681—Control of adaptation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/0054—Detection of the synchronisation error by features other than the received signal transition

- H04L7/0058—Detection of the synchronisation error by features other than the received signal transition detection of error based on equalizer tap values

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Cable Transmission Systems, Equalization Of Radio And Reduction Of Echo (AREA)

- Dc Digital Transmission (AREA)

Description

(付記1)

加算端子および減算端子を有し、入力信号の加算を行う第1加算回路と、

前記第1加算回路の出力信号を比較する比較回路と、

前記比較回路の出力データを保持するラッチ回路と、

等化係数が正の値のときに前記等化係数の絶対値に対応する第1信号を出力する第1デジタル/アナログ変換回路と、

前記等化係数が負の値のときに前記等化係数の絶対値に対応する第2信号を出力する第2デジタル/アナログ変換回路と、

前記ラッチ回路に保持されたデータに基づいて、前記第1デジタル/アナログ変換回路の出力端子および前記第2デジタル/アナログ変換回路の出力端子と、前記加算端子および前記減算端子の間の接続を切り替えるスイッチ回路と、を有する

ことを特徴とする等化回路。

前記第1デジタル/アナログ変換回路は、前記等化係数が負の値のときに前記等化係数が零である場合に対応する信号を出力し、

前記第2デジタル/アナログ変換回路は、前記等化係数が正の値のときに前記等化係数が零である場合に対応する信号を出力する

ことを特徴とする付記1に記載の等化回路。

さらに、

前記比較回路の出力データを保持して外部に出力する出力ラッチ回路を有する、

ことを特徴とする付記1または付記2に記載の等化回路。

前記第1信号および前記第2信号は、第1電流信号および第2電流信号であり、

前記第1デジタル/アナログ変換回路および前記第2デジタル/アナログ変換回路は、第1電流DACおよび第2電流DACである、

ことを特徴とする付記1乃至付記3のいずれか1項に記載の等化回路。

前記入力信号は、差動のシリアル信号である、

ことを特徴とする付記1乃至付記4のいずれか1項に記載の等化回路。

前記等化回路は、nを2以上の整数として、過去のn個のデータによるシンボル間干渉を除去するためのn個のシンボル間干渉除去ユニットを含み、

それぞれの前記シンボル間干渉除去ユニットは、前記ラッチ回路、前記第1デジタル/アナログ変換回路、前記第2デジタル/アナログ変換回路、および、前記スイッチ回路を含み、

前記n個の前記シンボル間干渉除去ユニットにおける前記ラッチ回路は、縦列接続されて過去のn個前までのシンボルのデータを保持するシフトレジスタを形成する、

ことを特徴とする付記1乃至付記5のいずれか1項に記載の等化回路。

さらに、

前記n個のシンボル間干渉除去ユニットにおける前記スイッチ回路の出力を加算する第2加算回路を有し、

前記第1加算回路は、前記入力信号に前記第2加算回路の出力を加算する、

ことを特徴とする付記6に記載の等化回路。

それぞれの前記シンボル間干渉除去ユニットにおける前記等化係数は、前記入力信号が伝送される信号伝送路の特性に基づいて決められる、

ことを特徴とする付記6または付記7に記載の等化回路。

付記1乃至付記8のいずれか1項に記載の等化回路と、

前記等化回路の出力データを受け取ってシリアル/パラレル変換し、受信パラレルデータを受信クロックと共に出力するデマルチプレクサと、

前記デマルチプレクサの出力に基づいて、前記等化回路で使用するデータ取り込みクロックを生成するデータ取り込みクロック生成回路と、を有する、

ことを特徴とする受信回路。

さらに、

受信信号を受け取って増幅し、増幅された前記入力信号を前記等化回路に出力する増幅回路と、

前記等化回路で使用する前記等化係数の情報を前記等化回路に供給する制御回路と、を有する、

ことを特徴とする付記9に記載の受信回路。

付記9または付記10に記載の受信回路と、

前記受信回路から前記受信パラレルデータおよび前記受信クロックを受け取って処理を行う内部回路と、

前記内部回路から送信パラレルデータおよび送信クロックを受け取ってパラレル/シリアル変換し、シリアル変換された送信信号を出力する送信回路と、を有する、

ことを特徴とする集積回路装置。

加算端子および減算端子を有し、入力信号の加算を行う第1加算回路と、

前記第1加算回路の出力信号を比較する比較回路と、

前記比較回路の出力データを保持するラッチ回路と、

等化係数の絶対値に対応する第3信号を出力するデジタル/アナログ変換回路と、

前記ラッチ回路に保持されたデータおよび前記等化係数の符号情報に基づいて、前記デジタル/アナログ変換回路の出力端子と、前記加算端子および前記減算端子の間の接続を切り替えるスイッチ回路と、を有する

ことを特徴とする等化回路。

前記スイッチ回路は、

前記ラッチ回路に保持されたデータに基づいて、前記デジタル/アナログ変換回路の出力端子と、自身の出力端子の間の接続を切り替える第1スイッチ回路と、

前記等化係数の符号情報に基づいて、前記第1スイッチ回路の出力端子と、前記加算端子および前記減算端子の間の接続を切り替える第2スイッチ回路と、を有する、

ことを特徴とする付記12に記載の等化回路。

さらに、

前記比較回路の出力データを保持して外部に出力する出力ラッチ回路を有する、

ことを特徴とする付記12または付記13に記載の等化回路。

前記第3信号は、第3電流信号であり、

前記デジタル/アナログ変換回路は、電流DACである、

ことを特徴とする付記12乃至付記14のいずれか1項に記載の等化回路。

前記入力信号は、差動のシリアル信号である、

ことを特徴とする付記12乃至付記15のいずれか1項に記載の等化回路。

前記等化回路は、nを2以上の整数として、過去のn個のデータによるシンボル間干渉を除去するためのn個のシンボル間干渉除去ユニットを含み、

それぞれの前記シンボル間干渉除去ユニットは、前記ラッチ回路、前記デジタル/アナログ変換回路、および、前記スイッチ回路を含み、

前記n個のシンボル間干渉除去ユニットにおける前記ラッチ回路は、縦列接続されて過去のn個前までのシンボルのデータを保持するシフトレジスタを形成する、

ことを特徴とする付記12乃至付記16のいずれか1項に記載の等化回路。

さらに、

前記n個のシンボル間干渉除去ユニットにおける前記スイッチ回路の出力を加算する第2加算回路を有し、

前記第1加算回路は、前記入力信号に前記第2加算回路の出力を加算する、

ことを特徴とする付記17に記載の等化回路。

それぞれの前記シンボル間干渉除去ユニットにおける前記等化係数は、前記入力信号が伝送される信号伝送路の特性に基づいて決められる、

ことを特徴とする付記17または付記18に記載の等化回路。

付記12乃至付記19のいずれか1項に記載の等化回路と、

前記等化回路の出力データを受け取ってシリアル/パラレル変換し、受信パラレルデータを受信クロックと共に出力するデマルチプレクサと、

前記デマルチプレクサの出力に基づいて、前記等化回路で使用するデータ取り込みクロックを生成するデータ取り込みクロック生成回路と、を有する、

ことを特徴とする受信回路。

さらに、

受信信号を受け取って増幅し、増幅された前記入力信号を前記等化回路に出力する増幅回路と、

前記等化回路で使用する前記等化係数の情報を前記等化回路に供給する制御回路と、を有する、

ことを特徴とする付記20に記載の受信回路。

付記20または付記21に記載の受信回路と、

前記受信回路から前記受信パラレルデータおよび前記受信クロックを受け取って処理を行う内部回路と、

前記内部回路から送信パラレルデータおよび送信クロックを受け取ってパラレル/シリアル変換し、シリアル変換された送信信号を出力する送信回路と、を有する、

ことを特徴とする集積回路装置。

加算端子および減算端子を有し、入力信号の加算を行う第1加算回路と、

前記第1加算回路の出力信号を比較する比較回路と、

前記比較回路の出力データに基づく第1の値を保持するラッチ回路と、

等化係数の絶対値に対応する第4信号を出力するデジタル/アナログ変換回路と、

前記ラッチ回路に保持されたデータに基づいて、前記デジタル/アナログ変換回路の出力端子と、前記加算端子および前記減算端子の間の接続を切り替えるスイッチ回路と、を有し、

前記第1の値は、前記比較回路の出力データと、前記等化係数の符号情報を乗算した値である

ことを特徴とする等化回路。

前記等化回路は、nを2以上の整数として、過去のn個のデータによるシンボル間干渉を除去するためのn個のシンボル間干渉除去ユニットを含み、

それぞれの前記シンボル間干渉除去ユニットは、前記ラッチ回路、前記デジタル/アナログ変換回路、および、前記スイッチ回路を含み、

前記n個のシンボル間干渉除去ユニットにおける前記ラッチ回路は、縦列接続されて過去のn個前までのシンボルのデータを保持するシフトレジスタを形成する、

ことを特徴とする付記23に記載の等化回路。

それぞれの前記シンボル間干渉除去ユニットは、さらに、

前記比較回路の出力データの1つである、1つ前のシンボルのデータと前記1つ前のシンボルに対する等化係数の符号情報を乗算した第2の値と、現時点のシンボルに対する等化係数の符号情報と前記1つ前のシンボルに対する等化係数の符号情報の排他的論理和である第3の値との排他的論理和を取って前記第1の値を出力する第1エクスクルーシブオア回路を有し、

それぞれの前記シンボル間干渉除去ユニットにおいて、

前記ラッチ回路は、前記第1エクスクルーシブオア回路によって出力される前記第1の値を保持し、

前記デジタル/アナログ変換回路は、前記現時点のシンボルに対する等化係数の絶対値情報に対応する前記第4信号を出力する、

ことを特徴とする付記24に記載の等化回路。

さらに、

前記第3の値を出力する第2エクスクルーシブオア回路を有する、

ことを特徴とする付記25に記載の等化回路。

さらに、

前記n個のシンボル間干渉除去ユニットにおける前記スイッチ回路の出力を加算する第2加算回路を有し、

前記第1加算回路は、前記入力信号に前記第2加算回路の出力を加算する、

ことを特徴とする付記24乃至付記26のいずれか1項に記載の等化回路。

それぞれの前記シンボル間干渉除去ユニットにおける前記等化係数は、前記入力信号が伝送される信号伝送路の特性に基づいて決められる、

ことを特徴とする付記24乃至付記27のいずれか1項に記載の等化回路。

さらに、

前記比較回路の出力データを保持して外部に出力する出力ラッチ回路を有する、

ことを特徴とする付記23乃至付記28のいずれか1項に記載の等化回路。

前記第4信号は、第4電流信号であり、

前記デジタル/アナログ変換回路は、電流DACである、

ことを特徴とする付記23乃至付記29のいずれか1項に記載の等化回路。

前記入力信号は、差動のシリアル信号である、

ことを特徴とする付記23乃至付記30のいずれか1項に記載の等化回路。

付記23乃至付記31のいずれか1項に記載の等化回路と、

前記等化回路の出力データを受け取ってシリアル/パラレル変換し、受信パラレルデータを受信クロックと共に出力するデマルチプレクサと、

前記デマルチプレクサの出力に基づいて、前記等化回路で使用するデータ取り込みクロックを生成するデータ取り込みクロック生成回路と、を有する、

ことを特徴とする受信回路。

さらに、

受信信号を受け取って増幅し、増幅された前記入力信号を前記等化回路に出力する増幅回路と、

前記等化回路で使用する前記等化係数の情報を前記等化回路に供給する制御回路と、を有する、

ことを特徴とする付記32に記載の受信回路。

付記32または付記33に記載の受信回路と、

前記受信回路から前記受信パラレルデータおよび前記受信クロックを受け取って処理を行う内部回路と、

前記内部回路からの送信パラレルデータおよび送信クロックを受け取ってパラレル/シリアル変換し、シリアル変換された送信信号を出力する送信回路と、を有する、

ことを特徴とする集積回路装置。

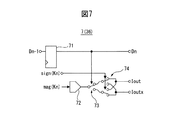

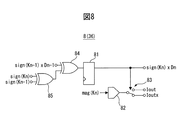

21-1,21-2,…,31-1,31-2,… 加算回路

22,32 比較回路

23,24-1〜24-n,33,34-1〜34-n,51,61,71,81 ラッチ回路(フリップフロップ)

25-1〜25-n,35-1〜35-n 乗算回路

26,36 シンボル間干渉除去ユニット

52,62,63,72,82 DAC(デジタル/アナログ変換回路:電流DAC)

53,64,73,74,83 スイッチ

54,84,85 エクスクルーシブオア回路(排他的論理和回路:XORゲート)

100 受信回路

101 フロントエンド回路

102 論理回路

103 クロック生成回路

111 増幅回路

112 等化回路(判定帰還型等化回路:DFE)

113 デマルチプレクサ(DMUX)

121 クロックデータリカバリ(CDR)部

122 制御回路

200 送信回路

300 内部回路(ユーザ回路)

Claims (15)

- 加算端子および減算端子を有し、入力信号の加算を行う第1加算回路と、

前記第1加算回路の出力信号を所定のしきい値と比較する比較回路と、

前記比較回路の出力データを保持するラッチ回路と、

等化係数が正の値のときに前記等化係数の絶対値に対応する第1信号を出力する第1デジタル/アナログ変換回路と、

前記等化係数が負の値のときに前記等化係数の絶対値に対応する第2信号を出力する第2デジタル/アナログ変換回路と、

前記ラッチ回路に保持されたデータに基づいて、前記第1デジタル/アナログ変換回路の出力端子および前記第2デジタル/アナログ変換回路の出力端子と、前記加算端子および前記減算端子の間の接続を切り替えるスイッチ回路と、を有し、

前記第1デジタル/アナログ変換回路は、前記等化係数が負の値のときに前記等化係数が零である場合に対応する信号を出力し、

前記第2デジタル/アナログ変換回路は、前記等化係数が正の値のときに前記等化係数が零である場合に対応する信号を出力する

ことを特徴とする等化回路。 - 前記第1信号および前記第2信号は、第1電流信号および第2電流信号であり、

前記第1デジタル/アナログ変換回路および前記第2デジタル/アナログ変換回路は、第1電流DACおよび第2電流DACである、

ことを特徴とする請求項1に記載の等化回路。 - 前記等化回路は、nを2以上の整数として、過去のn個のデータによるシンボル間干渉を除去するためのn個のシンボル間干渉除去ユニットを含み、

それぞれの前記シンボル間干渉除去ユニットは、前記ラッチ回路、前記第1デジタル/アナログ変換回路、前記第2デジタル/アナログ変換回路、および、前記スイッチ回路を含み、

前記n個の前記シンボル間干渉除去ユニットにおける前記ラッチ回路は、縦列接続されて過去のn個前までのシンボルのデータを保持するシフトレジスタを形成する、

ことを特徴とする請求項1または請求項2に記載の等化回路。 - 請求項1乃至請求項3のいずれか1項に記載の等化回路と、

前記等化回路の出力データを受け取ってシリアル/パラレル変換し、受信パラレルデータを受信クロックと共に出力するデマルチプレクサと、

前記デマルチプレクサの出力に基づいて、前記等化回路で使用するデータ取り込みクロックを生成するデータ取り込みクロック生成回路と、を有する、

ことを特徴とする受信回路。 - 請求項4に記載の受信回路と、

前記受信回路から前記受信パラレルデータおよび前記受信クロックを受け取って処理を行う内部回路と、

前記内部回路から送信パラレルデータおよび送信クロックを受け取ってパラレル/シリアル変換し、シリアル変換された送信信号を出力する送信回路と、を有する、

ことを特徴とする集積回路装置。 - 加算端子および減算端子を有し、入力信号の加算を行う第1加算回路と、

前記第1加算回路の出力信号を所定のしきい値と比較する比較回路と、

前記比較回路の出力データを保持するラッチ回路と、

等化係数の絶対値に対応する第3信号を出力するデジタル/アナログ変換回路と、

前記ラッチ回路に保持されたデータおよび前記等化係数の符号情報に基づいて、前記デジタル/アナログ変換回路の出力端子と、前記加算端子および前記減算端子の間の接続を切り替えるスイッチ回路と、を有し、

前記スイッチ回路は、

前記ラッチ回路に保持されたデータに基づいて、前記デジタル/アナログ変換回路の出力端子と、自身の出力端子の間の接続を切り替える第1スイッチ回路と、

前記等化係数の符号情報に基づいて、前記第1スイッチ回路の出力端子と、前記加算端子および前記減算端子の間の接続を切り替える第2スイッチ回路と、を有する

ことを特徴とする等化回路。 - 前記第3信号は、第3電流信号であり、

前記デジタル/アナログ変換回路は、電流DACである、

ことを特徴とする請求項6に記載の等化回路。 - 前記等化回路は、nを2以上の整数として、過去のn個のデータによるシンボル間干渉を除去するためのn個のシンボル間干渉除去ユニットを含み、

それぞれの前記シンボル間干渉除去ユニットは、前記ラッチ回路、前記デジタル/アナログ変換回路、および、前記スイッチ回路を含み、

前記n個のシンボル間干渉除去ユニットにおける前記ラッチ回路は、縦列接続されて過去のn個前までのシンボルのデータを保持するシフトレジスタを形成する、

ことを特徴とする請求項6または請求項7に記載の等化回路。 - 請求項6乃至請求項8のいずれか1項に記載の等化回路と、

前記等化回路の出力データを受け取ってシリアル/パラレル変換し、受信パラレルデータを受信クロックと共に出力するデマルチプレクサと、

前記デマルチプレクサの出力に基づいて、前記等化回路で使用するデータ取り込みクロックを生成するデータ取り込みクロック生成回路と、を有する、

ことを特徴とする受信回路。 - 請求項9に記載の受信回路と、

前記受信回路から前記受信パラレルデータおよび前記受信クロックを受け取って処理を行う内部回路と、

前記内部回路から送信パラレルデータおよび送信クロックを受け取ってパラレル/シリアル変換し、シリアル変換された送信信号を出力する送信回路と、を有する、

ことを特徴とする集積回路装置。 - 加算端子および減算端子を有し、入力信号の加算を行う第1加算回路と、

前記第1加算回路の出力信号を所定のしきい値と比較する比較回路と、

前記比較回路の出力データに基づく第1の値を保持するラッチ回路と、

等化係数の絶対値に対応する第4信号を出力するデジタル/アナログ変換回路と、

前記ラッチ回路に保持されたデータに基づいて、前記デジタル/アナログ変換回路の出力端子と、前記加算端子および前記減算端子の間の接続を切り替えるスイッチ回路と、を有し、

前記第1の値は、前記比較回路の出力データと、前記等化係数の符号情報を乗算した値である

ことを特徴とする等化回路。 - 前記等化回路は、nを2以上の整数として、過去のn個のデータによるシンボル間干渉を除去するためのn個のシンボル間干渉除去ユニットを含み、

それぞれの前記シンボル間干渉除去ユニットは、前記ラッチ回路、前記デジタル/アナログ変換回路、および、前記スイッチ回路を含み、

前記n個のシンボル間干渉除去ユニットにおける前記ラッチ回路は、縦列接続されて過去のn個前までのシンボルのデータを保持するシフトレジスタを形成する、

ことを特徴とする請求項11に記載の等化回路。 - 前記第4信号は、第4電流信号であり、

前記デジタル/アナログ変換回路は、電流DACである、

ことを特徴とする請求項11または請求項12に記載の等化回路。 - 請求項11乃至請求項13のいずれか1項に記載の等化回路と、

前記等化回路の出力データを受け取ってシリアル/パラレル変換し、受信パラレルデータを受信クロックと共に出力するデマルチプレクサと、

前記デマルチプレクサの出力に基づいて、前記等化回路で使用するデータ取り込みクロックを生成するデータ取り込みクロック生成回路と、を有する、

ことを特徴とする受信回路。 - 請求項14に記載の受信回路と、

前記受信回路から前記受信パラレルデータおよび前記受信クロックを受け取って処理を行う内部回路と、

前記内部回路からの送信パラレルデータおよび送信クロックを受け取ってパラレル/シリアル変換し、シリアル変換された送信信号を出力する送信回路と、を有する、

ことを特徴とする集積回路装置。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2016/068926 WO2017221427A1 (ja) | 2016-06-24 | 2016-06-24 | 等化回路,受信回路および集積回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2017221427A1 JPWO2017221427A1 (ja) | 2019-04-18 |

| JP6690708B2 true JP6690708B2 (ja) | 2020-04-28 |

Family

ID=60784399

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018523272A Active JP6690708B2 (ja) | 2016-06-24 | 2016-06-24 | 等化回路,受信回路および集積回路装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10476710B2 (ja) |

| EP (1) | EP3477869B1 (ja) |

| JP (1) | JP6690708B2 (ja) |

| CN (1) | CN109328434B (ja) |

| WO (1) | WO2017221427A1 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11005492B2 (en) * | 2018-12-31 | 2021-05-11 | Tektronix, Inc. | Dual output signal paths for signal source channels to optimize for bandwidth and amplitude range |

| CN117334230A (zh) * | 2022-06-23 | 2024-01-02 | 长鑫存储技术有限公司 | 数据接收电路、数据接收系统以及存储装置 |

| CN118410747A (zh) * | 2024-07-04 | 2024-07-30 | 山东云海国创云计算装备产业创新中心有限公司 | 一种信号均衡电路、接口、片上系统以及服务器 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001044895A (ja) | 1999-06-29 | 2001-02-16 | 3 Com Technol | 判定フィードバックエンコーダおよび受信機 |

| EP1145475A1 (en) * | 1999-10-21 | 2001-10-17 | Koninklijke Philips Electronics N.V. | An adaptive digital beamforming receiver to improve signal reception |

| US6993107B2 (en) * | 2001-01-16 | 2006-01-31 | International Business Machines Corporation | Analog unidirectional serial link architecture |

| US7433401B1 (en) * | 2003-05-22 | 2008-10-07 | Marvell International Ltd. | Mixed-mode signal processor architecture and device |

| US7233164B2 (en) | 2003-12-17 | 2007-06-19 | Rambus Inc. | Offset cancellation in a multi-level signaling system |

| DE09165754T1 (de) * | 2003-12-17 | 2014-07-03 | Rambus Inc. | Schnelles Signalisierungssystem mit adaptiver Vorverzerrung, Auslöschung von Reflexionen und Unterdrückung von Gleichspannungsversätzen |

| JP5072199B2 (ja) * | 2005-06-23 | 2012-11-14 | 株式会社東芝 | デジタル変調信号受信装置及びその受信方法 |

| CN1937600A (zh) * | 2005-09-05 | 2007-03-28 | 冲电气工业株式会社 | 均衡器和均衡方法 |

| JP4956840B2 (ja) * | 2008-03-14 | 2012-06-20 | 日本電気株式会社 | 判定帰還等化装置及び方法 |

| US8134885B2 (en) * | 2009-11-24 | 2012-03-13 | Bae Systems Information And Electronic Systems Integration Inc. | High-speed compression architecture for memory |

| US9806917B2 (en) * | 2014-02-21 | 2017-10-31 | Hitachi, Ltd. | Electric signal transmission apparatus |

| JP2015192200A (ja) * | 2014-03-27 | 2015-11-02 | 富士通株式会社 | 受信回路 |

-

2016

- 2016-06-24 WO PCT/JP2016/068926 patent/WO2017221427A1/ja unknown

- 2016-06-24 CN CN201680087084.4A patent/CN109328434B/zh active Active

- 2016-06-24 EP EP16906343.5A patent/EP3477869B1/en active Active

- 2016-06-24 JP JP2018523272A patent/JP6690708B2/ja active Active

-

2018

- 2018-12-04 US US16/209,616 patent/US10476710B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20190109738A1 (en) | 2019-04-11 |

| EP3477869A1 (en) | 2019-05-01 |

| EP3477869B1 (en) | 2020-11-04 |

| CN109328434A (zh) | 2019-02-12 |

| WO2017221427A1 (ja) | 2017-12-28 |

| JPWO2017221427A1 (ja) | 2019-04-18 |

| EP3477869A4 (en) | 2019-11-13 |

| US10476710B2 (en) | 2019-11-12 |

| CN109328434B (zh) | 2021-07-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7388908B2 (en) | High-speed adaptive interconnect architecture with nonlinear error functions | |

| CN108781195B (zh) | 用于提供高速均衡的方法和装置 | |

| US20140056346A1 (en) | High-speed parallel decision feedback equalizer | |

| US8301036B2 (en) | High-speed adaptive decision feedback equalizer | |

| CN103081422B (zh) | 用于判决反馈均衡器的自适应电路和方法 | |

| US10476710B2 (en) | Equalizer circuit, receiver circuit, and integrated circuit device | |

| CN109845204B (zh) | 信号处理装置、信号处理方法和程序 | |

| TWI828540B (zh) | 用於位元位準模式重計時器之相位內插器電路系統 | |

| JP2015220492A (ja) | 判定帰還型等化器 | |

| US11675732B2 (en) | Multiphase data receiver with distributed DFE | |

| JP5817516B2 (ja) | 受信回路 | |

| Shafik et al. | A 10 Gb/s hybrid ADC-based receiver with embedded analog and per-symbol dynamically enabled digital equalization | |

| CN113796016B (zh) | 符号判定装置和符号判定方法 | |

| CN111541633B (zh) | 使用间隔间定时误差估计的改进的时钟恢复 | |

| JP4764814B2 (ja) | 波形等化係数調整方法および回路、レシーバ回路、ならびに伝送装置 | |

| CN111566953B (zh) | 符号判定装置和符号判定方法 | |

| US11876648B2 (en) | DFE implementation for wireline applications | |

| US6765958B1 (en) | High-speed adaptive interconnect architecture | |

| Hoyos et al. | Mixed-signal equalization architectures for printed circuit board channels | |

| KR101775834B1 (ko) | 디지털 이퀄라이저 및 디지털 이퀄라이징 방법 | |

| US11347476B2 (en) | Digital filtering using combined approximate summation of partial products | |

| Li et al. | Sign3‐LMS data‐transition decision feedback equaliser | |

| WO2017037836A1 (ja) | 信号伝送装置および信号伝送システム | |

| JP2011217343A (ja) | 受信回路 | |

| JP2014230168A (ja) | 送信システム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181122 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190522 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200121 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200302 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200310 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200323 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6690708 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |