JP6541599B2 - 制御装置、基板処理システム、基板処理方法及びプログラム - Google Patents

制御装置、基板処理システム、基板処理方法及びプログラム Download PDFInfo

- Publication number

- JP6541599B2 JP6541599B2 JP2016063220A JP2016063220A JP6541599B2 JP 6541599 B2 JP6541599 B2 JP 6541599B2 JP 2016063220 A JP2016063220 A JP 2016063220A JP 2016063220 A JP2016063220 A JP 2016063220A JP 6541599 B2 JP6541599 B2 JP 6541599B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- condition

- forming

- laminated

- film forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B32—LAYERED PRODUCTS

- B32B—LAYERED PRODUCTS, i.e. PRODUCTS BUILT-UP OF STRATA OF FLAT OR NON-FLAT, e.g. CELLULAR OR HONEYCOMB, FORM

- B32B37/00—Methods or apparatus for laminating, e.g. by curing or by ultrasonic bonding

- B32B37/02—Methods or apparatus for laminating, e.g. by curing or by ultrasonic bonding characterised by a sequence of laminating steps, e.g. by adding new layers at consecutive laminating stations

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B32—LAYERED PRODUCTS

- B32B—LAYERED PRODUCTS, i.e. PRODUCTS BUILT-UP OF STRATA OF FLAT OR NON-FLAT, e.g. CELLULAR OR HONEYCOMB, FORM

- B32B37/00—Methods or apparatus for laminating, e.g. by curing or by ultrasonic bonding

- B32B37/14—Methods or apparatus for laminating, e.g. by curing or by ultrasonic bonding characterised by the properties of the layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/67155—Apparatus for manufacturing or treating in a plurality of work-stations

- H01L21/67207—Apparatus for manufacturing or treating in a plurality of work-stations comprising a chamber adapted to a particular process

- H01L21/67225—Apparatus for manufacturing or treating in a plurality of work-stations comprising a chamber adapted to a particular process comprising at least one lithography chamber

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/10—Measuring as part of the manufacturing process

- H01L22/12—Measuring as part of the manufacturing process for structural parameters, e.g. thickness, line width, refractive index, temperature, warp, bond strength, defects, optical inspection, electrical measurement of structural dimensions, metallurgic measurement of diffusions

-

- H10P14/24—

-

- H10P72/0604—

-

- H10P74/203—

-

- H10P74/238—

-

- H10P74/27—

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B32—LAYERED PRODUCTS

- B32B—LAYERED PRODUCTS, i.e. PRODUCTS BUILT-UP OF STRATA OF FLAT OR NON-FLAT, e.g. CELLULAR OR HONEYCOMB, FORM

- B32B2457/00—Electrical equipment

- B32B2457/14—Semiconductor wafers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67242—Apparatus for monitoring, sorting or marking

- H01L21/67253—Process monitoring, e.g. flow or thickness monitoring

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Chemical Vapour Deposition (AREA)

Description

本実施形態の基板処理装置について説明する。本実施形態の基板処理装置は、基板の一例としての半導体ウエハ(以下「ウエハ」という。)が垂直方向に所定の間隔をおいて多数枚保持した基板保持具を処理容器に収容し、多数枚のウエハに対して同時に膜を成膜することが可能なバッチ式の装置である。

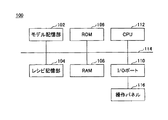

本実施形態の制御装置100について、図2に基づき説明する。図2は、本実施形態の制御装置の一例を示す概略構成図である。

(D−poly膜の目標膜厚)=(D−poly膜の膜厚の測定値)+(膜厚調整量)(1)

(膜厚調整量)=(積層膜の目標膜厚)−(積層膜の予測膜厚)(2)

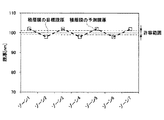

図5は、D−poly膜の目標膜厚を算出する方法を説明するための図である。図5では、ゾーンごとの積層膜の予測膜厚、積層膜の目標膜厚、D−poly膜の膜厚の測定値及びD−poly膜の目標膜厚を示している。図5中、積層膜の予測膜厚を太い破線で示し、積層膜の目標膜厚を細い点線で示し、D−poly膜の膜厚の測定値を細い実線で示し、D−poly膜の目標膜厚を細い破線で示している。

102 モデル記憶部

104 レシピ記憶部

106 ROM

108 RAM

110 I/Oポート

112 CPU

114 バス

116 操作パネル

W ウエハ

Claims (14)

- 基板に第1の膜を成膜した後に第2の膜を成膜して積層膜を形成する基板処理装置の動作を制御する制御装置であって、

前記第1の膜を成膜する第1の成膜条件と、前記第2の膜を成膜する第2の成膜条件と、を含む成膜条件を記憶するレシピ記憶部と、

前記第1の成膜条件が前記第1の膜の特性に与える影響を表す第1のプロセスモデルと、前記第2の成膜条件が前記第2の膜の特性に与える影響を表す第2のプロセスモデルと、を含むプロセスモデルを記憶するモデル記憶部と、

前記レシピ記憶部に記憶された前記第1の成膜条件及び前記第2の成膜条件により成膜された前記第1の膜と前記第2の膜とを含む前記積層膜の特性の測定値と、前記モデル記憶部に記憶された前記第2のプロセスモデルと、に基づいて、前記第2の成膜条件を調整し、前記第1の成膜条件及び調整された前記第2の成膜条件により前記積層膜を形成する場合に予測される前記積層膜の特性の予測値に基づいて、前記第1の成膜条件を調整するか否かを判定する制御部と、

を有する、制御装置。 - 前記制御部は、前記積層膜の特性の予測値が目標とする前記積層膜の特性を満たしていない場合、前記第1の成膜条件を調整すると判定する、

請求項1に記載の制御装置。 - 前記制御部は、前記第1の成膜条件を調整すると判定した場合、前記第1の成膜条件の調整が必要であることを報知する、

請求項1又は2に記載の制御装置。 - 前記制御部は、前記第1の成膜条件を調整すると判定した場合、前記レシピ記憶部に記憶された前記第1の成膜条件及び前記第2の成膜条件により成膜された前記第1の膜と前記第2の膜とを含む前記積層膜の特性の測定値と、前記モデル記憶部に記憶された前記第1のプロセスモデルと、に基づいて、前記積層膜の特性の予測値が前記積層膜の特性の目標値と一致するように前記第1の成膜条件を調整する、

請求項1乃至3のいずれか一項に記載の制御装置。 - 前記制御部は、前記第1の成膜条件を調整すると判定した場合、調整された前記第1の成膜条件と調整された前記第2の成膜条件とにより、前記積層膜を形成するように前記基板処理装置の動作を制御する、

請求項4に記載の制御装置。 - 前記積層膜は、前記基板処理装置において連続して成膜される膜である、

請求項1乃至5のいずれか一項に記載の制御装置。 - 前記第1の膜と前記第2の膜とは、同一の元素を含む膜である、

請求項1乃至6のいずれか一項に記載の制御装置。 - 前記積層膜の特性は膜厚である、

請求項1乃至7のいずれか一項に記載の制御装置。 - 前記積層膜の特性は不純物濃度である、

請求項1乃至7のいずれか一項に記載の制御装置。 - 基板に第1の膜を成膜した後に第2の膜を成膜して積層膜を形成する基板処理装置と、

前記基板処理装置の動作を制御する制御装置と、

を有し、

前記制御装置は、

前記第1の膜を成膜する第1の成膜条件と、前記第2の膜を成膜する第2の成膜条件と、を含む成膜条件を記憶するレシピ記憶部と、

前記第1の成膜条件が前記第1の膜の特性に与える影響を表す第1のプロセスモデルと、前記第2の成膜条件が前記第2の膜の特性に与える影響を表す第2のプロセスモデルと、を含むプロセスモデルを記憶するモデル記憶部と、

前記レシピ記憶部に記憶された前記第1の成膜条件及び前記第2の成膜条件により成膜された前記第1の膜と前記第2の膜とを含む前記積層膜の特性の測定値と、前記モデル記憶部に記憶された前記第2のプロセスモデルと、に基づいて、前記第2の成膜条件を調整し、前記第1の成膜条件及び調整された前記第2の成膜条件により前記積層膜を形成する場合に予測される前記積層膜の特性の予測値に基づいて、前記第1の成膜条件を調整するか否かを判定する制御部と、

を有する、基板処理システム。 - 基板に第1の成膜条件で第1の膜を成膜する第1の成膜工程と、前記第1の膜の上に第2の成膜条件で第2の膜を成膜する第2の成膜工程と、を含む成膜工程と、

前記成膜工程で成膜された前記第1の膜と前記第2の膜とを含む積層膜の特性を測定する測定工程と、

前記測定工程で測定された前記積層膜の特性の測定値と、前記第2の成膜条件が前記第2の膜の特性に与える影響を表す第2のプロセスモデルと、に基づいて、前記第2の成膜条件を調整する調整工程と、

前記第1の成膜条件及び前記調整工程で調整された前記第2の成膜条件により前記積層膜を形成する場合に予測される前記積層膜の特性の予測値に基づいて、前記第1の成膜条件を調整するか否かを判定する判定工程と、

を有する、基板処理方法。 - 前記成膜工程は、前記第1の膜に対して所定の処理を行う処理工程を含み、

前記処理工程は、前記第1の成膜工程の後であって、前記第2の成膜工程の前に行われる、

請求項11に記載の基板処理方法。 - 前記所定の処理は、前記第1の膜をエッチングするエッチング処理を含む、

請求項12に記載の基板処理方法。 - 請求項11乃至13のいずれか一項に記載の基板処理方法をコンピュータに実行させる、プログラム。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016063220A JP6541599B2 (ja) | 2016-03-28 | 2016-03-28 | 制御装置、基板処理システム、基板処理方法及びプログラム |

| TW106109248A TWI692026B (zh) | 2016-03-28 | 2017-03-21 | 控制裝置、基板處理系統、基板處理方法及程式 |

| US15/466,277 US10395934B2 (en) | 2016-03-28 | 2017-03-22 | Control device, substrate processing system, substrate processing method, and program |

| KR1020170036706A KR102147563B1 (ko) | 2016-03-28 | 2017-03-23 | 제어 장치, 기판 처리 시스템, 기판 처리 방법 및 프로그램 |

| CN201710191094.9A CN107236936B (zh) | 2016-03-28 | 2017-03-28 | 控制装置、基板处理系统、基板处理方法以及存储介质 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016063220A JP6541599B2 (ja) | 2016-03-28 | 2016-03-28 | 制御装置、基板処理システム、基板処理方法及びプログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017183311A JP2017183311A (ja) | 2017-10-05 |

| JP6541599B2 true JP6541599B2 (ja) | 2019-07-10 |

Family

ID=59898147

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016063220A Active JP6541599B2 (ja) | 2016-03-28 | 2016-03-28 | 制御装置、基板処理システム、基板処理方法及びプログラム |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10395934B2 (ja) |

| JP (1) | JP6541599B2 (ja) |

| KR (1) | KR102147563B1 (ja) |

| CN (1) | CN107236936B (ja) |

| TW (1) | TWI692026B (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6959191B2 (ja) | 2018-07-25 | 2021-11-02 | 旭化成エレクトロニクス株式会社 | 学習処理装置、学習処理方法、化合物半導体の製造方法、および、プログラム |

| JP7161896B2 (ja) * | 2018-09-20 | 2022-10-27 | 株式会社Screenホールディングス | 基板処理装置および基板処理システム |

| JP7594914B2 (ja) * | 2018-11-21 | 2024-12-05 | 東京エレクトロン株式会社 | 基板処理の条件設定支援方法、基板処理システム、記憶媒体及び学習モデル |

| CN110442930B (zh) * | 2019-07-19 | 2023-12-15 | Tcl华星光电技术有限公司 | 虚拟量测方法和虚拟量测装置 |

| JP7516203B2 (ja) * | 2019-12-17 | 2024-07-16 | 東京エレクトロン株式会社 | 基板処理方法及び基板処理システム |

| JP7442407B2 (ja) * | 2020-07-14 | 2024-03-04 | 東京エレクトロン株式会社 | 制御装置、システム及び制御方法 |

| US12265379B2 (en) * | 2022-05-05 | 2025-04-01 | Applied Materials, Inc. | Methods and mechanisms for adjusting film deposition parameters during substrate manufacturing |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05190457A (ja) * | 1992-01-17 | 1993-07-30 | Fuji Electric Co Ltd | 学習指示機能付半導体製造装置 |

| JPH0766291A (ja) * | 1993-08-31 | 1995-03-10 | Nippondenso Co Ltd | 半導体装置の製造方法 |

| JP3901958B2 (ja) * | 2000-08-24 | 2007-04-04 | 東京エレクトロン株式会社 | 熱処理装置設定温度の作成方法、および熱処理方法 |

| US8257546B2 (en) * | 2003-04-11 | 2012-09-04 | Applied Materials, Inc. | Method and system for monitoring an etch process |

| US20050287806A1 (en) * | 2004-06-24 | 2005-12-29 | Hiroyuki Matsuura | Vertical CVD apparatus and CVD method using the same |

| JP4511488B2 (ja) * | 2006-03-31 | 2010-07-28 | 株式会社堀場製作所 | 有機el素子の製造装置 |

| US7467064B2 (en) * | 2006-02-07 | 2008-12-16 | Timbre Technologies, Inc. | Transforming metrology data from a semiconductor treatment system using multivariate analysis |

| JP4942174B2 (ja) * | 2006-10-05 | 2012-05-30 | 東京エレクトロン株式会社 | 基板処理システムの処理レシピ最適化方法,基板処理システム,基板処理装置 |

| JP4464979B2 (ja) * | 2007-03-05 | 2010-05-19 | 東京エレクトロン株式会社 | 処理システム、処理方法、及び、プログラム |

| JP5212281B2 (ja) * | 2009-07-03 | 2013-06-19 | 日立電線株式会社 | 半導体光素子基板の製造方法 |

| JP2012004542A (ja) * | 2010-05-20 | 2012-01-05 | Tokyo Electron Ltd | シリコン膜の形成方法およびその形成装置 |

| JP5766647B2 (ja) * | 2012-03-28 | 2015-08-19 | 東京エレクトロン株式会社 | 熱処理システム、熱処理方法、及び、プログラム |

| JP5774532B2 (ja) * | 2012-03-28 | 2015-09-09 | 東京エレクトロン株式会社 | 連続処理システム、連続処理方法、及び、プログラム |

| JP5788355B2 (ja) * | 2012-03-29 | 2015-09-30 | 東京エレクトロン株式会社 | 熱処理システム、熱処理方法、及び、プログラム |

| US8994013B2 (en) | 2012-05-18 | 2015-03-31 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting element, light-emitting device, display device, electronic device, and lighting device |

| JP2014127627A (ja) * | 2012-12-27 | 2014-07-07 | Tokyo Electron Ltd | 薄膜形成装置の洗浄方法、薄膜形成方法、薄膜形成装置、及び、プログラム |

| JP6106519B2 (ja) * | 2013-05-09 | 2017-04-05 | 東京エレクトロン株式会社 | 基板処理方法、プログラム、制御装置、成膜装置及び基板処理システム |

| US9797042B2 (en) * | 2014-05-15 | 2017-10-24 | Lam Research Corporation | Single ALD cycle thickness control in multi-station substrate deposition systems |

-

2016

- 2016-03-28 JP JP2016063220A patent/JP6541599B2/ja active Active

-

2017

- 2017-03-21 TW TW106109248A patent/TWI692026B/zh active

- 2017-03-22 US US15/466,277 patent/US10395934B2/en active Active

- 2017-03-23 KR KR1020170036706A patent/KR102147563B1/ko active Active

- 2017-03-28 CN CN201710191094.9A patent/CN107236936B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| KR102147563B1 (ko) | 2020-08-24 |

| JP2017183311A (ja) | 2017-10-05 |

| US10395934B2 (en) | 2019-08-27 |

| TWI692026B (zh) | 2020-04-21 |

| US20170278714A1 (en) | 2017-09-28 |

| CN107236936B (zh) | 2020-03-03 |

| CN107236936A (zh) | 2017-10-10 |

| TW201801173A (zh) | 2018-01-01 |

| KR20170113201A (ko) | 2017-10-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6541599B2 (ja) | 制御装置、基板処理システム、基板処理方法及びプログラム | |

| TWI681356B (zh) | 控制裝置、基板處理系統、基板處理方法及程式 | |

| JP5788355B2 (ja) | 熱処理システム、熱処理方法、及び、プログラム | |

| JP5766647B2 (ja) | 熱処理システム、熱処理方法、及び、プログラム | |

| JP5049303B2 (ja) | 熱処理装置、熱処理装置の温度調整方法、及び、プログラム | |

| US9798317B2 (en) | Substrate processing method and control apparatus | |

| KR101149170B1 (ko) | 열처리 장치, 열처리 장치의 온도 조정 방법, 및 컴퓨터 프로그램을 기록한 기록 매체 | |

| JP6596316B2 (ja) | 熱処理システム、熱処理方法、及び、プログラム | |

| JP6066847B2 (ja) | 基板処理方法及び制御装置 | |

| JP5049302B2 (ja) | 熱処理装置、熱処理装置の温度調整方法、及び、プログラム | |

| JP5752634B2 (ja) | 熱処理システム、熱処理方法、及び、プログラム | |

| JP6267881B2 (ja) | 基板処理方法及び制御装置 | |

| US20170271218A1 (en) | Control device, substrate processing system, substrate processing method, and program | |

| JP6353802B2 (ja) | 処理システム、処理方法、及び、プログラム | |

| JP6378639B2 (ja) | 処理システム、処理方法、及び、プログラム | |

| JP6566897B2 (ja) | 制御装置、基板処理システム、基板処理方法及びプログラム | |

| JP6335128B2 (ja) | 熱処理システム、熱処理方法、及び、プログラム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180808 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190424 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190514 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190611 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6541599 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |