JP6539149B2 - 撮像装置及び撮像システム - Google Patents

撮像装置及び撮像システム Download PDFInfo

- Publication number

- JP6539149B2 JP6539149B2 JP2015159788A JP2015159788A JP6539149B2 JP 6539149 B2 JP6539149 B2 JP 6539149B2 JP 2015159788 A JP2015159788 A JP 2015159788A JP 2015159788 A JP2015159788 A JP 2015159788A JP 6539149 B2 JP6539149 B2 JP 6539149B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- differential amplifier

- input

- input terminal

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/78—Readout circuits for addressed sensors, e.g. output amplifiers or A/D converters

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

本発明の別の観点による撮像装置は、複数の画素と、前記複数の画素が接続された信号線と、前記信号線に電気的に接続された第1の入力端子と、基準電圧が入力される第2の入力端子とを有する差動増幅器と、前記差動増幅器に接続された第1の電流源と、前記差動増幅器にスイッチを介して接続された第2の電流源と、前記差動増幅器の前記第1の入力端子に電気的に接続された第1の入力端子、しきい値電圧が入力される第2の入力端子、及び、前記スイッチに接続された出力端子を有する比較部と、を有することを特徴とする。

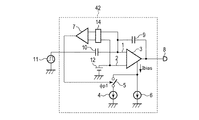

図面を参照しながら本発明の第1実施形態を説明する。図1(a)は、第1実施形態による撮像装置の構成を示すブロック図である。撮像装置は、画素アレイ100A、垂直走査回路20、信号処理回路40、参照信号発生回路50、カウンタ60、タイミング発生回路70及び水平走査回路80を有する。

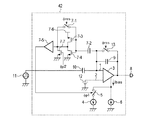

図4、図5及び図6を用いて第2実施形態を説明する。本実施形態は、第1実施形態の列アンプ42の構成を変形したものである。その他の部分の構成は第1実施形態と同様であるため説明を省略する。また、第1実施形態と同様の機能を有する構成要素には同一の符号を付し、その説明を省略又は簡略化することもある。

図7乃至図10を用いて第3実施形態を説明する。本実施形態は、第2実施形態の列アンプ42の構成を変形したものである。その他の部分の構成は第2実施形態と同様であるため説明を省略する。また、第2実施形態と同様の機能を有する構成要素には同一の符号を付し、その説明を省略又は簡略化することもある。

第4実施形態に係る撮像システムを説明する。撮像システムとして、デジタルスチルカメラ、デジタルカムコーダ、複写機、ファクシミリ、携帯電話、車載カメラ、観測衛星などがあげられる。図13に、第4実施形態に係る撮像システムの例としてデジタルスチルカメラのブロック図を示す。

2 差動増幅器の非反転入力端子

3 差動増幅器

4 ブースト用電流源

5 スイッチ

6 バイアス電流源

7 比較器

Claims (12)

- 光電変換により入射光に応じた信号を生成する画素と、

前記画素からの信号に基づく電圧が入力される第1の入力端子と、基準電圧が入力される第2の入力端子とを有する差動増幅器と、

前記差動増幅器にバイアス電流を供給する電流供給部と、

前記差動増幅器の前記第1の入力端子の電圧としきい値電圧との比較を行い、比較結果に基づく制御信号を前記電流供給部に出力する比較部と、を有し、

前記電流供給部は、前記比較部から入力される前記制御信号に応じて、前記差動増幅器に供給する前記バイアス電流の大きさを異ならせ、

前記制御信号が、前記画素からの信号に基づく電圧が変動したことを示す場合に、前記電流供給部は、前記差動増幅器に供給する前記バイアス電流を大きくすることを特徴とする撮像装置。 - 前記電流供給部は、第1の電流源と、第2の電流源と、スイッチとを有し、

前記電流供給部は、前記制御信号に応じて前記スイッチを切り替えることにより、前記第1の電流源のみが前記バイアス電流を供給する第1の状態と、前記第1の電流源及び前記第2の電流源の双方が前記バイアス電流を供給する第2の状態とを切り替えることを特徴とする請求項1に記載の撮像装置。 - 前記しきい値電圧は、前記差動増幅器の第2の入力端子の電圧に相当することを特徴とする請求項1又は2に記載の撮像装置。

- 前記比較部は、

比較器と、

前記比較器の入力オフセット電圧及び前記差動増幅器の入力オフセット電圧の差をキャンセルするオフセット電圧キャンセル部と

をさらに有することを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。 - 前記オフセット電圧キャンセル部は、クランプ容量を有し、

前記オフセット電圧キャンセル部は、前記クランプ容量に前記比較器の入力オフセット電圧と前記差動増幅器の入力オフセット電圧との差に相当する電圧を保持させて入力オフセット電圧のキャンセルを行うことを特徴とする請求項4に記載の撮像装置。 - 前記比較部は、前記しきい値電圧をシフトするしきい値電圧シフト部をさらに有することを特徴とする請求項4又は5に記載の撮像装置。

- 前記しきい値電圧シフト部は、前記入力オフセット電圧のキャンセルが行われた後に、前記しきい値電圧のシフトを行うことを特徴とする請求項6に記載の撮像装置。

- 前記比較部は、インバータと、クランプ容量とを有し、

前記クランプ容量は、前記差動増幅器の前記第2の入力端子の電圧と、前記インバータの論理しきい値と、前記差動増幅器の入力オフセット電圧とに基づく電圧を前記しきい値電圧として保持し、

前記差動増幅器の前記第1の入力端子の電圧が、前記クランプ容量を介して前記インバータに入力されることにより、前記比較が行われることを特徴とする請求項1又は2に記載の撮像装置。 - 前記比較部は、前記インバータの論理しきい値をシフトするしきい値電圧シフト部をさらに有することを特徴とする請求項8に記載の撮像装置。

- 前記しきい値電圧シフト部は、前記クランプ容量への電圧の保持が行われた後に、前記しきい値電圧のシフトを行うことを特徴とする請求項9に記載の撮像装置。

- 複数の画素と、

前記複数の画素が接続された信号線と、

前記信号線に電気的に接続された第1の入力端子と、基準電圧が入力される第2の入力端子とを有する差動増幅器と、

前記差動増幅器に接続された第1の電流源と、

前記差動増幅器にスイッチを介して接続された第2の電流源と、

前記差動増幅器の前記第1の入力端子に電気的に接続された第1の入力端子、しきい値電圧が入力される第2の入力端子、及び、前記スイッチに接続された出力端子を有する比較部と、を有することを特徴とする撮像装置。 - 請求項1乃至11のいずれか1項に記載の撮像装置と、

前記撮像装置から出力される信号を処理する信号処理部と

を有する撮像システム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015159788A JP6539149B2 (ja) | 2015-08-13 | 2015-08-13 | 撮像装置及び撮像システム |

| US15/217,526 US9954026B2 (en) | 2015-08-13 | 2016-07-22 | Imaging apparatus and imaging system |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015159788A JP6539149B2 (ja) | 2015-08-13 | 2015-08-13 | 撮像装置及び撮像システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017038315A JP2017038315A (ja) | 2017-02-16 |

| JP2017038315A5 JP2017038315A5 (ja) | 2018-08-02 |

| JP6539149B2 true JP6539149B2 (ja) | 2019-07-03 |

Family

ID=57994966

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015159788A Expired - Fee Related JP6539149B2 (ja) | 2015-08-13 | 2015-08-13 | 撮像装置及び撮像システム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9954026B2 (ja) |

| JP (1) | JP6539149B2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN106575075B (zh) * | 2014-07-21 | 2018-10-12 | 万睿视影像有限公司 | 具有自动感测功能的低功率成像器 |

| JP6632421B2 (ja) | 2016-02-22 | 2020-01-22 | キヤノン株式会社 | 固体撮像装置および撮像装置 |

| KR102546186B1 (ko) * | 2016-05-18 | 2023-06-22 | 에스케이하이닉스 주식회사 | 이미지 센싱 장치 및 그의 구동 방법 |

| JP6833531B2 (ja) | 2017-01-30 | 2021-02-24 | キヤノン株式会社 | 固体撮像装置 |

| TW201832548A (zh) * | 2017-02-21 | 2018-09-01 | 原相科技股份有限公司 | 逐一輸出不同感測像素單元之感測訊號電荷及重置訊號電荷之影像感測器及感測像素陣列 |

| CN108538867B (zh) * | 2017-03-01 | 2020-07-28 | 原相科技股份有限公司 | 影像感测器及感测像素阵列 |

| CN109040629A (zh) | 2017-06-09 | 2018-12-18 | 松下知识产权经营株式会社 | 摄像装置及照相机系统 |

| CN109218638B (zh) * | 2017-06-30 | 2021-04-02 | 京东方科技集团股份有限公司 | 像素读出电路及驱动方法、x射线探测器 |

| FR3084545B1 (fr) | 2018-07-27 | 2021-05-14 | Soc Fr De Detecteurs Infrarouges Sofradir | Dispositif d’echantillonnage avec gestion de la consommation electrique |

| KR20220112362A (ko) | 2021-02-04 | 2022-08-11 | 삼성전자주식회사 | 이미지 센서 |

| JP2022141460A (ja) * | 2021-03-15 | 2022-09-29 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子及び撮像装置 |

| WO2025249098A1 (ja) * | 2024-05-30 | 2025-12-04 | ソニーセミコンダクタソリューションズ株式会社 | センシングデバイス、電子機器およびセンシングデバイスの制御方法 |

| US20260006317A1 (en) * | 2024-06-27 | 2026-01-01 | Idea Sistemas Eletronicôs Ltda S.A. | Dynamic power management for photon detectors |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6473906A (en) * | 1987-09-16 | 1989-03-20 | Fujitsu Ltd | Hysteresis comparator |

| JP3067903B2 (ja) * | 1992-08-20 | 2000-07-24 | 沖電気工業株式会社 | アナログ/ディジタル変換器 |

| JP3793016B2 (ja) | 2000-11-06 | 2006-07-05 | キヤノン株式会社 | 固体撮像装置及び撮像システム |

| JP4311181B2 (ja) * | 2003-12-05 | 2009-08-12 | ソニー株式会社 | 半導体装置の制御方法および信号処理方法並びに半導体装置および電子機器 |

| JP5156434B2 (ja) | 2008-02-29 | 2013-03-06 | キヤノン株式会社 | 撮像装置および撮像システム |

| JP5484208B2 (ja) | 2010-06-14 | 2014-05-07 | キヤノン株式会社 | 撮像装置 |

| JP5645543B2 (ja) | 2010-08-20 | 2014-12-24 | キヤノン株式会社 | 撮像装置 |

| JP5814539B2 (ja) | 2010-11-17 | 2015-11-17 | キヤノン株式会社 | 撮像装置 |

| JP2012124835A (ja) * | 2010-12-10 | 2012-06-28 | Konica Minolta Advanced Layers Inc | 固体撮像装置 |

| JP2015080178A (ja) | 2013-10-18 | 2015-04-23 | キヤノン株式会社 | 撮像素子、撮像装置、カメラ、および、撮像装置の駆動方法 |

| JP6300488B2 (ja) | 2013-10-22 | 2018-03-28 | キヤノン株式会社 | 撮像装置、固体撮像素子及びカメラ |

| JP6391290B2 (ja) | 2014-05-08 | 2018-09-19 | キヤノン株式会社 | 撮像装置 |

| JP2016019137A (ja) | 2014-07-08 | 2016-02-01 | キヤノン株式会社 | 固体撮像装置及びその駆動方法 |

| US9979916B2 (en) | 2014-11-21 | 2018-05-22 | Canon Kabushiki Kaisha | Imaging apparatus and imaging system |

| US9854231B2 (en) * | 2014-12-18 | 2017-12-26 | General Electric Company | Silicon photomultipliers with internal calibration circuitry |

-

2015

- 2015-08-13 JP JP2015159788A patent/JP6539149B2/ja not_active Expired - Fee Related

-

2016

- 2016-07-22 US US15/217,526 patent/US9954026B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20170048475A1 (en) | 2017-02-16 |

| JP2017038315A (ja) | 2017-02-16 |

| US9954026B2 (en) | 2018-04-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6539149B2 (ja) | 撮像装置及び撮像システム | |

| US8400546B2 (en) | Image capturing device, image capturing system, and method of driving image capturing device | |

| JP5856392B2 (ja) | 固体撮像装置およびカメラ | |

| US9438830B2 (en) | Analog-to-digital converter and CMOS image sensor including the same | |

| CN104079846B (zh) | 比较器、固态摄像器件、电子设备及驱动方法 | |

| US9344652B2 (en) | Photoelectric conversion apparatus and image pickup system including an ad conversion unit to convert a signal into a digital signal | |

| US8841595B2 (en) | Image sensor with sample and hold circuitry for addressing time variant noise | |

| US9838637B2 (en) | Solid-state image sensor, method of controlling the same, image sensing system, and camera | |

| JP6739288B2 (ja) | 固体撮像装置、その制御方法、撮像システム及びカメラ | |

| JP2016042633A (ja) | 撮像装置、撮像システム及び撮像システムの駆動方法 | |

| US10044964B2 (en) | Column signal processing unit with driving method for photoelectric conversion apparatus, photoelectric conversion apparatus, and image pickup system | |

| WO2019107084A1 (ja) | 固体撮像装置、及びab級スーパーソースフォロワ | |

| US10811448B2 (en) | Solid-state imaging device | |

| US20160050380A1 (en) | Solid-state imaging apparatus and imaging system | |

| US20160286152A1 (en) | Imaging apparatus, method of driving imaging apparatus, and imaging system | |

| JP2017050669A (ja) | 固体撮像装置および撮像システム | |

| CN107231534B (zh) | 像素输出电平控制器件及使用其的cmos图像传感器 | |

| KR20060022804A (ko) | 이미지 센서 검출회로 | |

| CN106060428B (zh) | 像素放大装置、包括其的cmos图像传感器及其操作方法 | |

| CN102821257B (zh) | 成像装置和成像系统 | |

| JP6029352B2 (ja) | 固体撮像装置 | |

| JP6532224B2 (ja) | 撮像装置、撮像システム、及び撮像装置の駆動方法 | |

| JP2016015651A (ja) | 撮像装置、撮像システム、撮像装置の駆動方法 | |

| JP6422319B2 (ja) | 撮像装置、及びそれを用いた撮像システム | |

| US9807333B2 (en) | Imaging apparatus and imaging system |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD05 | Notification of revocation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7425 Effective date: 20171214 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20180126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180620 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180620 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190410 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190509 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190607 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6539149 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| LAPS | Cancellation because of no payment of annual fees |